# Hard Disk Improved MFM Generator

#### **FEATURES**

- ☐ Single + 5 Volt Power Supply

- ☐ Write Precompensation

- ☐ Address Mark Generation

- ☐ 5 Mbit Data Rate

- □ Converts NRZ to MFM

- 20 Pin DIP

- ☐ n-Channel COPLAMOS® Silicon Gate Technology

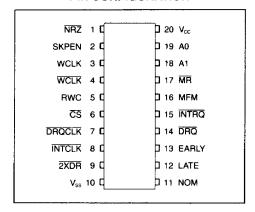

#### PIN CONFIGURATION

### **GENERAL DESCRIPTION**

The HDC 1100-12 "improved" MFM Generator converts serial NRZ data into an MFM (Modified Frequency Modulated) data stream. The MFM signal may be used to record information on a Winchester Disk.

In addition, the HDC 1100-12 generates Write Precompen-

sation signals required to compensate for bit shift effects on the recording medium.

The HDC 1100-12 has the ability to delete clock pulses in the outgoing data stream in order to record Address Marks.

# **DESCRIPTION OF PIN FUNCTIONS**

| PIN NUMBER | PIN FUNCTION                                  | NAME                       | FUNCTION                                                                                                                                      |  |  |  |  |

|------------|-----------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1 NRZ      |                                               | NON-RETURN-TO<br>ZERO      | NRZ data input that is strobed into the MFM generator by WCLK (1).                                                                            |  |  |  |  |

| 2          | SKPEN                                         | SKIP ENABLE                | This input arms the SKIP logic for recording Address Marks when set to a logic 1.                                                             |  |  |  |  |

| 3          | WCLK                                          | WRITE CLOCK                | Complimentary clock inputs. NRZ data is clocked into the MFM Generator on the high-to-low transition of                                       |  |  |  |  |

| 4          | WCLK                                          | WRITE CLOCK                | WCLK (pin 3).                                                                                                                                 |  |  |  |  |

| 5          | RWC                                           | REDUCED WRITE<br>CURRENT   | This signal when high, enables EARLY, LATE and NOM outputs.                                                                                   |  |  |  |  |

| 9          | 2 x DR                                        | 2 TIMES DATA RATE          | This input is used to latch EARLY, LATE, NOM and MFM outputs.                                                                                 |  |  |  |  |

| 10         | V <sub>ss</sub>                               | V <sub>SS</sub>            | Ground.                                                                                                                                       |  |  |  |  |

| 11         | NOM                                           | NOMINAL                    | Output signal from the Write Precompensation Logic used to signify that data is to be written nominal.                                        |  |  |  |  |

| 12         | LATE                                          | LATE                       | Output signal from the Write Precompensation Logic used to signify that data is to be shifted LATE before writing                             |  |  |  |  |

| 13         | EARLY                                         | EARLY                      | Output signal from the Write Precompensation Logic used to signify that data is to be shifted EARLY before writing.                           |  |  |  |  |

| 16         | MFM                                           | MFM DATA                   | This output contains the MFM encoded data derived from the NRZ (pin 1) line.                                                                  |  |  |  |  |

| 6          | CS                                            | CHIP SELECT                | Low input signal used to enable the Address decode logic.                                                                                     |  |  |  |  |

| 8          | INTCLK                                        | INTERRUPT<br>REQUEST CLOCK | A high-to-low transition on this line will latch the INTRQ (pin 15) at a logic 0.                                                             |  |  |  |  |

| 7          | DRQCLK                                        | DATA REQUEST<br>CLOCK      | A high-to-low transition on this line will latch the DRQ (pin 14) at a logic 0.                                                               |  |  |  |  |

| 15         | INTRQ                                         | INTERRUPT<br>REQUEST       | This output is latched at a logic 0 when INTCLK (pin 8) makes a high-to-low transition while the decode logic is disabled.                    |  |  |  |  |

| 14         | DRQ                                           | DATA REQUEST               | This output is latched at a logic 0 when DRQCLK (pin 7) makes a high-to-low transition while the decode logic is disabled.                    |  |  |  |  |

| 17         | MR                                            | MASTER RESET               | A low level on this line causes DRQ and INTRQ to set at a logic 1.                                                                            |  |  |  |  |

| 18, 19     | <b>A</b> <sub>0</sub> , <b>A</b> <sub>1</sub> | ADDRESS 1, 0               | When CS is low and the address lines are high, INTRO is cleared; if the address lines are low then DRQ gets cleared. (i.e. set at a logic 1). |  |  |  |  |

|            | +                                             | V <sub>cc</sub>            | +5V power supply input.                                                                                                                       |  |  |  |  |

| 20         | V <sub>cc</sub>                               | V <sub>CC</sub>            | 1 . 2 . F                                                                                                                                     |  |  |  |  |

## **OPERATION**

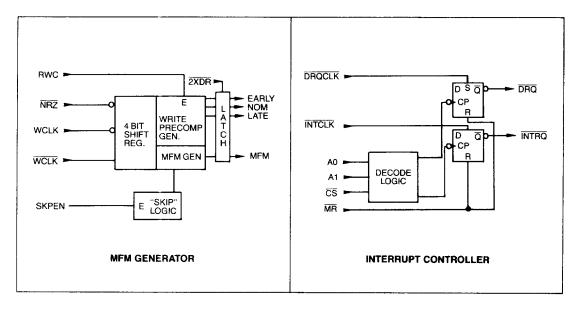

The HDC 1100-12 is divided into two sections: MFM Generator and Interrupt Logic. The MFM Generator converts NRZ data into MFM data and provides Write Precompensation signals. The Interrupt Logic may be used to generate Interrupt signals. The two sections of the device are isolated and have no common input or output signals.

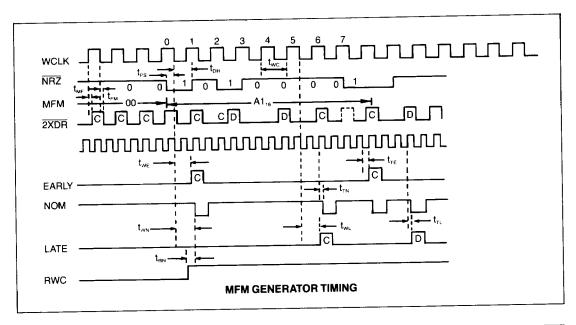

Prior to entering data, the SKPEN line must be set to a logic 0 to enable only clocks in the data stream. Data is entered on the NRZ line and strobed on the high-to-low transition of WCLK. The encoded NRZ data appears on the MFM (pin 16) output lagging by one clock cycle.

Write Precompensation signals EARLY, LATE, and NOM are generated as each data or clock pulse becomes available at the input when RWC is logic 1.

The SKPEN signal is used to record a unique data/clock pattern as an Address Mark, using A1 data with 0A clock. This pattern is used for synchronization prior to data or ID fields that are read from the disk.

When the SKPEN signal is set to a logic 1, the internal skip

logic is enabled. As long as zeroes are being shifted into the NRZ line, the device generates normal MFM data. On receipt of the first non-zero bit (typically the MSB of the A1 16) the skip logic begins to count WCLK cycles. When the MFM generator tries to produce a clock between data bits 2 and 3, the skip logic disables the MFM generator during that time. The result for A1  $_{\rm 16}$  data is a clock pattern of 0A  $_{\rm 16}$ instead of OE<sub>16</sub>. Although other data patterns may be used,

| MR | Α, | Ao | CS | DRQ            | INTRO          |

|----|----|----|----|----------------|----------------|

| 0  | Х  | X  | Х  | Н              | Н              |

| 1  | Х  | Х  | 1  | Q <sub>N</sub> | Q <sub>N</sub> |

| 1  | 0  | 0  | 0  | Н              | Q <sub>N</sub> |

| 1  | 1  | 1  | 0  | Q <sub>N</sub> | Н              |

| 1  | 1  | 0  | 0  | Q <sub>N</sub> | Q <sub>N</sub> |

| 1  | 0  | 1  | 0  | Q <sub>N</sub> | Q <sub>N</sub> |

X = Don't care

$Q_N = remains$  at previous state

INTERRUPT REQUEST LOGIC TABLE

.0°C to +50°C

+ 300°C

+7.0V

-55° to +150°C

the MSB of the pattern must be a 1 (80<sub>16</sub> or higher) in order to enable the skip logic at the proper time. After the skip logic has performed, it then disables itself and MFM data is recorded normally starting with the succeeding byte. To reenable the skip logic again, the SKPEN line must be strobed.

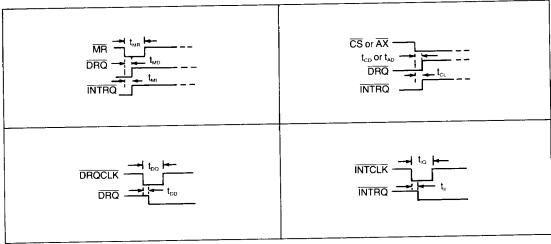

and Interrupt Requests (INTRQ) by selecting  $\overline{CS}$  (pin 6) in combination with A0 and A1. The  $\overline{MR}$  (Master Reset) signal is used to clear both  $\overline{DRQ}$  and  $\overline{INTRQ}$  simultaneously.  $\overline{DRQ}$  and  $\overline{INTRQ}$  can be set to a logic 0 only by a low level or  $\overline{DRQCLK}$  and  $\overline{INTCLK}$  respectively. The signal will remain at a logic 0 until cleared by a  $\overline{MR}$  or proper address selection via  $\overline{CS}$ , A1 and A0.

The Interrupt Logic is used to clear Data Requests (DRQ)

| LAST DATA SENT |          | LAST DATA SENT SENDING |   | EARLY | LATE | NOM |

|----------------|----------|------------------------|---|-------|------|-----|

| X              | 1        | 1                      | 0 | н     | L    | L   |

| X              | 0        | 1                      | 1 | L     | Н    | L   |

| 0              | 0        | 0                      | 1 | Н     | L    | L   |

| 1              | 0        | 0                      | 0 | L     | Н    | L   |

| ANY OTHER      | RPATTERN |                        |   | L     | L    | Н   |

### WRITE PRECOMPENSATION LOGIC TABLE

| MAXIMUM | GUARA | INTEED RATINGS | * |

|---------|-------|----------------|---|

Operating Temperature Range

Storage Temperature Range

Lead Temperature (soldering, 10 sec.)

\*Stresses above those listed may cause permanent damage to the device. This is a stress rating only and tudevice at these or at any other condition above those indicated in the operational sections of this specification is

DC ELECTRICAL CHARACTERISTICS:  $T_A = 0^{\circ}\text{C}$  to  $50^{\circ}\text{C}$ ;  $V_{\text{CC}} = +5\text{V} \pm 10\%$ ;  $V_{\text{SS}} = 0\text{V}$

| SYMBOL          | PARAMETER           | MIN   | TYP1 | MAX | UNIT | CONDITION                |

|-----------------|---------------------|-------|------|-----|------|--------------------------|

| V <sub>IL</sub> | Input Low Voltage   | - 0.2 |      | 0.8 | V    |                          |

| V <sub>IH</sub> | Input High Voltage  | 2.4   |      |     | V    |                          |

| V <sub>ol</sub> | Output Low Voltage  |       |      | 0.4 | V    | $I_{01} = 3.2 \text{mA}$ |

| V <sub>OH</sub> | Output High Voltage | 2.4   |      |     | Ιv   | $I_{OH} = -200 \mu A$    |

| $V_{cc}$        | Supply Voltage      | 4.5   | 5.0  | 5.5 | ĺ v  |                          |

| lcc             | Supply Current      |       |      | 100 | mA   | All Outputs Open         |

AC ELECTRICAL CHARACTERISTICS:  $T_A = 0^{\circ}C$  to  $50^{\circ}C$ ;  $V_{cc} = +5V \pm 10\%$ ;  $V_{ss} = 0V$

| SYMBOL          | PARAMETER                        | MIN | TYP1 | MAX  | UNIT | CONDITION |

|-----------------|----------------------------------|-----|------|------|------|-----------|

| t <sub>en</sub> | WCLK FREQUENCY                   |     |      | 5.25 | MHZ  |           |

| t <sub>os</sub> | Data Setup w.r.t. ↓ WCLK         | 10  |      |      | nsec |           |

| t <sub>o+</sub> | Data hold w.r.t. I WCLK          | 25  | 1    |      | nsec |           |

| t <sub>me</sub> | ↑ WCLK to ↑MFM delay             |     |      | 210  | nsec | Pin 1 LOW |

| t <sub>FM</sub> | ↓ WCLK to ↓ MFM delay            |     |      | 230  | nsec | Pin 1 LOW |

| t <sub>wn</sub> | Data delay to NOM from UCLK      |     |      | 240  | nsec |           |

| t <sub>we</sub> | Data delay to EARLY from  ↓ WCLK |     |      | 230  | nsec |           |

| t <sub>wL</sub> | Data delay to LATE from WCLK     |     |      | 230  | nsec |           |

| t <sub>me</sub> | Master reset pulse width         | 50  |      |      | nsec |           |

| t <sub>MD</sub> | J MR to ↑ DRQ                    |     |      | 150  | nsec |           |

| t <sub>mi</sub> | IMR to ↑ INTRQ                   |     |      | 150  | nsec |           |

| t <sub>oo</sub> | DRQCLK pulse width               | 50  |      |      | nsec |           |

| t <sub>io</sub> | INTCLK pulse width               | 50  |      |      | nsec |           |

| too             | DRQCLK to DRQ                    |     |      | 120  | nsec |           |

| t,,             | ↓ INTCLK to INTRQ                |     |      | 120  | nsec |           |

| t <sub>ad</sub> | ↓ AX to ↑ DRQ                    |     |      | 145  | nsec |           |

| t <sub>Al</sub> | ↑ AX to ↑ INTRQ                  |     |      | 160  | nsec |           |

| t <sub>co</sub> | ↓ CS to ↑ DRQ                    |     |      | 145  | nsec |           |

| t <sub>cı</sub> | ↓ CS to ¹ INTRQ                  | i   |      | 180  | nsec |           |

| t <sub>en</sub> | ↑ RWC to . NOM                   |     |      | 145  | nsec |           |

| t <sub>⊤E</sub> | 1 2XDR to * EARLY                |     |      | 75   | nsec |           |

| t <sub>tn</sub> | ↓ 2XDR to ↑ NOM                  |     |      | 75   | nsec |           |

| t <sub>TL</sub> |                                  |     |      | 75   | nsec |           |

Notes: 1. Typical Values are for  $T_{\scriptscriptstyle A}=25^{\circ}C$  and  $V_{\scriptscriptstyle CC}=\pm5.0V$ .

Circuit diagrams utilizing SMC products are included as a means of illustrating typical semiconductor applications; consequently complete information sufficient for construction purposes is not necessarily given. The

information has been carefully checked and is believed to be entirely reliable. However, no responsibility is

assumed for inaccuracies. Furthermore, such information does not convey to the purchaser of the semiconductor

devices described any license under the patent rights of SMC or others. SMC reserves the right to make changes

at any time in order to improve design and supply the best product possible.