# SPS Secondary-Side CC/CV Controller

## **General Description**

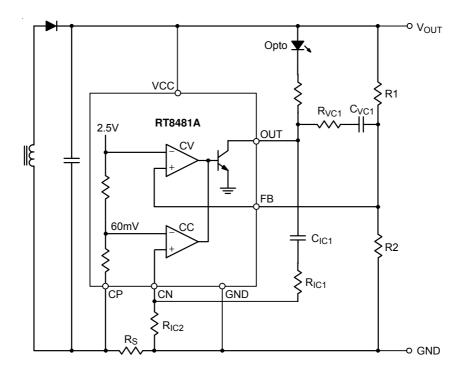

The RT8481A is a secondary-side CC/CV controller for SPS applications. It integrates a Constant Current (CC) regulating amplifier, a Constant Voltage (CV) regulating amplifier, and 2 precision reference voltages.

The CC regulating amplifier is featured with an extended input common mode voltage below GND level to insure the performance of low-side current sense, and a very low input offset voltage to guarantee the sensing accuracy. A 60mV reference voltage is internally connected between the inverting input of the CC regulating amplifier and the CP pin. The non-inverting input is the CN pin, at which the voltage will be regulated 60mV higher than that at the CP pin. The inverting input pin CP is equiped with –5V antireverse immunity.

The CV regulating amplifier with low input offset voltage is biased with a 2.5V reference voltage at the inverting input. The non-inverting input is the FB pin, at which the voltage will be regulated with 2.5V from GND. The CC and CV amplifiers share an open-collector output pin to minimize application circuit.

The RT8481A is available in the SOT-23-6 package.

#### **Features**

- Secondary-Side Constant Voltage (CV) and Constant Current (CC) Control

- 4.75V to 50V Operation Voltage Range

- ±1% Output Voltage Accuracy at Full Temperature Range

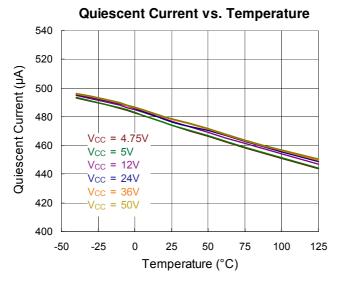

- 0.6mA Quiescent Current

- Smooth Transition Between CC and CV Control Loops

- -5V Negative Voltage Tolerance at CP pin

## **Applications**

- · Battery Chargers

- AC/DC Adaptors

- LED Drivers

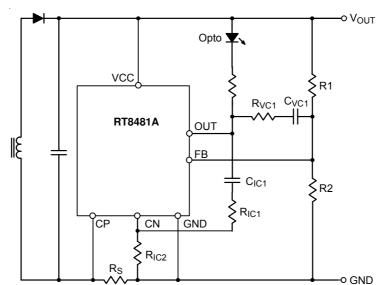

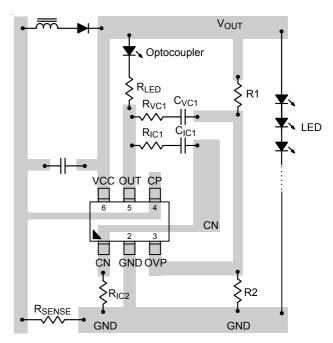

# **Simplified Application Circuit**

# **Ordering Information**

### RT8481A 🗆 🗖 Package Type E: SOT-23-6 Lead Plating System G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

# (TOP VIEW)

**Pin Configurations**

SOT-23-6

# **Marking Information**

3Y=DNN

3Y=: Product Code DNN: Date Code

## **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                   |  |  |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | CN       | Non-inverting Input of the CC Regulating Amp. It has 60mV offset from the CP pin. The CN pin should be connected to the "current-in" node of the current sensing resistor, Rs. |  |  |

| 2       | GND      | Ground.                                                                                                                                                                        |  |  |

| 3       | FB       | Non-inverting Input of the CV Regulating Amp. The pin should be connected to the mid-point of a resistor divider from "Secondary Side VOUT" (usually the VCC) to GND.          |  |  |

| 4       | СР       | Inverting Input of the CC Regulating Amp with –60mV offset from CN pin. The CP pin should be connected to the "current-out" node of the current sensing resistor.              |  |  |

| 5       | OUT      | Common Open-collector Output of CC and CV Regulating Amps. The pin sinks a regulated current and driver the opto-coupler to transmit the error signal to primary-side.         |  |  |

| 6       | VCC      | Supply Voltage Input. A $0.1\mu F$ bypass capacitor should be connected between VCC and GND.                                                                                   |  |  |

DS8481A-00 January 2016

## **Function Block Diagram & Typical Application Circuit**

## **Operation**

The available input voltage range is from 4.75V to 50V for the RT8481A. An internal 2.5V reference voltage is generated from VCC input power. The RT8481A can be used to monitor the transformer secondary-side output voltage by the CV control loop and regulate the output current by the CC control loop at the same time.

The transformer secondary-side output voltage can be monitored by the FB pin voltage. The sensed FB pin voltage is compared with the 2.5V internal reference. When the FB pin voltage is higher than 2.5V, the OUT pin will sink more current at the external opto-coupler and instruct the controller at primary-side to adjust the output voltage.

The output current can be regulated by the voltage across the CN and CP pins through the current sense resistor connected between the CN and CP pins. The voltage difference between CN and CP pins is compared with the 60mV internal reference. When the voltage difference between CN and CP pins is greater than 60mV, the OUT pin will sink more current at the external opto-coupler and instruct the controller at primary-side to adjust the output current.

# Absolute Maximum Ratings (Note 1)

| • Supply Input Voltage, V <sub>CC</sub>                                     | 0.3V to 60V             |

|-----------------------------------------------------------------------------|-------------------------|

| • CP                                                                        | 5V to 1V                |

| • CN                                                                        | 0.3V to 1V              |

| • FB                                                                        | 0.3V to V <sub>CC</sub> |

| • OUT                                                                       | 0.3V to 50V             |

| • OUT Current                                                               | 20mA to 20mA            |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                         |

| SOT-23-6                                                                    | 0.41W                   |

| Package Thermal Resistance (Note 2)                                         |                         |

| SOT-23-6, $\theta_{JA}$                                                     | 243.3°C/W               |

| Lead Temperature (Soldering, 10 sec.)                                       | 260°C                   |

| • Junction Temperature                                                      | 150°C                   |

| Storage Temperature Range                                                   | 65°C to 150°C           |

| ESD Susceptibility (Note 3)                                                 |                         |

| HBM (Human Body Model)                                                      | 2kV                     |

| MM (Machine Model)                                                          | 200V                    |

| Recommended Operating Conditions (Note 4)                                   |                         |

| • Supply Input Voltage, V <sub>CC</sub> (Note 5)                            |                         |

| Junction Temperature Range                                                  | 40°C to 125°C           |

#### **Electrical Characteristics**

( $V_{CC}$  = 12V,  $T_A$  = 25°C, unless otherwise specified)

| Parameter Symbol                                  |                                                                                   | Test Condition                                                                 | Min   | Тур   | Max   | Unit  |  |

|---------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Device Supply                                     |                                                                                   |                                                                                |       |       |       |       |  |

|                                                   |                                                                                   | CV Close Loop, V <sub>CN</sub> = V <sub>CP</sub> = 0V                          |       | 500   | 600   |       |  |

| Quiescent Current                                 | Icc                                                                               | CV Close Loop, $V_{CN} = V_{CP} = 0V$ , $T_A = -25^{\circ}C$ to $105^{\circ}C$ |       |       | 800   | μА    |  |

| Voltage Control Loop OP Amp                       |                                                                                   |                                                                                |       |       |       |       |  |

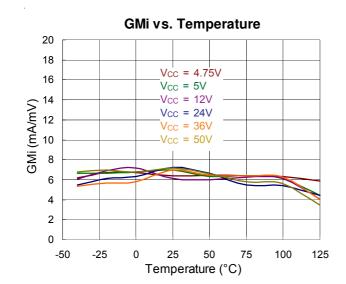

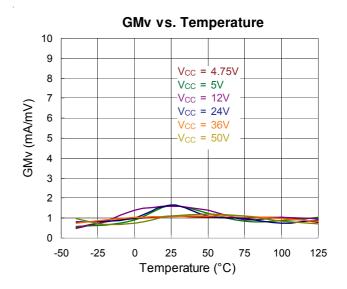

| Transconductance                                  | ansconductance GMv V <sub>CC</sub> = 4.75V to 45V                                 |                                                                                |       | 1     |       | S     |  |

| Power Supply Rejection Rate                       | PSRR                                                                              | V <sub>CC</sub> = 4.75V to 45V                                                 |       | 60    |       | dB    |  |

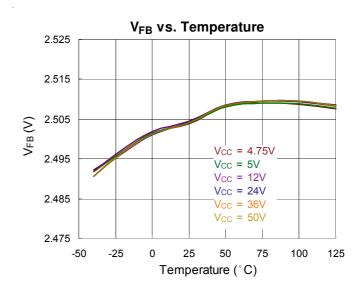

| ED Voltogo                                        | \/                                                                                | V <sub>CN</sub> = V <sub>CP</sub> = 0V                                         | 2.487 | 2.5   | 2.513 | V     |  |

| FB Voltage                                        | V <sub>FB</sub>                                                                   | $V_{CN} = V_{CP} = 0V$ , $T_A = -25^{\circ}C$ to $105^{\circ}C$                | 2.475 |       | 2.525 |       |  |

| FB Line Regulation                                | B Line Regulation $dV_{LINE-FB}$ $V_{CN} = V_{CP} = 0V$ , $V_{CC} = 4.75V$ to 45V |                                                                                |       | 0.2   |       | %     |  |

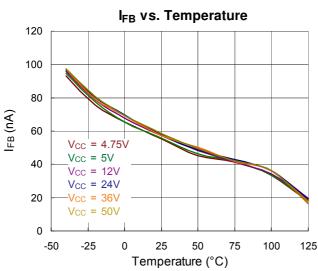

| CD Input Dice Current                             | I <sub>FB</sub>                                                                   | V <sub>FB</sub> = 2.4 to 2.6V                                                  |       |       | 100   |       |  |

| FB Input Bias Current                             |                                                                                   | $V_{FB}$ = 2.4 to 2.6V, $T_A$ = -25°C to 105°C                                 |       |       | 200   | nA    |  |

| Current Control Loop                              |                                                                                   |                                                                                |       |       |       |       |  |

| Transconductance $V_{CC} = 4.75V \text{ to } 45V$ |                                                                                   | V <sub>CC</sub> = 4.75V to 45V                                                 |       | 6     |       | S     |  |

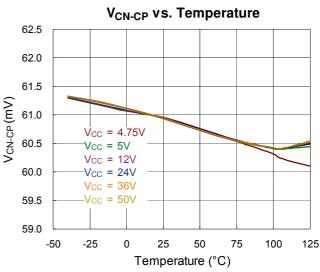

| CN CD Voltage                                     | \/                                                                                | V <sub>FB</sub> = 2.4V                                                         | 59    | 61    | 63    | ma\ / |  |

| CN – CP Voltage                                   | V <sub>CN-CP</sub>                                                                | T <sub>A</sub> = -25°C to 105°C                                                | 58    | 58 64 |       | mV    |  |

| Parameter               | Symbol                   | Test Condition                                               |                    | Тур | Max | Unit |  |

|-------------------------|--------------------------|--------------------------------------------------------------|--------------------|-----|-----|------|--|

| CN – CP Line Regulation | dV <sub>LINE-CN-CP</sub> | V <sub>FB</sub> = 2.4V, V <sub>CC</sub> = 4.75V to 45V       |                    | 0.2 |     | %/V  |  |

| CNI Innuit Diag Current | ICN                      | Close Loop                                                   |                    |     | 100 | ^    |  |

| CN Input Bias Current   |                          | Close Loop, T <sub>A</sub> = -25°C to 105°C                  | √ = −25°C to 105°C |     | 200 | nA   |  |

| Output Stage            |                          |                                                              |                    |     |     |      |  |

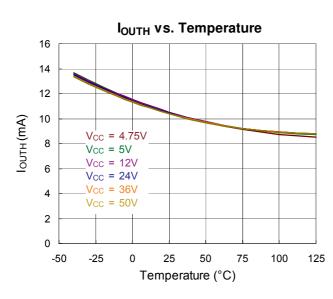

| OUT Maximum Sink        | la=                      | V <sub>OUT</sub> = 1.5V                                      |                    | 8   |     | m A  |  |

| Current                 | Гоитн                    | $V_{OUT}$ = 1.5V, $T_A$ = -25°C to 105°C                     |                    | 8   |     | mA   |  |

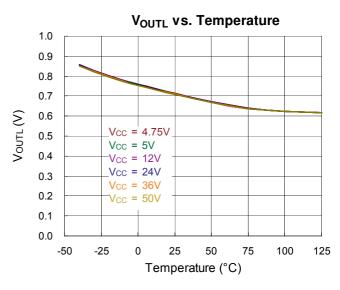

| OUT Minimum Voltage     | \/a=                     | I <sub>OUT</sub> = 2mA                                       | 1                  | 1   | 1.2 | V    |  |

| Oo'r Miriinium voltage  | Voutl                    | $I_{OUT} = 2mA, T_A = -25^{\circ}C \text{ to } 105^{\circ}C$ |                    |     | 1.5 | V    |  |

- **Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

- **Note 5.** RT8481A starts regulation at  $V_{CC} \ge 4.5V$ , and meets all parameter specs at  $V_{CC} \ge 4.75V$ .

# **Typical Operating Characteristics**

## **Application Information**

#### **Output Voltage Setting**

The voltage control loop is controlled via the first transconductance operational amplifier. An optocoupler which is directly connected to the output and an external resistor bridge is connected between the output positive line and the ground reference. The middle point is to be connected to the FB pin of RT8481A, where R2 is the upper resistor and R1 the lower resistor of the bridge. The relationship between R2 and R1 is shown below:

$$V_{OUT} = V_{FB} \times \frac{(R1 + R2)}{R2}$$

$$R1 = R2 \times \frac{(V_{OUT} - V_{FB})}{V_{FB}}$$

where V<sub>OUT</sub> is the desired maximum output voltage and V<sub>FB</sub> is the feedback voltage (2.5V typ). When under constant voltage control mode, the output voltage is fixed due to the R1/R2 resistor bridge. To avoid discharge of the load, the resistor bridge R1, R2, should be highly resistive. For this type of application a total value of  $100k\Omega$ (or more) would be appropriate for the resistors R1 and R2.

As an example, with R1 =  $80k\Omega$  and R2 =  $20k\Omega$ ,  $V_{OUT} = 12.5V$

#### **Output Current Setting**

The current control loop is controlled via the second transconductance operational amplifier. An optocoupler and the sense resistor, Rs, is placed in series on the output negative line. V<sub>CN-CP</sub> threshold is achieved externally by a resistor bridge tied to the Vref voltage reference. Its middle point is tied to the positive input of the current control operational amplifier and its foot is to be connected to the lower potential point of the sense resistor. The resistors of the bridge are matched to provide the best precision. With V<sub>CN-CP</sub> and Rs, the expected output current I<sub>OUT</sub> can be obtained as below equation.

$$I_{OUT} = \frac{V_{CN-CP}}{R_S}$$

As an example, with  $R_S = 200 \text{m}\Omega$

$V_{CN-CP}$  = 60mV,  $I_{OUT}$  = 300mA

where I<sub>OUT</sub> is the desired maximum output current, and

V<sub>CN-CP</sub> the threshold voltage for the current control loop. Note that R<sub>SENSE</sub> resistor should be chosen taking into account its maximum power dissipation (PLIM) during full load operation.

#### Compensation

Both the voltage control trans-conductance amplifier and the current control trans-conductance amplifier can be fully compensated. The output and negative inputs are directly accessible for external compensation components, as shown in the Typical Application Circuit.

The typical component values for the compensation network of voltage control loop is  $C_{VC1}$  = 2.2nF and  $R_{VC1}$ =  $22k\Omega$ . The typical component values for the compensation network of current control loop is C<sub>IC1</sub> = 2.2nF,  $R_{IC1}$  = 22k $\Omega$  and  $R_{IC2}$  = 1k $\Omega$ . However, in many application conditions, the current control loop can be stable even without compensation network ( $R_{IC2} = 0$ , no  $C_{IC1}$  nor  $R_{IC1}$ ).

When the voltage control loop is used as the voltage limit protection or the current control loop is used as the current limit protection, no compensation network is needed for the protecting control loop.

A resistor, R<sub>OPT</sub>, must be connected in series with the opto-coupler since it is part of the compensation network. Although the value of ROPT is not critical, it's recommended to be in the range from  $0.33k\Omega$  to  $(V_{OUT}-2)/(0.005)\Omega$ .

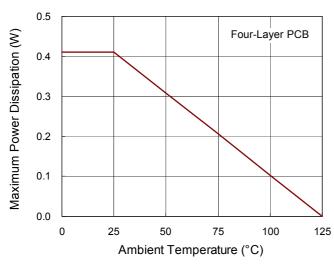

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where T<sub>J(MAX)</sub> is the maximum junction temperature, T<sub>A</sub> is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOT-23-6 packages, the thermal resistance,  $\theta_{JA}$ , is 243.3°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C - 25°C) / (243.3°C/W) = 0.41W for SOT-23-6 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve of Maximum Power Dissipation

#### **Layout Consideration**

For the best performance of the RT8481A, the following PCB Layout guidelines must be strictly followed.

- ▶ Place the R<sub>SENSE</sub> resistor as close to IC as possible.

- Keep the input/output traces as wide and short as possible.

Figure 2. PCB Layout Guide

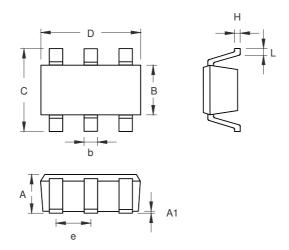

# **Outline Dimension**

| Cumbal | Dimensions | In Millimeters | Dimensions In Inches |       |  |  |  |

|--------|------------|----------------|----------------------|-------|--|--|--|

| Symbol | Min        | Max            | Min                  | Max   |  |  |  |

| Α      | 0.889      | 1.295          | 0.031                | 0.051 |  |  |  |

| A1     | 0.000      | 0.152          | 0.000                | 0.006 |  |  |  |

| В      | 1.397      | 1.803          | 0.055                | 0.071 |  |  |  |

| b      | 0.250      | 0.560          | 0.010                | 0.022 |  |  |  |

| С      | 2.591      | 2.997          | 0.102                | 0.118 |  |  |  |

| D      | 2.692      | 3.099          | 0.106                | 0.122 |  |  |  |

| е      | 0.838      | 1.041          | 0.033                | 0.041 |  |  |  |

| Н      | 0.080      | 0.254          | 0.003                | 0.010 |  |  |  |

| L      | 0.300      | 0.610          | 0.012                | 0.024 |  |  |  |

**SOT-23-6 Surface Mount Package**

#### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.