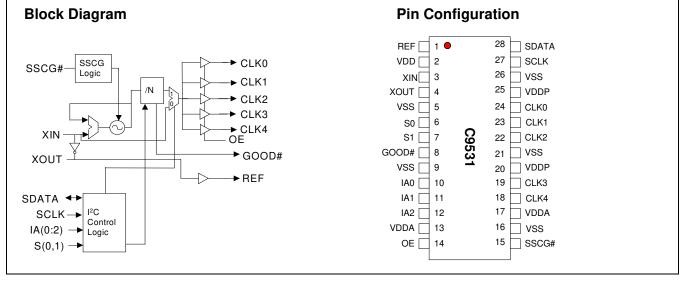

# PCIX I/O System Clock Generator with EMI Control Features

### Features

- Dedicated clock buffer power pins for reduced noise, crosstalk and jitter

- Input clock frequency of 25 MHz to 33 MHz

- Output frequencies of XINx1, XINx2, XINx3 and XINx4

- · One output bank of five clocks

- One REF XIN clock output

- SMBus clock control interface for individual clock disabling and SSCG control

- Output clock duty cycle is 50% (± 5%)

- < 250 ps skew between output clocks within a bank</p>

- Output jitter <175 ps</li>

- Spread Spectrum feature for reduced electromagnetic interference (EMI)

- OE pin for entire output bank enable control and testability

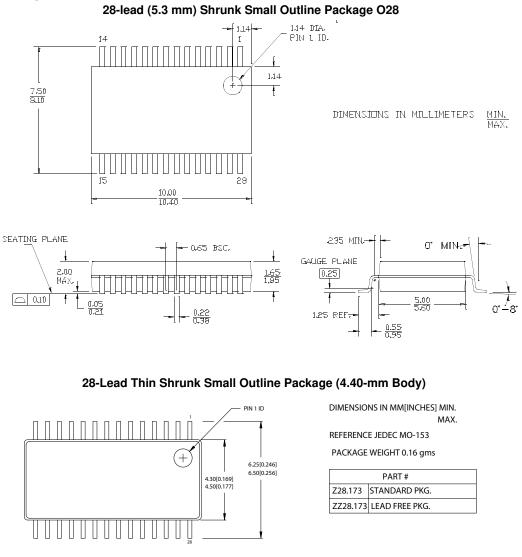

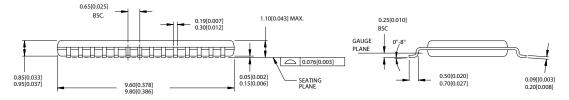

- 28-pin SSOP and TSSOP packages

Note:

1. XIN is the frequency of the clock on the device's XIN pin.

#### Table 1. Test Mode Logic Table<sup>[1]</sup>

| Input Pins |      |      | Output Pins |             |

|------------|------|------|-------------|-------------|

| OE         | S1   | S0   | CLK         | REF         |

| HIGH       | LOW  | LOW  | XIN         | XIN         |

| HIGH       | LOW  | HIGH | 2 * XIN     | XIN         |

| HIGH       | HIGH | LOW  | 3 * XIN     | XIN         |

| HIGH       | HIGH | HIGH | 4 * XIN     | XIN         |

| LOW        | Х    | Х    | Three-state | Three-state |

# **Pin Description**<sup>[3]</sup>

| Pin <sup>[2]</sup> | Name     | <b>PWR</b> <sup>[4]</sup> | I/O | Description                                                                                                                                                                                      |

|--------------------|----------|---------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3                  | XIN      | VDDA                      | I   | Crystal Buffer Input Pin. Connects to a crystal, or an external clock source. Serves as input clock TCLK, in Test mode.                                                                          |

| 4                  | XOUT     | VDDA                      | 0   | <b>Crystal Buffer Output Pin</b> . Connects to a crystal only. When a Can Oscillator is used or in test mode, this pin is kept unconnected.                                                      |

| 1                  | REF      | VDD                       | 0   | Buffered inverted outputs of the signal applied at Xin, typically 33.33 or 25.0 MHz.                                                                                                             |

| 14*                | OE       | VDD                       | Ι   | <b>Output Enable for Clock Bank</b> . Causes the CLK (0:4) output clocks to be in a three-state condition when driven to a logic low level.                                                      |

| 24, 23, 22, 19, 18 | CLK(0:4) | VDDP                      | 0   | A bank of five XINx1, XINx2, XINx3 and XINx4 output clocks.                                                                                                                                      |

| 8                  | GOOD#    | VDD                       | 0   | When his output signal is a logic low level, it indicates that the <b>output clocks of the bank are locked to the input reference clock</b> . This output is latched.                            |

| 6*, 7*             | S(0,1)   | VDD                       | Ι   | <b>Clock Bank Selection Bits</b> . These control the clock frequency that will be present on the outputs of the bank of buffers. See table on page one for frequency codes and selection values. |

| 20, 25             | VDDP     |                           | PWR | 3.3V common power supply pin for all PCI clocks CLK (0:4).                                                                                                                                       |

| 10*, 11*, 12*      | IA(0:2)  | VDD                       | I   | SMBus Address Selection Input Pins. See Table 3 on page 3.                                                                                                                                       |

| 15*                | SSCG#    | VDD                       | Ι   | <b>Spread Spectrum Clock Generator</b> . Enables Spread Spectrum clock modulation when at a logic low level, see Spread Spectrum Clocking on page 6.                                             |

| 28                 | SDATA    | VDD                       | I/O | Data for the Internal SMBus Circuitry. See Table 3 on page 3.                                                                                                                                    |

| 27                 | SCLK     | VDD                       | I   | Clock for the Internal SMBus Circuitry. See Table 3 on page 3.                                                                                                                                   |

| 13, 17             | VDDA     |                           | Ι   | <b>Power for Internal Analog Circuitry</b> . This supply should have a separately decoupled current source from VDD.                                                                             |

| 2                  | VDD      |                           | PWR | Power supply for internal core logic.                                                                                                                                                            |

| 5, 9, 16, 21, 26   | VSS      |                           | PWR | Ground pins for the device.                                                                                                                                                                      |

#### Notes:

Pin numbers ending with \* indicate that they contain device internal pull-up resistors that will insure that they are sensed as a logic 1 if no external circuitry is connected to them.

A bypass capacitor (0.1 μF) should be placed as close as possible to each V<sub>DD</sub> pin. If these bypass capacitors are not close to the pins their high frequency filtering characteristic will be cancelled by the lead inductance of the trace.

PWR = Power connection, I = Input, O = Output and I/O = both input and output functionality of the pin(s).

# Serial Data Interface

To enhance the flexibility and function of the clock synthesizer, a two-signal serial interface is provided. Through the Serial Data Interface, various device functions, such as individual clock output buffers, can be individually enabled or disabled. The registers associated with the Serial Data Interface initializes to their default setting upon power-up, and therefore use of this interface is optional. Clock device register changes are normally made upon system initialization, if any are required.

#### Table 2. Block Read and Block Write Protocol

### **Data Protocol**

The clock driver serial protocol accepts block write a operations from the controller. The bytes must be accessed in sequential order from lowest to highest byte (most significant bit first) with the ability to stop after any complete byte has been transferred. The C9531 does not support the Block Read function.

The block write protocol is outlined in *Table 2*. The addresses are listed in *Table 3*.

|       | Block Write Protocol                                          |  |  |  |  |  |  |

|-------|---------------------------------------------------------------|--|--|--|--|--|--|

| Bit   | Description                                                   |  |  |  |  |  |  |

| 1     | Start                                                         |  |  |  |  |  |  |

| 2:8   | Slave address – 7 bits                                        |  |  |  |  |  |  |

| 9     | Write = 0                                                     |  |  |  |  |  |  |

| 10    | Acknowledge from slave                                        |  |  |  |  |  |  |

| 11:18 | Command Code – 8 bits<br>'0000000' stands for block operation |  |  |  |  |  |  |

| 19    | Acknowledge from slave                                        |  |  |  |  |  |  |

| 20:27 | Byte Count – 8 bits                                           |  |  |  |  |  |  |

| 28    | Acknowledge from slave                                        |  |  |  |  |  |  |

| 29:36 | Data byte 1 – 8 bits                                          |  |  |  |  |  |  |

| 37    | Acknowledge from slave                                        |  |  |  |  |  |  |

| 38:45 | Data byte 2 – 8 bits                                          |  |  |  |  |  |  |

| 46    | Acknowledge from slave                                        |  |  |  |  |  |  |

|       |                                                               |  |  |  |  |  |  |

|       | Data Byte (N-1) - 8 bits                                      |  |  |  |  |  |  |

|       | Acknowledge from slave                                        |  |  |  |  |  |  |

|       | Data Byte N – 8 bits                                          |  |  |  |  |  |  |

|       | Acknowledge from slave                                        |  |  |  |  |  |  |

|       | Stop                                                          |  |  |  |  |  |  |

|       |                                                               |  |  |  |  |  |  |

|       |                                                               |  |  |  |  |  |  |

#### Table 3. SMBus Address Selection Table

| SMBus Address of the Device | IA0 Bit (Pin 10) | IA1 Bit (Pin 11) | IA2 Bit (Pin 12) |

|-----------------------------|------------------|------------------|------------------|

| DE                          | 0                | 0                | 0                |

| DC                          | 1                | 0                | 0                |

| DA                          | 0                | 1                | 0                |

| D8                          | 1                | 1                | 0                |

| D6                          | 0                | 0                | 1                |

| D4                          | 1                | 0                | 1                |

| D0                          | 0                | 1                | 1                |

| D2                          | 1                | 1                | 1                |

# **Serial Control Registers**

# Byte 0: Output Register

| Bit | @Pup | Name   | Description                                                                                                            |  |

|-----|------|--------|------------------------------------------------------------------------------------------------------------------------|--|

| 7   | 1    | TESTEN | Test Mode Enable.<br>1 = Normal operation, 0 = Test mode                                                               |  |

| 6   | 0    | SSEN   | Spread Spectrum modulation control bit (effective only when Bit 0 of this register is set to a 0) $0 = OFF$ , $1 = ON$ |  |

| 5   | 1    | SSSEL  | SSCG Spread width select. 1 = 0.5%, 0 = 1.0% See Table 4 below for clarification                                       |  |

| 4   | 0    | S1     | S1 Bank MSB frequency control bit (effective only when Bit 0 of this register is set to a 0)                           |  |

| 3   | 0    | S0     | 60 Bank LSB frequency control bit (effective only when Bit 0 of this register is set o a 0)                            |  |

| 2   | 0    |        | Not used                                                                                                               |  |

| 1   | 0    |        | Not used                                                                                                               |  |

| 0   | 1    | HWSEL  | Hardware/SMBus frequency control. 1 = Hardware (pins 6, 7, and 15), 0 = SMBus Byte 0 bits 3, 4, & 6                    |  |

### Table 4. Clarification Table for Byte0, bit 5

| Byte0, bit6 | Byte0, bit5 | Description                         |

|-------------|-------------|-------------------------------------|

| 0           | 0           | Frequency generated from second PLL |

| 0           | 1           | Frequency generated from XIN        |

| 1           | 0           | Spread @ -1.0%                      |

| 1           | 1           | Spread @ -0.5%                      |

### Table 5. Test Table

|                     | Outputs |     |                                                                                      |

|---------------------|---------|-----|--------------------------------------------------------------------------------------|

| Test Function Clock | CLK     | REF | Note                                                                                 |

| Frequency           | XIN/4   | XIN | XIN is the frequency of the clock that is present on the XIN input during test mode. |

### Byte 1: CPU Register

| Bit | @Pup | Name  | Description                                 |

|-----|------|-------|---------------------------------------------|

| 7   | 1    |       | Reserved                                    |

| 6   | 1    |       | Reserved                                    |

| 5   | 1    | REFEN | REF Output Enable<br>0 = Disable, 1= Enable |

| 4   | 1    |       | Reserved                                    |

| 3   | 1    |       | Reserved                                    |

| 2   | 1    |       | Reserved                                    |

| 1   | 1    |       | Reserved                                    |

| 0   | 1    |       | Reserved                                    |

### Byte 2: PCI Register

| Bit | @Pup | Name | Description                                  |

|-----|------|------|----------------------------------------------|

| 7   | 1    |      | Reserved                                     |

| 6   | 1    |      | Reserved                                     |

| 5   | 1    |      | Reserved                                     |

| 4   | 1    |      | CLK4 Output Enable<br>0 = Disable, 1= Enable |

### Byte 2: PCI Register (continued)

| Bit | @Pup | Name | Description                                  |

|-----|------|------|----------------------------------------------|

| 3   | 1    | 19   | CLK3 Output Enable<br>0 = Disable, 1= Enable |

| 2   | 1    | 22   | CLK2Output Enable<br>0 = Disable, 1= Enable  |

| 1   | 1    | 23   | CLK1 Output Enable<br>0 = Disable, 1= Enable |

| 0   | 1    | 24   | CLK0 Output Enable<br>0 = Disable, 1= Enable |

# **Output Clock Three-state Control**

All of the clocks in the Bank may be placed in a three-state condition by bringing their relevant OE pins to a logic low state. This transition to and from a three-state and active condition is a totally asynchronous event and clock glitching may occur during the transitioning states. This function is intended as a board level testing feature. When output clocks are being enabled and disabled in active environments the SMBus control register bits are the preferred mechanism to control these signals in an orderly and predictable manner.

The output enable pin contains an internal pull-up resistor that will insure that a logic 1 is maintained and sensed by the device if no external circuitry is connected to this pin.

# **Output Clock Frequency Control**

All of the output clocks have their frequency selected by the logic state of the S0 and S1 control bits. The source of these

control signals is determined by the SMBus register Byte 0 bit 0. At initial power up this bit is set of a logic 1 state and thus the frequency selections are controlled by the logic levels present on the device's S(0,1) pins. If the application does not use an SMBus interface then hardware frequency selection S(0,1) must be used. If it is desired to control the output clocks using an SMBus interface, then this bit (B0b0) must first be set to a low state. After this is done the device will use the contents of the internal SMBus register Bytes 0 bits 3 and 4 to control the output clock's frequency.

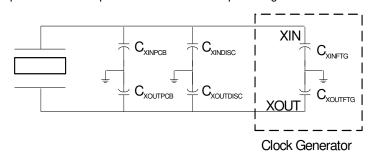

The following formula and schematic may be used to understand and calculate either the loading specification of a crystal for a design or the additional discrete load capacitance that must be used to provide the correct load to a known load rated crystal.

$$\mathbf{C_{L}} = \frac{(C_{XINPCB} + C_{XINFTG} + C_{XINDISC}) \mathbf{x} (C_{XOUTPCB}) + C_{XOUTFTG}) + C_{XOUTDISC})}{(C_{XINPCB} + C_{XINFTG} + C_{XINDISC}) \mathbf{x} (C_{XOUTPCB}) + C_{XOUTFTG}) + C_{XOUTDISC})}$$

where:

$C_{XTAL}$  = The load rating of the crystal.

C<sub>XINFTG</sub> = The clock generators XIN pin effective device internal capacitance to ground.

C<sub>XOUTFTG</sub> = The clock generators XOUT pin effective device internal capacitance to ground.

C<sub>XINPCB</sub> = The effective capacitance to ground of the crystal to device PCB trace.

$C_{XOUTPCB}$  = The effective capacitance to ground of the crystal to device PCB trace.

$C_{XINDISC}$  = Any discrete capacitance that is placed between the XIn pin and ground.

$C_{XOUTDISC}$  = Any discrete capacitance that is placed between the XIn pin and ground.

As an example and using this formula for this data sheet's device, a design that has no discrete loading capacitors ( $C_{DISC}$ ) and each of the crystal device PCB traces has a capacitance ( $C_{PCB}$ ) to ground of 4 pF (typical value) would calculate as:

$$\mathbf{C_L} = \frac{(4 \text{ pF} + 36 \text{ pF} + 0 \text{ pF}) \mathbf{x} (4 \text{ pF} + 36 \text{ pF} + 0 \text{ pF})}{(4 \text{ pF} + 36 \text{ pF} + 0 \text{ pF}) \mathbf{x} (4 \text{ pF} + 36 \text{ pF} + 0 \text{ pF})} = \frac{40 \times 40}{40 \times 40} = \frac{1600}{80} = 20 \text{ pF}.$$

Therefore, to obtain output frequencies that are as close to this data sheets specified values as possible, in this design example, you should specify a parallel cut crystal that is designed to work into a load of 20 pF.

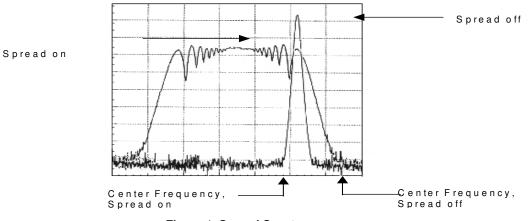

#### Spread Spectrum Clocking

#### **Down Spread Description**

Spread Spectrum is a modulation technique for distributing clock period over a certain bandwidth (called Spread Bandwidth). This technique allows the distribution of the undesirable electromagnetic energy (EMI) over a wide range of frequencies therefore reducing the average radiated energy present at any frequency over a given time period. As the spread is specified as a percentage of the resting (non-spread) frequency value, it is effective at the fundamental and, to a greater extent, at all of its harmonics.

In this device Spread Spectrum is enabled externally through pin 15 (SSCG#) or internally via SMBus Byte 0 Bit 0 and 6. Spread spectrum is enabled externally when the SSCG# pin is low. This pin has an internal device pull up resistor, which causes its state to default to a HIGH (spread spectrum modulation disabled) unless externally forced to a low. It may also be enabled by programming SMBus Byte 0 Bit 0 LOW (to enable SMBus control of the function) and then programming SMBus byte 0 bit 6 low to set the feature active.

Figure 1. Spread Spectrum

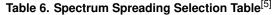

|                        | % of Frequer           |                        |             |

|------------------------|------------------------|------------------------|-------------|

| Output Clock Frequency | SMBus Byte 0 Bit 5 = 0 | SMBus Byte 0 Bit 5 = 1 | Mode        |

| 33.3 MHz (XIN)         | 1.0% (-1.0% + 0%)      | 0.5% (-0.5% + 0%)      | Down Spread |

| 66.6 MHz (XIN*2)       | 1.0% (-1.0% + 0%)      | 0.5% (-0.5% + 0%)      | Down Spread |

| 100.0 MHz (XIN*3)      | 1.0% (-1.0% + 0%)      | 0.5% (-0.5% + 0%)      | Down Spread |

| 133.3 MHz (XIN*4)      | 1.0% (-1.0% + 0%)      | 0.5% (-0.5% + 0%)      | Down Spread |

#### Note:

5. When SSCG is enabled, the device will down spread the clock over a range that is 1% of its resting frequency. This means that for a 100-MHz output clock frequency will sweep through a spectral range from 99 to 100 MHz.

# **Absolute Maximum Conditions**

| Parameter                         | Description                                        | Condition                                  | Min.             | Max.                  | Unit |

|-----------------------------------|----------------------------------------------------|--------------------------------------------|------------------|-----------------------|------|

| V <sub>DD</sub> ,V <sub>DDP</sub> | Core Supply Voltage                                |                                            | -0.5             | 4.6                   | V    |

| V <sub>DDA</sub>                  | Analog Supply Voltage                              |                                            | -0.5             | 4.6                   | V    |

| V <sub>IN</sub>                   | Input Voltage                                      | Relative to V <sub>SS</sub>                | -0.5             | V <sub>DD</sub> + 0.5 | VDC  |

| Τ <sub>S</sub>                    | Temperature, Storage                               | Non-functional                             | -65              | +150                  | °C   |

| T <sub>A</sub>                    | Temperature, Operating Ambient                     | Functional                                 | 0                | 70                    | °C   |

| TJ                                | Temperature, Junction                              | Functional                                 | -                | 150                   | °C   |

| ESD <sub>HBM</sub>                | ESD Protection (Human Body Model)                  | MIL-STD-883, Method 3015                   | 2000             | _                     | V    |

| Ø <sub>JC</sub>                   | Dissipation, Junction to Case                      | Mil-Spec 883E Method 1012.1                |                  |                       | °C/W |

| Ø <sub>JA</sub>                   | Dissipation, Junction to Ambient                   | JEDEC (JESD 51)                            |                  |                       | °C/W |

| UL-94                             | Flammability Rating                                | At 1/8 in.                                 | V                | ′—0                   |      |

| MSL                               | Moisture Sensitivity Level                         |                                            |                  | 1                     |      |

| Multiple Supplie                  | s: The voltage on any input or I/O pin cannot exce | ed the power pin during power-up. Power su | upply sequencing | g is NOT required.    |      |

# **DC Electrical Specifications**

| Parameter                                               | Description                   | Condition                                                              | Min.                | Max.                  | Unit |

|---------------------------------------------------------|-------------------------------|------------------------------------------------------------------------|---------------------|-----------------------|------|

| V <sub>DD</sub> , V <sub>DDP,</sub><br>V <sub>DDA</sub> | 3.3V Operating Voltage        | 3.3V ± 5%                                                              | 3.135               | 3.465                 | V    |

| V <sub>ILI2C</sub>                                      | Input Low Voltage             | SDATA, SCLK                                                            | -                   | 1                     | V    |

| V <sub>IHI2C</sub>                                      | Input High Voltage            | SDATA, SCLK                                                            | 2.2                 | _                     | _    |

| V <sub>IL</sub>                                         | Input Low Voltage             |                                                                        | V <sub>SS</sub> 0.5 | 0.8                   | V    |

| V <sub>IH</sub>                                         | Input High Voltage            |                                                                        | 2.0                 | V <sub>DD</sub> +0. 5 | V    |

| IIL                                                     | Input Leakage Current         | except Pull-ups or Pull-downs<br>0 < V <sub>IN</sub> < V <sub>DD</sub> | -5                  | 5                     | μA   |

| V <sub>OL</sub>                                         | Output Low Voltage            | I <sub>OL</sub> = 1 mA                                                 | -                   | 0.4                   | V    |

| V <sub>OH</sub>                                         | Output High Voltage           | I <sub>OH</sub> = -1 mA                                                | 2.4                 | -                     | V    |

| I <sub>OZ</sub>                                         | High-Impedance Output Current |                                                                        | -10                 | 10                    | μA   |

| C <sub>IN</sub>                                         | Input Pin Capacitance         |                                                                        | 2                   | 5                     | pF   |

| C <sub>OUT</sub>                                        | Output Pin Capacitance        |                                                                        | 3                   | 6                     | pF   |

| L <sub>IN</sub>                                         | Pin Inductance                |                                                                        | -                   | 7                     | nH   |

| C <sub>XTAL</sub>                                       | Crystal Pin Capacitance       | From XIN and XOUT pins to<br>ground                                    | 32                  | 38                    | pF   |

| V <sub>XIH</sub>                                        | Xin High Voltage              |                                                                        | 0.7V <sub>DD</sub>  | V <sub>DD</sub>       | V    |

| V <sub>XIL</sub>                                        | Xin Low Voltage               |                                                                        | 0                   | 0.3V <sub>DD</sub>    | V    |

| I <sub>DD</sub>                                         | Dynamic Supply Current        | At 133 MHz and all outputs loaded per Table 7                          | -                   | 300                   | mA   |

| I <sub>PD</sub>                                         | Power-down Supply Current     | PD# Asserted                                                           | -                   | 1                     | mA   |

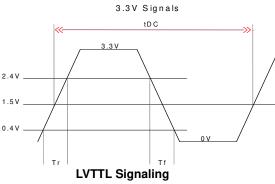

# **AC Electrical Specifications**

| Parameter                       | Description               | Condition                                                            | Min. | Max. | Unit |

|---------------------------------|---------------------------|----------------------------------------------------------------------|------|------|------|

| Crystal                         |                           |                                                                      |      |      |      |

| T <sub>DC</sub>                 | XIN Duty Cycle            | The device will operate reliably with input duty cycles up to 30/70% | 45   | 55   | %    |

| XIN <sub>FREQ</sub>             | XIN Frequency             | When Xin is driven from an external clock source                     | 25   | 33.3 | MHz  |

| T <sub>R</sub> / T <sub>F</sub> | XIN Rise and Fall Times   | Measured between 0.3V <sub>DD</sub> and 0.7V <sub>DD</sub>           | -    | 10.0 | ns   |

| T <sub>CCJ</sub>                | XIN Cycle to Cycle Jitter | As an average over 1µs duration                                      | -    | 500  | ps   |

| L <sub>ACC</sub>                | Long Term Accuracy        | Over 150 ms                                                          |      | 300  | ppm  |

# AC Electrical Specifications (continued)

| Parameter                       | Description                        | Condition                      | Min. | Max. | Unit |

|---------------------------------|------------------------------------|--------------------------------|------|------|------|

| CLK                             |                                    |                                |      |      |      |

| T <sub>DC</sub>                 | CLK Duty Cycle                     | Measurement at 1.5V            | 45   | 55   | %    |

| T <sub>PERIOD33</sub>           | 33-MHz CLK Period                  | Measurement at 1.5V            | 29.5 | 30.5 | ns   |

| T <sub>PERIOD66</sub>           | 66-MHz CLK Period                  | Measurement at 1.5V            | 14.5 | 15.5 | ns   |

| T <sub>PERIOD100</sub>          | 100-MHz CLK Period                 | Measurement at 1.5V            | 9.5  | 10.5 | ns   |

| T <sub>PERIOD133</sub>          | 133-MHz CLK Period                 | Measurement at 1.5V            | 7.0  | 8.0  | ns   |

| T <sub>R</sub> / T <sub>F</sub> | CLK Rise and Fall Times            | Measured between 0.4V and 2.4V | 0.5  | 2.0  | ns   |

| T <sub>SKEW</sub>               | Any CLK to Any CLK Clock Skew      | Measurement at 1.5V            | -    | 250  | ps   |

| T <sub>CCJ</sub>                | CLK Cycle to Cycle Jitter          | Measurement at 1.5V            | -    | 175  | ps   |

| REF                             |                                    |                                |      |      |      |

| T <sub>DC</sub>                 | REF Duty Cycle                     | Measurement at 1.5V            | 45   | 55   | %    |

| T <sub>R</sub> / T <sub>F</sub> | REF Rise and Fall Times            | Measured between 0.4V and 2.4V | 1.0  | 4.0  | ns   |

| T <sub>CCJ</sub>                | REF Cycle to Cycle Jitter          | Measurement at 1.5V            | -    | 750  | ps   |

| ENABLE/DISABLE and SET-UP       |                                    |                                |      |      |      |

| tpZL,tpZH                       | Output Enable Delay (all outputs)  |                                | -    | 10.0 | ns   |

| tpLZ,tpZH                       | Output Disable Delay (all outputs) |                                | -    | 10.0 | ns   |

| T <sub>STABLE</sub>             | Clock Stabilization from Power-up  |                                | -    | 3.0  | ms   |

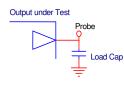

# **Test and Measurement Set-up**

# Lumped Load

Figure 2. Test and Measurement Set-up

### Table 7. Loading

| Output Name | Max Load (in pF) |  |

|-------------|------------------|--|

| CLK         | 30               |  |

| REF         | 20               |  |

# **Ordering Information**

| Part Number | Package Type                 | Product Flow           |

|-------------|------------------------------|------------------------|

| IMIC9531CY  | 28-Pin SSOP                  | Commercial, 0° to 70°C |

| IMIC9531CYT | 28-Pin SSOP – Tape and Reel  | Commercial, 0° to 70°C |

| IMIC9531CT  | 28-Pin TSSOP                 | Commercial, 0° to 70°C |

| IMIC9531CTT | 28-Pin TSSOP – Tape and Reel | Commercial, 0° to 70°C |

| Lead Free   |                              |                        |

| CYI9531OXC  | 28-Pin SSOP                  | Commercial, 0° to 70°C |

| CYI9531OXCT | 28-Pin SSOP – Tape and Reel  | Commercial, 0° to 70°C |

| CYI9531ZXC  | 28-Pin TSSOP                 | Commercial, 0° to 70°C |

| CYI9531ZXCT | 28-Pin TSSOP – Tape and Reel | Commercial, 0° to 70°C |

# Package Drawing and Dimensions

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products must not be used within any Life Support System without the specific to result in significant personal injury or death. Silicon Laboratories products are generally not intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Laboratories products are generally not intended for military applications. Silicon Laboratories shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc., Silicon Laboratories, Silicon Labs, SiLabs and the Silicon Labs logo, CMEMS®, EFM, EFM32, EFR, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZMac®, EZRadio®, EZRadioPRO®, DSPLL®, ISOmodem ®, Precision32®, ProSLIC®, SiPHY®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

# http://www.silabs.com