# IBM ®

## **IBM Processor for Network Resources**

Revision 2.5

**Databook**

© Copyright International Business Machines Corporation 1999, 2000

All Rights Reserved

Printed in the United States of America August 2000

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

IBM IBM Logo

PowerPC

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in implantation or other life support applications where malfunction may result in injury or death to persons. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

IBM Microelectronics Division 1580 Route 52, Bldg. 504 Hopewell Junction, NY 12533-6351 The IBM home page can be found at http://www.ibm.com

The IBM Microelectronics Division home page can be found at http://www.chips.ibm.com

pnr25.01 August 14, 2000

## **Contents**

| Features                                                           | 21 |

|--------------------------------------------------------------------|----|

| Description                                                        | 21 |

| Conventions                                                        | 22 |

| Standards Compliance                                               | 23 |

| Environmental Ratings                                              |    |

| Functional Description                                             |    |

| Subsystem Blocks                                                   |    |

| External Architecture                                              |    |

| Internal Architecture                                              |    |

| Logical Channel Support                                            |    |

| Virtual Memory Support                                             |    |

| Queues                                                             |    |

| Scheduling                                                         |    |

| System Environment                                                 | 34 |

| Data Flows                                                         | 36 |

| Transmit Path                                                      |    |

| Receive Path                                                       |    |

| neceive raui                                                       |    |

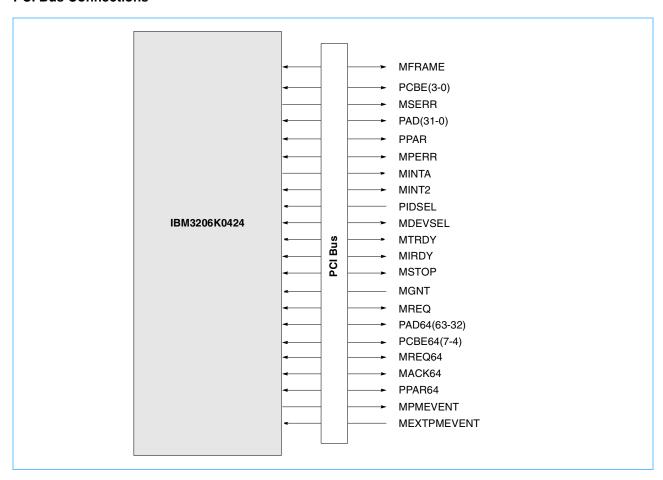

| Input/Output Definitions                                           | Д1 |

| DRAM Memory Bus Interface                                          |    |

| DRAM Memory Bus Interface                                          |    |

| •                                                                  |    |

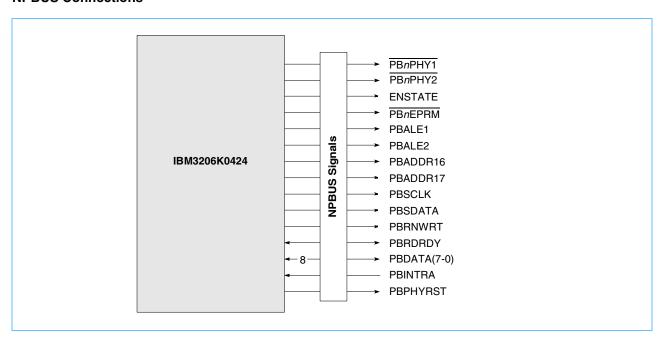

| NPBUS                                                              |    |

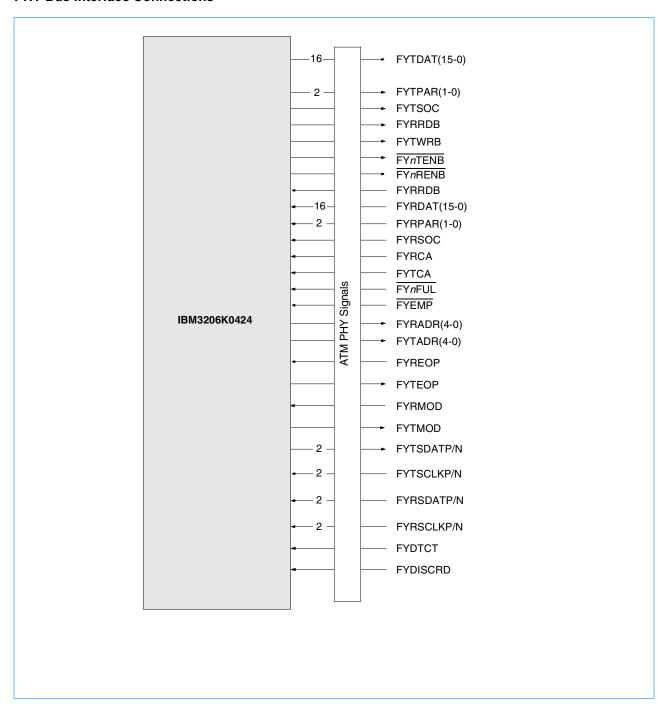

| ATM PHY Bus Interface                                              | 51 |

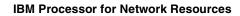

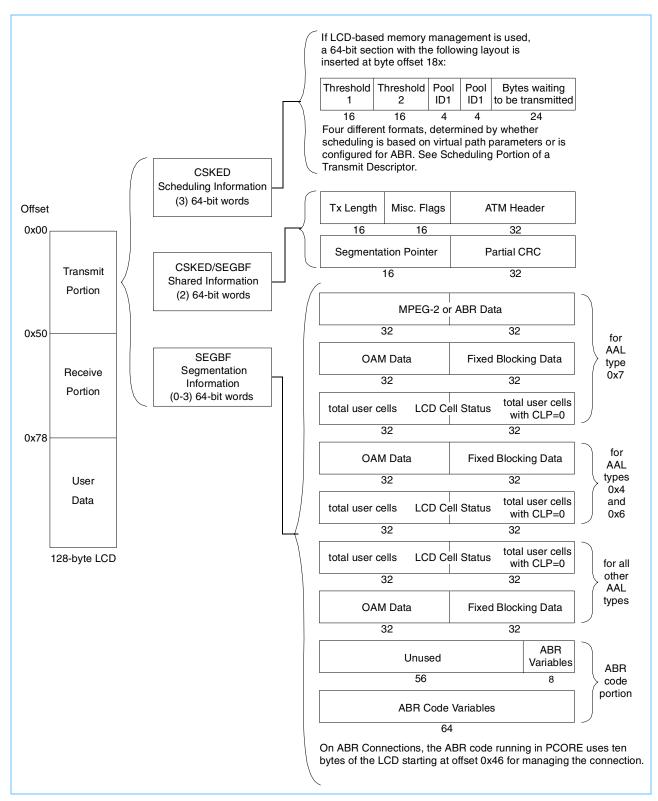

| Data Structures                                                    | 61 |

|                                                                    |    |

| Packet Header  Transmit Logical Channel Descriptor Data Structures |    |

| Field Definitions                                                  |    |

| Receive LCD Data Structure and Modes                               |    |

| Raw LCD                                                            |    |

| Raw Routed LCD                                                     |    |

| Raw Routed Early Drop LCD                                          |    |

| Raw Scatter/Cut-Through LCD                                        |    |

| AAL5 LCD                                                           |    |

| AAL5 Routed LCD                                                    | 85 |

| AAL5 Cut-Through/Scatter Mode LCD                                  | 86 |

| Packet LCD                                                         | 87 |

| Packet Routed LCD                                                  |    |

| Packet Cut-Through Scatter Mode LCD                                | 89 |

|                                                                    | 90 |

| Internal Organization: Entity Descriptions        | 93  |

|---------------------------------------------------|-----|

| Note on Set/Clear Type Registers                  |     |

| Control Processor Bus Interface Entities          | 93  |

| The IOP Bus Specific Interface Controller (PCINT) |     |

| PCI Options Taken                                 |     |

| PCI Target Response                               |     |

| PCI Master Response                               |     |

| PCI Master Retry                                  |     |

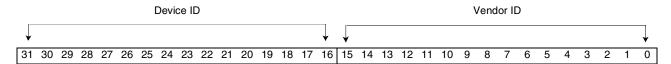

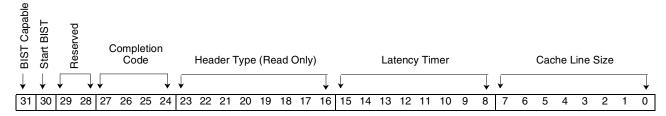

| PCINT Config Word 0                               |     |

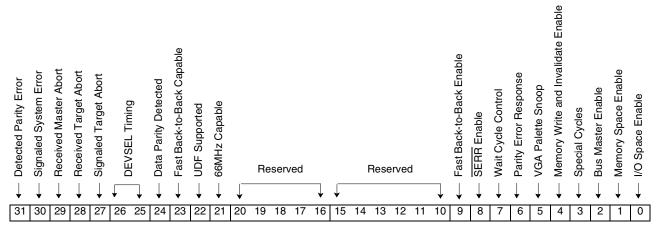

| PCINT Config Word 1                               |     |

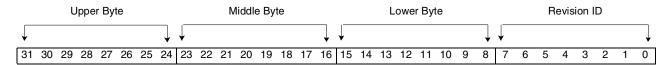

| PCINT Config Word 2                               |     |

| PCINT Config Word 3                               |     |

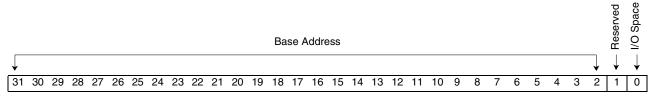

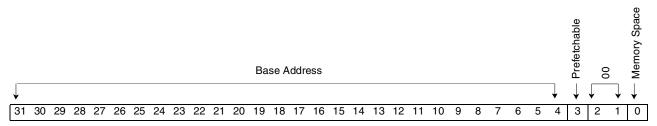

| PCINT Base Address 1 (I/O for Register)           | 99  |

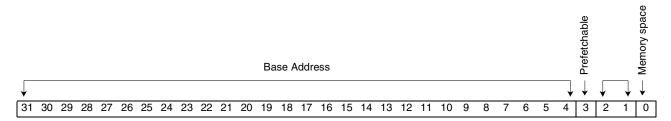

| PCINT Base Address 2 (Mem for Register)           |     |

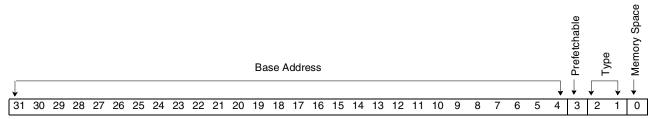

| PCINT Base Addresses 3-6 (Memory)                 | 103 |

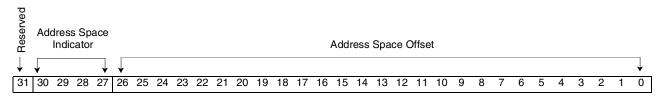

| PCINT CardBus CIS Pointer                         | 105 |

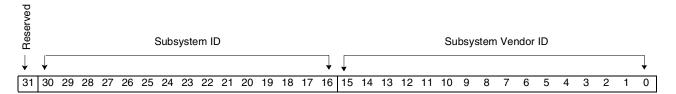

| PCINT Subsystem ID/Vendor ID                      | 106 |

| PCINT ROM Base Address                            | 107 |

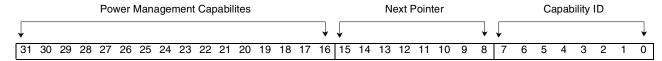

| Capabilities Pointer                              | 108 |

| PCINT Config Word 15                              | 109 |

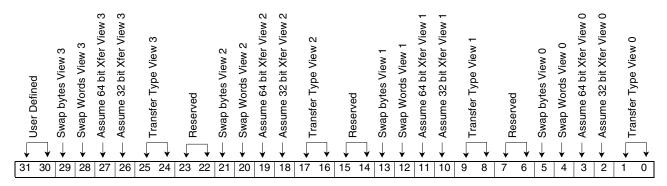

| PCINT Endian Control Register                     | 110 |

| PCINT Base Address Control Register               |     |

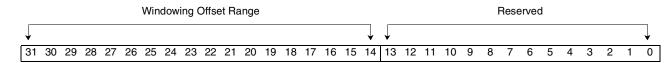

| PCINT Window Offsets for Base Addresses 3-6       |     |

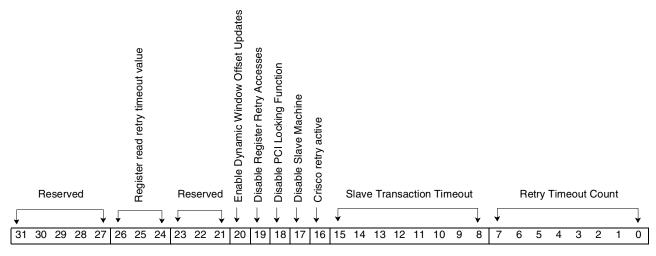

| PCINT Count Timeout Register                      |     |

| PCINT 64-bit Control Register                     |     |

| PCINT 64-bit Enable Register                      |     |

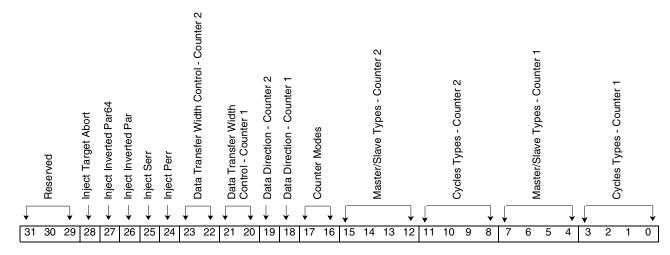

| PCINT Perf Counters Control Register              |     |

| PCINT Perf Counter 1                              |     |

| PCINT Perf Counter 2                              |     |

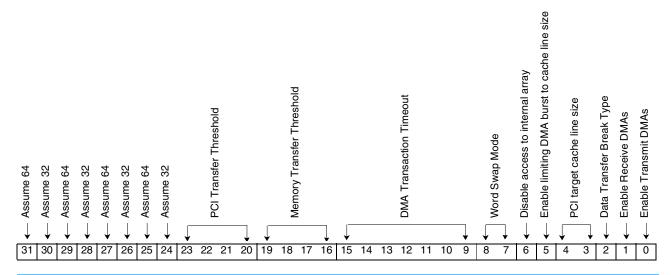

| PCI Master Options Control                        |     |

| Power Management Program Control                  |     |

| Message Signaled Interrupts-Word 1                |     |

| Message Signaled Interrupts-Word 2                |     |

| Message Signaled Interrupts-Word 3                |     |

| Message Signaled Interrupts-Word 4                |     |

| Power Management Interface-Word 1                 |     |

| Power Management Interface-Word 2                 |     |

| Vital Product Data Interface-Word 1               |     |

| Vital Product Data Interface-Word 2               |     |

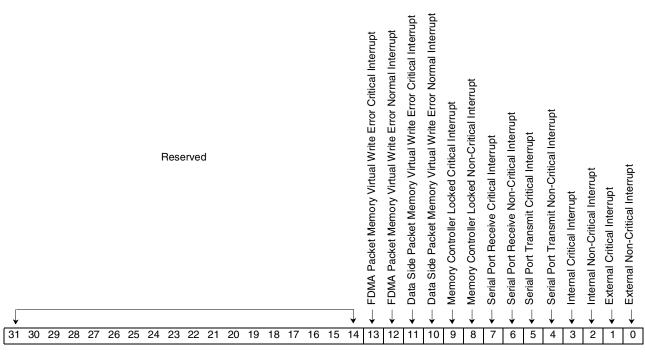

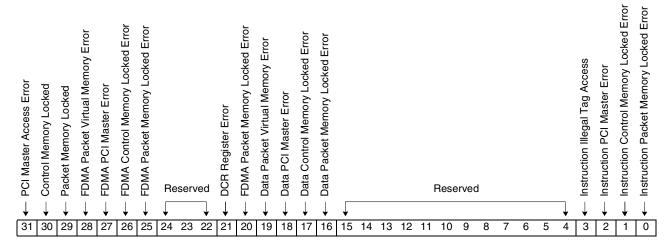

| Interrupt and Status/Control (INTST)              |     |

| INTST Interrupt 1 Prioritized Status              |     |

| INTST Interrupt 2 Prioritized Status              |     |

| INTST Control Register                            |     |

| INTST Interrupt Source                            |     |

| INTST Enable for Interrupt 1 (MINTA)              |     |

| INTST Enable for Interrupt 2 (MINT2)              |     |

| INTST Interrupt Source without Enables            |     |

| INTST CPB Status                                  |     |

| INTST CPB Status Enable                           |     |

| INTST IBM3206K0424 Halt Enable                    | 144 |

| INTST CPB Capture Enable                      | 144 |

|-----------------------------------------------|-----|

| INTST CPB Captured Address                    |     |

| INTST General Purpose Timer Pre-scaler        |     |

| INTST General Purpose Timer Compare           |     |

| INTST General Purpose Timer Counter           |     |

| INTST General Purpose Timer Status            |     |

| INTST General Purpose Timer Mode Control      |     |

| INTST Enable for PCORE Normal Interrupt       |     |

| INTST Enable for PCORE Critical Interrupt     |     |

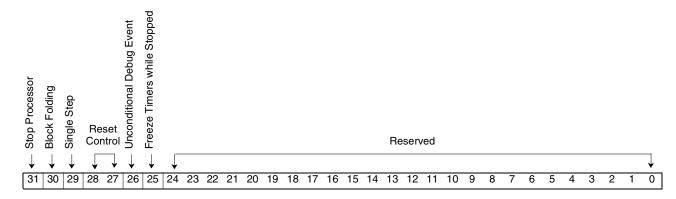

| INTST Debug States Control                    |     |

| INTST Delayed Interrupts DMA System Address 1 |     |

| INTST Delayed Interrupts DMA System Address 2 |     |

| Current PCI Master Address Counter for Debug  |     |

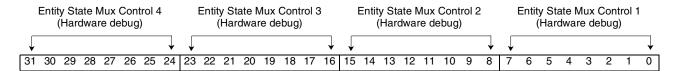

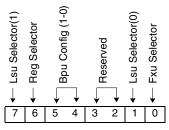

| External Entity States Read                   |     |

| DMA QUEUES (DMAQS)                            |     |

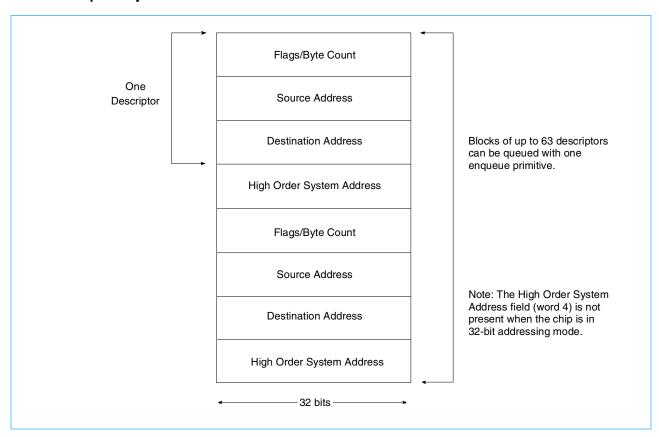

| DMA Descriptors                               |     |

| DMA Types and Options                         |     |

| Descriptor Based DMAs                         |     |

| Register Based DMAs                           |     |

| Polling, Interrupts, or Events                |     |

| Error Detection and Recovery                  |     |

| DMA/Queue Scheduling Options                  |     |

| Address Size                                  |     |

| Data Width                                    |     |

| Initialization of DMAQS                       |     |

| DMAQS Lower Bound Registers                   |     |

| DMAQS Upper Bound Registers                   |     |

| DMAQS Head Pointer Registers                  |     |

| DMAQS Tail Pointer Registers                  |     |

| DMAQS Length Registers                        |     |

| DMAQS Threshold Registers                     |     |

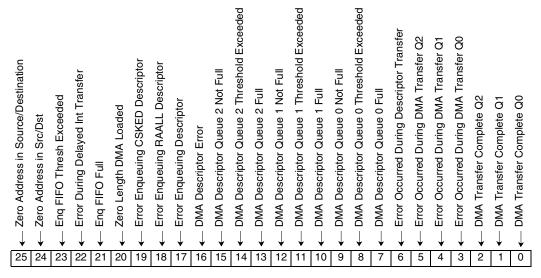

| DMAQS Interrupt Status                        |     |

| DMAQS Interrupt Enable                        |     |

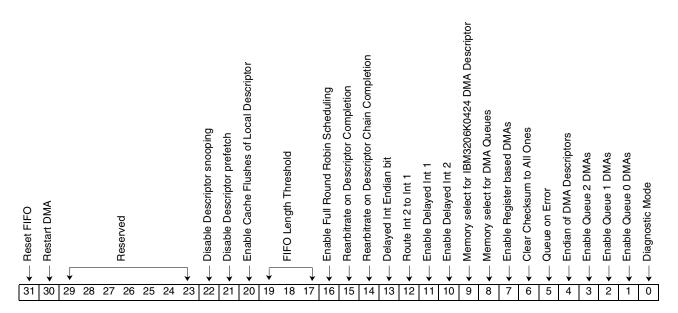

| DMAQS Control Register                        |     |

| DMAQS Enqueue DMA Descriptor Primitive        |     |

| DMAQS Source Address Register                 |     |

| DMAQS Destination Address Register            |     |

| DMAQS Buffer Address Register                 |     |

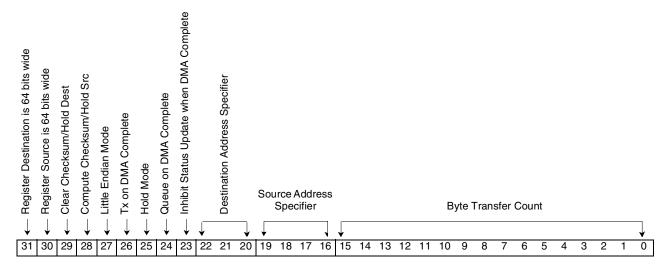

| DMAQS Transfer Count and Flag Register        |     |

| DMAQS System Descriptor Address               |     |

| DMAQS Checksum Register                       |     |

| DMAQS Local Descriptor Range Registers        |     |

| DMAQS Event Queue Number Register             |     |

| DMAQS DMA Request Size Register               |     |

| DMAQS Enq FIFO Register                       |     |

| General Purpose DMA (GPDMA)                   |     |

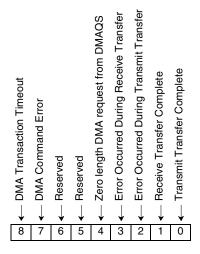

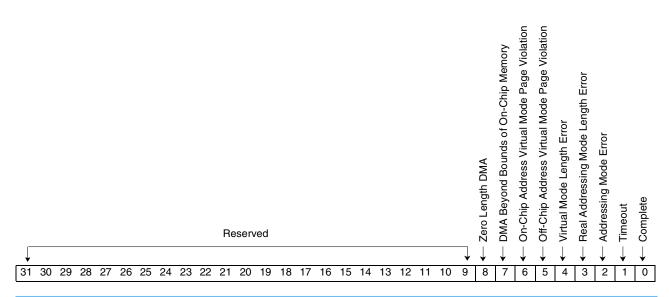

| GPDMA Interrupt Status                        |     |

| GPDMA Interrupt Clated                        |     |

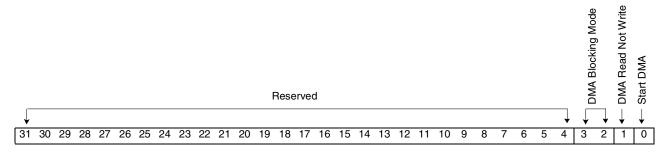

| GPDMA Control Register                        |     |

| GPDMA Source Address Register                 |     |

| GPDMA Destination Address Register            |     |

| ·                                             |     |

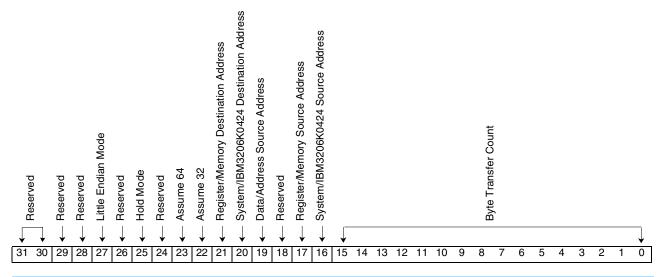

|     | GPDMA Transfer Count and Flag Register                | 179 |

|-----|-------------------------------------------------------|-----|

|     | GPDMA DMA Max Burst Time                              |     |

|     | GPDMA Maximum Memory Transfer Count                   | 181 |

|     | GPDMA Checksum Register                               |     |

|     | GPDMA Read DMA Byte Count                             |     |

|     | GPDMA Write DMA Byte Count                            |     |

|     | GPDMA Array Read Address                              |     |

|     | GPDMA Array Write Address                             |     |

|     | GPDMA Array                                           | 183 |

|     |                                                       |     |

| Men | nory Controlling Entities                             | 184 |

| Т   | he DRAM Controllers (COMET/PAKIT)                     | 184 |

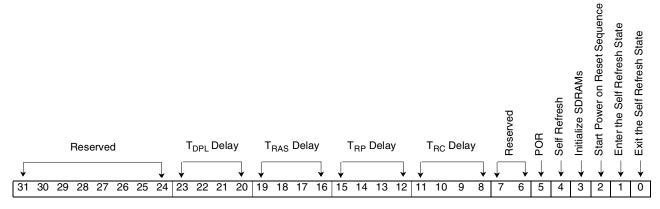

|     | Memory Reset Sequence                                 | 185 |

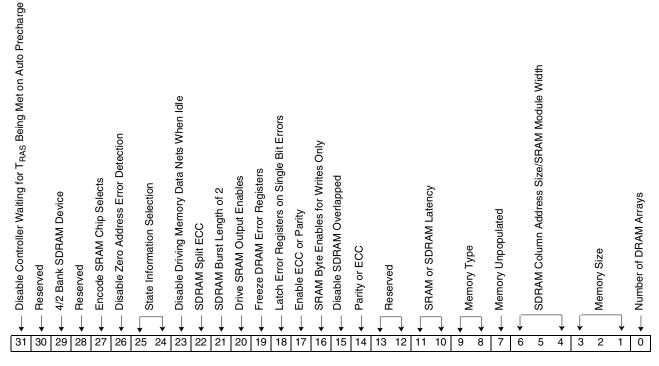

|     | COMET/PAKIT Control Register                          |     |

|     | COMET/PAKIT Status Register                           | 189 |

|     | COMET/PAKIT Interrupt Enable Register                 |     |

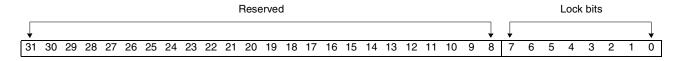

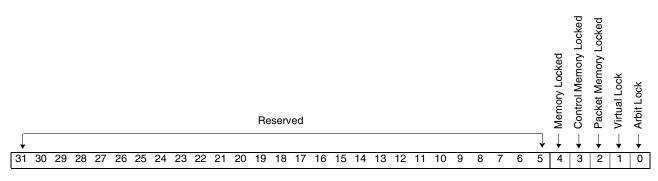

|     | COMET/PAKIT Lock Enable Register                      | 190 |

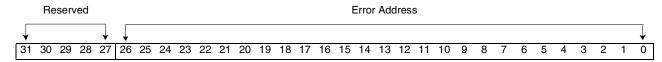

|     | COMET/PAKIT Memory Error Address Register             |     |

|     | COMET/PAKIT SDRAM Command and Status Register         | 192 |

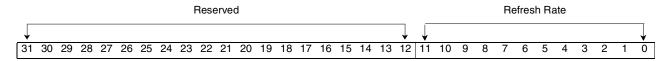

|     | COMET/PAKIT DRAM Refresh Rate Register                |     |

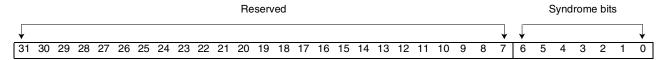

|     | COMET/PAKIT Syndrome Register                         | 195 |

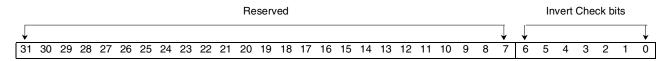

|     | COMET/PAKIT Checkbit Inversion Register               | 197 |

|     | COMET/PAKIT Memory Controller Write Enable Register   | 197 |

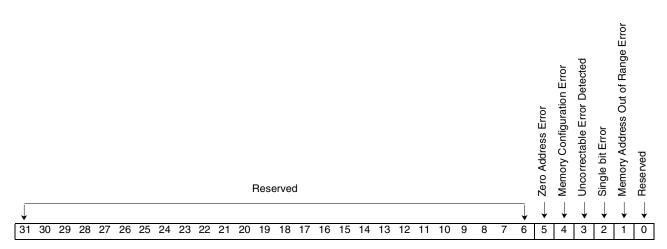

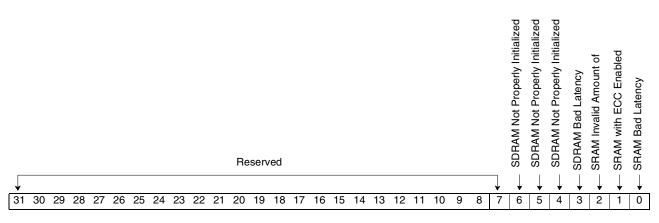

|     | COMET/PAKIT Memory Configuration Error Sense Register | 198 |

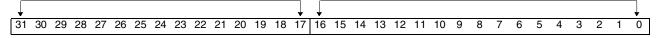

| Δ   | ATM Virtual Memory Logic (VIMEM)                      | 200 |

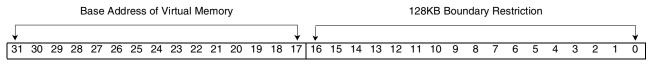

|     | VIMEM Virtual Memory Base Address                     | 200 |

|     | On-Chip Memory Base Address                           | 201 |

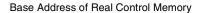

|     | VIMEM Control Memory Base Address                     | 201 |

|     | VIMEM Packet Memory Base Address                      | 202 |

|     | VIMEM Virtual Memory Total Bytes                      | 203 |

|     | VIMEM Virtual/Real Memory Buffer Size                 | 204 |

|     | VIMEM Packet Memory Offset                            | 205 |

|     | VIMEM Maximum Buffer Size                             | 205 |

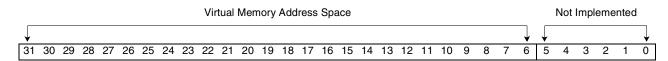

|     | VIMEM Access Control Register                         | 206 |

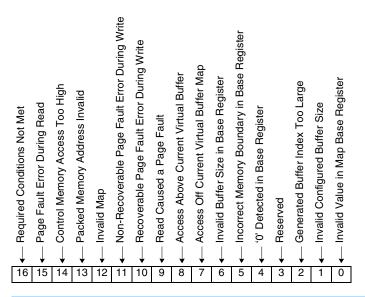

|     | VIMEM Access Status Register                          | 207 |

|     | VIMEM Access Status Interrupt Enable Register         | 209 |

|     | VIMEM Memory Lock Enable Register                     | 209 |

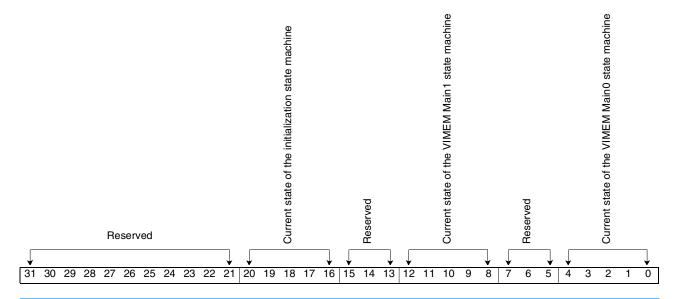

|     | VIMEM State Machine Current State                     | 210 |

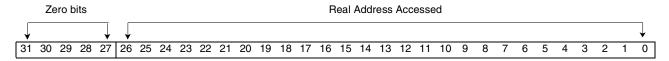

|     | VIMEM Last Processor Read Real Address                | 211 |

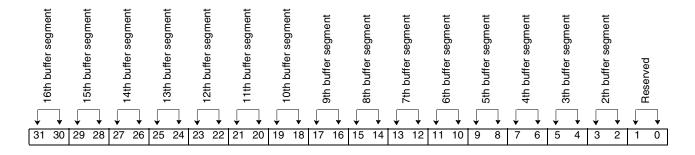

|     | VIMEM Virtual Buffer Segment Size Register            | 212 |

|     | VIMEM Buffer Map Base Address                         | 214 |

|     | VIMEM Real Buffer Base Addresses                      | 215 |

| A   | ATM Packet/Control Memory Arbitration Logic (ARBIT)   | 217 |

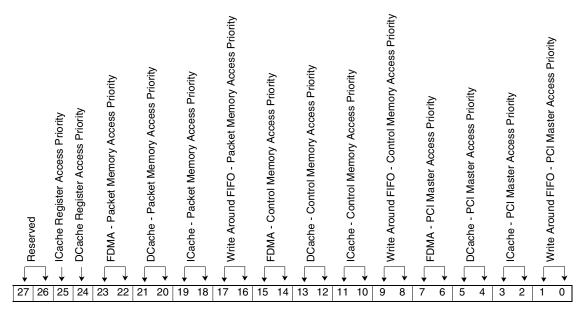

|     | ARBIT Control Priority Resolution Register High       | 217 |

|     | ARBIT Control Priority Resolution Register Low        | 218 |

|     | ARBIT Control Error Mask Register                     |     |

|     | ARBIT Control Error Source Register                   |     |

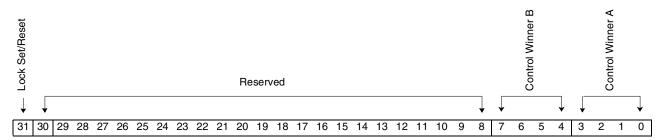

|     | ARBIT Control Winner Register                         |     |

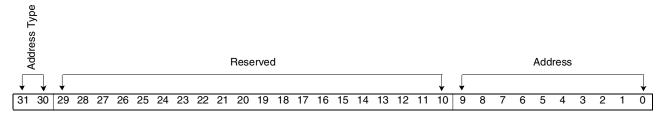

|     | ARBIT Control Address Register A                      |     |

|     | ARBIT Control Address Register B                      | 222 |

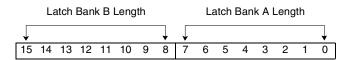

|     | ARBIT Control Length Register                         | 223 |

|     |                                                       |     |

| ARBIT Control Lock Entity Enable Register                      | 224 |

|----------------------------------------------------------------|-----|

| ARBIT Control Config Register                                  |     |

| ARBIT Packet Priority Resolution Register High                 | 225 |

| ARBIT Packet Priority Resolution Register Low                  | 227 |

| ARBIT Packet Entity Error Mask Register                        |     |

| ARBIT Packet Error Source Register                             |     |

| ARBIT Packet Winner Register                                   |     |

| ARBIT Packet Address Register A                                |     |

| ARBIT Packet Address Register B                                |     |

| ARBIT Packet Length Register                                   |     |

| ARBIT Packet Lock Entity Enable Register                       |     |

| ARBIT Packet Config Register                                   | 234 |

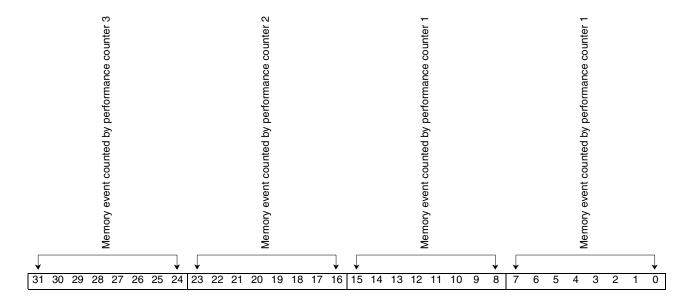

| ARBIT Performance Counter Control                              |     |

| Arbit Memory Performance Counter                               | 237 |

| The Bus DRAM Cache Controller (BCACH)                          |     |

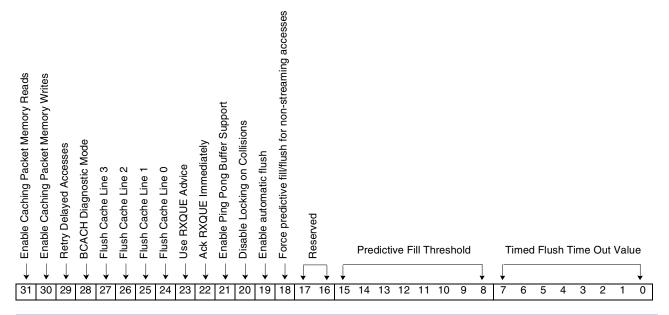

| BCACH Control Register                                         |     |

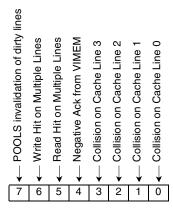

| BCACH Status Register                                          |     |

| BCACH Interrupt Enable Register                                |     |

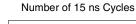

| BCACH High Priority Timer Value                                |     |

| BCACH Line Tag Registers                                       |     |

| BCACH Line Valid Bytes Register                                |     |

| BCACH Line Status Register                                     |     |

| BCACH Cache Line Array                                         |     |

| Buffer Pool Management (POOLS)                                 |     |

| Basic Operation in Real Memory Mode                            |     |

| Basic Operation in Virtual Memory Mode                         |     |

| Resource Controls                                              |     |

| Virtual Memory Overview                                        |     |

| POOLS Get Pointer Primitive                                    |     |

| POOLS Free Pointer Primitive                                   |     |

| POOLS Common Pools Count Registers                             |     |

| POOLS Client Thresholds Array                                  |     |

| POOLS User Threshold and Client Active Packet Count Array      |     |

| POOLS Pointer Queues DRAM Head Pointer Offset Address Register |     |

| POOLS Pointer Queues DRAM Tail Pointer Offset Address Register |     |

| POOLS Pointer Queues DRAM Lower Bound Address Register         |     |

| POOLS Pointer Queues DRAM Upper Bound Register                 | 259 |

| POOLS Pointer Queues Length Registers                          | 261 |

| POOLS Interrupt Enable Register                                |     |

| POOLS Event Enables                                            | 262 |

| POOLS Event Hysteresis Register                                | 262 |

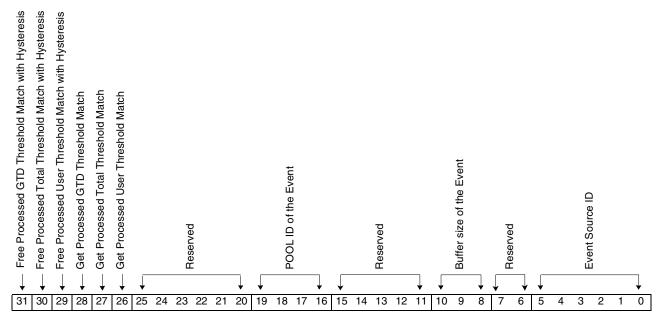

| POOLS Event Data Register                                      | 263 |

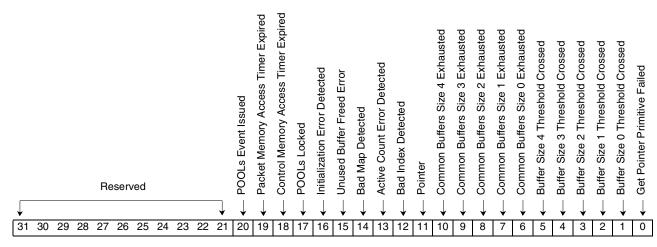

| POOLS Status Register                                          | 265 |

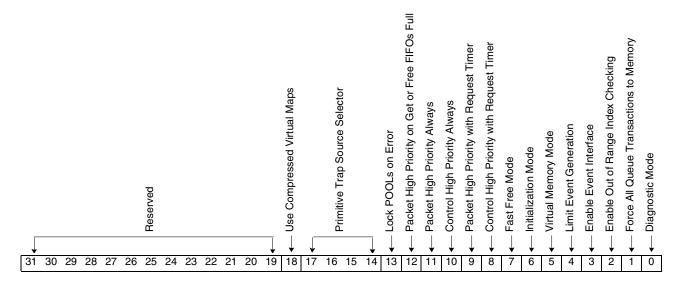

| POOLS Control Register                                         | 267 |

| POOLS Buffer Threshold Registers 0-4                           | 269 |

| POOLS Index Threshold Registers 0-4                            |     |

| POOLS Last Primitive Trap Register                             |     |

| POOLS Last Buffer Map Read on Free Register                    |     |

| POOLS Error Lock Enable Register                               |     |

| POOLS Packet and Control Memory Access Threshold               |     |

| POOLS Buffer Map Group                                         |     |

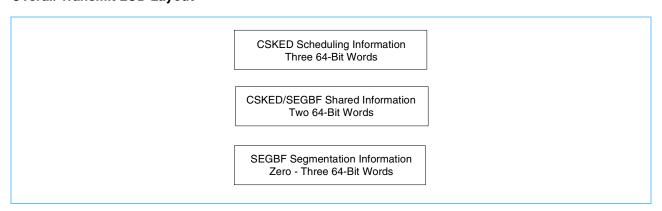

| Transmit Data Path Entities               | 273 |

|-------------------------------------------|-----|

| Transmit Buffer (CSKED)                   | 273 |

| Scheduling Overview                       |     |

| Operational Description                   |     |

| LCD Initialization                        |     |

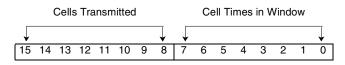

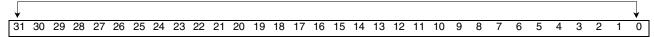

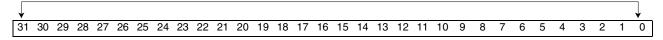

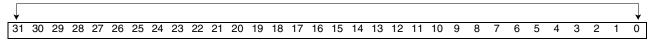

| A Scheduling Example                      | 274 |

| CSKED Initialization                      |     |

| Packet Initialization                     | 276 |

| Scheduling Options                        |     |

| ABR Scheduling                            |     |

| Frame Scheduling                          |     |

| Path Scheduling                           | 277 |

| Primitives                                |     |

| Enqueue                                   | 277 |

| Close Connection                          | 277 |

| Start/Stop Timer                          | 278 |

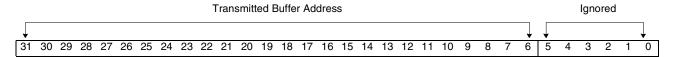

| Transmit Enqueue Primitive                | 278 |

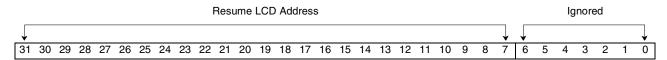

| Resume Transmission Primitive             | 278 |

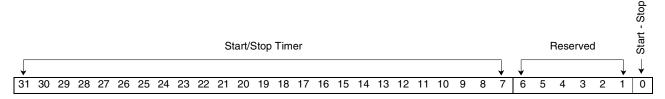

| Start/Stop Timer Primitive                | 279 |

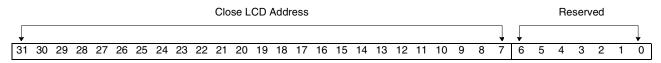

| Close Connection Primitive                | 279 |

| Timeslot Prescaler Register               | 280 |

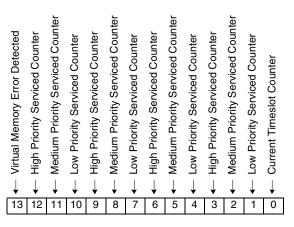

| Current Timeslot Counter                  | 280 |

| CSKED Control Register                    | 281 |

| Transmit Segmentation Throttle Register   |     |

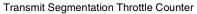

| Transmit Segmentation Throttle Counter    |     |

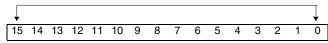

| MPEG Conversion Register                  |     |

| ABR Timer Prescaler Register              |     |

| RM Cell Timer                             |     |

| CSKED LCD Update Data Registers           |     |

| CSKED LCD Update Mask Registers           |     |

| CSKED LCD Update Operation Registers      |     |

| Drop Access Control Register              |     |

| Performance Registers                     |     |

| High Priority Bandwidth Limit Register    |     |

| Medium Priority Bandwidth Limit Register  |     |

| Low Priority Bandwidth Limit Register     |     |

| High Priority Cells Transmitted Counter   |     |

| Medium Priority Cells Transmitted Counter |     |

| Low Priority Cells Transmitted Counter    |     |

| Bytes Queued Counters                     |     |

| Debugging Register Access                 |     |

| Fast Serviced Counters                    |     |

| Slow Serviced Counters                    |     |

| Timer Serviced Counters                   |     |

| CSKED Status Register                     |     |

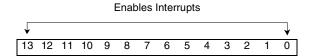

| CSKED Interrupt Enable Register           |     |

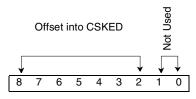

| CSKED Timing Data Array Pointer           |     |

| CSKED Timing Data Array Data              |     |

| CSKED Time Wheel Array Pote               |     |

| CSKED I CD Cacho Array Pointer            |     |

| CSKED LCD Cache Array Pointer             | ∠99 |

|    | CSKED LCD Cache Array Data                        | 300 |

|----|---------------------------------------------------|-----|

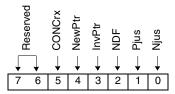

|    | CSKED Congestion Control Register                 | 300 |

|    | State Machine Variables                           | 301 |

|    | ATM Transmit Buffer Segmentation (SEGBF)          | 302 |

|    | SEGBF Software LCD Enqueue                        |     |

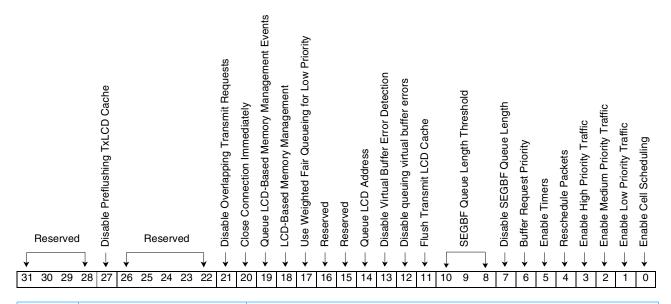

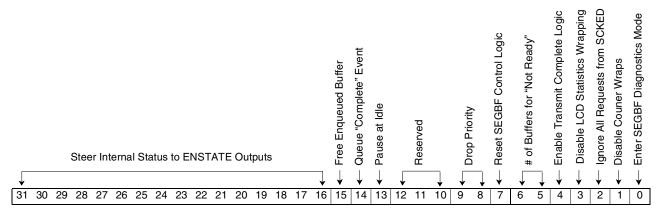

|    | SEGBF Control Register                            | 306 |

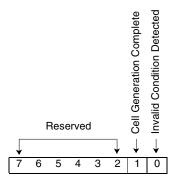

|    | SEGBF Status Register                             | 308 |

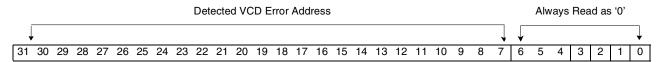

|    | SEGBF Invalid LCD Register                        | 309 |

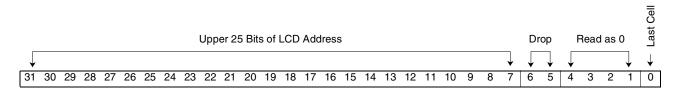

|    | SEGBF Software LCD Complete                       | 310 |

|    | SEGBF Interrupt Enable Register                   | 311 |

|    | SEGBF Programmable Counters                       | 311 |

|    | SEGBF Transmit LCD Size                           | 312 |

|    | SEGBF Cell Queue Status                           |     |

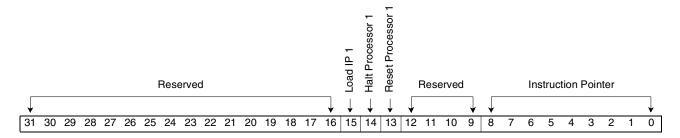

|    | SEGBF Processor 1 Control/Status                  | 314 |

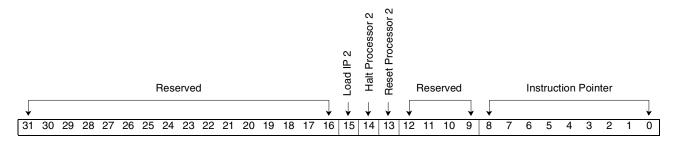

|    | SEGBF Processor 2 Control/Status                  | 315 |

|    | SEGBF Programmable Counter Source Specification   | 316 |

|    | SEGBF Cell Staging Array Pointer                  |     |

|    | SEGBF Cell Staging Array Data                     |     |

|    | SEGBF Instruction SRAM Pointer                    |     |

|    | SEGBF Instruction SRAM Data                       |     |

|    | MPEG-2 PCR Increment Register                     | 319 |

|    |                                                   |     |

| Re | ceive Data Path Entities                          |     |

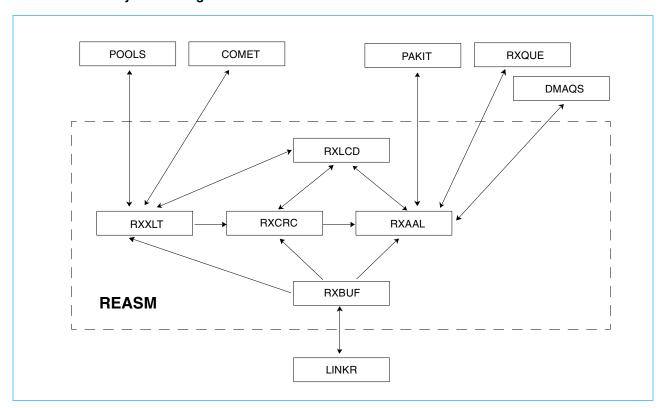

|    | Cell/Packet Re-assembly (REASM)                   | 320 |

|    | Miscellaneous Reassembly Functions                | 322 |

|    | ATM OAM Cell Processing                           |     |

|    | TCP/IP Receive Checksum Verification              |     |

|    | Scatter/Cut Through Receive Processing            |     |

|    | REASM Logical Channel Descriptor Base Register    |     |

|    | REASM Mode Register                               |     |

|    | REASM Reassembly Modes Register                   |     |

|    | REASM Status Register                             |     |

|    | REASM Interrupt Enable Register                   |     |

|    | REASM DEBUG State Selector Register               |     |

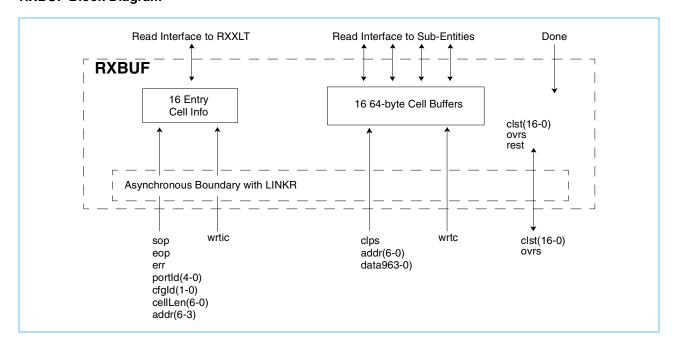

|    | RXBUF Functional Description                      |     |

|    | RXBUF Cell Data Buffer Address                    | 333 |

|    | roles con bala barror rioda, virto r or imminimum |     |

|    | RXBUF Cell Info Buffer Address                    |     |

|    | RXBUF Receive Buffer Threshold                    |     |

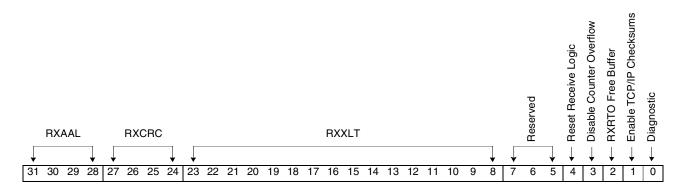

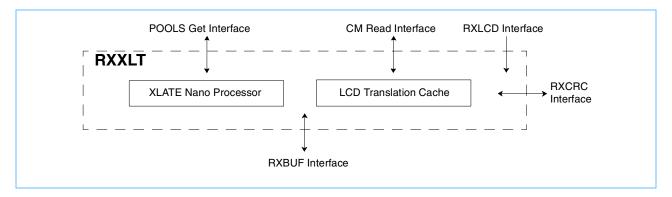

|    | RXXLT Functional Description                      |     |

|    | RXXLT Register Array Address Port                 |     |

|    | RXXLT Register Array Read/Write Port              |     |

|    | RXXLT Processor State Selector                    |     |

|    | RXXLT Processor State Read/Write Port             |     |

|    | RXXLT Instruction Array Address Port              |     |

|    | RXXLT Instruction Array Read/Write Port           |     |

|    | RXXLT Last LCD Index Register                     |     |

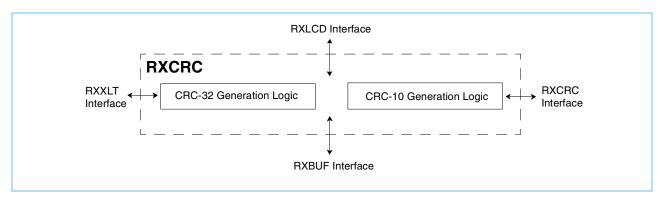

|    | RXCRC Functional Description                      |     |

|    | RXCRC Instruction Array Address Port              |     |

|    | RXCRC Instruction Array Read/Write Port           |     |

|    | •                                                 |     |

| RXCRC Processor State Selector                        | 345 |

|-------------------------------------------------------|-----|

| RXCRC Processor State Read/Write Port                 | 346 |

| RXCRC Last LCD Index Register                         | 346 |

| RXCRC Checksum Protocol Registers                     | 346 |

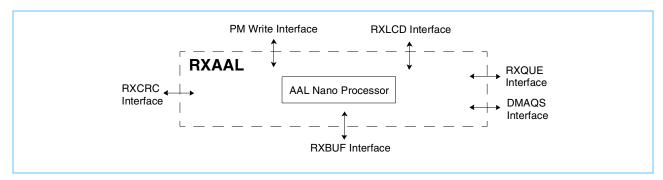

| RXAAL Functional Description                          | 347 |

| RXAAL Instruction Array Address Port                  | 348 |

| RXAAL Instruction Array Read/Write Port               | 348 |

| RXAAL Processor State Selector                        | 349 |

| RXAAL Processor State Read/Write Port                 | 349 |

| RXAAL Last LCD Index Register                         | 350 |

| RXAAL Transmit Queue Length Compression Configuration |     |

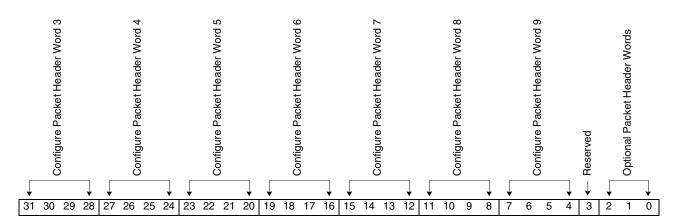

| RXAAL Packet Header Configuration                     | 352 |

| RXAAL Error Count Register                            |     |

| RXAAL Dropped Count Register                          | 354 |

| RXAAL Maximum SDU Length Register                     |     |

| RXAAL OAM LCD Information Register                    |     |

| RXALL - Scatter/Cut Through Info Registers            |     |

| RXALL - Scatter/Cut Through Flag Registers            |     |

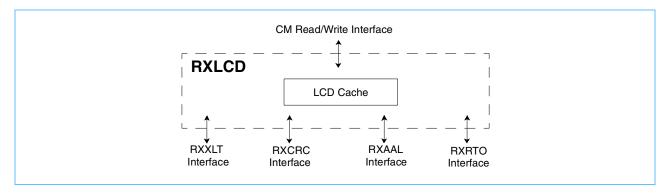

| RXLCD Functional Description                          |     |

| RXLCD Cache Data Array Address Port                   | 359 |

| RXLCD Cache Data Array Read/Write Port                | 360 |

| RXLCD Cache Line Info Registers                       | 360 |

| RXLCD Mode Register                                   |     |

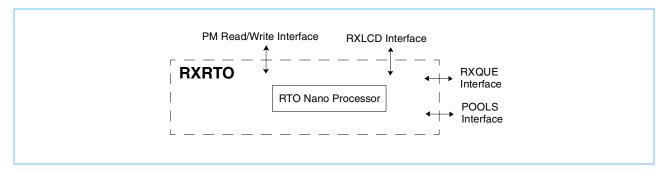

| RXRTO Functional Description                          | 362 |

| Reassembly Timeout (RTO) Processing                   | 362 |

| RXRTO LCD Update Data Registers                       |     |

| RXRTO LCD Update Mask Registers                       | 363 |

| RXRTO LCD Update Op Registers                         | 364 |

| RXRTO RTO LCD Table Bound Registers                   | 364 |

| RXRTO Reassembly Timeout Value Register               | 365 |

| RXRTO Reassembly Timeout Pre-Scaler Register          | 365 |

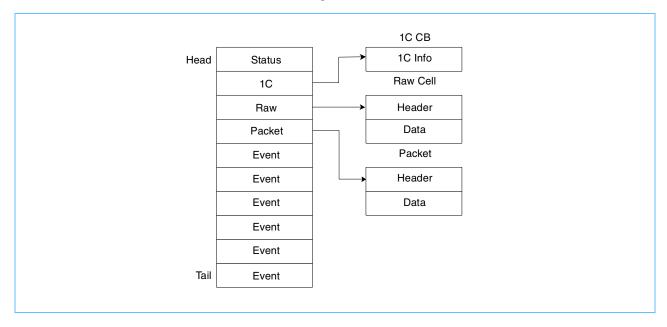

| Receive Queues (RXQUE)                                | 366 |

| Functional Description                                |     |

| Receive Queue Interface                               |     |

| AAL5 Packet Events                                    | 370 |

| Cell Events                                           | 371 |

| LC Events                                             | 372 |

| ABR Events                                            | 372 |

| RXQUE Structure                                       |     |

| RXQUE Initialization                                  | 377 |

| RXQUE Event Routing                                   | 378 |

| RXQUE Normal Operation                                | 379 |

| RXQUE Queue Full Operation                            | 379 |

| RXQUE Event Timestamping                              |     |

| RXQUE System Receive Queues                           |     |

| RXQUE Lower Bound Registers                           |     |

| RXQUE Properties Registers                            |     |

| RXQUE Head Pointer Registers                          |     |

| RXQUE Tail Pointer Registers                          |     |

| RXQUE Length Registers                                |     |

| RXQUE Threshold Registers                             |     |

|    | RXQUE Dequeue Registers                                                                | 390 |

|----|----------------------------------------------------------------------------------------|-----|

|    | RXQUE Enqueue Registers                                                                | 391 |

|    | RXQUE Next Lower Bound Registers                                                       | 392 |

|    | RXQUE Last Event Dropped Register                                                      | 393 |

|    | RXQUE Timestamp Register                                                               |     |

|    | RXQUE Timestamp Pre-Scaler Register                                                    | 393 |

|    | RXQUE Timestamp Shift Register                                                         | 394 |

|    | RXQUE Event Routing Registers                                                          |     |

|    | RXQUE Event Latency Timer Register                                                     |     |

|    | RXQUE Queues Status Register                                                           |     |

|    | RXQUE Interrupt Enable Registers                                                       |     |

|    | RXQUE Status and Enabled Status Registers                                              |     |

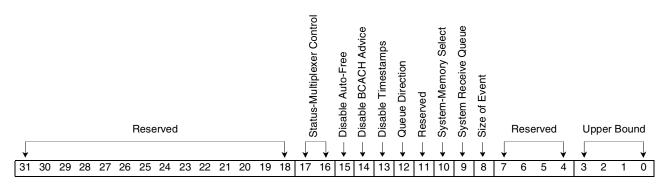

|    | RXQUE Control Register                                                                 |     |

|    | Debugging Register Access                                                              |     |

|    | RXQUE RXQ State Machine Variable Register                                              |     |

|    | RXQUE RXQ ENQ State Machine Variable Register                                          |     |

|    | RXQUE Enq FIFO Head Ptr Register                                                       |     |

|    | RXQUE Enq FIFO Tail Ptr Register                                                       |     |

|    | RXQUE Enq FIFO Array                                                                   | 402 |

| ь. | V I aval latarfaces                                                                    | 400 |

|    | Y Level Interfaces                                                                     |     |

|    | The PHY Interface (LINKC)                                                              |     |

|    | Functional Description                                                                 |     |

|    | Multi-Drop                                                                             |     |

|    | POS-PHY                                                                                |     |

|    | Moving Cells To and From the IBM3206K0424LINKC Global Control Register                 |     |

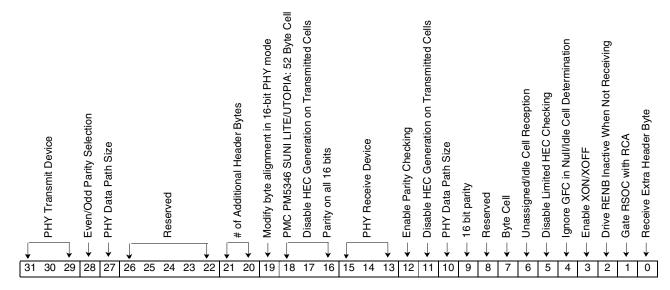

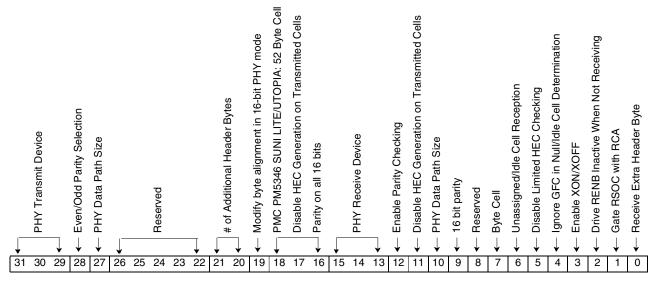

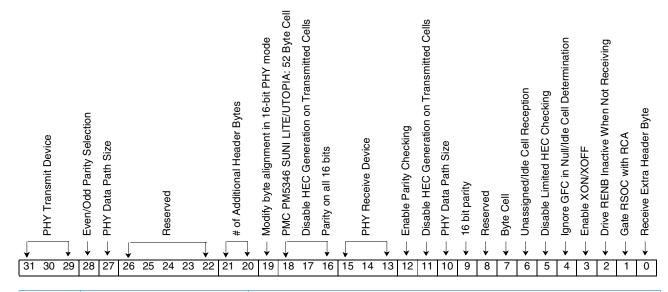

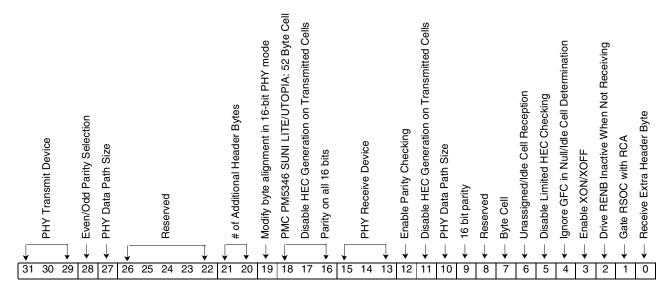

|    | LINKC Global Control RegisterLINKC Configuration 0 Transmit & Receive Control Register |     |

|    | LINKC Configuration o Transmit & Receive Control Register                              |     |

|    | LINKC Configuration 2 Transmit & Receive Control Register                              |     |

|    | LINKC Configuration 3 Transmit & Receive Control Register                              |     |

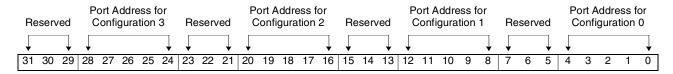

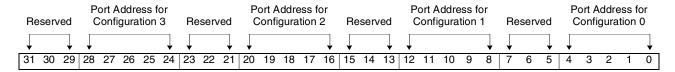

|    | LINKC Map Transmit Configurations to Port Addresses                                    |     |

|    | LINKC Map Receive Configurations to Port Addresses                                     |     |

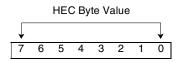

|    | LINKC Transmitted HEC Control Byte                                                     |     |

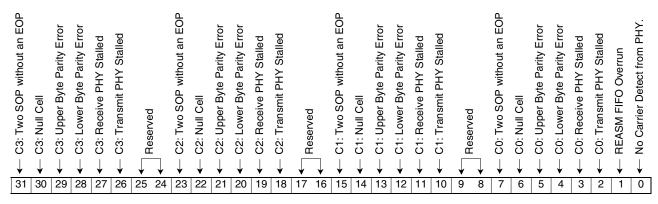

|    | LINKC Interrupt/Status Register                                                        |     |

|    | LINKC Interrupt Enable Register                                                        |     |

|    | LINKC Prioritized Interrupts                                                           |     |

|    | LINKC Transmit State Machine Register                                                  | 425 |

|    | LINKC Receive State Machine Register                                                   | 425 |

|    | LINKC LAN Address Register                                                             | 426 |

|    | LINKC Canonical LAN Address Register                                                   | 426 |

|    | LINKC Passed TX Data Register                                                          | 427 |

|    | Nodal Processor Bus Interface (NPBUS)/CRISCO Processor for Register Initialization     |     |

|    | from EPROM Data                                                                        |     |

|    | NPBUS Control Register                                                                 |     |

|    | NPBUS Status Register                                                                  |     |

|    | NPBUS Interrupt Enable Register                                                        |     |

|    | NPBUS EPROM Address/Command Register                                                   |     |

|    | NPBUS EPROM Data Register                                                              |     |

|    | PHY 1 Registers                                                                        |     |

|    | PHY 2 Registers                                                                        | 434 |

| Hardware Protocol Assist Entities                       | 435 |

|---------------------------------------------------------|-----|

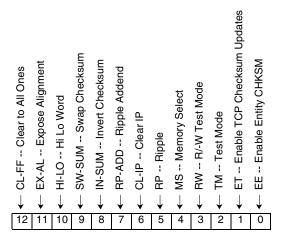

| On-chip Checksum and DRAM Test Support (CHKSM)          | 435 |

| Functional Description                                  |     |

| CHKSM Base Address Register                             | 435 |

| CHKSM Read/Write Count Register                         | 436 |

| CHKSM TCP/IP Checksum Data Register                     | 437 |

| CHKSM Ripple Base Register                              | 437 |

| CHKSM Ripple Limit Register                             | 438 |

| CHKSM Interrupt Enable Register                         | 438 |

| CHKSM Status Register                                   | 439 |

| CHKSM Control Register                                  | 440 |

| Debugging Register Access                               | 441 |

| CHKSM Internal State                                    | 441 |

| Software Use of CHKSM                                   | 442 |

| Running a TCP/IP Checksum in Packet/Control Memory      | 443 |

| Processor Core (PCORE)                                  |     |

| DCR Interface                                           |     |

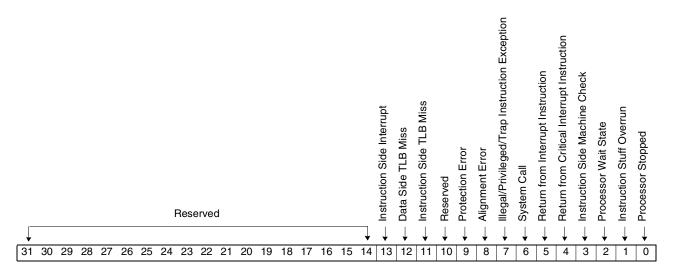

| Interrupt Controller                                    | 444 |

| Bridge-Address Translation                              |     |

| OCM SRAM                                                | 444 |

| Control Memory                                          | 444 |

| Packet Memory                                           | 444 |

| PCI Master Interface-External                           | 444 |

| Processor Register Space                                | 444 |

| Address Translation Examples                            | 445 |

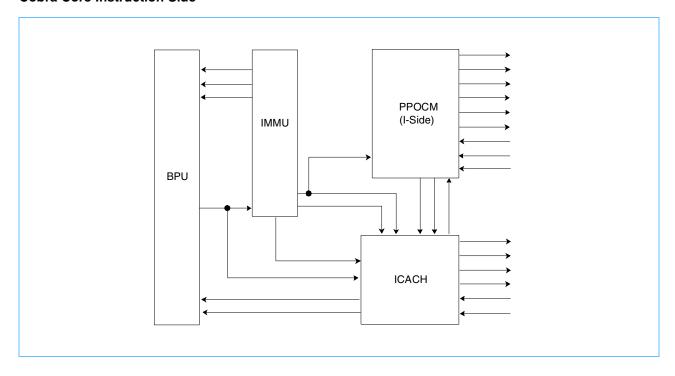

| Cobra Structure                                         | 445 |

| Cobra Core "Glossy" Description                         | 446 |

| Features                                                | 446 |

| Interfaces                                              | 448 |

| Performance                                             | 449 |

| Instruction Set                                         |     |

| Cobra Instruction Overview                              | 449 |

| Cobra Facilities Overview                               |     |

| Cobra Specific Register Definitions                     |     |

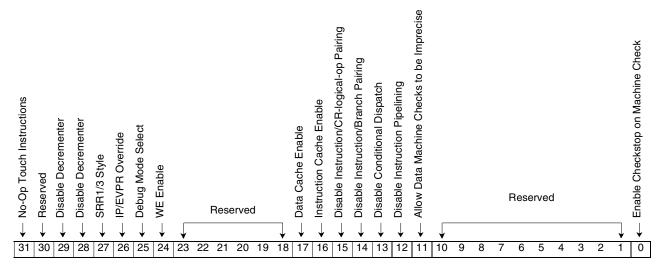

| Hardware Implementation Detail 0 Register (HID0)        | 456 |

| Machine State Register (MSR)                            |     |

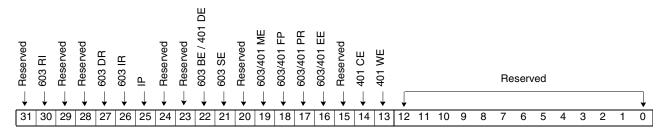

| Exception Status Register (ESR)                         |     |

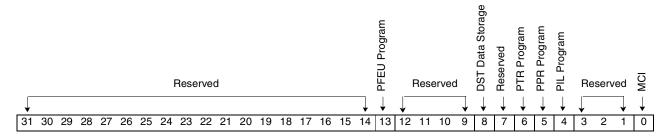

| Machine Check Enable Register (MCHK)                    |     |

| PCORE Register Definitions                              |     |

| PCORE Control Register                                  |     |

| PCORE Reset Control Register                            |     |

| PCORE Status Register                                   |     |

| PCORE User Status Register                              |     |

| PCORE Cobra Core External Status Register               |     |

| PCORE Cobra Core External Machine Check Status Register |     |

| PCORE JTAG Debug Control Register                       |     |

| PCORE JTAG Debug Status Register                        |     |

| PCORE JTAG Instruction Stuff Buffer                     |     |

| PCORE JTAG Debug Data Register                          |     |

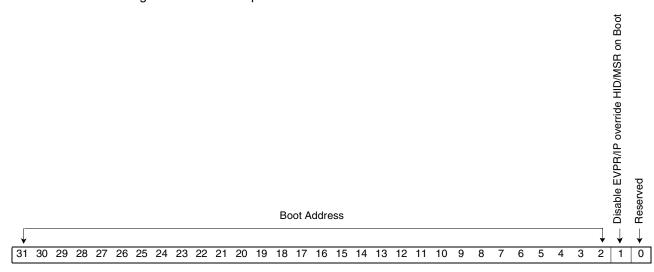

| PCORE Cobra Core Boot Address                           |     |

| PCORE Cobra Core Access Priority Control Register       | 478 |

|    | PCORE Transaction Dead Man Timer Value Registers        | 480 |

|----|---------------------------------------------------------|-----|

|    | PCORE High Priority Access Timer Value Registers        |     |

|    | PCORE Transaction Dead Man Timer Register               |     |

|    | PCORE IBM3206K0424 Shadow Status Register               |     |

|    | PCORE IBM3206K0424 Packet Last Write with Error Address |     |

|    | PCORE IBM3206K0424 RXQUE Master Status Register         |     |

|    | PCORE IBM3206K0424 RXQUE Enabled Status Register 1      |     |

|    | PCORE IBM3206K0424 RXQUE Enabled Status Register 2      |     |

|    | PCORE IBM3206K0424 RXQUE Upper Queues Status Register   |     |

|    | PCORE IBM3206K0424 RXQUE Lower Queues Status Register   |     |

|    | PCORE DMAQS Master Status Register                      |     |

|    | PCORE DMAQS Enabled Status Register                     |     |

|    | PCORE RXQUE Queue Length Registers                      |     |

|    | PCORE DMAQS Queue Length Registers                      |     |

|    | PCORE Interrupt Enable Register                         |     |

|    | PCORE User Interrupt Enable                             |     |

|    | PCORE Cobra Core Interrupt Enable Register              |     |

|    | PCORE Cobra Core External Machine Check Enable Register |     |

|    | PCORE Error Lock Enable Register                        |     |

|    | PCORE User Error Lock Enable Register                   |     |

|    | PCORE RXQUE Event Interface Enqueue Register            |     |

|    | PCORE DMAQS DMA Enqueue Register                        |     |

|    | PCORE RXQUE Event Interface Deque Register              |     |

|    | PCORE Cobra SPR Read Data Access Register               |     |

|    | PCORE Cobra SPR Write Data Access Register              |     |

|    | PCORE Cobra SPR Access Address Register                 |     |

|    | PCORE Address Translation Offset Address Facilities     |     |

|    | PCORE PCI 64 Bit Address Translation Facilities         |     |

|    | PCORE PCI Master Target Tag Controls                    |     |

|    | PCORE Last Packet Address Register                      |     |

|    | PCORE Last Control Address Register                     |     |

|    | PCORE Last PCI Lower Address Register                   |     |

|    | PCORE Last Register Address Register                    |     |

|    | PCORE SRAM Base Address                                 |     |

|    | PCORE Read Data Transfer Buffers                        |     |

|    | PCORE Write Data Transfer Buffers                       |     |

|    | PCORE Polling Register                                  |     |

|    | PCORE Integer Input Rate Conversion Register            |     |

|    | PCORE ABR Output Rate Register                          |     |

|    | PCORE Debug States Control                              |     |

|    | PCORE Debug States Config                               |     |

| D  |                                                         |     |

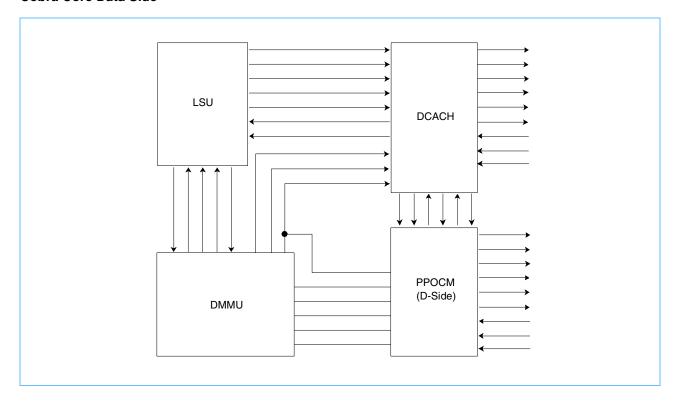

| PO | verPC On-Chip Memory (PPOCM) Entity                     |     |

|    | DMA Controller                                          |     |

|    | PPOCM Status Register                                   |     |

|    | PPOCM Interpret Freehle Perinter                        |     |

|    | PPOCM Interrupt Enable Register                         |     |

|    | PPOCM DMA Or Objective Address Register                 |     |

|    | PPOCM DMA On-Chip Effective Address Register            |     |

|    | PPOCM DMA Length Register                               |     |

|    | PPOCM DMA Timeout Timer Register                        | 504 |

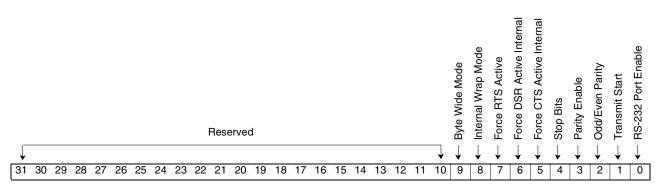

| RS-232 Interface Logic (RS-232)         | 505 |

|-----------------------------------------|-----|

| RS-232 Interface Logic Registers        | 505 |

| RS-232 Control Register                 | 505 |

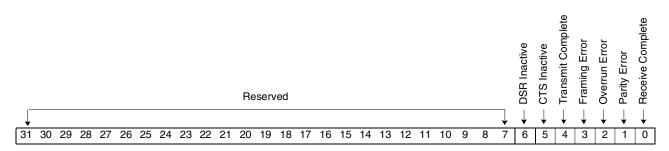

| RS-232 Status Register                  | 506 |

| RS-232 Interrupt Enable Register        | 507 |

| RS-232 Transmit Buffer                  | 507 |

| RS-232 Receive Buffer                   | 508 |

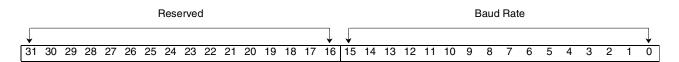

| RS-232 Baud Rate Register               |     |

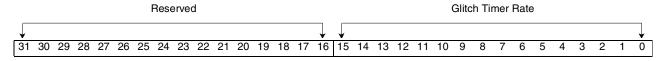

| RS-232 CTS/DSR Glitch Timer Rate        | 509 |

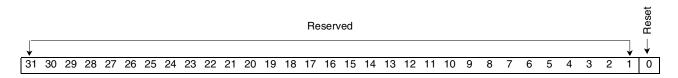

| RS-232 Reset Register                   | 509 |

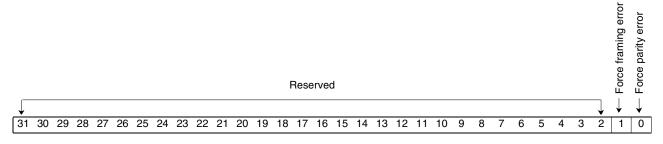

| RS-232 Error Forcing Register           |     |

| Reset and Power-on Logic (CRSET)        | 511 |

| Reset and Power-on Logic Registers      | 511 |

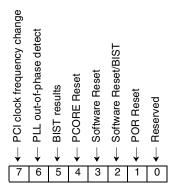

| Reset Status Register                   |     |

| Software Reset Enable Register          | 512 |

| Software Reset Register                 |     |

| Memory Type Register                    | 513 |

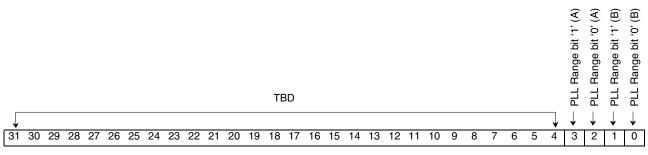

| CRSET PLL Range Debug                   | 514 |

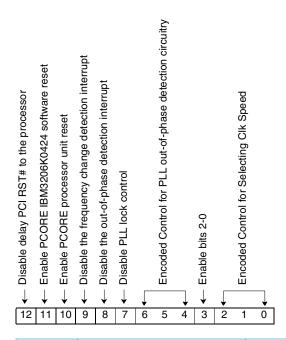

| CRSET Control Register                  | 515 |

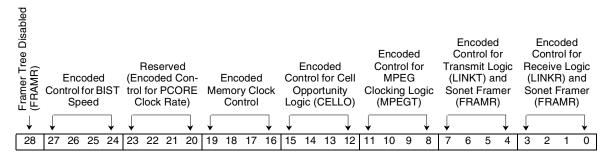

| Clock Control Register (Nibble Aligned) | 516 |

| CBIST PRPG Results                      | 518 |

| CBIST MISR Results                      | 518 |

| CBIST BIST Rate                         | 518 |

| CBIST PRPG Expected Signature           | 518 |

| CBIST MISR Expected Signature           |     |

| CBIST CYCT Load Value                   | 519 |

| JTAG Interface Logic (CJTAG)            | 520 |

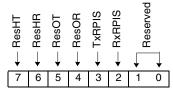

| Scanning                                | 520 |

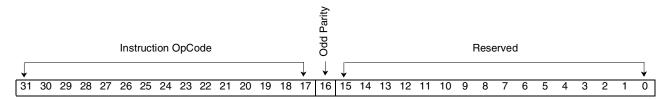

| Instruction Format                      | 521 |

| Instructions                            | 522 |

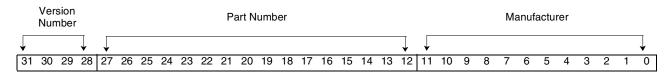

| IDCODE                                  |     |

| SAMPLE/PRELOAD                          |     |

| EXTEST                                  | 522 |

| BYPASS                                  | 522 |

| RUNBIST                                 | 523 |

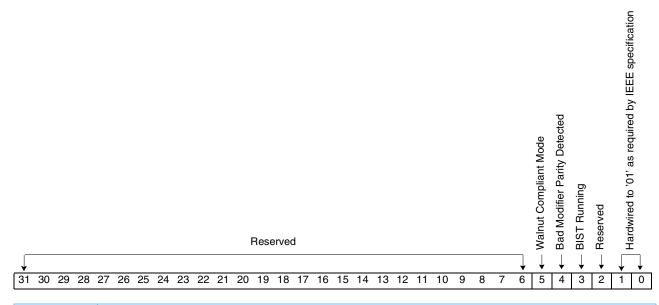

| BIST_RESULTS                            |     |

| WALNUT_MODE                             |     |

| COMPLIANT_MODE                          |     |

| STOP                                    | 523 |

| SCAN                                    |     |

| SCAN_IN                                 |     |

| SCAN_OUT                                |     |

| Private_RW1                             |     |

| Private_RW2                             |     |

| Private RW3                             | 524 |

| net Framer Core (FRAMR Chiplet Address Mapping)               |     |

|---------------------------------------------------------------|-----|

| GPPINT Architecture                                           |     |

| Overview                                                      |     |

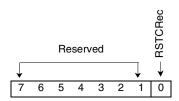

| Reset Register                                                |     |

| Interrupt Registers                                           |     |

| Handshaking Error Registers                                   |     |

| Clock Monitor Status Registers                                |     |

| Local Gppint Configuration Registers                          |     |

| Global Static Configuration Registers                         |     |

| Status Registers                                              |     |

| GPPINT Register Description                                   | 528 |

| Chiplet Reset Register (RESGP)                                | 528 |

| Chiplet Interrupt and Mask Registers (IRQGP1 (IRMGP1))        | 529 |

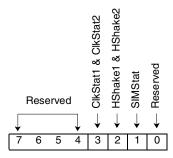

| Handshaking Error Indication and Mask Registers (HShake1)     | 530 |

| Clock Monitor Status and Mask Registers (ClkStat1 (ClkMask1)) | 531 |

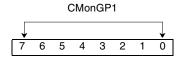

| Clock Monitor Test Period Register (CMonGP1)                  | 532 |

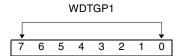

| Watchdog Timer Period Register (WDTGP1)                       | 532 |

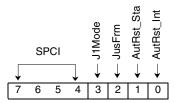

| GPPINT Local Configuration Registers (ConfGP1)                | 533 |

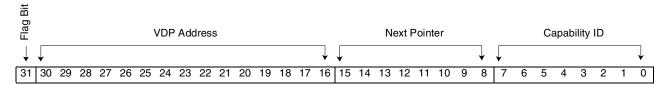

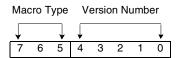

| Vital Macro Data Register (VPD)                               | 534 |

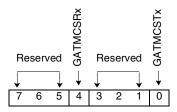

| Static Configuration Register (GATMCS)                        | 534 |

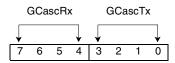

| GCasc                                                         | 535 |

| GLoopTx                                                       | 535 |

| GLoopRx                                                       | 536 |

| GExtRes                                                       | 536 |

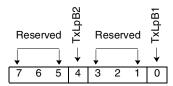

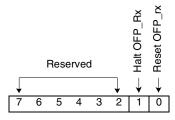

| OFPTXGP                                                       | 537 |

| OFPRXGP1                                                      | 537 |

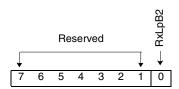

| OFPRXGP2                                                      | 538 |

| PIMRConf2                                                     | 538 |

| SIMStat                                                       | 539 |

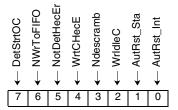

| GPPHandler Architecture                                       | 540 |

| Overview                                                      | 540 |

| Counter Registers                                             |     |

| Reset Registers                                               |     |

| Command Registers                                             |     |

| Event Latch Registers                                         |     |

| Interrupt Registers                                           |     |

| Configuration Registers                                       |     |

| Register Types                                                |     |

| ATM Cell Handler Architecture : Transmit Direction            |     |

| ACH Tx Register Description                                   |     |

| Counter Registers                                             |     |

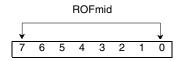

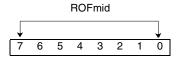

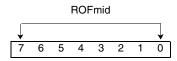

| ROFmid                                                        |     |

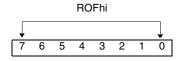

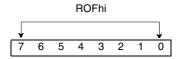

| ROFhi                                                         |     |

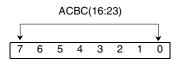

| ACBC                                                          |     |

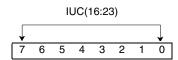

| IUC                                                           |     |

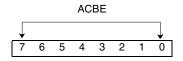

| ACBE                                                          |     |

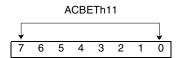

| ACBETh11                                                      |     |

|                                                               |     |

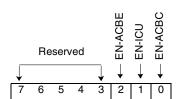

| CntEn1                                                        |     |

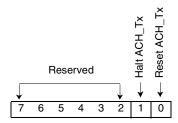

| Reset Register (RESET)                                        |     |

| Status Registers                                              |     |

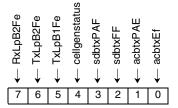

| STAT1                                                         | 548 |

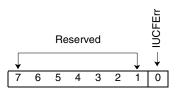

|    | IUCSTAT1                                       | 549 |

|----|------------------------------------------------|-----|

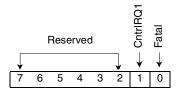

|    | Interrupt Request and Mask Registers           | 549 |

|    | MainIRQ                                        |     |

|    | M MainIRQ                                      |     |

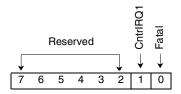

|    | CntrlRQ1                                       |     |

|    | M CntrlRQ1                                     |     |

|    | Configuration Registers                        |     |

|    | CELLTENABLE                                    |     |

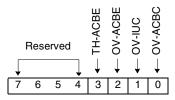

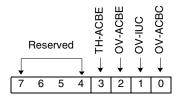

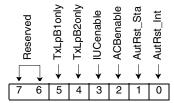

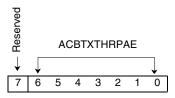

|    | ACBTXTHRPAE                                    |     |

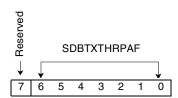

|    | SDBTXTHRPAF                                    |     |

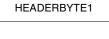

|    | HEADERBYTE1                                    |     |

|    | HEADERBYTE2                                    |     |

|    | HEADERBYTE3                                    |     |

|    | HEADERBYTE4                                    |     |

|    | HEADERBYTE5                                    |     |

|    | PAYLOADBYTE                                    |     |

|    | HECENCTRL                                      |     |

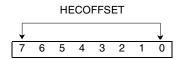

|    | HECOFFSET                                      |     |

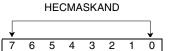

|    | HECMASKAND                                     |     |

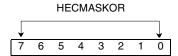

|    | HECMASKOR                                      |     |

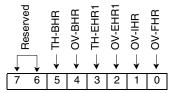

| ΔΤ | M Cell Handler Architecture: Receive Direction |     |

| ٠  | ACH_Rx Register Description                    |     |

|    | Counter Registers                              |     |

|    | ROFmid                                         |     |

|    | ROFhi                                          |     |

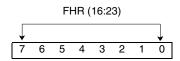

|    | FHR                                            |     |

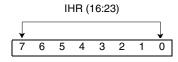

|    | IHR                                            |     |

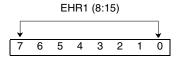

|    | EHR1                                           |     |

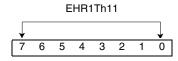

|    | EHR1Th11                                       |     |

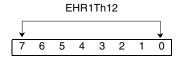

|    | EHT1Th12                                       |     |

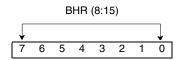

|    | BHR                                            |     |

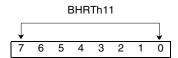

|    | BHRTh11                                        |     |

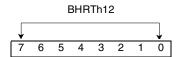

|    | BHRTh12                                        |     |

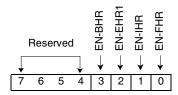

|    | CntEn1                                         |     |

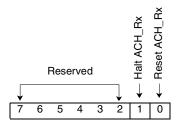

|    | Reset Register (RESET)                         |     |

|    | Command Register (CMD1)                        |     |

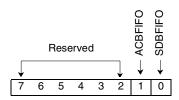

|    | Status Register (STAT1)                        |     |

|    | Interrupt Request and Mask Registers           |     |

|    | MainIRQ                                        |     |

|    | M MainIRQ                                      |     |

|    | CntrlRQ1                                       |     |

|    | M CntrlRQ1                                     |     |

|    | Configuration Registers                        |     |

|    | CONF5                                          |     |

|    | CONF6                                          |     |

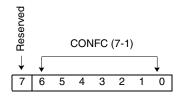

|    | CONFC                                          |     |

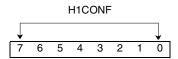

|    | H1CONF                                         |     |

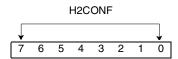

|    | H2CONF                                         |     |

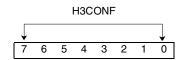

|    | H3CONF                                         |     |

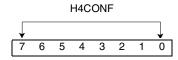

|    | H4CONF                                         |     |

|    | H5CONF                                         |     |

|    |                                                | -   |

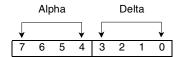

| Overhead Frame Processor Architecture: Transmit Direction | 579 |

|-----------------------------------------------------------|-----|

| OFP_Tx Register Description                               | 582 |

| Counter Registers                                         | 582 |

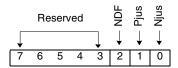

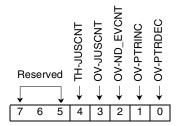

| PTRINC                                                    | 582 |

| PTRDEC                                                    | 582 |

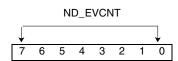

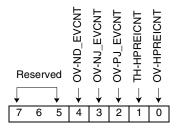

| ND_EVCNT                                                  |     |

| JUSCNT                                                    |     |

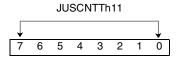

| JUSCNTTh11                                                |     |

| CntEn1                                                    |     |

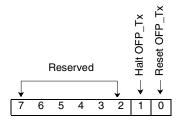

| Reset Register (RESET)                                    |     |

| Command Register (CMD1)                                   |     |

| Status Registers                                          |     |

| STAT1                                                     |     |

| STAT2                                                     |     |

| Interrupt and Mask Registers                              |     |

| MainIRQ                                                   |     |

| M MainIRQ                                                 |     |

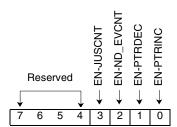

| CntrIRQ1                                                  |     |

| M CntrIRQ1                                                |     |

| IRQ3                                                      |     |

| M IRQ3                                                    |     |

|                                                           |     |

| Configuration Registers                                   |     |

|                                                           |     |

| CONF2                                                     |     |

| CONF4                                                     |     |

| CONF4                                                     |     |

| CONF5                                                     |     |

| CONF6                                                     |     |

| CONF7                                                     |     |

| CONF8                                                     |     |

| CONF9                                                     |     |

| CONF10                                                    |     |

| Overhead Frame Processor Architecture: Receive Direction  |     |

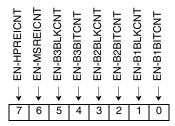

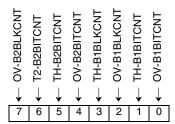

| Counter Registers                                         |     |

| ROFmid                                                    |     |

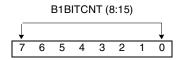

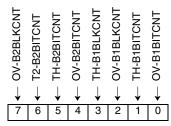

| B1BITCNT                                                  |     |

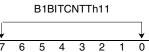

| B1BITCNTTh11                                              |     |

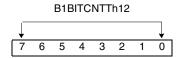

| B1BITCNTTh12                                              |     |

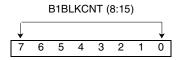

| B1BLKCNT                                                  |     |

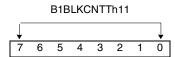

| B1BLKCNTTh11                                              | 606 |

| B1BLKCNTTh12                                              | 607 |

| B2BITCNT                                                  |     |

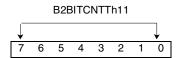

| B2BITCNTTh11                                              |     |

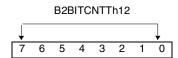

| B2BITCNTTh12                                              | 608 |

| B2BITCNTTh21                                              | 609 |

| B2BITCNTTh22                                              | 609 |

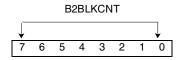

| B2BLKCNT                                                  | 610 |

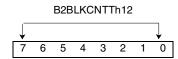

| B2BLKCNTTh11                                              | 610 |

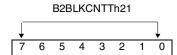

| B2BLKCNTTh12                                              | 611 |

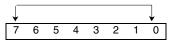

| B2BLKCNTTh21                                              | 611 |

| B2BLKCNTTh22                                              | 612 |

| B3BITCNT                     | .612 |

|------------------------------|------|

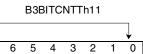

| B3BITCNTTh11                 | .613 |

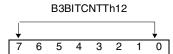

| B3BITCNTTh12                 | .613 |

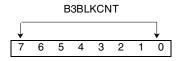

| B3BLKCNT                     | .614 |

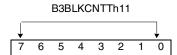

| B3BLKCNTTh11                 | .614 |

| B3BLKCNTTh12                 | .615 |

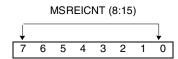

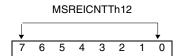

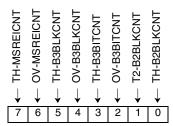

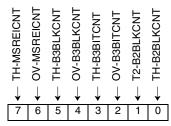

| MSREICNT                     | .615 |

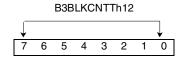

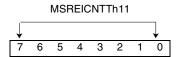

| MSREICNTTh11                 | .616 |

| MSREICNTTh12                 | .616 |

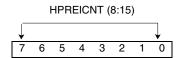

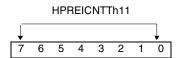

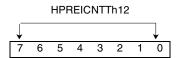

| HPREICNT                     | .617 |

| HPREICNTTh11                 | .617 |

| HPREICNTTh12                 | .618 |

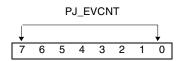

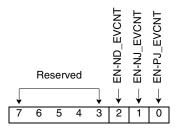

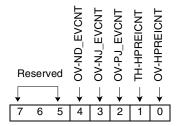

| PJ_EVCNT                     | .618 |

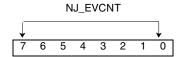

| NJ_EVCNT                     | .619 |

| ND_EVCNT                     | .619 |

| CntEn1                       | .620 |

| CntEn2                       |      |

| Reset Register (RESET)       |      |

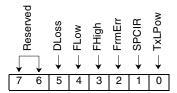

| Status Registers             |      |

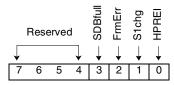

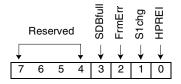

| STAT1                        | .622 |

| STAT2                        | .623 |

| STAT3                        | .624 |

| STAT4                        | .625 |

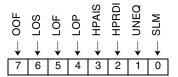

| Interrupt and Mask Registers |      |

| MainIRQ                      | .626 |

| M_MainIRQ                    | .627 |

| CntrlRQ1                     |      |

| M_CntrIRQ1                   | .629 |

| CntrlRQ2                     | .630 |

| M_CntrIRQ2                   | .631 |

| CntrlRQ3                     | .632 |

| M_CntrIRQ3                   |      |

| IRQ6                         | .634 |

| M_IRQ6                       |      |

| IRQ7                         |      |

| M_IRQ7                       |      |

| IRQ8                         |      |

| M_IRQ8                       | .639 |

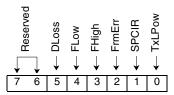

| Configuration Registers      |      |

| CONF1                        |      |

| CONF2                        | .641 |

| CONF3                        |      |

| CONF4                        |      |

| CONF7                        |      |

| CONF8                        |      |

| CONFO                        | CAE  |

| Memory Map for Registers and Arrays |     |  |  |  |  |  |  |

|-------------------------------------|-----|--|--|--|--|--|--|

| Signal Pin Listing By Signal Name   | 648 |  |  |  |  |  |  |

| AC Timing Characteristics           | 653 |  |  |  |  |  |  |

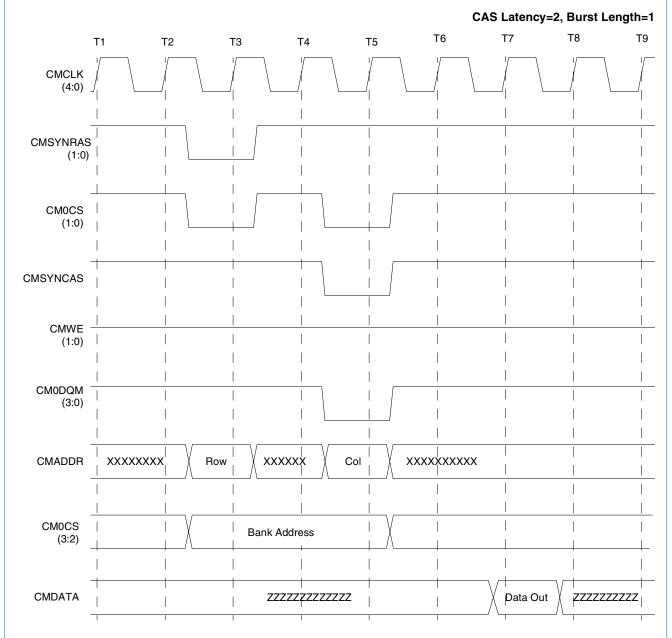

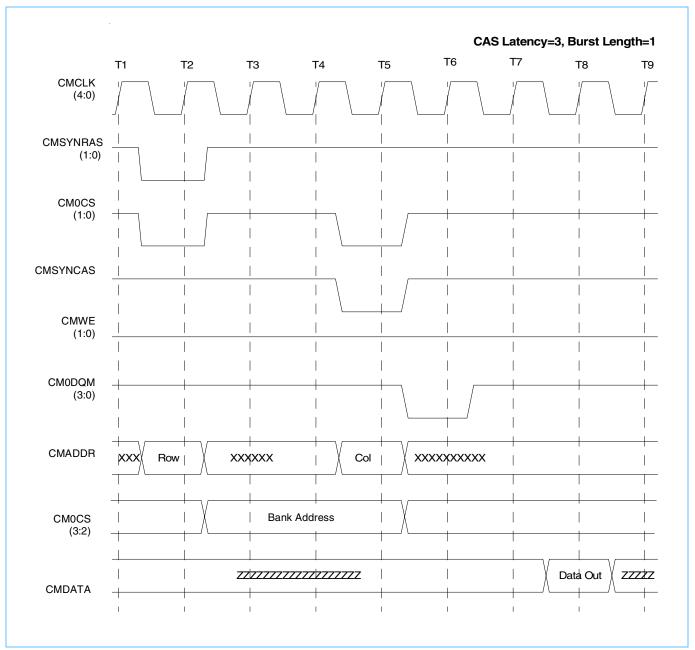

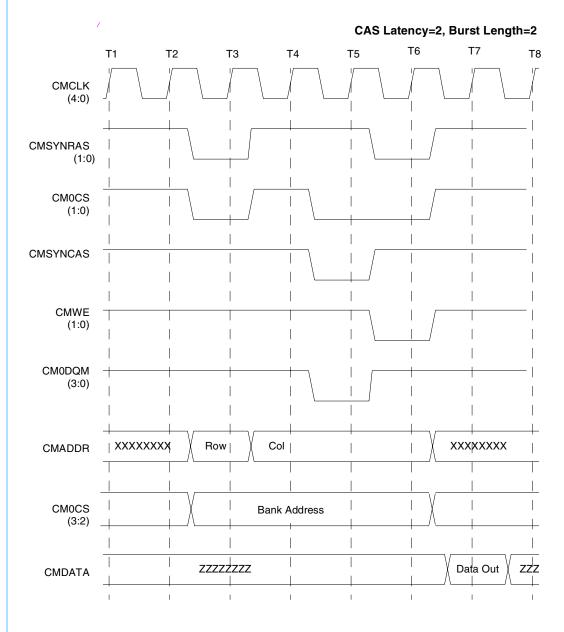

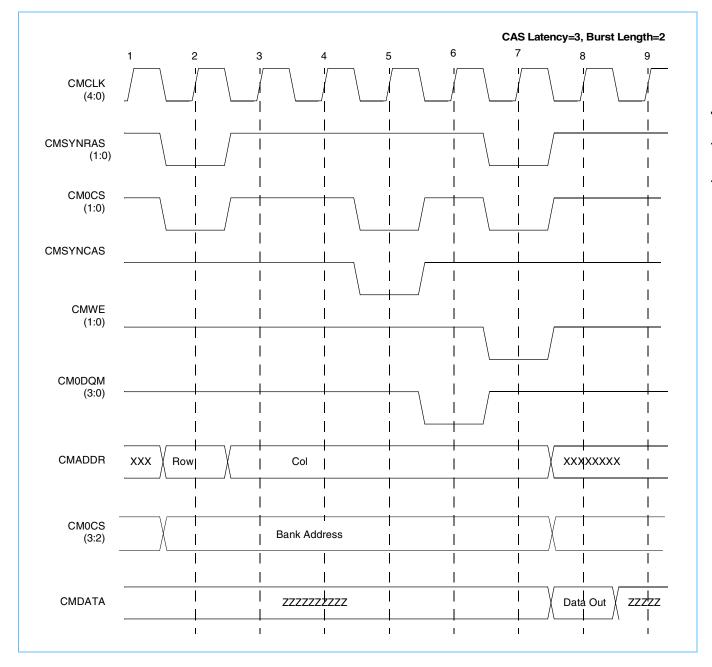

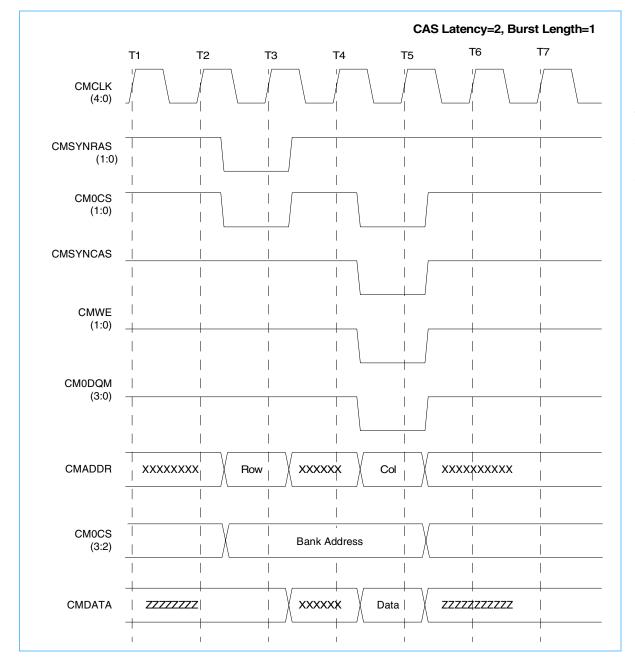

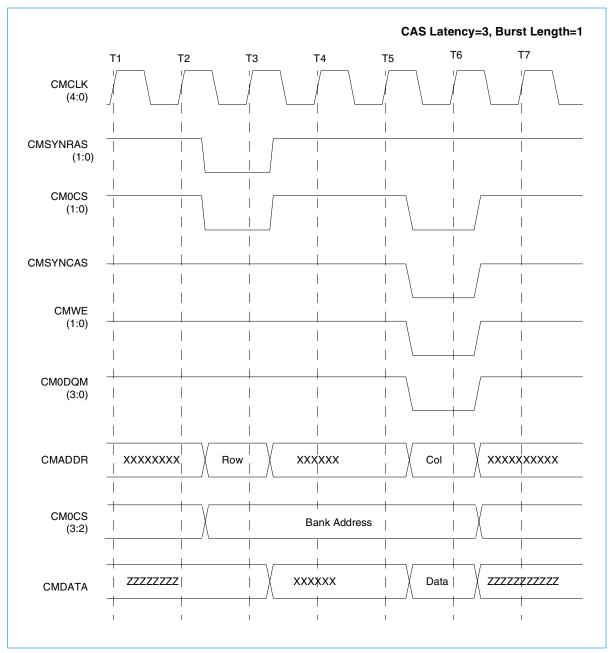

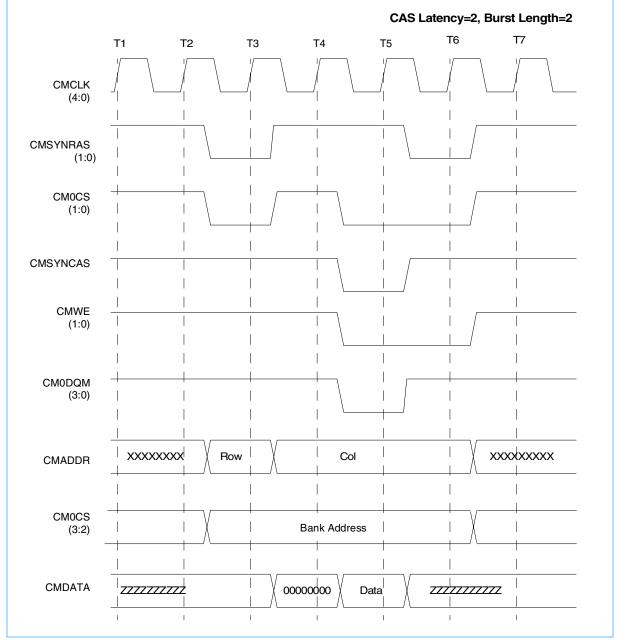

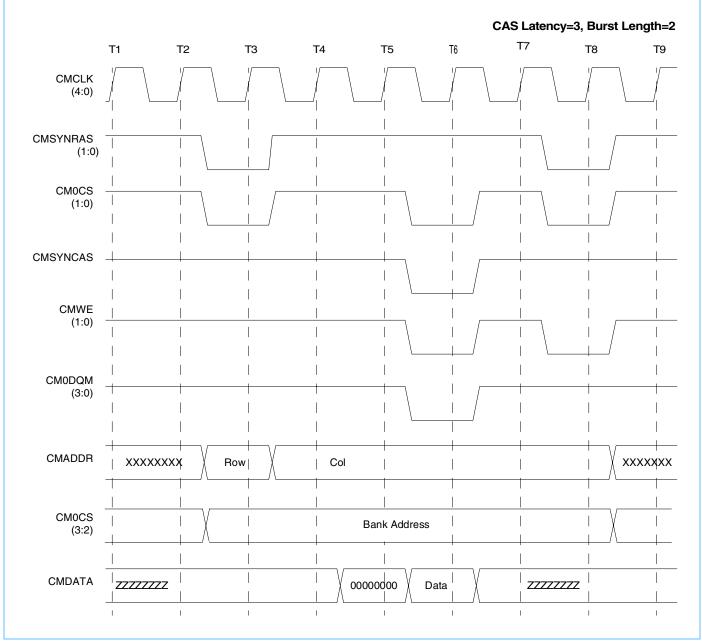

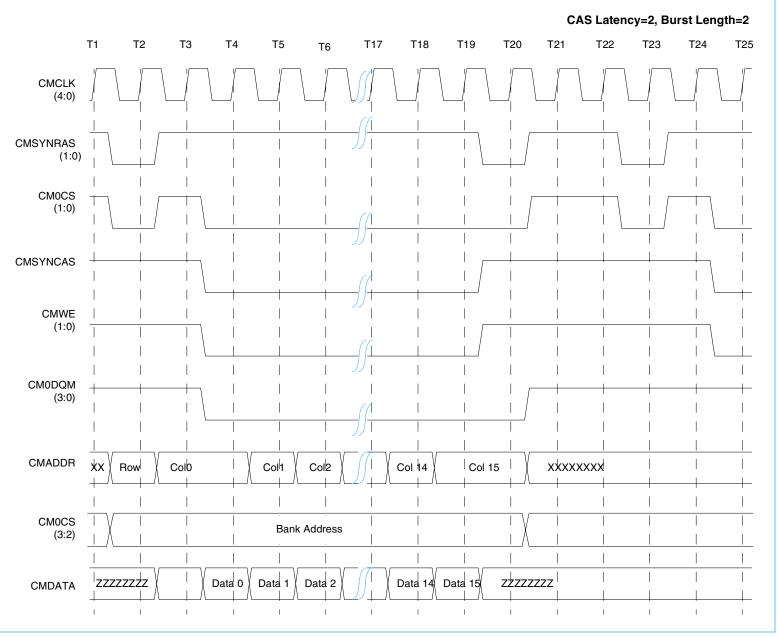

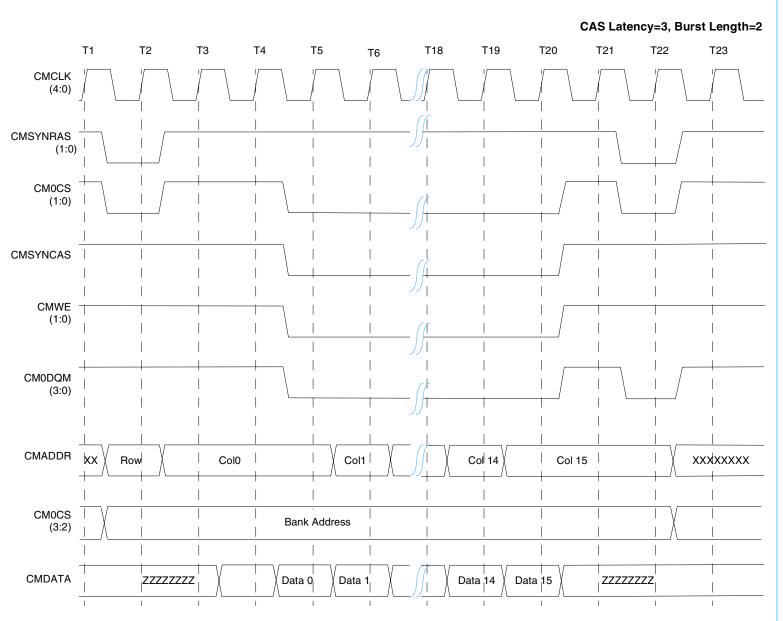

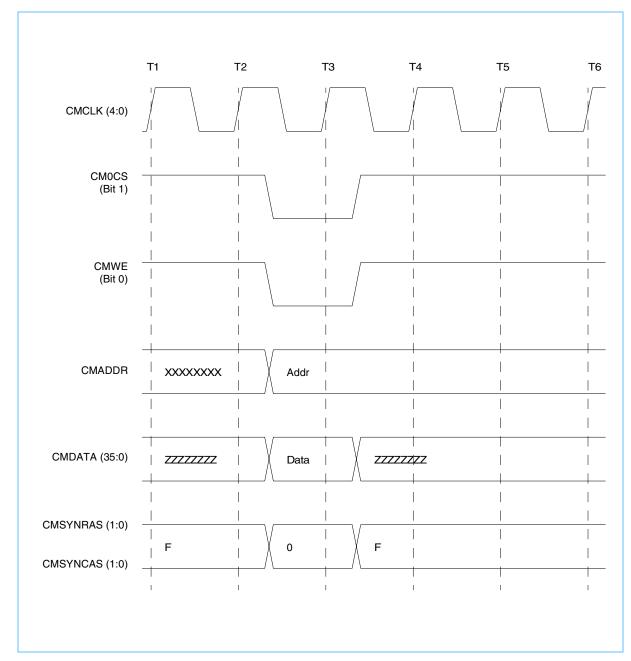

| Synchronous DRAM Timing Diagrams    | 656 |  |  |  |  |  |  |

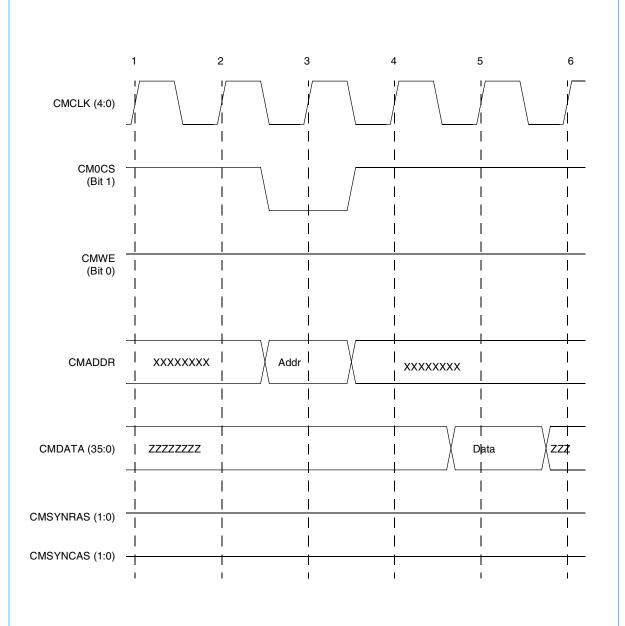

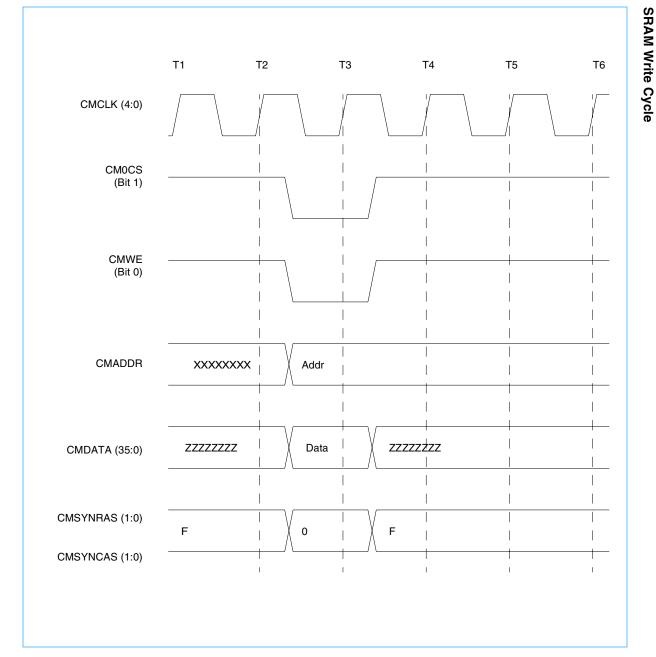

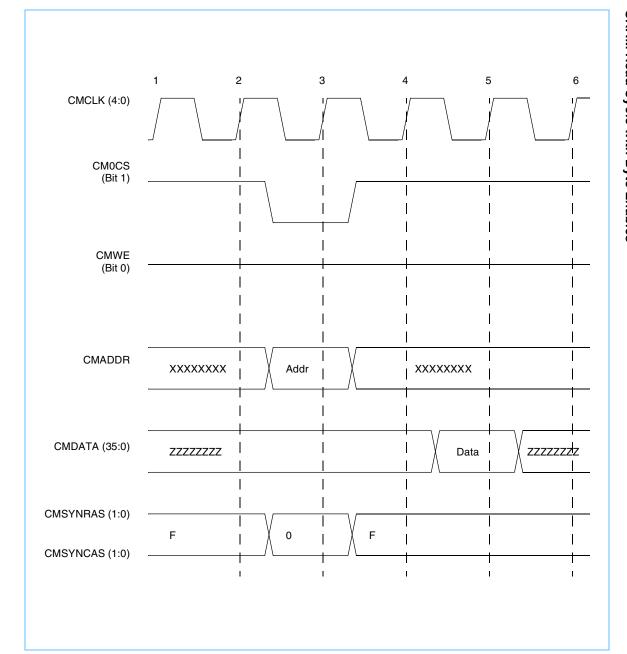

| SRAM Timing Diagrams                | 666 |  |  |  |  |  |  |

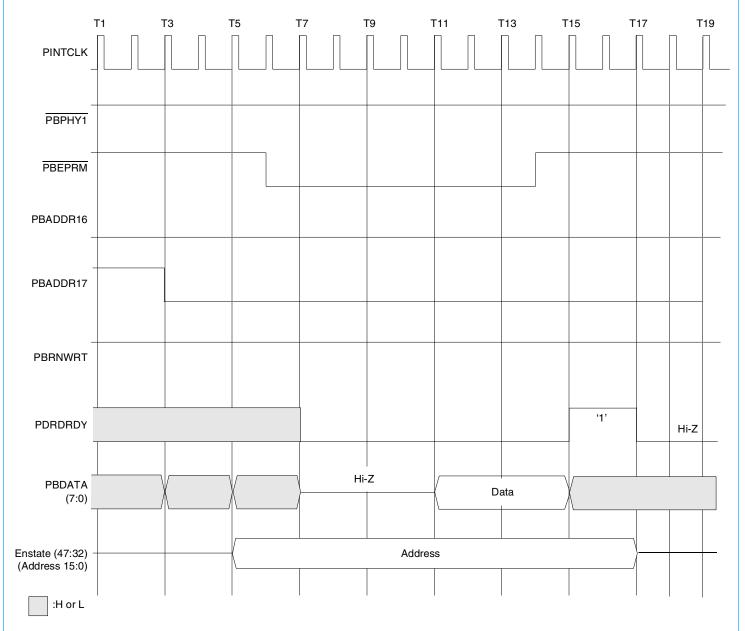

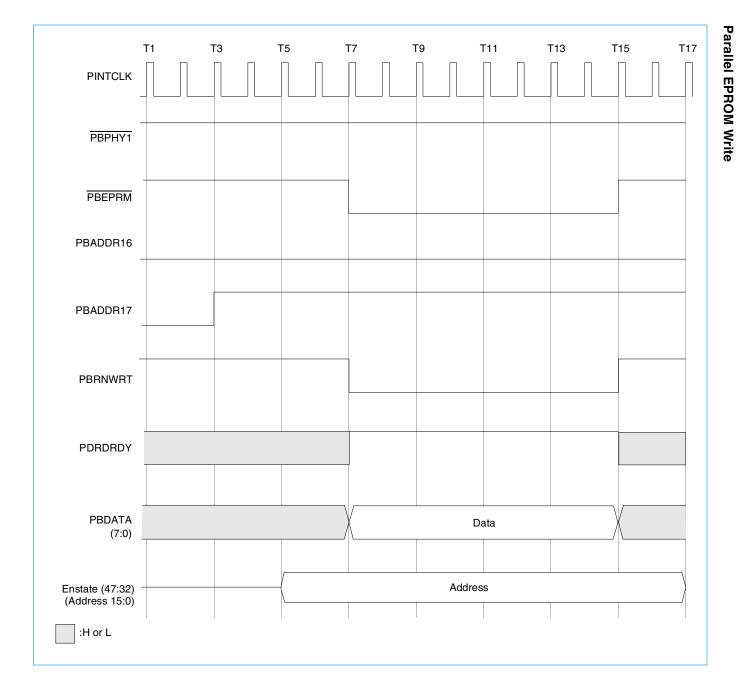

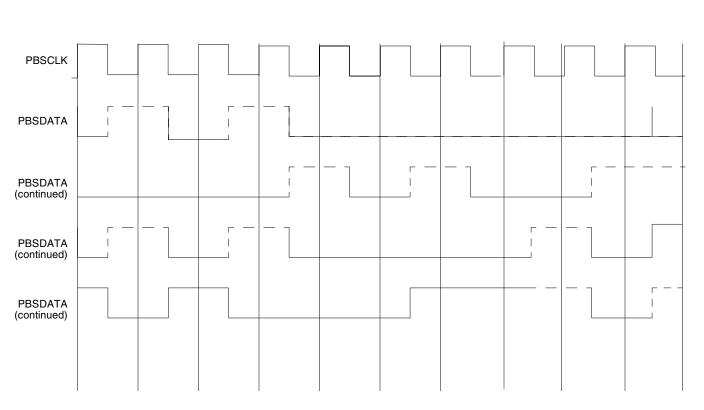

| EPROM Timing Diagrams               | 670 |  |  |  |  |  |  |

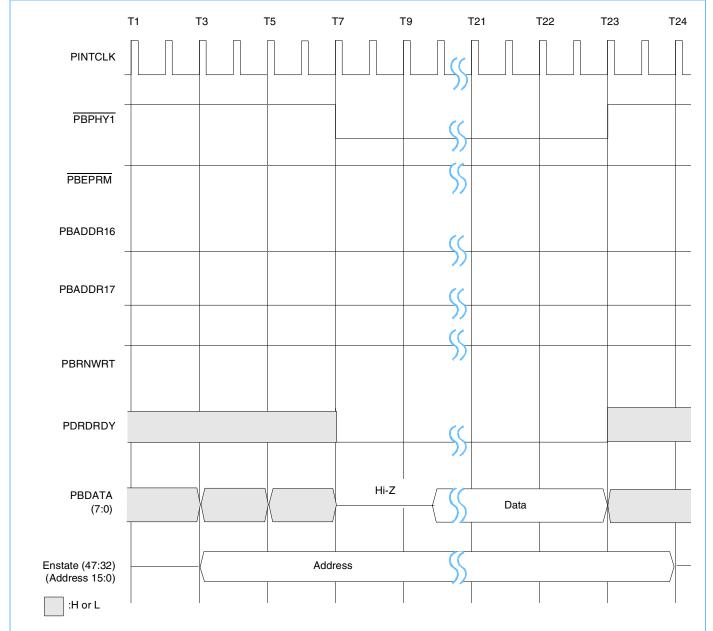

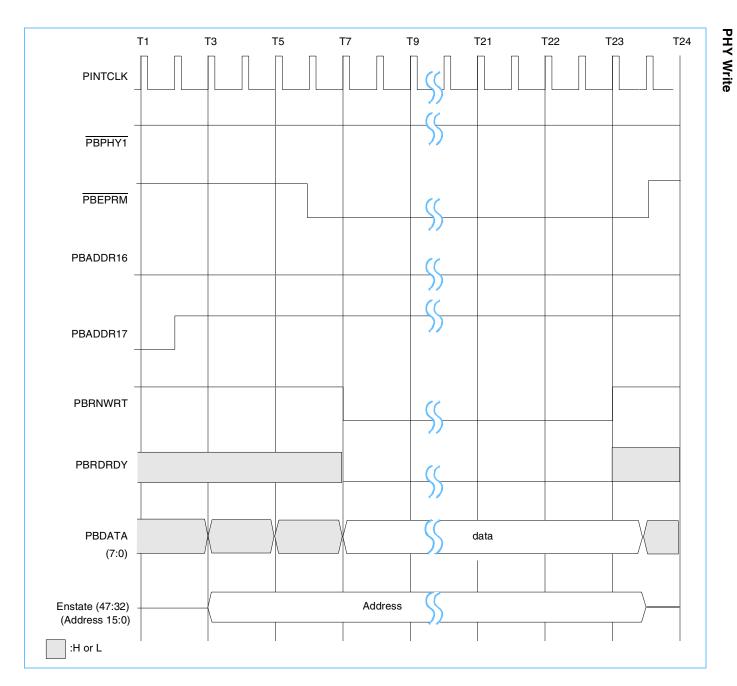

| PHY Timing Diagrams                 |     |  |  |  |  |  |  |

| Revision Log                        | 676 |  |  |  |  |  |  |

### **IBM Processor for Network Resources**

#### **Features**

- Supports multiple protocols, including ATM, POS, Frame Relay, and 10/100/Gigabit Ethernet

- Has a customizable on-chip 133 MHz PowerPC™ processor core

- Manages up to 65535 simultaneous logical channels, individually or in groups

- Integrated 155 Mb/s SONET (Synchronous Optical Network) Framer for simpler, low bandwidth designs

- Flexible ATM Forum-compliant UTOPIA II interface with up to four PHYs

- · Switch Interface Extensions

- PCI 32/64-bit interface up to 66MHz.

- Configurable for sustained performance through the subsystem:

- 155Mb/s full duplex internal SONET framer

- 622Mb/s full duplex using an external SONET framer

- 622Mb/s across up to four full duplex 155Mb/s links using an external quad framer

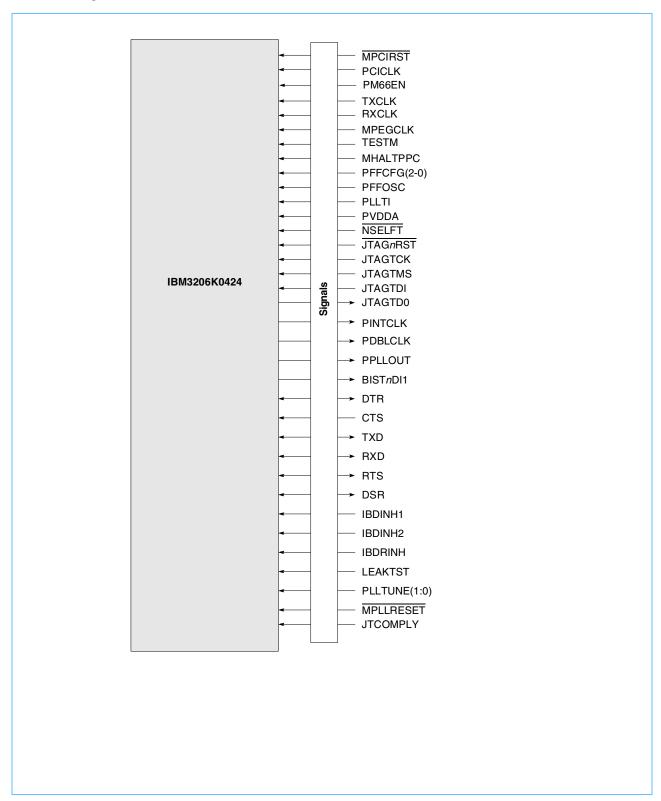

- · JTAG Test Interface

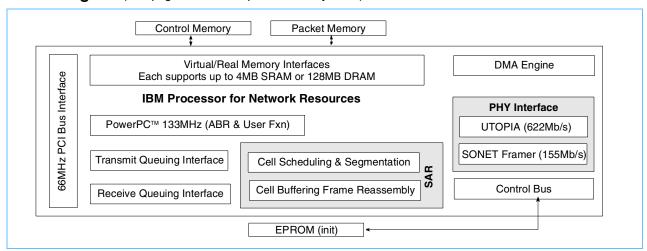

- Package: 624 lead, 32 mm x 32 mm CBGA

- Power Supply: 2.6 V ±2%; 3.3 V ±5%.

## **Description**

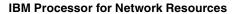

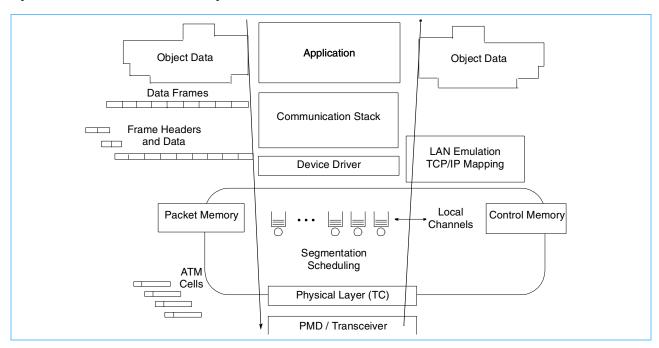

The IBM Processor for Network Resources (IBM3206K0424) is an Asynchronous Transfer Mode (ATM) support device. It is an interface and translator between a Peripheral Component Interconnect (PCI) bus and an ATM Utopia or similar interface to an ATM PHY. The IBM3206K0424 has an integrated Packet/Frame Memory (DRAM con-

troller) and performs Segmentation and Reassembly (SAR) functions for several of the ATM Adaptation Layers (AALs). The IBM3206K0424 functions are illustrated in the *Block Diagram* on page 21. A Network Interface Card example is shown in *System Context of an ATM Subsystem* on page 34.

### **Block Diagram** (See page 29 for descriptions of subsystems)

Preliminary

### **Ordering Information**

| Part Number  | Description              |

|--------------|--------------------------|

| IBM3206K0424 | Network Resource Manager |

### Conventions

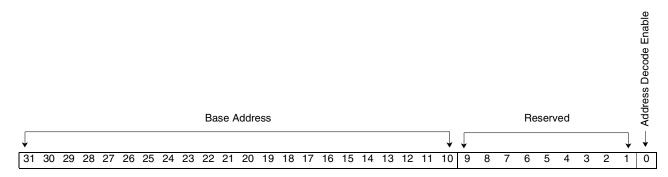

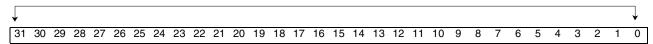

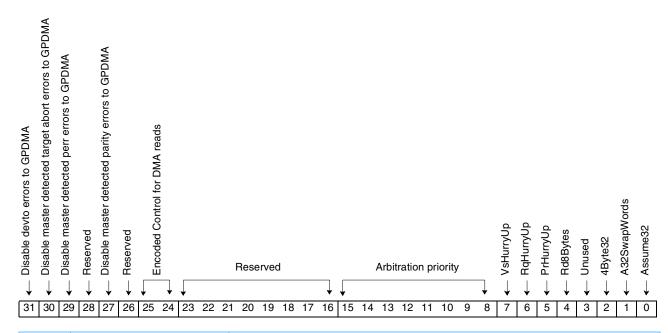

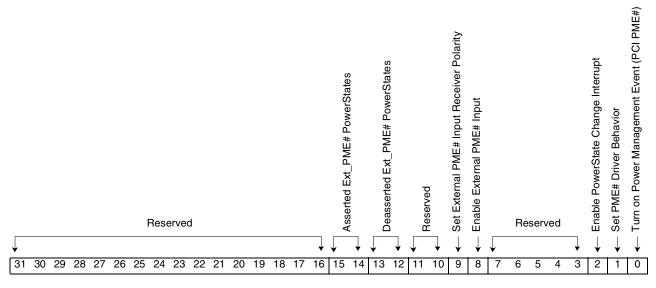

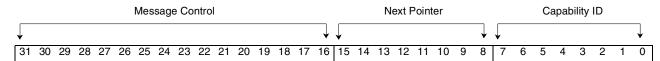

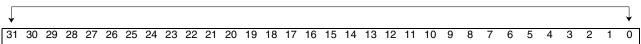

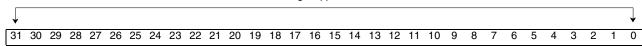

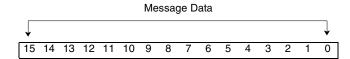

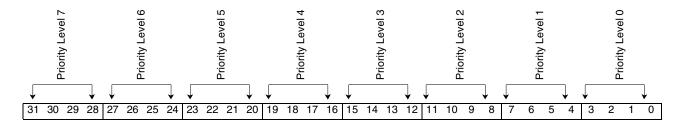

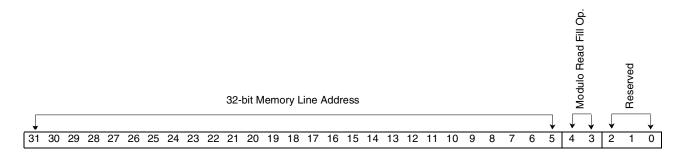

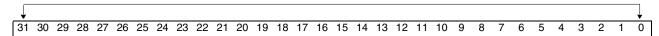

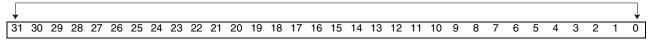

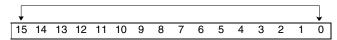

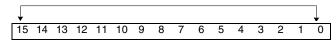

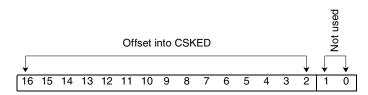

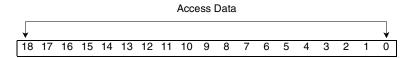

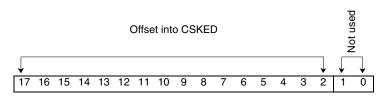

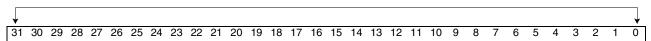

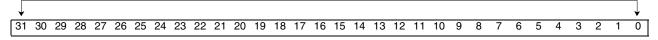

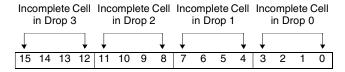

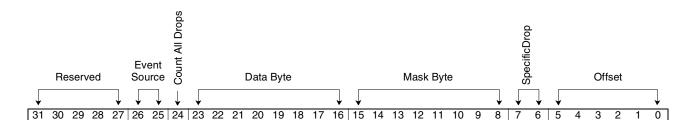

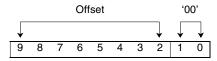

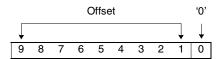

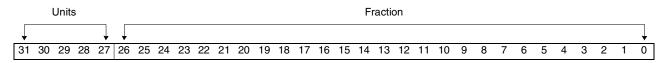

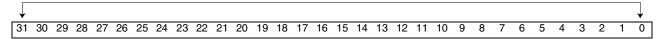

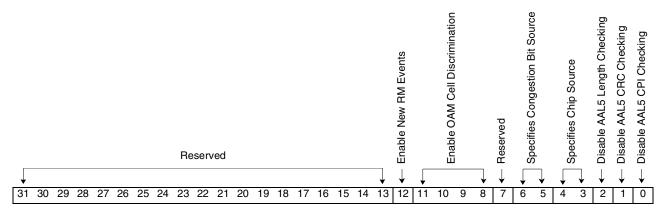

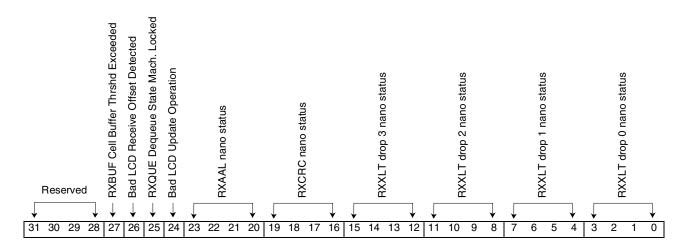

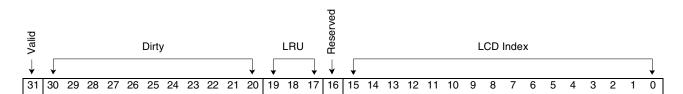

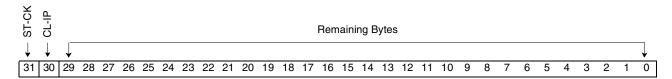

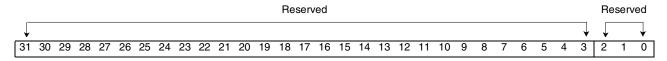

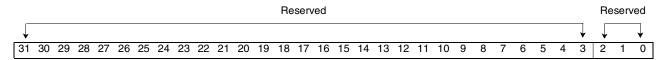

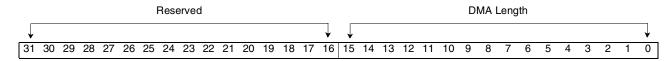

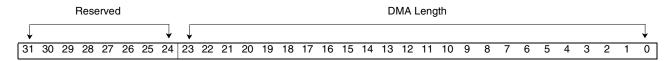

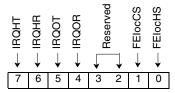

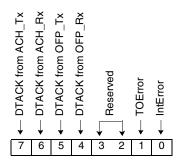

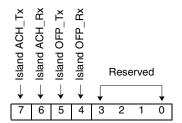

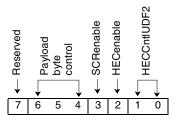

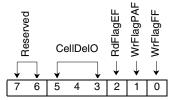

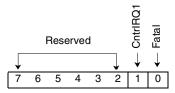

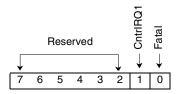

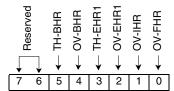

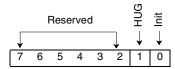

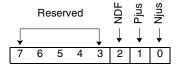

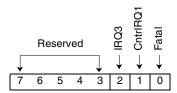

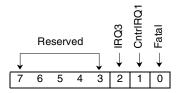

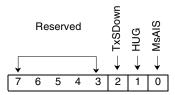

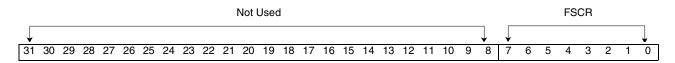

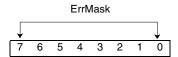

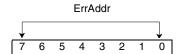

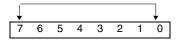

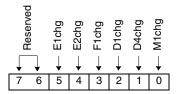

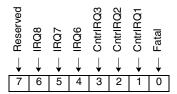

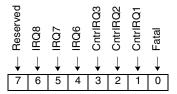

The bit notation is non-IBM, meaning that bit zero is the least significant bit and bit 31 is the most significant bit for a four-byte word.

The internal addressing view of the IBM3206K0424 registers and memory is big endian. In most cases, a system will wire its PCI bus interface to make the register view transparent, that is, the most significant bit in this specification will be the most significant bit in the register. If registers are read and written 32 bits at a time (which is the only way to access many of the registers), the endian-ness should not be a programming issue with respect to the registers.

The IBM3206K0424 DMA controller can transfer data in either big endian or little endian mode. See *General Purpose DMA (GPDMA)* on page 175 for details.

Numeric notation is as follows:

- Hexadecimal values are usually preceded by x or X. For example: X'0B00'. For individual registers, Address values are hexadecimal without any special markings. For example, XXXX 1C3C.

- Binary values in text are either spelled out (zero and one) or appear in quotation marks. For example: '10101'.

- Binary values in the Default and Description columns of the register sections are often isolated from text as in this example:

- 0: No action on read access

- 1: Auto-reset interrupt request register upon read access

## **Standards Compliance**

The IBM Processor for Network Resources, part number IBM3206K0424, has been designed with a number of standards in mind. These standards are listed below, grouped according to the area of IBM3206K0424 functionality they address.

- Network (defined by ITU-TS (formerly CCITT), ANSI and ATM Forum)

- ITU Recommendation I-361 B-ISDN ATM layer specification

- ITU Recommendation I.362 B-ISDN ATM Adaptation Layer (AAL) functional description

- ITU Recommendation I.363 B-ISDN ATM Adaptation Layer (AAL) specification

- ITU Recommendation I.413 B-ISDN user-network interface

- ITU Recommendation I-432 B-ISDN user-network interface Physical Layer specification

- ITU Recommendation I-610 OAM principles of B-ISDN access

- ANSI T1.ATM-199x Draft, Broadband ISDN ATM Layer Functionality and Specification

- ANSI T1.CBR-199x Draft, Broadband ISDN ATM Adaptation Layer for Constant Bit Rate Service Functionality and Specification

- ATM Forum 93-620R2 ATM User-Network Interface Specification Version 2.3 (July 27, 1993)

- Bellcore TA-NWT-001248 Generic Requirements for Operations of Broadband Switching Systems (October 1993)

#### System Interface

- PCI Local Bus Specification, Production Version, Revision 2.1, June 1, 1995. Interface Technical Reference, 11/89, Part number 15F2160

#### · PHY Interface

- SATURN User Network Interface, PMC-Sierra, Inc., February 1995

- ATM Forum 93-727 An ATM PHY Data path interface, Version 2.01, March 24, 1994

- Am7968/Am7969 TAXIchip(tm) Handbook, Transparent Asynchronous Transmitter/Receiver Interface, published by Advanced Micro Devices, 1994

pnr25.chapt01.01 Standards Compliance

August 14, 2000 Page 23 of 676

## **Environmental Ratings**

## **Absolute Maximum Ratings**

| Parameter                              | Rating     | Unit | Note |

|----------------------------------------|------------|------|------|

| Supply Voltage, V <sub>DD</sub> 1      | 2.3 to 2.7 | V    | 1    |

| Supply Voltage, V <sub>DD</sub> 2      | 3.0 to 3.6 | V    | 1    |

| Storage Temperature                    | -65 to 150 | °C   | 1    |

| Ambient Temperature with Power Applied | -40 to 100 | °C   | 1    |

<sup>1.</sup> These are the maximum ratings that can be applied to the device without damage. The device function and specifications are valid only within the Recommended Operating Conditions.

## **Recommended Operating Conditions**

| Parameter                                                 | Rating   | Unit |

|-----------------------------------------------------------|----------|------|

| Junction Temperature                                      | 0 to 85  | °C   |

| Supply Voltage, V <sub>DD</sub> 1, with respect to Ground | 2.6 ± 2% | V    |

| Supply Voltage, V <sub>DD</sub> 2, with respect to Ground | 3.3 ± 5% | V    |

## **Power Dissipation**

| Parameter                   | Rating | Unit |

|-----------------------------|--------|------|

| V <sub>DD</sub> 1 (nominal) | 6      | W    |

| V <sub>DD</sub> 2 (nominal) | 2      | W    |

Standards Compliance Page 24 of 676

## Package Diagram

## **Pinout Viewed from Above**

| AE  | AD   | AC  | AB   | AA  | Y    | W   | ٧    | U | T    | R   | P     | N     | M    | L   | К    | J  | Н    | G   | F    | Е   | D    | С   | В    | A   |    |         |         |

|-----|------|-----|------|-----|------|-----|------|---|------|-----|-------|-------|------|-----|------|----|------|-----|------|-----|------|-----|------|-----|----|---------|---------|

| S   | S    | T   | s    | T   | s    | T   | S    | s | S    | DCT | DCT   | DCT   | DCT  | DCT | s    | s  | s    | Т   | s    | Т   | S    | T   | S    | 0   | 1  |         |         |

| S   | G    | S   | VDD4 | S   | G    | S   | VDD  | S | G    | S   | VDD4  | DCT   | VDD  | S   | G    | S  | VDD  | S   | G    | S   | VDD4 | S   | G    | S   | 2  |         |         |

| Т   | s    | T   | s    | Т   | s    | T   | S    | s | S    | s   | DCT   | DCT   | DCT  | s   | s    | S  | s    | Т   | s    | Т   | S    | Т   | S    | T   | 3  |         |         |

| S   | VDD  | S   | G    | S   | VDD  | S   | G    | S | VDD4 | S   | G     | DCT   | G    | S   | VDD4 | S  | G    | S   | VDD  | S   | G    | s   | VDD  | S   | 4  | SIGNAL  | 467     |

| T   | S    | T   | s    | Т   | S    | S   | S    | S | S    | s   | T     | DCT   | T    | S   | S    | S  | S    | S   | s    | T   | S    | Т   | S    | T   | 5  | VDD     | 44      |

| S   | G    | S   | VDD3 | S   | G    | S   | VDD4 | S | G    | S   | VDD   | DCT   | VDD  | S   | G    | S  | VDD4 | S   | G    | S   | VDD5 | S   | G    | S   | 6  | VDD2    | 9       |

| Т   | S    | T   | S    | S   | S    | S   | S    | S | S    | s   | T     | DCT   | T    | S   | S    | S  | S    | S   | s    | S   | S    | Т   | S    | T   | 7  | VDD3    | 9       |

| S   | VDD3 | S   | G    | S   | VDD  | S   | G    | S | VDD4 | S   | G     | DCT   | G    | S   | VDD4 | S  | G    | S   | VDD  | S   | G    | S   | VDD5 | S   | 8  | VDD4    | 9       |

| S   | s    | S   | S    | S   | s    | S   | S    | S | s    | s   | S     | s     | S    | s   | s    | S  | S    | s   | s    | s   | S    | s   | S    | s   | 9  | VDD5    | 9       |

| S   | G    | S   | VDD  | S   | G    | S   | VDD3 | S | G    | s   | VDD   | S     | VDD  | S   | G    | S  | VDD5 | S   | G    | S   | VDD  | s   | G    | s   | 10 | GND     | 77      |

| DCT | S    | S   | S    | S   | S    | S   | S    | S | S    | VDD | S     | G     | S    | VDD | S    | S  | S    | S   | s    | S   | S    | s   | S    | DCT | 11 | ORIENT  | 1       |

| DCT | VDD3 | DCT | G    | Т   | VDD3 | T   | G    | S | VDD  | S   | G     | VDD   | G    | S   | VDD  | S  | G    | T   | VDD5 | T   | G    | DCT | VDD5 | DCT | 12 | TOTAL   | 625     |

| DCT | DCT  | DCT | DCT  | DCT | DCT  | DCT | DCT  | S | S    | G   | VDD   | G     | VDD  | G   | S    | S  | DCT  | DCT | DCT  | DCT | DCT  | DCT | DCT  | DCT | 13 |         |         |

| DCT | VDD  | DCT | G    | Т   | VDD3 | T   | G    | S | VDD  | S   | G     | VDD   | G    | S   | VDD  | S  | G    | T   | VDD5 | T   | G    | DCT | VDD  | DCT | 14 |         |         |

| DCT | S    | S   | S    | S   | S    | S   | S    | S | S    | VDD | S     | G     | S    | VDD | S    | S  | S    | S   | S    | S   | S    | s   | S    | DCT | 15 |         |         |

| S   | G    | S   | VDD  | S   | G    | S   | VDD3 | S | G    | s   | VDD   | S     | VDD  | s   | G    | S  | VDD5 | S   | G    | S   | VDD  | S   | G    | S   | 16 | V1=VDD  |         |

| S   | S    | S   | S    | S   | S    | S   | S    | S | S    | S   | S     | S     | S    | S   | S    | S  | S    | S   | S    | S   | S    | S   | S    | s   | 17 | V2=VDD2 |         |

| S   | VDD3 | S   | G    | S   | VDD  | S   | G    | S | VDD2 | S   | G     | DCT   | G    | S   | VDD2 | S  | G    | S   | VDD  | S   | G    | S   | VDD5 | S   | 18 | =VDD3   |         |

| T   | S    | T   | S    | S   | S    | S   | S    | S | S    | S   | T     | DCT   | T    | S   | S    | S  | S    | S   | S    | S   | S    | Т   | S    | T   | 19 | =VDD4   |         |

| S   | G    | S   | VDD3 | S   | G    | S   | VDD2 | S | G    | S   | VDD   | DCT   | VDD  | s   | G    | S  | VDD2 | S   | G    | S   | VDD5 | S   | G    | S   | 20 | =VDD5   |         |

| Т   | S    | T   | S    | Т   | S    | S   | S    | S | S    | S   | T     | DCT   | T    | S   | S    | S  | S    | S   | S    | T   | S    | T   | S    | T   | 21 |         |         |

| S   | VDD  | S   | G    | S   | VDD  | S   | G    | S | VDD2 | s   | G     | DCT   | G    | s   | VDD2 | S  | G    | S   | VDD  | S   | G    | s   | VDD  | S   | 22 | DCT=DC  | Test    |

| T   | S    | T   | S    | Т   | S    | T   | S    | S | S    | S   | DCT   | DCT   | DCT  | S   | S    | S  | S    | T   | S    | T   | S    | Т   | S    | T   | 23 | T=TST=A | C Test  |

| S   | G    | S   | VDD2 | S   | G    | S   | VDD  | S | G    | S   | VDD2  | DCT   | VDD  | S   | G    | S  | VDD  | S   | G    | S   | VDD2 | S   | G    | S   | 24 |         |         |

| S   | S    | T   | S    | Т   | S    | T   | S    | S | S    | DCT | DCT   | DCT   | DCT  | DCT | S    | S  | S    | T   | S    | T   | S    | T   | S    | S   | 25 | View    |         |

|     |      |     |      |     |      |     |      |   |      |     |       |       |      |     |      |    |      |     |      |     |      |     |      |     |    | /II/    |         |

|     |      |     |      |     |      |     |      |   |      |     |       |       |      | ļ   |      |    |      | ļ   |      |     |      |     |      |     |    |         | MLC     |

|     |      |     |      |     |      |     |      | B | SM - | 32X | :32 № | ana c | :BG/ | ത   | 1.27 | ли | PITC | :H  |      |     |      |     |      |     |    | 000000  | BSM Bal |

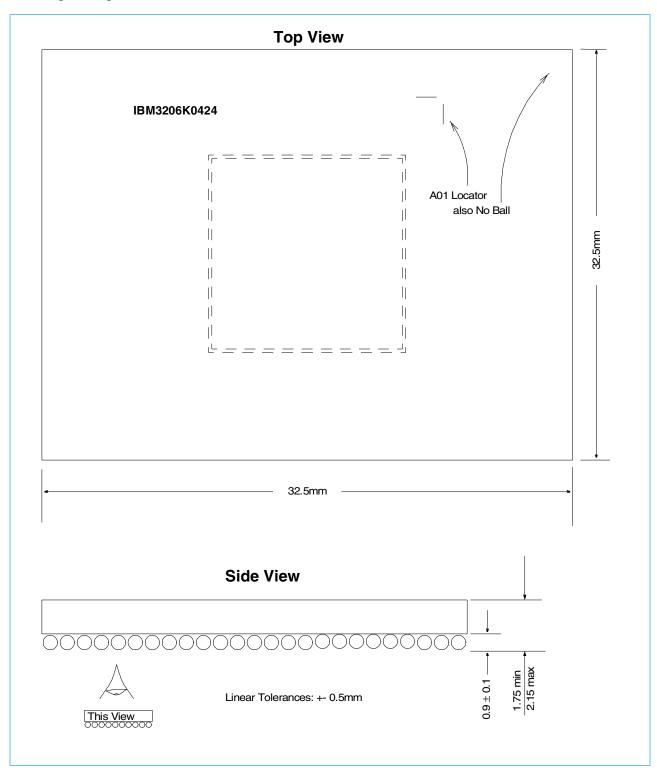

## **Dataflow**

## **Functional Description**

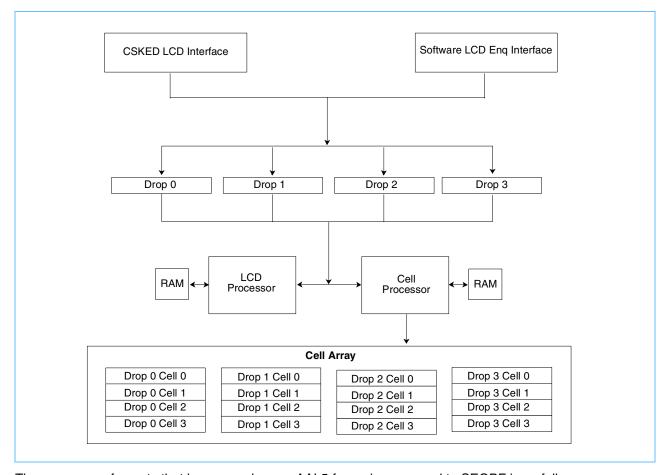

The IBM3206K0424 has been designed by breaking the implementation of the various functions and dataflows into separate entities (major functional units).

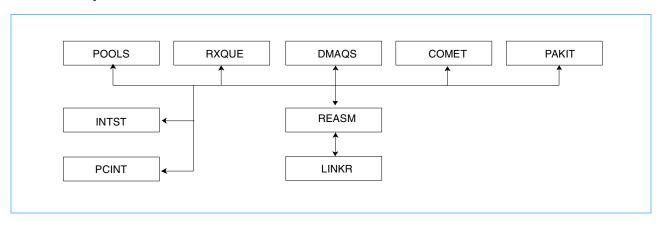

This processor acts as a conversion unit from a bus memory interface (which is Work Queue oriented) to a PHY level ATM. To accomplish this, the IBM3206K0424 contains the major functional units listed below and shown in the *Dataflow* on page 27.

### Control Processor Bus Interface

PCINT PCI Interface entity

INTST Interrupt Status entity

GPDMA General Purpose DMA entity

DMAQS Queue control for DMA activity

Memory Control

MEMRY DRAM controlling entity containing the COMET (Control) and PAKIT (Packet)

memory controllers

VIMEM Virtual Memory controller

ARBIT Memory subsystem requestor arbitration

BCACH Bus Cache entity

POOLS Memory Pool manager

Transmit Data Path

CSKED Cell Scheduler

SEGBF Cell Segmentation entity

Receive Data Path

REASM Cell Re-assembly entity

RAALL AAL processor

RXQUE Receive Queue manager

PHY Level Interfaces

LINKC Asynchronous Physical Layer interface

NPBUS Nodal Processor Bus interface

FRAMR Full SONET framing support logic

Hardware Protocol Assist

CHKSM TCP/IP Checksum Logic

PCORE Embedded 401 Processor Core

**Base Device Functions**

SCLCK System Clock Generation and Repowering entity

CRSET Hardware and Software Reset Controlling entity

CBIST Built-In Self Test logic entity

CJTAG JTAG Test Interface Logic entity

## **Subsystem Blocks**

**The IBM Processor for Network Resources** provides the host bus interfacing, memory management for buffers and control, cell segmentation and reassembly, and PHY hardware control for an ATM adapter.

**External Memory** consists of a number of SRAM modules, or two SDRAM arrays used for the storage of packet data and the control structures used by the IBM3206K0424. Both the Packet and Control Memory arrays consist of two 32-bit wide banks.

When running at 102Mb/s or slower (full duplex aggregate throughput), a single array of memory can be used. Both control and data store are contained in this single array of memory. For a detailed description of the external memory organization refer to *The DRAM Controllers (COMET/PAKIT)* on page 184.

**The PHY (Physical) Layer** interface connects to several available hardware support devices. This layer of hardware converts a parallel data stream into a serial data stream to be shipped to and from the PMD layer.

The PHY and PMD end of a card design can be implemented as one of several encoding schemes and speeds, supporting both copper and fibre optic serial links. The interface will support the ATM Forum "Utopia spec," the PMC chip, and a 25Mb/s serial interface to the IBM UTP solution. (See *Standards Compliance* on page 23 for documents which describe these interfaces.)

**The PMD (Physical Media Dependent) Layer** interface connects to the line drivers and receivers. This could be either a copper or a fibre optic transceiver.

### **External Architecture**

The IBM Processor for Network Resources has four major interfaces:

A System Bus which acts as an actively cached memory slave and as a master for the PCI 32-bit bus.

**The Physical (PHY) Interface** which supports several physical layer hardware devices that perform parallel to serial data conversion and the rest of the transmission convergence.

**An External DRAM Interface** that controls one or two arrays of two-bank interleaved DRAM with 60 ns access time for Packet and Control Memory. The interface is direct drive to the DRAM.

**The Control and Configuration Interface** which covers a number of functions. It gives access from the system bus to the PHYs and to EPROM. The EPROM can also be used to hold initial device configuration, up to and including PVC configurations.

Note: IBM3206K0424 has built-in, self-test logic.

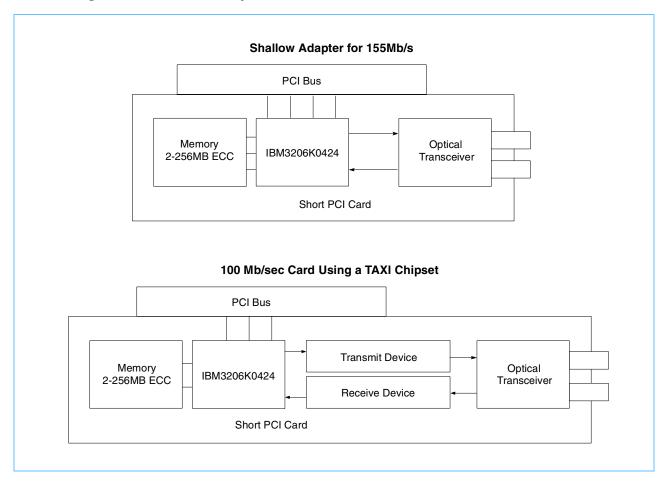

The four major interfaces allow the IBM Processor for Network Resources to be used in both "deep" and "shallow" adaptors with minimal external logic. (See *Block Diagrams of Possible Systems* on page 33 for examples.)

### **Internal Architecture**

## **Logical Channel Support**

The Logical Channel is the unit of resource allocation in ATM. At one level, the End Station negotiates with the Network Interface to determine the characteristics of each End Station-to-End Station connection. The resources that may be reserved in the network are defined in the ATM UNI (User Network Interface) Specification (see references in *Standards Compliance* on page 23). These resources include (but are not limited to) the peak and average bandwidth to be used by the logical channel, the maximum burst length that may be transmitted at the burst rate, the latency and variance of the connection, and the loss probability.

The term Logical Channel rather than virtual circuit or VPI/VCI is used in this databook to provide a level of abstraction from these specific instances.

A Switched Virtual Circuit (SVC) can be negotiated with specific characteristics specifically for it.

A virtual path can be negotiated with the network. Several virtual circuits within that path can then be multiplexed, using the VCI on that single VPI, without having to renegotiate for each additional VCI. The Logical channel, with respect to the network, would be the Virtual Path. There would be multiple logical channels internal to the End Station based on the Virtual Circuits used within the path.

Using ATM Adaptation Layers 3 and 4, a Multiplexing IDentifier (MID) can be used to provide multiple Logical Channels across a single VPI/VCI.

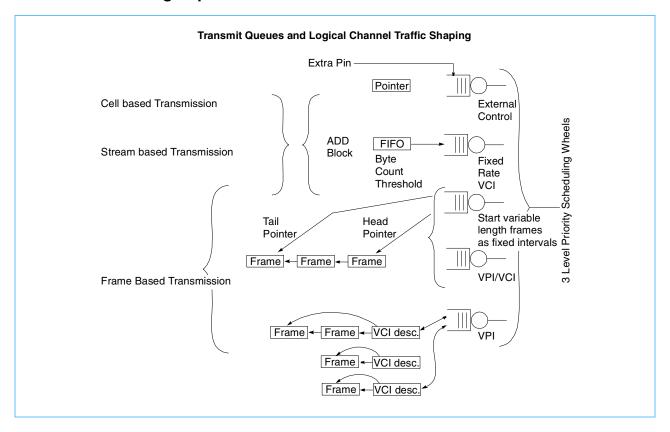

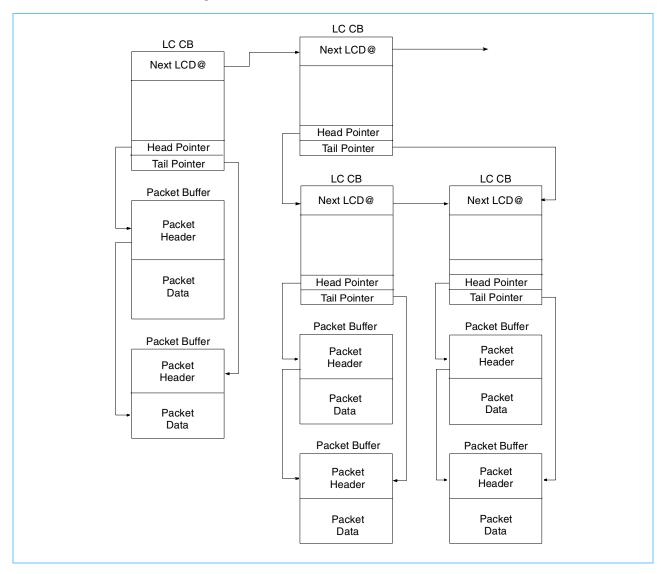

All of these Logical Channels are dealt with uniformly in IBM3206K0424. A hierarchy of Logical Channel Descriptors can be built up, and frames or buffers can be queued to each of the LCDs. See *Transmit Buffer (CSKED)* on page 273 for details.

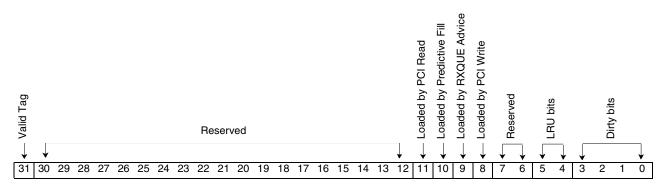

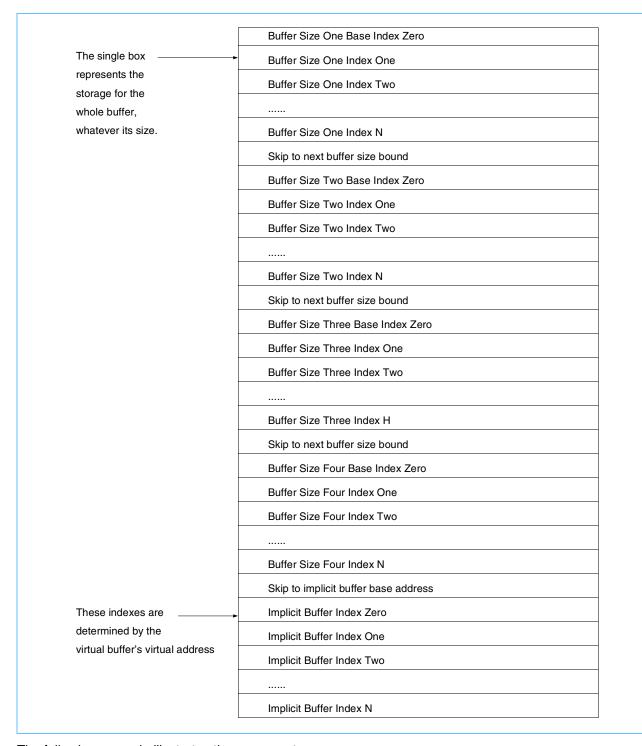

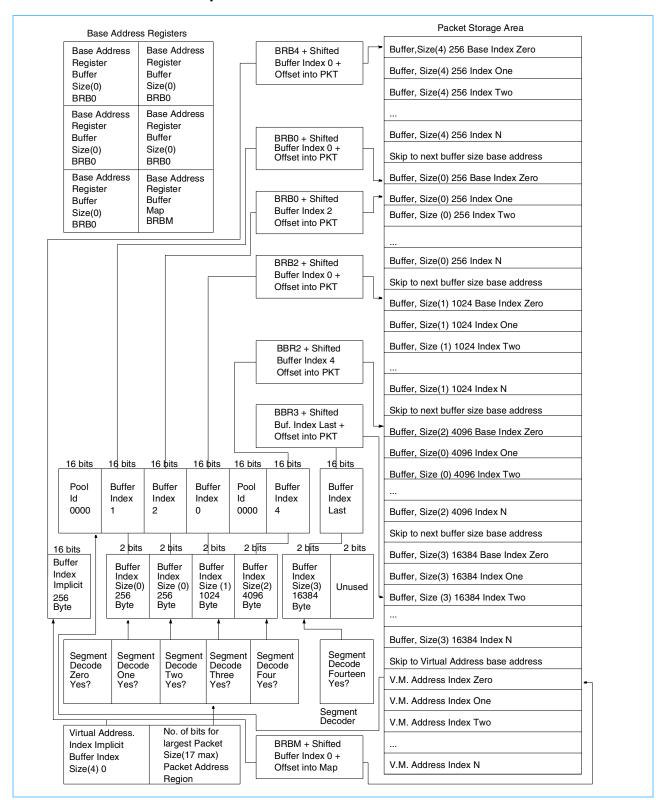

### **Virtual Memory Support**

The Packet Memory space appears on the bus as a group of *up to* 128K buffers (configurable size). A level of indirection has been added to the addressing of Packet memory to provide these large frame buffers without requiring memory behind all of them at the same time. This has been done for a number of reasons:

- The frames on the network can be up to 64KB long.

- The receiver does not know how long a frame will be until it is completely received.

- Software generally has a much easier time dealing with contiguous memory.

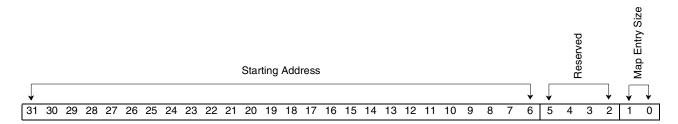

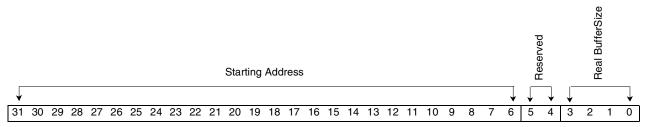

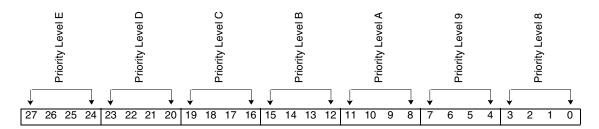

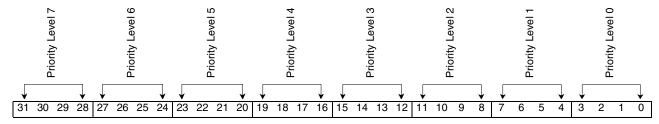

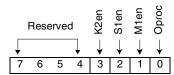

The memory does not page or swap. There are two major efficiencies used internally: