Click here to ask an associate for production status of specific part numbers.

#### MAX22515

## **IO-Link Transceiver with Integrated Protection**

### **General Description**

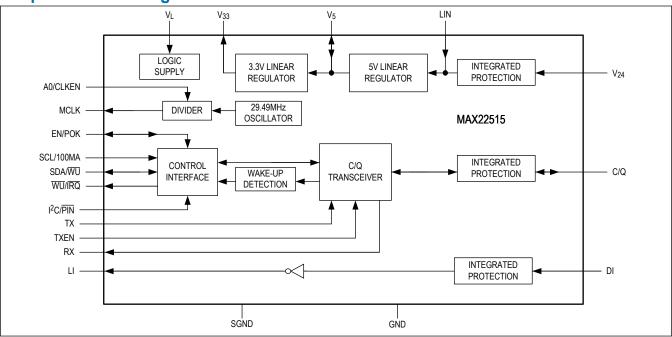

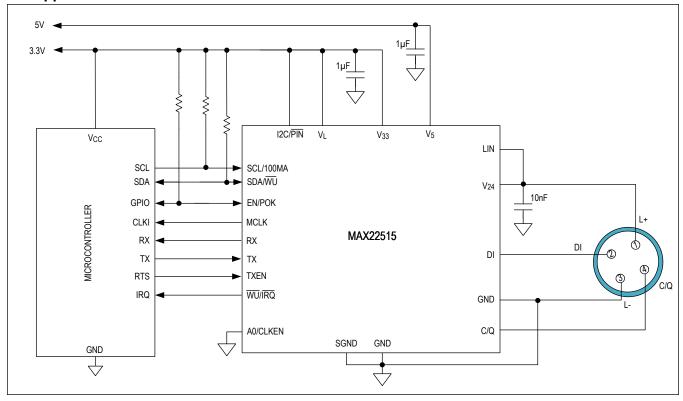

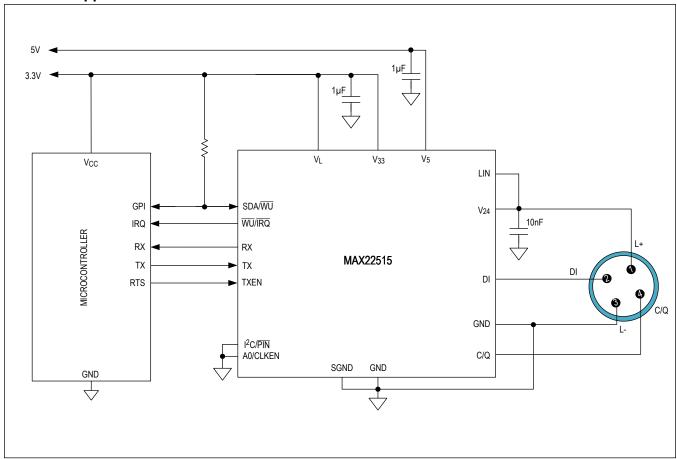

The MAX22515 low-power industrial transceiver can operate as either an IO-Link device or an IO-Link master transceiver in industrial applications. The MAX22515 features a selectable control interface (pin mode or I<sup>2</sup>C), two integrated linear regulators, and integrated surge protection for robust communication. The transceiver includes one C/Q input-output channel and one digital input (DI) channel.

The device features a flexible control interface. Pin-control logic inputs allow for operation with switching sensors that do not use a microcontroller. For sensors that use a microcontroller, an I<sup>2</sup>C interface is available providing extensive configuration and diagnostics. Additionally, an integrated oscillator simplifies the clock generation for IO-Link devices.

The MAX22515 features extensive integrated protection to ensure robust communication in harsh industrial environments. All IO-Link line interface pins (V<sub>24</sub>, C/Q, DI, and GND) are reverse voltage protected, short-circuit protected, hot-plug protected, and feature integrated  $\pm 1.2 \text{kV}/500\Omega$  surge protection.

The MAX22515 is available in a tiny WLP package (2.5mm x 2.0mm) or a 24-pin TQFN-EP package (4mm x 4mm) and operates over the -40°C to +125°C temperature range.

## **Applications**

- IO-Link Sensor and Actuator Devices

- Industrial Sensors

- IO-Link Masters

#### **Benefits and Features**

- High Configurability and Integration Reduces SKU

- · Operates from 8V to 36V

- Auxiliary Digital Input (DI)

- I<sup>2</sup>C or Pin Mode Control

- Selectable C/Q Driver Current: 50mA to 250mA

- Selectable C/Q Driver Slew Rate (I<sup>2</sup>C Mode)

- Integrated Oscillator for IO-Link Communication

- · IO-Link Wake-Up Detection and Wake-Up

- Generation

- Integrated Linear Regulators: 3.3V and 5V

- Compatible Register Set to MAX22513

- Able to Communicate at COM1, COM2, and COM3 Data Rates

- Integrated Protection Enables Robust Systems

- ±1.2kV/500Ω Surge Protection on V<sub>24</sub>, C/Q, DI, and GND

- Reverse Polarity Protection on V<sub>24</sub>, C/Q, DI, and GND

- Hot-Plug Protection on Supply Input (V<sub>24</sub>)

- · Glitch Filters for Improved Burst Resilience

- · Selectable Driver Overcurrent Configuration

- -40°C to +125°C Operating Temperature Range

- Fast Demagnetization of Inductive Loads

- Optimized for Small Designs

- Low Power Dissipation:  $2\Omega$  (typ) C/Q Driver On-Resistance

- 1.3mA (typ) Supply Current

- · Available in Two Tiny Packages:

- 20-Bump WLP (2.5mm x 2.0mm)

- 24-Pin TQFN-EP (4mm x 4mm)

# **Simplified Block Diagram**

## **Absolute Maximum Ratings**

| All voltages referenced to GND, unless otherwise noted                            | MCLK, RX, LI0.3V to (V <sub>L</sub> +0.3)V                        |

|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|

| V <sub>24</sub> (Continuous)36V to +36V                                           | SGND0.3V to +0.3V                                                 |

| V <sub>24</sub> (Peak, 100µs)52V to +65V                                          | Continuous Current into V <sub>24</sub> and GND±1A                |

| LIN (LIN is connected to V <sub>24</sub> , Continuous)36V to +36V                 | Continuous Current into LIN±100mA                                 |

| LIN (LIN is connected to V <sub>24</sub> , Peak)52V to +65V                       | Continuous Current into C/Q±500mA                                 |

| LIN max(-0.3V, V <sub>5</sub> - 0.3V) to V <sub>24</sub>                          | Continuous Current into V <sub>5</sub> and V <sub>33</sub> ±60mA  |

| C/Q (Continuous) max(-36V, V <sub>24</sub> - 36V) to min(+36V, (V <sub>24</sub> + | Continuous Current into Any Other Pin±50mA                        |

| 36V)                                                                              | Continuous Power Dissipation 24-Pin TQFN (T <sub>A</sub> = +70°C) |

| C/Q (Peak, 100µs)max(-52V, V <sub>24</sub> - 52V) to min (+52V, V <sub>24</sub> + | (derate at 27.8mW/°C above +70°C)2222mW                           |

| 52V)                                                                              | 20-bump WLP ( $T_A = +70$ °C)                                     |

| DI (Continuous)36V to +36V                                                        | (derate at 21.35mW°/C above +70°C)1700mW                          |

| DI (Peak, 100μs)52V to +52V                                                       | Operating Temperature Range40°C to +125°C                         |

| V <sub>5</sub> , V <sub>L</sub> 0.3V to +6V                                       | Maximum Junction Temperature+160°C                                |

| V <sub>33</sub> 0.3V to (V <sub>5</sub> + 0.3V)                                   | Storage Temperature Range65°C to +150°C                           |

| LOGIC PINS                                                                        | Soldering Temperature (TQFN only, 10 sec)+300°C                   |

| I <sup>2</sup> C/PIN, EN/POK, CLKEN, SCL/100MA,                                   | Bump Reflow Temperature+260°C                                     |

| SDA/WU, WU/IRQ, TXEN, TX0.3V to +6V                                               |                                                                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Package Information**

#### 24 TQFN-EP

| Package Code                                           | T2444+4 |  |  |  |  |

|--------------------------------------------------------|---------|--|--|--|--|

| Outline Number                                         | 21-0139 |  |  |  |  |

| Land Pattern Number                                    | 90-0022 |  |  |  |  |

| THERMAL RESISTANCE, SINGLE-LAYER BOARD                 |         |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 48°C/W  |  |  |  |  |

| Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )  |         |  |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD                   |         |  |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> )                 | 36°C/W  |  |  |  |  |

| Junction-to-Case Thermal Resistance (θ <sub>JC</sub> ) | 3°C/W   |  |  |  |  |

### 20 (5 x 4) WLP

| Package Code                           | W201L2+1                       |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Outline Number                         | <u>21-100314</u>               |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                |  |  |  |

| Junction-to-Ambient (θ <sub>JA</sub> ) | 46.83°C/W                      |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

### **Electrical Characteristics—DC**

$(V_{24}$  = 8V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V, All logic inputs at  $V_L$  or GND,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                                       | SYMBOL                                      | COND                                                                                                              | ITIONS                                                                                                | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|------|------|------|-------|

| DC ELECTRICAL CHAR                                              | ACTERISTICS / I                             | POWER SUPPLY                                                                                                      |                                                                                                       |      |      |      | '     |

| V <sub>24</sub> Supply Voltage                                  | V <sub>24</sub>                             |                                                                                                                   |                                                                                                       | 8    |      | 36   | V     |

| V <sub>24</sub> Undervoltage                                    |                                             | V <sub>24</sub> rising                                                                                            |                                                                                                       | 6.9  | 7.5  | 8    |       |

| Lockout Threshold                                               | V <sub>24UVLO</sub>                         | V <sub>24</sub> falling                                                                                           |                                                                                                       | 6.4  | 6.9  | 7.5  | \ \ \ |

| V <sub>24</sub> Undervoltage<br>Lockout Threshold<br>Hysteresis | V <sub>24</sub> UVLO_HYS                    |                                                                                                                   |                                                                                                       |      | 500  |      | mV    |

| V <sub>24</sub> Low Voltage<br>Warning Threshold                | V <sub>24_W</sub>                           | V <sub>24</sub> falling                                                                                           |                                                                                                       | 14.5 | 15.3 | 16.3 | V     |

| V Supply Current                                                |                                             | V <sub>5</sub> powered                                                                                            | C/Q is high impedance                                                                                 |      | 16   | 30   |       |

| V <sub>24</sub> Supply Current                                  | l <sub>24</sub>                             | externally, no load<br>on C/Q                                                                                     | C/Q is in push-pull and is high or low                                                                |      | 285  | 400  | μA    |

| V <sub>5</sub> Supply Voltage                                   | V <sub>5</sub>                              | LIN = V <sub>5</sub> , V <sub>5</sub> supplie                                                                     | d externally                                                                                          | 4.5  |      | 5.5  | V     |

| V <sub>5</sub> Undervoltage                                     | \/                                          | V <sub>5</sub> rising                                                                                             |                                                                                                       |      |      | 3.5  | V     |

| Lockout Threshold                                               | V <sub>5UVLO</sub>                          | V <sub>5</sub> falling                                                                                            |                                                                                                       | 3    |      |      | ]     |

|                                                                 |                                             | LIN = V <sub>5</sub> , V <sub>5</sub> is<br>powered externally,<br>no load on V <sub>33</sub> , no<br>load on C/Q | C/Q is high<br>impedance, V <sub>33</sub> is<br>disabled, MCLK is<br>disabled                         |      | 560  | 850  | μА    |

| V <sub>5</sub> Supply Current                                   | 15                                          | I <sub>5</sub> LIN = V <sub>5</sub> , V <sub>5</sub> is                                                           | C/Q is in push-pull<br>mode and is high<br>or low, V <sub>33</sub> is<br>enabled, MCLK is<br>disabled |      | 1.08 | 1.5  |       |

|                                                                 | no load on V <sub>33</sub> , no load on C/Q | C/Q is in push-pull<br>mode and is high<br>or low, V <sub>33</sub> is<br>enabled, MCLK is<br>enabled              |                                                                                                       | 1.5  | 2.2  | – mA |       |

| V <sub>L</sub> Logic Level Supply<br>Voltage                    | VL                                          |                                                                                                                   |                                                                                                       | 2.5  |      | 5.5  | V     |

| V <sub>L</sub> Undervoltage<br>Threshold                        | V <sub>LUVLO</sub>                          | V <sub>L</sub> rising                                                                                             |                                                                                                       | 0.5  | 0.85 | 1.2  | V     |

|                                                                 |                                             |                                                                                                                   | MCLK disabled                                                                                         |      | 1    | 10   |       |

| V <sub>L</sub> Logic Level Supply                               |                                             | All logic inputs at                                                                                               | MCLK enabled, f = 29.49MHz                                                                            |      | 800  |      | μA    |

| Current                                                         | I <sub>VL</sub>                             | GND or V <sub>L</sub> , no load<br>on any logic output                                                            | MCLK enabled,<br>10pF load on<br>MCLK, V <sub>L</sub> = 3.3V, f<br>= 29.49MHz                         |      | 1.56 |      | mA    |

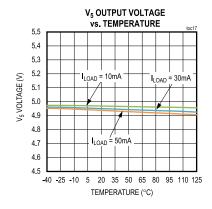

| DC ELECTRICAL CHAR                                              | ACTERISTICS /                               | V LINEAR REGULA                                                                                                   | TOR (V <sub>5</sub> )                                                                                 |      |      |      |       |

| V <sub>5</sub> Input Supply Voltage                             | V <sub>LIN</sub>                            |                                                                                                                   |                                                                                                       | 8    |      | 36   | V     |

| V <sub>5</sub> Output Voltage                                   | V <sub>5</sub>                              | 8V ≤ V <sub>LIN</sub> ≤ 36V, no                                                                                   | load on V <sub>5</sub>                                                                                | 4.9  | 5    | 5.1  | V     |

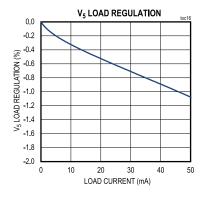

| V <sub>5</sub> Load Regulation                                  | ΔV <sub>5 LDR</sub>                         | V <sub>LIN</sub> = 24V, 1mA ≤ I                                                                                   | LOAD ≤ 50mA                                                                                           |      | 0.8  | 2    | %     |

Analog Devices | 4 www.analog.com

# **Electrical Characteristics—DC (continued)**

$(V_{24}$  = 8V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V, All logic inputs at  $V_L$  or GND,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                             | SYMBOL                  | CON                                                                                                                  | DITIONS                                                                                                       | MIN                 | TYP   | MAX  | UNITS                |

|-------------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------|-------|------|----------------------|

| V <sub>5</sub> Line Regulation                        | $\Delta V_{5\_LNR}$     | 8V ≤ V <sub>LIN</sub> ≤ 36V, I <sub>L</sub>                                                                          | <sub>-OAD</sub> = 1mA                                                                                         |                     | 0.007 | 0.3  | mV/V                 |

| V <sub>5</sub> Power Supply<br>Rejection Ratio (PSRR) | PSRR <sub>V5</sub>      | f = 100kHz, I <sub>LOAD</sub>                                                                                        | = 20mA                                                                                                        |                     | -65   |      | dB                   |

| V <sub>5</sub> Load Capacitance                       | C <sub>V5</sub>         | External capacitano                                                                                                  | ce required on V <sub>5</sub>                                                                                 | 0.8                 | 1     |      | μF                   |

| DC ELECTRICAL CHARA                                   | ACTERISTICS /           | 3.3V LINEAR REGU                                                                                                     | LATOR (V <sub>33</sub> )                                                                                      |                     |       |      |                      |

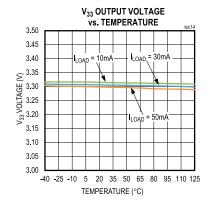

| V <sub>33</sub> Output Voltage                        | V <sub>33</sub>         | No load                                                                                                              |                                                                                                               | 3.22                | 3.32  | 3.42 | V                    |

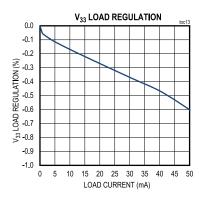

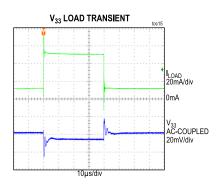

| V <sub>33</sub> Load Regulation                       | $\Delta V_{33\_LR}$     | 1mA ≤ I <sub>LOAD</sub> ≤ 50n                                                                                        | nA                                                                                                            |                     | 0.1   | 0.8  | %                    |

| V <sub>33</sub> Load Capacitance                      | C <sub>V33</sub>        | External capacitano                                                                                                  | ce required on V <sub>33</sub>                                                                                | 0.8                 | 1     |      | μF                   |

| DC ELECTRICAL CHARA                                   | ACTERISTICS /           | C/Q DRIVER                                                                                                           |                                                                                                               |                     |       |      |                      |

| C/Q Driver On-                                        | R <sub>OH</sub>         | High-side enabled, -200mA (Note 3)                                                                                   | CL[1:0] = 11, I <sub>LOAD</sub> =                                                                             |                     | 2.65  | 4.6  | Ω                    |

| Resistance                                            | R <sub>OL</sub>         | Low-side enabled,<br>+200mA (Note 3)                                                                                 | CL[1:0] = 11, I <sub>LOAD</sub> =                                                                             |                     | 2.2   | 4.2  |                      |

|                                                       |                         |                                                                                                                      | CL[1:0] = 00                                                                                                  | 50                  | 66    | 80   |                      |

| C/O Driver Current Limit                              | : Limit I <sub>CL</sub> | V <sub>DROP</sub> = 3V                                                                                               | CL[1:0] = 01<br>(I <sup>2</sup> C mode) or SDA/<br>100MA = high (pin<br>mode)                                 | 100                 | 120   | 140  | mA                   |

| C/Q Driver Current Limit                              |                         | (Note 4)                                                                                                             | CL[1:0] = 10<br>( <sup>12</sup> C mode) or SDA/<br>100MA = low (pin<br>mode)                                  | 210                 | 240   | 270  | - mA                 |

|                                                       |                         |                                                                                                                      | CL[1:0] =                                                                                                     | CL[1:0] = 11        | 260   | 300  | 340                  |

| C/Q Leakage Current                                   | I <sub>LEAK_CQ</sub>    | $I^2$ C mode only, $V_{24}$<br>$V_{C/Q} \le 36V$ ,<br>C/Q driver and rece<br>$(CQ\_EN = 0, RXDI)$                    |                                                                                                               | -40                 |       | +30  | μА                   |

|                                                       |                         | C/Q driver disabled 24V, $0 \le V_{C/Q} \le (V_{C})$                                                                 | I (CQ_EN = 0), V <sub>24</sub> =<br><sub>24</sub> - 0.5V)                                                     | -2                  |       | +2   |                      |

| C/Q Output Reverse<br>Current                         | I <sub>REV_CQ</sub>     | EN = 1) and in pusl                                                                                                  | C/Q driver enabled (TXEN = high, CQ_<br>EN = 1) and in push-pull<br>(CQ_PP = 1), $V_{C/Q} = (V_{24} + 5V)$ or |                     |       | +300 | μА                   |

| C/Q Weak Pulldown<br>Current                          | I <sub>PD</sub>         | I <sup>2</sup> C mode only, V <sub>C/Q</sub> > 5V, TXEN = low,<br>CQ_EN = 1, CQ_PD = 1, CQ_PU = 0<br>(Note 5)        |                                                                                                               | +230                | +320  | +400 | μΑ                   |

| C/Q Weak Pullup<br>Current                            | I <sub>PU</sub>         | I <sup>2</sup> C mode only,V <sub>C/Q</sub> = (V24 - 5V), TXEN<br>= low, CQ_EN = 1, CQ_PD = 0, CQ_PU<br>= 1 (Note 5) |                                                                                                               | -400                | -300  | -230 | μА                   |

| DC ELECTRICAL CHARA                                   | ACTERISTICS /           | C/Q, DI RECEIVER                                                                                                     |                                                                                                               |                     |       |      |                      |

| Input Voltage Range                                   | V <sub>IN</sub>         | For valid RX/LI logi                                                                                                 | С                                                                                                             | V <sub>24</sub> -36 |       | 36   | V                    |

| Input Threshold High                                  | V                       | TXEN = low                                                                                                           | V <sub>24</sub> ≥ 18V                                                                                         | 10.8                |       | 12.5 | V                    |

| input miconolu mign                                   | V <sub>TH</sub> TXI     | IALIN - IUW                                                                                                          | V <sub>24</sub> < 18V                                                                                         | 57.5                |       | 72   | % of V <sub>24</sub> |

# **Electrical Characteristics—DC (continued)**

$(V_{24}$  = 8V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V, All logic inputs at  $V_L$  or GND,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                       | SYMBOL                  | CON                                                             | IDITIONS                                                  | MIN                  | TYP                    | MAX                  | UNITS                |

|-------------------------------------------------|-------------------------|-----------------------------------------------------------------|-----------------------------------------------------------|----------------------|------------------------|----------------------|----------------------|

| Input Throshold Low                             | \/                      | TXEN = low                                                      | V <sub>24</sub> ≥ 18V                                     | 8.8                  |                        | 10.5                 | V                    |

| Input Threshold Low                             | $V_{TL}$                | I XEIN = IOW                                                    | V <sub>24</sub> < 18V                                     | 45                   |                        | 63                   | % of V <sub>24</sub> |

| Innut I luctorosio                              | V                       | TVEN - low                                                      | V <sub>24</sub> ≥ 18V                                     |                      | 2                      |                      | V                    |

| Input Hysteresis                                | V <sub>HYS</sub>        | TXEN = low                                                      | V <sub>24</sub> < 18V                                     |                      | 11                     |                      | % of V <sub>24</sub> |

| C/Q Input Capacitance                           | C <sub>IN_CQ</sub>      | Driver disabled, CO<br>CQ_PD = 0, CQ_F<br>f = 100kHz            | Q_EN = 0, RXDIS = 0,<br>PU = 0,                           |                      | 45                     |                      | pF                   |

| DI Input Capacitance                            | C <sub>IN_DI</sub>      | DIDIS = 0, LIDIS =                                              | 0, f = 100kHz                                             |                      | 4                      |                      | pF                   |

| DI Input Current                                | I <sub>DI_IN</sub>      | V <sub>24</sub> = 24V, DI rece<br>36V) ≤ V <sub>DI</sub> ≤ 36V  | eiver enabled, (V <sub>24</sub> -                         | -10                  |                        | +15                  | μA                   |

| DC ELECTRICAL CHAR                              | ACTERISTICS /           | LOGIC INPUTS (A0                                                | /CLKEN, SCL/100MA, S                                      | DA/WU, TX            | EN, TX, I <sup>2</sup> | C/PIN, EN/           | POK)                 |

| Logic Input Voltage Low                         | V <sub>IL</sub>         |                                                                 |                                                           |                      |                        | 0.2 x V <sub>L</sub> | V                    |

| Logic Input Voltage High                        | V <sub>IH</sub>         |                                                                 |                                                           | 0.7 x V <sub>L</sub> |                        |                      | V                    |

| Logic Input Leakage<br>Current                  | I <sub>LEAK</sub>       | A0/CLKEN, SC <u>L/1</u><br>TXEN, TX, I <sup>2</sup> C/PIN<br>VL | 00MA, SDA/WU,<br>, Logic input = GND or                   | -1                   |                        | +1                   | μA                   |

| EN/POK Input Pullup<br>Resistance               | R <sub>PU</sub>         | EN/POK                                                          |                                                           | 60                   | 100                    | 140                  | kΩ                   |

| DC ELECTRICAL CHAR                              | ACTERISTICS /           | LOGIC OUTPUTS (                                                 | WU/IRQ, MCLK, SDA/W                                       | U, RX, LI)           |                        |                      |                      |

| Logic Output Voltage<br>Low                     | V <sub>OL</sub>         | LI, RX, MCLK, SDA                                               | A/WU, I <sub>LOAD</sub> = +5mA                            |                      |                        | 0.15                 | V                    |

| Logic Output Voltage<br>High                    | V <sub>OH</sub>         | LI, RX, MCLK, I <sub>LO</sub> ,                                 | <sub>AD</sub> = -5mA                                      | V <sub>L</sub> - 0.2 |                        |                      | V                    |

| Open-Drain High<br>Impedance Leakage<br>Current | I <sub>LK_OD</sub>      | WU/IRQ, output no                                               | ot asserted                                               | -1                   |                        | +1                   | μА                   |

| Logic Output Leakage<br>Current                 | I <sub>LKG_OUT</sub>    |                                                                 | DIS = 1, RXDIS = 1,<br>gic output = GND or V <sub>L</sub> | -1                   |                        | +1                   | μA                   |

| SDA/WU Leakage<br>Current                       | I <sub>LK_SDA</sub>     |                                                                 |                                                           | -1                   |                        | +1                   | μA                   |

| DC ELECTRICAL CHAR                              | ACTERISTICS /           | THERMAL MANAG                                                   | EMENT                                                     |                      |                        |                      |                      |

| C/Q Driver Shutdown<br>Temperature              | T <sub>SHUT_D</sub>     | Driver temperature bit is set and driver                        | e rising, C/Q driver fault<br>r is disabled               |                      | +150                   |                      | °C                   |

| C/Q Driver Shutdown<br>Hysteresis               | T <sub>SHUT_DHYS</sub>  | Driver temperature automatically reena                          | falling, C/Q driver is abled                              |                      | 10                     |                      | °C                   |

| IC Thermal Warning<br>Threshold                 | T <sub>WRN</sub>        | Die temperature ris<br>THERMWINT bits                           | sing, THERMW and are set                                  |                      | +140                   |                      | °C                   |

| IC Thermal Warning<br>Threshold Hysteresis      | T <sub>WRN_HYS</sub>    | Die temperature fa cleared                                      | lling, THERMW bit is                                      |                      | 15                     |                      | °C                   |

| IC Junction Thermal<br>Shutdown Threshold       | T <sub>SHUT_IC</sub>    | Die temperature ris                                             | sing                                                      |                      | +160                   |                      | °C                   |

| IC Junction Thermal<br>Shutdown Hysteresis      | T <sub>SHUT_ICHYS</sub> | Die temperature fa                                              | lling                                                     |                      | 15                     |                      | °C                   |

### **Electrical Characteristics—AC**

$(V_{24}$  = 8V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V, All logic inputs at  $V_L$  or GND,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                   | SYMBOL                                                           | COND                                                                                       | ITIONS                                                             | MIN   | TYP  | MAX   | UNITS |

|---------------------------------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-------|------|-------|-------|

| AC ELECTRICAL CHARA                         | ACTERISTICS /                                                    | C/Q DRIVER                                                                                 |                                                                    |       |      |       | '     |

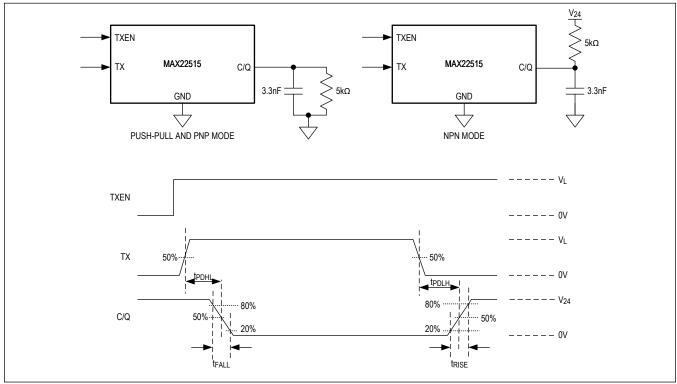

| C/Q Driver Low-to-High<br>Propagation Delay | t <sub>PDLH_PP</sub>                                             | CQSLEW[1:0] =                                                                              | Push-pull or PNP mode                                              |       | 0.5  | 0.75  | μs    |

| Propagation Delay                           | t <sub>PDLH_OC</sub>                                             | - 00, <u>Figure 1</u>                                                                      | NPN mode                                                           |       | 1    |       |       |

| C/Q Driver High-to-Low<br>Propagation Delay | t <sub>PDHL_PP</sub>                                             | CQSLEW[1:0] = 00, Figure 1                                                                 | Push-pull or NPN mode                                              |       | 0.45 | 0.75  | μs    |

| Propagation Delay                           | t <sub>PDHL_OC</sub>                                             | - 00, <u>Figure 1</u>                                                                      | PNP mode                                                           |       | 1    |       |       |

| C/Q Driver Skew                             | tskew                                                            | t <sub>PDLH</sub> - t <sub>PDHL</sub>  , CQ                                                | SLEW[1:0] = 00                                                     | -0.25 | 0.05 | +0.25 | μs    |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 00                                                   | 0.05  | 0.15 | 0.3   |       |

| C/Q Driver Rise Time                        | t <sub>RISE</sub>                                                | Push-pull or PNP<br>mode,<br>V <sub>24</sub> (max) = 30V,                                  | CQSLEW[1:0] = 01<br>(I <sup>2</sup> C mode) or<br>when in pin mode | 0     | 0.3  | 0.84  | μs    |

|                                             |                                                                  | Figure 1                                                                                   | CQSLEW[1:0] = 10                                                   | 0.45  | 0.9  | 1.4   |       |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 11                                                   | 1.5   | 3.3  | 6     |       |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 00                                                   | 0.05  | 0.16 | 0.3   |       |

| C/Q Driver Fall Time                        | $t_{FALL}$ Push-pull or NPN mode, $V_{24}(max) = 30V$ , Figure 1 | CQSLEW[1:0] = 01<br>(I <sup>2</sup> C mode) or<br>when in pin mode                         | 0.15                                                               | 0.33  | 0.5  | μs    |       |

|                                             |                                                                  | CQSLEW[1:0] = 10                                                                           | 0.45                                                               | 0.8   | 1.3  |       |       |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 11                                                   | 1.5   | 3.3  | 6     | 1     |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 00                                                   |       | 0.01 |       |       |

| Difference in C/Q Rise and Fall Time        |                                                                  | t <sub>RISE</sub> - t <sub>FALL</sub>  ,<br>Push-pull mode,<br>V <sub>24</sub> (max) = 30V | CQSLEW[1:0] = 01<br>(I <sup>2</sup> C mode) or<br>when in pin mode |       | 0.03 |       | μs    |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 10                                                   |       | 0.1  |       | 1     |

|                                             |                                                                  |                                                                                            | CQSLEW[1:0] = 11                                                   |       | 0    |       | 1     |

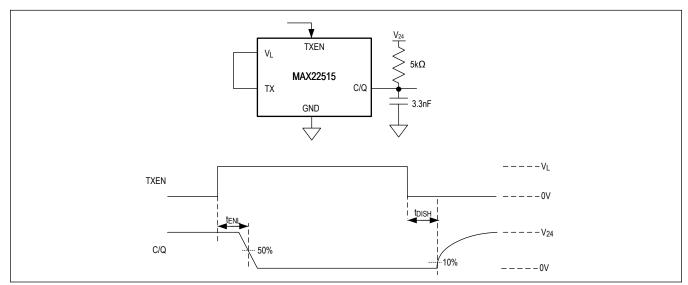

| C/Q Driver Enable Time<br>High              | t <sub>ENH</sub>                                                 | Push-pull or NPN co                                                                        | onfiguration, <u>Figure 2</u>                                      |       | 0.5  | 0.75  | μs    |

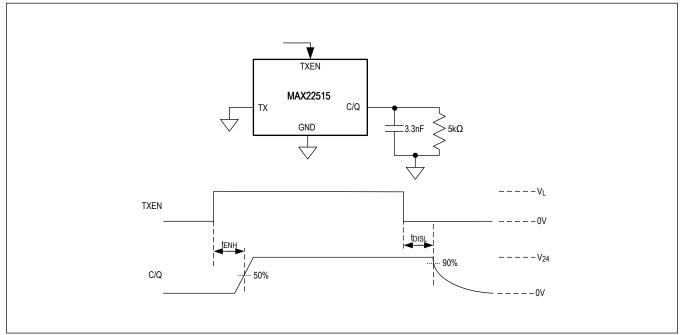

| C/Q Driver Enable Time<br>Low               | t <sub>ENL</sub>                                                 | Push-pull or PNP co                                                                        | onfiguration, Figure 3                                             |       | 0.2  | 0.4   | μs    |

| C/Q Driver Disable Time<br>High             | <sup>t</sup> DISH                                                | Push-pull or NPN co                                                                        | onfiguration, <u>Figure 2</u>                                      |       | 1.8  |       | μs    |

| C/Q Driver Disable Time<br>Low              | t <sub>DISL</sub>                                                | Push-pull or PNP co                                                                        | onfiguration, Figure 3                                             |       | 1.8  |       | μs    |

| AC ELECTRICAL CHARA                         | ACTERISTICS /                                                    | C/Q, DI RECEIVER                                                                           |                                                                    |       |      |       |       |

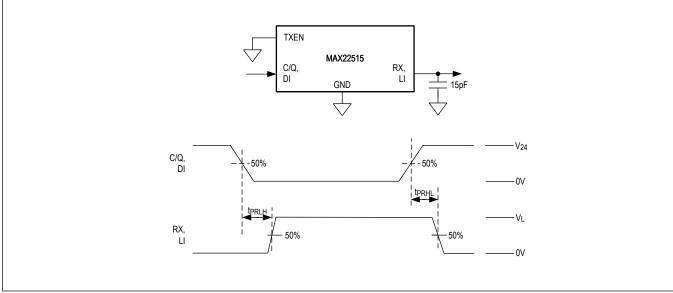

| C/Q Receiver Low-to-                        | topuu oo                                                         | Figure 4                                                                                   | RXFILTER = 1                                                       | 0.85  | 1.35 | 1.8   | 116   |

| High Propagation Delay                      | <sup>t</sup> PRLH_CQ                                             | i iguie <del>i</del>                                                                       | RXFILTER = 0                                                       | 0.25  | 0.38 | 0.55  | μs    |

| C/Q Receiver High-to-                       | topu" aa                                                         | Figure 4                                                                                   | RXFILTER = 1                                                       | 0.85  | 1.28 | 1.8   | lie.  |

| Low Propagation Delay                       | tprhl_cq                                                         | riguie 4                                                                                   | RXFILTER = 0                                                       | 0.2   | 0.3  | 0.5   | μs    |

| C/Q Receiver Skew                           |                                                                  | RXFILTER = 1                                                                               |                                                                    |       | 70   |       | ns    |

| OIG VECEIVE! SVEW                           |                                                                  | RXFILTER = 0                                                                               |                                                                    |       | 70   |       |       |

Analog Devices | 7 www.analog.com

# **Electrical Characteristics—AC (continued)**

$(V_{24}$  = 8V to 36V,  $V_5$  = 4.5V to 5.5V,  $V_L$  = 2.5V to 5.5V, All logic inputs at  $V_L$  or GND,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $V_{24}$  = 24V,  $V_5$  = 5V,  $V_L$  = 3.3V, and  $T_A$  = +25°C, unless otherwise noted.) (Notes 1, 2)

| PARAMETER                                                               | SYMBOL                | CON                                      | IDITIONS                           | MIN       | TYP   | MAX   | UNITS |

|-------------------------------------------------------------------------|-----------------------|------------------------------------------|------------------------------------|-----------|-------|-------|-------|

| DI Receiver Low-to-High                                                 |                       | Figure 4                                 | DIFILTER = 1                       | 1.2       | 1.8   | 2.4   |       |

| Propagation Delay                                                       | <sup>t</sup> PRLH_DI  | Figure 4                                 | DIFILTER = 0                       | 0.6       | 0.9   | 1.2   | μs    |

| DI Receiver High-to-Low                                                 |                       | Fig. 4                                   | DIFILTER = 1                       | 1.2       | 1.7   | 2.4   |       |

| Propagation Delay                                                       | <sup>t</sup> PRHL_DI  | Figure 4                                 | DIFILTER = 0                       | 0.5       | 0.75  | 1.1   | μs    |

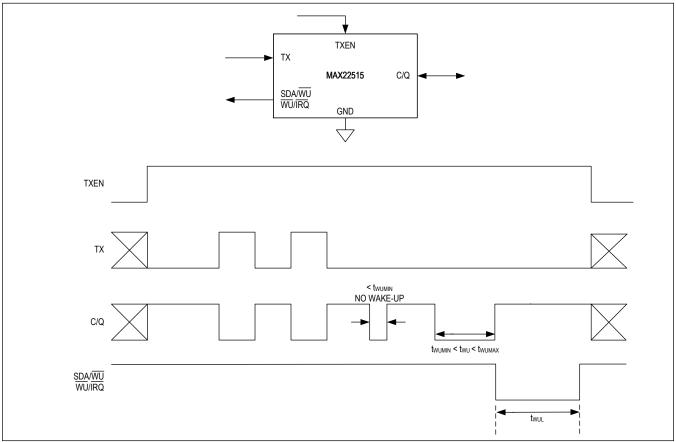

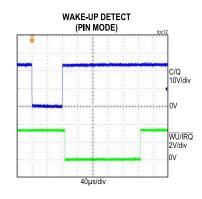

| AC ELECTRICAL CHARA                                                     | ACTERISTICS /         | WAKE-UP DETECT                           | ION ( <u>Figure 5</u> )            | 1         |       |       | •     |

| Wake-Up Input<br>Minimum Pulse Width                                    | twumin                | C <sub>LOAD</sub> = 3nF                  |                                    | 60        | 66    | 70    | μs    |

| Wake-Up Input<br>Maximum Pulse Width                                    | t <sub>WUMAX</sub>    | C <sub>LOAD</sub> = 3nF                  |                                    | 85        | 95    | 110   | μs    |

| SDA/WU (Pin mode),<br>WU/IRQ (I <sup>2</sup> C Mode)<br>Output Low Time | t <sub>WUL</sub>      | Valid wake-up con                        | dition on C/Q (Note 6)             | 150       | 200   | 250   | μs    |

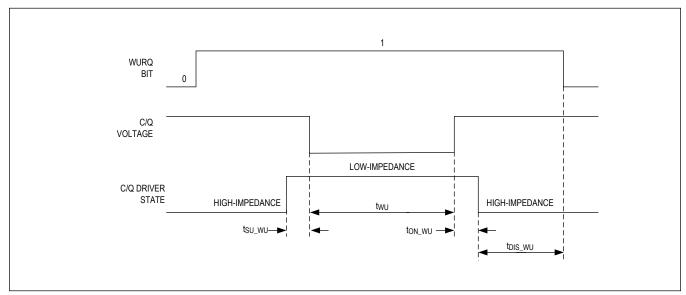

| AC ELECTRICAL CHARA                                                     | ACTERISTICS /         | WAKE-UP GENERA                           | ATION (I <sup>2</sup> C mode only, | Figure 6) |       |       |       |

| Setup Time before<br>Wake-Up                                            | tsu_wu                |                                          |                                    |           | 80    |       | μs    |

| Wake-Up Pulse<br>Duration                                               | t <sub>WU</sub>       | Wake-up pulse hat the existing C/Q le    | s opposite polarity of vel         | 75        | 80    | 85    | μs    |

| On-Time after Wake-Up                                                   | t <sub>ON_WU</sub>    | C/Q driver enabled after t <sub>WU</sub> | d with original polarity           |           | 2     |       | μs    |

| High Impedance Time after Wake-Up                                       | t <sub>DIS_WU</sub>   | C/Q driver is high i                     | mpedance after                     |           | 418   |       | μs    |

| C/Q Driver Current Limit<br>During Wake-Up Pulse                        | I <sub>WU</sub>       | WURQ = 1, CLDIS                          | S = 0 or 1                         | 500       |       |       | mA    |

| AC ELECTRICAL CHARA                                                     | ACTERISTICS /         | MCLK CLOCK TIMI                          | NG                                 | •         |       |       |       |

|                                                                         |                       | CLKDIV[2:0] = 000                        | )                                  | 3.612     | 3.686 | 3.761 |       |

|                                                                         |                       | CLKDIV[2:0] = 001                        |                                    | 7.225     | 7.373 | 7.523 | 1     |

| MCLK Frequency                                                          | f <sub>MCLK</sub>     | CLKDIV[2:0] = 010                        | )                                  | 14.45     | 14.74 | 15.05 | MHz   |

|                                                                         |                       | CLKDIV[2:0] = 011                        |                                    | 28.90     | 29.49 | 30.09 | 1     |

|                                                                         |                       | CLKDIV[2:0] = 100                        |                                    | 1.806     | 1.843 | 1.881 |       |

| MCLK Duty Cycle                                                         | D <sub>MCLK</sub>     |                                          |                                    |           | 50    |       | %     |

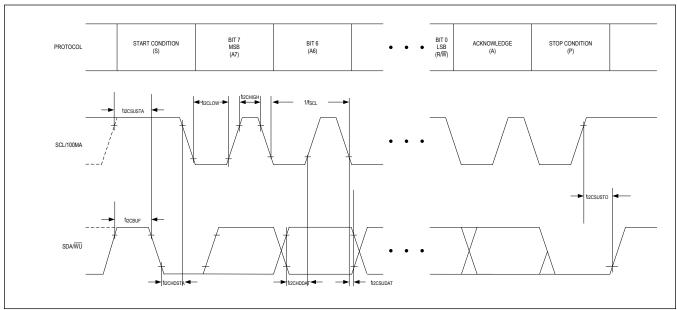

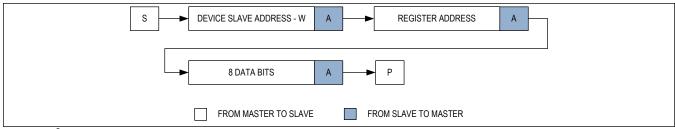

| AC ELECTRICAL CHARA                                                     | ACTERISTICS /         | I <sup>2</sup> C TIMING SPECIF           | FICATIONS ( <u>Figure 7</u> )      |           |       |       |       |

| Maximum I <sup>2</sup> C Clock<br>Frequency                             | f <sub>I2CCLK</sub>   |                                          |                                    |           |       | 2     | MHz   |

| Maximum Clock Period                                                    | tsclmax               |                                          |                                    | 100       |       |       | μs    |

| Bus Free Time Between<br>STOP and START<br>Condi- tions                 | <sup>t</sup> I2CBUF   |                                          |                                    | 0.16      |       |       | μs    |

| START Condition Setup<br>Time                                           | t <sub>I2CSUSTA</sub> |                                          |                                    | 0.05      |       |       | μs    |

| Repeat START<br>Condition Setup Time                                    | t <sub>I2CSUSTA</sub> | 90% to 90%                               |                                    | 0.05      |       |       | μs    |

| START Condition Hold<br>Time                                            | <sup>t</sup> I2CHDSTA | 10% of SDA/WU to                         | o 90% of SCL/100MA                 | 0.09      |       |       | μs    |

## **Electrical Characteristics—AC (continued)**

$(V_{24} = 8V \text{ to } 36V, V_5 = 4.5V \text{ to } 5.5V, V_L = 2.5V \text{ to } 5.5V, \text{ All logic inputs at } V_L \text{ or GND, } T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{24} = 24V, V_5 = 5V, V_L = 3.3V, \text{ and } T_A = +25^{\circ}\text{C}, \text{ unless otherwise noted.}$  (Notes 1, 2)

| PARAMETER                                                    | SYMBOL                 | CONDITIONS                                                                          | MIN  | TYP  | MAX | UNITS |

|--------------------------------------------------------------|------------------------|-------------------------------------------------------------------------------------|------|------|-----|-------|

| STOP Condition Setup<br>Time                                 | t <sub>12</sub> CSUSTO | 90% of SCL/100MA to 10% of SDA/WU                                                   | 0.05 |      |     | μs    |

| Clock Low Period                                             | t <sub>I2CLOW</sub>    | 10% to 10%                                                                          | 0.12 |      |     | μs    |

| Clock High Period                                            | t <sub>I2CHIGH</sub>   | 90% to 90%                                                                          | 0.18 |      |     | μs    |

| Data Valid to SCL/<br>100MA Rise Time                        | t <sub>I2CSUDAT</sub>  | Write Setup Time                                                                    | 50   |      |     | ns    |

| Data Hold Time                                               | t <sub>I2CHDDAT</sub>  | Write Hold Time                                                                     |      |      | 0   | ns    |

| Maximum SDA/WU<br>Drive Low Time                             | tDATLOW                |                                                                                     | 1.0  | 1.1  | 1.2 | ms    |

| ESD AND EMC TOLERA                                           | NCE                    |                                                                                     |      |      |     |       |

| ESD Protection<br>(V <sub>24</sub> , C/Q, DI Pins)           |                        | IEC 61000-4-2 Contact Discharge, 500pF load on C/Q, 1.5k $\Omega$ in series with DI |      | ±4   |     | kV    |

| ESD Protection<br>(All Other Pins)                           |                        | Human Body Model                                                                    |      | ±2   |     | kV    |

| Surge Protection<br>(V <sub>24</sub> , C/Q, DI, GND<br>Pins) | V <sub>SRG</sub>       | IEC 61000-4-5, 500Ω, 8/20μs surge                                                   |      | ±1.2 |     | kV    |

- **Note 1:** All devices 100% production tested at  $T_A = +25^{\circ}$ C. Limits over operating temperature range are guaranteed by design.

- Note 2: Currents out of the device are negative. Currents into the device are positive.

- Note 3: Not production tested. Guaranteed by design.

- Note 4:  $V_{DROP}$  is measured as the voltage from the driver output to GND ( $V_{DRIVER}$   $V_{GND}$ ) when measuring the low-side drivercurrent limit and as ( $V_{24}$   $V_{DRIVER}$ ) when measuring the high-side current limit.

- Note 5: When CQ\_PD or CQ\_PU are set to 1, the weak pullups and weak pulldowns are enabled in all C/Q operating modes: transceiver in receive mode and driver in push-pull, NPN, or PNP modes

- Note 6: SDA/WU always asserts when a valid wake-up condition is received when operating in pin mode. When operating the device in I<sup>2</sup>C mode, WU/IRQ asserts for t<sub>WUL</sub> only when no interrupts have been registered (INTERRUPT register) and the WUM = 1 in the IRQMASK register. If WUM = 0, WUINT is set when a valid wake-up event is detected and WU/IRQ asserts until the INTERRUPT register is read.

Figure 1. C/Q Driver Propagation Delays

Figure 2. C/Q Driver Enable Low and Disable High Timing

Figure 3. C/Q Driver Enable Time High and Disable Time Low

Figure 4. C/Q and DI Receiver Timing

Figure 5. Wake-Up Detection Timing

Figure 6. Wake-Up Generation Timing

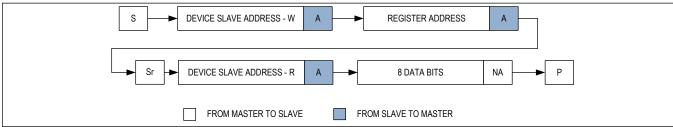

Figure 7. I<sup>2</sup>C Timing

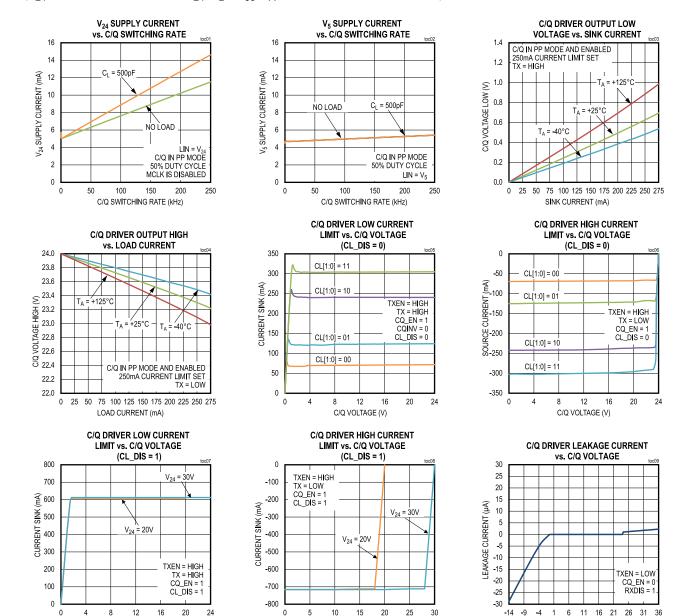

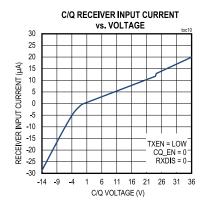

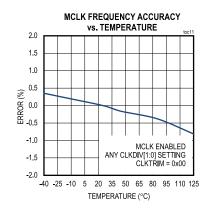

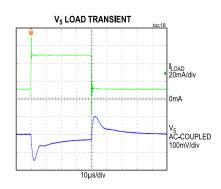

## **Typical Operating Characteristics**

C/Q VOLTAGE (V)

( $V_{24}$  = 24V, LIN is connected to  $V_{24}$ ,  $V_L$  =  $V_{33}$ ,  $T_A$  = 25°C, unless otherwise noted.)

www.analog.com Analog Devices | 14

C/Q VOLTAGE (V)

C/Q VOLTAGE (V)

# **Typical Operating Characteristics (continued)**

( $V_{24}$  = 24V, LIN is connected to  $V_{24}$ ,  $V_L$  =  $V_{33}$ ,  $T_A$  = 25°C, unless otherwise noted.)

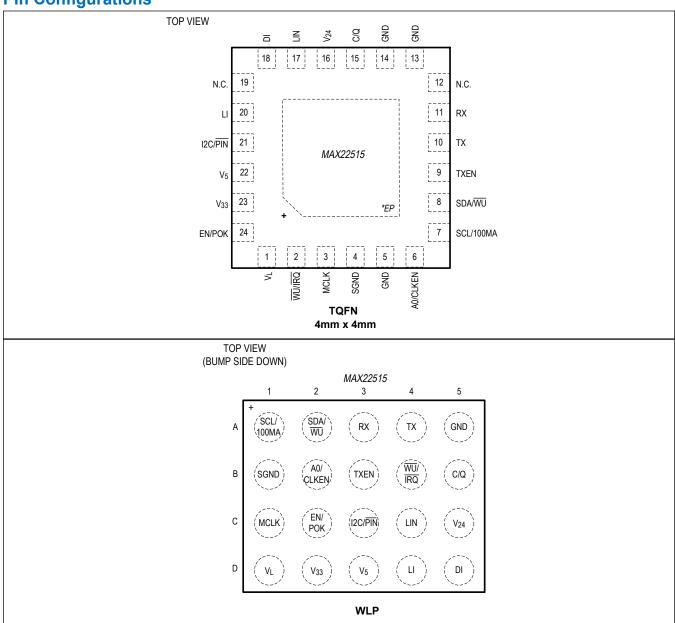

# **Pin Configurations**

# **Pin Description**

| Р     | IN  | NAME | FUNCTION                                                                                                                                                                                                                                      |

|-------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN  | WLP | NAME | FUNCTION                                                                                                                                                                                                                                      |

| POWER |     |      |                                                                                                                                                                                                                                               |

| 1     | D1  | VL   | Logic Supply Input. Bypass $V_L$ to GND with a 0.1 $\mu$ F capacitor as close to the device as possible. $V_L$ sets the logic level for all logic signals. Connect $V_L$ to $V_{33}$ , $V_5$ , or to an external voltage between 2.5V and 5V. |

| 4     | B1  | SGND | Signal Ground. Connect SGND to GND.                                                                                                                                                                                                           |

# **Pin Description (continued)**

| P             | PIN    |                 |                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|---------------|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFN          | WLP    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 5, 13, 14     | A5     | GND             | Ground                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 16            | C5     | V <sub>24</sub> | Supply Voltage Input. Apply a 24V (typ) supply to $V_{24}$ . Bypass $V_{24}$ to GND with a 10nF capacitor as close to the device as possible.                                                                                                                                                                                                                        |  |  |

| 17            | C4     | LIN             | 5V Linear Regulator Input. Bypass LIN to GND with a 10nF capacitor as close to the device as possible. Connect LIN to $V_{24}$ or to an external supply between 8V and 36V. Short LIN to $V_5$ to disable the internal regulator. Connect 5V to LIN and $V_5$ when the internal regulator is disabled.                                                               |  |  |

| 22            | D3     | V <sub>5</sub>  | 5V Linear Regulator Output/Supply Input. Bypass $V_5$ to GND with a 1µF capacitor as close to the device as possible. $V_5$ is the output of the internal 5V linear regulator. To disable the internal regulator, connect LIN to $V_5$ . 5V is required on $V_5$ for normal operation. If the 5V regulator is disabled, apply an external 5V power supply to $V_5$ . |  |  |

| 23            | D2     | V <sub>33</sub> | 3.3V Linear Regulator Output. Bypass $V_{33}$ to GND with a 1 $\mu$ F capacitor as close to the device as possible. $V_{33}$ is not required for normal operation.                                                                                                                                                                                                   |  |  |

| EP            | -      | EP              | Exposed Pad (TQFN Only). Connect EP to GND.                                                                                                                                                                                                                                                                                                                          |  |  |

| 24V LINE INTE | RFACE  |                 |                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 15            | B5     | C/Q             | IO-Link Transceiver Input/Output.  I <sup>2</sup> C Mode: C/Q is disabled at startup. Set CQ_EN = 1 and drive TXEN high to enable the C/Q driver.                                                                                                                                                                                                                    |  |  |

|               |        |                 | Pin mode: Drive TXEN high to enable the C/Q driver.                                                                                                                                                                                                                                                                                                                  |  |  |

|               |        |                 | Auxiliary Digital Input.                                                                                                                                                                                                                                                                                                                                             |  |  |

| 18            | D5     | DI              | I <sup>2</sup> C Mode: DI is enabled at power-up. Disable DI by setting the DIDIS bit in the CONTROL register.                                                                                                                                                                                                                                                       |  |  |

|               |        |                 | Pin mode: DI is enabled and cannot be disabled.                                                                                                                                                                                                                                                                                                                      |  |  |

| CONTROL INT   | ERFACE |                 |                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|               |        |                 | IO-Link Wake-Up Detection/Interrupt Open-Drain Output.                                                                                                                                                                                                                                                                                                               |  |  |

| 2             | B4     | WU/IRQ          | I <sup>2</sup> C Mode: WU/IRQ asserts low when a valid IO-Link wake-up is detected on the C/Q line or when a bit in the INTERRUPT register is set.                                                                                                                                                                                                                   |  |  |

|               |        |                 | Pin mode: WU/IRQ asserts low when a thermal or overcurrent fault occurs. WU/IRQ deasserts when the fault is no longer present.                                                                                                                                                                                                                                       |  |  |

|               |        |                 | I <sup>2</sup> C Address Select/MCLK Enable Input.                                                                                                                                                                                                                                                                                                                   |  |  |

| 6             | B2     | A0/CLKEN        | I <sup>2</sup> C Mode: Connect A0/CLKEN high or low to set the I <sup>2</sup> C address for the MAX22515. See the I <sup>2</sup> C Controller Interface section for more information.                                                                                                                                                                                |  |  |

|               |        |                 | Pin mode: Drive A0/CLKEN high to enable the clock output on MCLK. Drive A0/CLKEN low to disable the clock output. MCLK is 14.74MHz (typ) in pin mode. MCLK is high impedance when disabled.                                                                                                                                                                          |  |  |

|               |        |                 | I <sup>2</sup> C Serial Clock/C/Q Driver Current Limit Setting Input.                                                                                                                                                                                                                                                                                                |  |  |

| 7             | A1     | SCL/100MA       | I <sup>2</sup> C Mode: I <sup>2</sup> C interface clock input.                                                                                                                                                                                                                                                                                                       |  |  |

|               |        |                 | Pin mode: Drive SCL/100MA high to set the C/Q driver current limit to 100mA (min). Drive SCL/100MA low to set the driver current limit to 200mA (min).                                                                                                                                                                                                               |  |  |

# **Pin Description (continued)**

| Р           | IN    |                      |                                                                                                                                                                                                                                                                                 |  |  |

|-------------|-------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| TQFN        | WLP   | NAME                 | FUNCTION                                                                                                                                                                                                                                                                        |  |  |

|             |       |                      | I <sup>2</sup> C Serial Data Input/Ouput/Wake-Up Detection Output.                                                                                                                                                                                                              |  |  |

| 8           | 8 A2  | SDA/WU               | I <sup>2</sup> C Mode: I <sup>2</sup> C serial data input/output.                                                                                                                                                                                                               |  |  |

|             |       |                      | Pin mode: SDA/WU asserts when a valid IO-Link wake-up is detected on the C/Q line.                                                                                                                                                                                              |  |  |

|             |       |                      | DI Receiver Logic Output. The DI receiver is enabled by default.                                                                                                                                                                                                                |  |  |

| 20          | D4    | LI                   | I <sup>2</sup> C Mode: LI is inverted relative to the logic state of DI by default. Set the LIDIS bit in the CONTROL register to disable the LI output. LI is high impedance when LIDIS = 1.                                                                                    |  |  |

|             |       |                      | Pin mode: LI is inverted relative to the logic state of DI by default. LI cannot be disabled.                                                                                                                                                                                   |  |  |

| 21          | C3    | I <sup>2</sup> C/PIN | I <sup>2</sup> C or Pin Mode Control Interface Selection Input. Connect I <sup>2</sup> C/PIN high to configure and monitor the MAX22515 with the I2C interface. Connect I <sup>2</sup> C/PIN low to configure the MAX22515 for pin mode control.                                |  |  |

|             |       |                      | Dual Function Enable Input and Open-Drain Power-OK (POK) Output. Connect EN/POK to $V_L$ with a $10 \mathrm{k}\Omega$ resistor.                                                                                                                                                 |  |  |

| 24          | 24 C2 | EN/POK               | Enable Input: Drive EN/POK high to enable the MAX22515 for normal operation. Drive EN/POK low to disable the device. The C/Q driver is disabled and registers are reset (when using I <sup>2</sup> C mode) when EN/POK is low.                                                  |  |  |

|             |       |                      | POK Output: The MAX22515 drives EN/POK low when the $V_5$ voltage falls below 3V. The C/Q driver is disabled and registers are reset (when using I <sup>2</sup> C mode) when EN/POK is low. The MAX22515 releases EN/POK when the $V_5$ voltage rises above the 3.5V threshold. |  |  |

| UART INTERF | ACE   | 1                    |                                                                                                                                                                                                                                                                                 |  |  |

|             |       |                      | C/Q Driver Enable Logic Input. Connect TXEN to the RTS output of a microcontroller for IO-Link communication.                                                                                                                                                                   |  |  |

| 9           | В3    | TXEN                 | I <sup>2</sup> C Mode: Set CQ_EN = 1 and drive TXEN high to enable the C/Q driver.                                                                                                                                                                                              |  |  |

|             |       |                      | Pin mode: Drive TXEN high to enable the C/Q driver. Drive TXEN low to disable the driver.                                                                                                                                                                                       |  |  |

|             |       |                      | C/Q Driver Logic Input. Connect TX to the TX output of a UART for IO-Link communication.                                                                                                                                                                                        |  |  |

| 10          | A4    | TX                   | I <sup>2</sup> C Mode: TX is inverted relative to the logic state of C/Q by default.                                                                                                                                                                                            |  |  |

|             |       |                      | Pin mode: TX is inverted relative to the logic state of C/Q.                                                                                                                                                                                                                    |  |  |

|             |       |                      | C/Q Receiver Logic Output. Connect RX to the RX input of a UART for IO-Link communication.                                                                                                                                                                                      |  |  |

| 11          | А3    | RX                   | I <sup>2</sup> C Mode: RX is inverted relative to the logic state of C/Q by default. Set the RXDIS bit in the CONTROL register to disable RX. RX is high impedance when RXDIS = 1.                                                                                              |  |  |

|             |       |                      | Pin mode: RX is inverted relative to the logic state of C/Q. RX cannot be disabled.                                                                                                                                                                                             |  |  |

# **Pin Description (continued)**

| P             | PIN |         | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|---------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|