## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All recreations are done with the approval of the OCM.

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceed the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

• Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OEM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

### Not Intended For New Designs

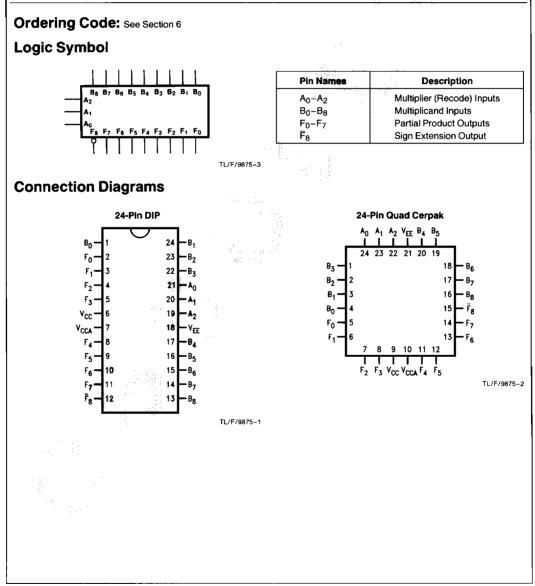

## 100183 2 x 8-Bit Recode Multiplier

### **General Description**

The 100183 is a 2 x 8-bit recode multiplier designed to perform high-speed hardware multiplication. In conjunction with the 100182 Wallace Tree Adder, the 100179 Carry Lookahead, and the 100180 High-speed Adder, the

100183 performs parallel multiplication of two signed numbers in twos complement form to produce a signed twos complement product. All inputs have 50 k $\Omega$  pull-down resistors.

### **Absolute Maximum Ratings**

Above which the useful life may be impaired. (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Storage Temperature-65°C to +150°CMaximum Junction Temperature (TJ)+150°C

### **DC Electrical Characteristics**

$V_{\text{EE}}=~-4.5V,\,V_{\text{CC}}=~V_{\text{CCA}}=~\text{GND},\,T_{\text{C}}=~0^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  (Note 3)

Units **Conditions (Note 4)** Symbol Parameter Min Тур Max VOH **Output HIGH Voltage** -1025 -955 -880VIN = VIH (Max) Loading with m٧ 50Ω to -2.0V or VIL (Min) **Output LOW Voltage** -1810 -1705 -1620VOL - 1035 VIN = VIH (Min) **Output HIGH Voltage** Loading with VOHC m٧ 50Ω to -2.0V or VIL (Max) Output LOW Voltage - 1610 VOLC VIH Guaranteed HIGH Signal Input HIGH Voltage mν -1165 -880 for All Inputs VII. Input LOW Voltage Guaranteed LOW Signal -1475 m٧ -1810 for All Inputs μA  $V_{IN} = V_{IL (Min)}$ Input LOW Current 0.50 հր

Case Temperature under Bias (T<sub>C</sub>)

VEE Pin Potential to Ground Pin

Output Current (DC Output HIGH)

Operating Range (Note 2)

Input Voltage (DC)

0°C to +85°C

V<sub>EE</sub> to +0.5V

-5.7V to -4.2V

– 50 mA

-7.0V to +0.5V

### **DC Electrical Characteristics**

$V_{EE} = -4.2V$ ,  $V_{CC} = V_{CCA} = GND$ ,  $T_C = 0^{\circ}C$  to  $+85^{\circ}C$  (Note 3)

| Symbol          | Parameter           | Min           | Тур                            | Mex    | Units | Conditions                               | s (Note 4)             |  |

|-----------------|---------------------|---------------|--------------------------------|--------|-------|------------------------------------------|------------------------|--|

| V <sub>OH</sub> | Output HIGH Voltage | - 1020        |                                | -870   | mν    | V <sub>IN</sub> = V <sub>IH (Max)</sub>  | Loading with           |  |

| VOL             | Output LOW Voltage  | - 1810        |                                | - 1605 |       | or V <sub>IL (Min)</sub>                 | 50 $\Omega$ to $-2.0V$ |  |

| VOHC            | Output HIGH Voltage | - 1030        |                                | 44     | mv    | V <sub>IN</sub> ≖ V <sub>IH (Min)</sub>  | Loading with           |  |

| VOLC            | Output LOW Voltage  | a             |                                | - 1595 |       | or V <sub>IL (Max)</sub>                 | 50Ω to −2.0V           |  |

| VIH             | Input HIGH Voltage  | -1150         | e<br>1.<br>N - <sup>1</sup> e- | ÷ 870  | m∨    | Guaranteed HIGH Signal<br>for All Inputs |                        |  |

| VIL             | Input LOW Voltage   | - <b>1810</b> |                                | -1475  | m∨    | Guaranteed LOW Signal for All Inputs     |                        |  |

| կլ              | Input LOW Current   | 0.50          |                                |        | μА    | $V_{IN} = V_{IL (Min)}$                  |                        |  |

### DC Electrical Characteristics

$V_{EE} = -4.8V, V_{CC} = V_{CCA} = GND, T_{C} = 0^{\circ}C$  to +85°C (Note 3)

| Symbol           | Parameter           | Min    | Тур | Max    | Units | Condition                                | s (Note 4)   |

|------------------|---------------------|--------|-----|--------|-------|------------------------------------------|--------------|

| V <sub>OH</sub>  | Output HIGH Voltage | - 1035 |     | 880    | mV    | VIN = VIH (Max)                          | Loading with |

| VOL              | Output LOW Voltage  | - 1830 |     | - 1620 |       | or V <sub>IL (Min)</sub> 50Ω to -2       |              |

| V <sub>OHC</sub> | Output HIGH Voltage | - 1045 |     |        | mV    |                                          | Loading with |

| VOLC             | Output LOW Voltage  |        |     | - 1610 |       | or V <sub>IL (Max)</sub>                 | 50Ω to −2.0V |

| ViH              | Input HIGH Voltage  | - 1165 |     | -880   | mV    | Guaranteed HIGH Signal<br>for All Inputs |              |

| VIL              | hput LOW Voltage    | - 1830 |     | -1490  | mV    | Guaranteed LOW Signal<br>for All Inputs  |              |

| IL Se            | Input LOW Current   | 0.50   |     |        | μΑ    | $V_{IN} = V_{IL}$ (Min)                  |              |

Note 1: Associate maximum ratings are those values beyond which the device may be damaged or have its useful life impaired. Functional operation under these conditions is not implied.

Note 2: Parametric values specified at -4.2V to -4.8V.

Note 3: The specified limits represent the "worst case" value for the parameter. Since these "worst case" values normally occur at the temperature extremes, additional noise immunity and guard banding can be achieved by decreasing the allowable system operating ranges.

Note 4: Conditions for testing shown in the tables are chosen to guarantee operation under "worst case" conditions.

| Symbol | Parameter                      | Min | Тур | Max  | Units | Conditions                |

|--------|--------------------------------|-----|-----|------|-------|---------------------------|

| Чн     | Input HIGH Current             |     |     |      |       | . 26                      |

|        | B <sub>0</sub> -B <sub>8</sub> |     |     | 215  |       |                           |

|        | Ao                             |     |     | 215  |       |                           |

|        | A <sub>1</sub>                 |     |     | 285  | μΑ    | ViN <del>≭</del> ViH (Max |

|        | A <sub>2</sub>                 |     |     | 310  | .a    |                           |

| IEE    | Power Supply Current           | 250 | 170 | -115 | mA    | Inputs Open               |

# Ceramic Dual-In-Line Package AC Electrical Characteristics $v_{EE} = -4.2V$ to -4.8V, $v_{CC} = v_{CCA} = GND$

**DC Electrical Characteristics**

| Symbol                               | Parameter                                         | T <sub>C</sub> = 0°C |      | T <sub>C</sub> = + 25°C |      | T <sub>C</sub> = +85°C |      | Units  | Conditions             |  |

|--------------------------------------|---------------------------------------------------|----------------------|------|-------------------------|------|------------------------|------|--------|------------------------|--|

| Cymbol                               |                                                   | Min                  | Max  | Min                     | Мах  | Min                    | Max  | - Onle | Conditions             |  |

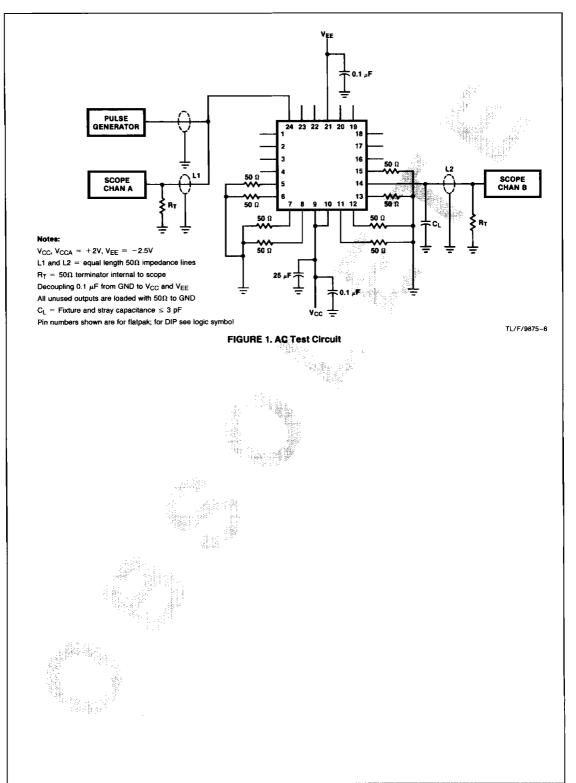

| <sup>t</sup> PLH<br>t <sub>PHL</sub> | Propagation Delay<br>$A_0 - A_2$ to $F_0 - F_7$   | 1.10                 | 3.90 | 1.10                    | 3.80 | 1.10                   | 4.20 | ns     | Figures 1 and 2        |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $A_0 - A_2$ to $\overline{F}_8$ | 0.90                 | 3.20 | 1.00                    | 3.10 | 1,00                   | 3.60 | ns     | rigures i anu z        |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>$B_0-B_8$ to $F_0-F_7$       | 0.80                 | 2.20 | 0.90                    | 2.15 | 0.90                   | 2.50 | ns     | Figures 1 and 2        |  |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $B_8$ to $\overline{F}_8$       | 0.80                 | 2.00 | 0.90                    | 2.00 | 0.90                   | 2.50 | ns     | <i>Figures i</i> and 2 |  |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition Time<br>20% to 80%, 80% to 20%         | 0.45                 | 2.50 | 0.45                    | 2.40 | 0.45                   | 2.60 | ns     | Figures 1 and 2        |  |

## Cerpak AC Electrical Characteristics $V_{EE} = -4.2V$ to -4.8V, $V_{CC} = V_{CCA} = GND$

| Symbol                               | Parameter                                          | Тс   | T <sub>C</sub> <b>=</b> 0°C |      | T <sub>C</sub> ⊨ + 25°C |      | T <sub>C</sub> = +85°C |       | Conditions      |

|--------------------------------------|----------------------------------------------------|------|-----------------------------|------|-------------------------|------|------------------------|-------|-----------------|

|                                      |                                                    | Min  | Mex                         | Min  | Max                     | Min  | Max                    | Units | Conditions      |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $A_0 - A_2$ to $F_0 - F_7$       | 1.10 | 3.70                        | 1.10 | 3.60                    | 1.10 | 4.00                   | ns    | Figures 1 and 2 |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay $A_0 - A_2$ to $F_8$             | 0.90 | 3.00                        | 1.00 | 2.90                    | 1.00 | 3.40                   | ns    |                 |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay $B_0-B_8$ to $F_0-F_7$           | 0.80 | 2.00                        | 0.90 | 1.95                    | 0.90 | 2.30                   | ns    | Figures 1 and 2 |

| <sup>t</sup> PLH<br>t <sub>PHL</sub> | Propagation <b>Delay</b> $B_8$ to $\overline{F}_8$ | 0.80 | 1.80                        | 0.90 | 1.80                    | 0.90 | 2.30                   | ns    | riguros rana z  |

| t <sub>TLH</sub><br>t <sub>THL</sub> | Transition Time<br>20% to 80%, 80% to 20%          | 0.45 | 2.40                        | 0.45 | 2.30                    | 0.45 | 2.50                   | ns    | Figures 1 and 2 |

3

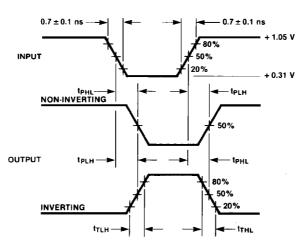

FIGURE 2. Propagation Delay and Transition Times

## Application

100183 is a 2 x 8-bit recode multiplier that performs parallel multiplication using twos complement arithmetic. In multiplying, the multiplier is partitioned into recode groups, then each recode group operates on the multiplicand to provide a partial product at the same time. The 100183, 2 x 8-bit recode multiplier provides partial products in 3.6 ns.

The 100182, 9-Bit Wallace Tree Adder combines the partial products to obtain the partial sum and partial carries in an additional 10.7 ns. Then the Carry Lookahead generator and 6-bit adder combine the results of a 16 x 16-bit multiply

for a total of 24.3 ns. The propagation delays and package count for implementing various size multipliers are listed in Tables I and II.

TL/F/9875-7

Multiplication of twos complement binary numbers is accomplished by first obtaining all the partial products. Then the weighted partial products are added together to yield the final result. In the Wallace Tree method of multiplication the sign bit is treated the same as the rest of the bits to obtain a signed result.

| Array<br>Size              | Recode<br>Multiplier<br>100183 | Wallace<br>Tree Adder<br>100182 | High-speed<br>Adder<br>100180 | Carry<br>Lookahead<br>100179 |   | Total (Max)<br>Delay |

|----------------------------|--------------------------------|---------------------------------|-------------------------------|------------------------------|---|----------------------|

| 16 x 16                    | 3.6                            | 10.7                            | 7.3                           | 2.7                          | = | 24.3 ns              |

| 17 x 17<br>thru<br>24 x 24 | 3.6                            | 21.4                            | 7.3                           | 2.7                          |   | 35.0 ns              |

| 25 x 25<br>thru<br>48 x 48 | 3.6                            | 21.4                            | 7.3                           | 5.4                          | = | 37.7 ns              |

| 49 x 49<br>thru<br>72 x 72 | 3.6                            | 21.4                            | 7.3                           | 8.1                          | = | 40.4 ns              |

| 73 x <b>73</b>             | 3.6                            | 32.1                            | 7.3                           | 10.8                         | = | 53.8 ns              |

#### **TABLE I. Propagation Delay Summation\***

\*Worst case, Flatpak

## Application (Continued)

100183

|         | 100102<br>100117 | 100183 | 100182 | 100180 | 100179 |     | Total |  |

|---------|------------------|--------|--------|--------|--------|-----|-------|--|

| 16 x 16 | 6                | 16     | 32     | 6      | 2      |     | 62    |  |

| 18 x 18 | 7                | 27     | 38     | 6      | 2      | =   | 70    |  |

| 24 x 24 | 9                | 36     | 60     | 8      | 2      | 447 | 115   |  |

| 32 x 32 | 11               | 64     | 96     | 11     | 4      | =   | 186   |  |

| 36 x 36 | 13               | 80     | 116    | 12     | 4      | =   | 225   |  |

| 64 x 64 | 24               | 256    | 328    | 22     | 6      | =   | 634   |  |

TABLE II. Package Count

For a quick review of the twos complement number format see Table III. Note that subtraction is accomplished by adding the negative number. An example of changing from a positive number to a negative number is shown.

1011 negative number-5

- 0100 bits inverted

- +0001 add one

- 0101 Results 5

#### TABLE III. Twos Complement Format

| Sign<br>Bit | 2 <sup>2</sup> | Magnitude<br>2 <sup>1</sup> | 2 <sup>0</sup> | Decimal<br>Number |

|-------------|----------------|-----------------------------|----------------|-------------------|

| 0           | 1              | 1                           | 1              | +7                |

| 0           | . 1            | 1                           | 0              | +6                |

| 0           | 1              | 0                           | 1              | +5                |

| 0           | 1              | 0                           | 0              | +4                |

| 0           | 0 -            | 1                           | 1              | +3                |

| 0           | 0              | 1                           | 0              | +2                |

| 0           | 0              | 0                           | 1              | +1                |

| 0           | 0              | 0                           | 0              | +0                |

| 1           | 1              | 1                           | 1              | 1                 |

| 1           | 1              | 1                           | 0              | 2                 |

| 1           | 1              | 0                           | 1              | -3                |

| 1           | 1              | 0                           | 0              | 4                 |

| 1           | 0              | 1                           | 1              | 5                 |

| 1           | 0              | 1                           | 0              | 6                 |

| 1           | 0              | 0                           | 1              | 7                 |

| 1           | 0              | 0                           | 0              | 8                 |

### **Multiplication Algorithm**

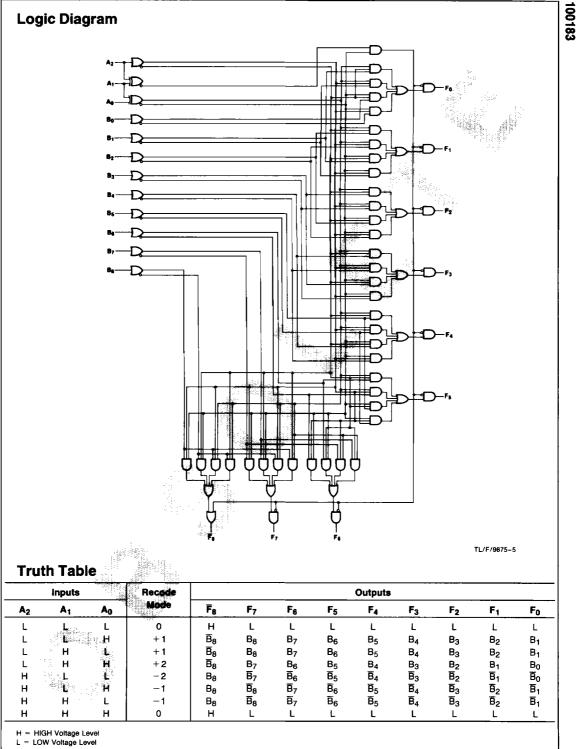

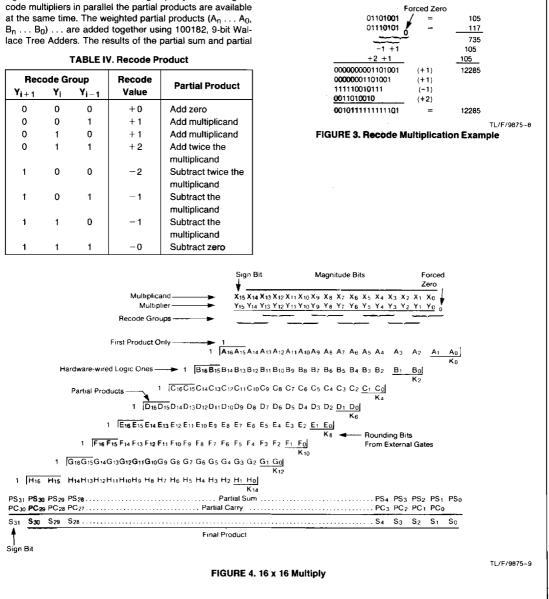

In the multiplication algorithm used, the multiplier  $(Y_n\ldots Y_0)$  is partitioned into recode groups and each recode group operates on the multiplicand  $(X_n\ldots X_0)$  as in *Figure 4*. The 100183, 2 x 8-bit recode multiplier partitions the multiplier  $(X_n\ldots X_0)$  into groups of eight and the multiplicand  $(Y_n\ldots Y_0)$  into groups of eight and the multiplicand  $(Y_n\ldots Y_0)$  into groups of two. Each recode group is two bits wide but requires three bits to determine the partial products. Table IV lists the significance of the various recode groups. The partial product is  $\pm 0, \pm$  multiplicand, or  $\pm$  two times the multiplicant bit of the first recode group. By connecting recode multipliers in parallel the partial products  $(A_n\ldots A_0, B_n\ldots B_0)\ldots$  are added together using 100182, 9-bit Wallace Tree Adders. The results of the partial sum and partial

carry are combined together using Carry Lookahead generators and 6-bit adders. An example of using recode multiplication is shown in *Figure 3*: multiplier ( $117_{10}$ ) 01110101 times multiplicand ( $105_{10}$ ) 01101001. The first recode group 010 requires adding the multiplicand; the second recode group 010 also requires adding the multiplicand, the third group 110 requires subtracting the multiplicand (the same as inverting each digit and adding 1); the fourth group 011 requires adding twice the multiplicand. Combining the results of four groups, 12285<sub>10</sub>, we have the correct answer.

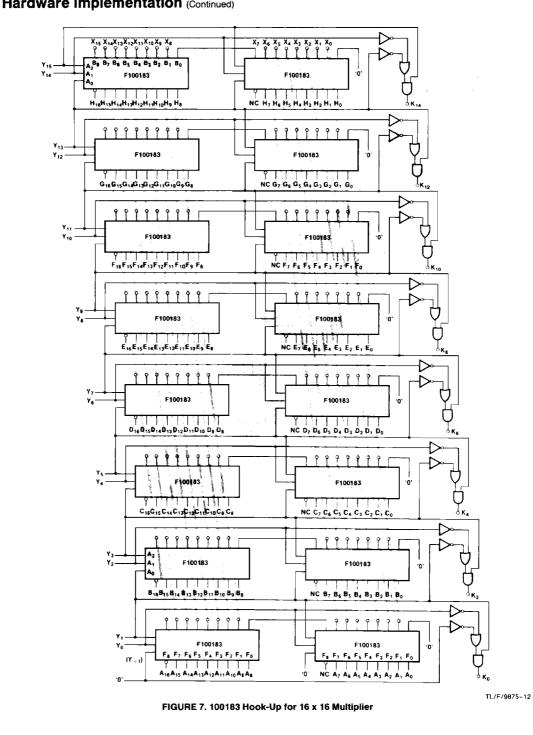

### **Hardware Implementation**

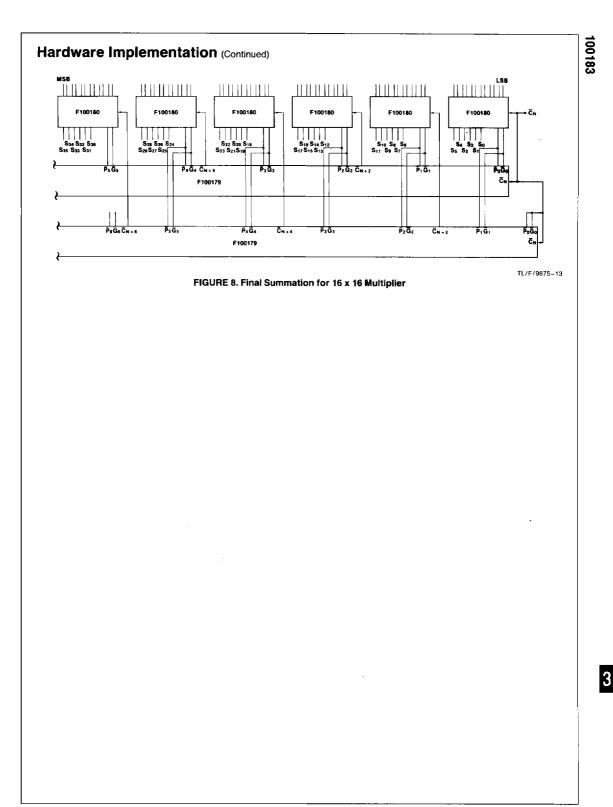

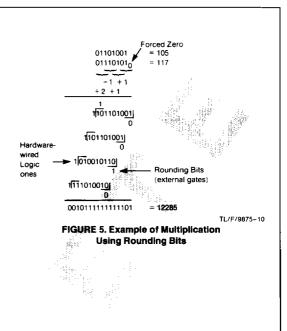

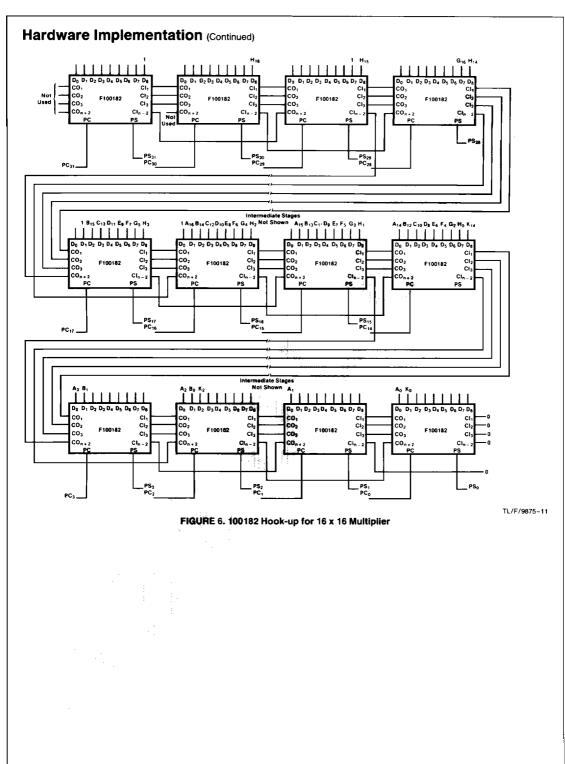

For the hardware implementation of the 100183 recode multiplier the sign bit is connected to the B<sub>8</sub> input, and B<sub>7</sub> through B<sub>0</sub> are the magnitude bits. Two extend the word length greater than eight bits, the B0 and B8 inputs of adjacent devices are connected together (see Figure 7). The device outputs F<sub>0</sub> through F<sub>7</sub> are used as the partial products; these correspond to A<sub>0</sub> through A<sub>7</sub>, or A<sub>8</sub> through A<sub>15</sub>, or  $B_0$  through  $B_7$ , etc. To reduce the hardware, the  $\overline{F}_8$  bit (A16 in Figure 7) is used as the sign bit of the partial product. The sign bits are extended by using hardware wired logic "1s". The ones are located in front of each partial product with an extra "1" at the sign bit of the first partial product as in Figure 4. The logic "1s" are wired as inputs into the Wallace Tree Adders as shown in Figure 6. If the recode group requires the multiplicand to be added, then the 100183 outputs the correct partial products to be added. But when the recode group requires that the multiplicand be subtracted, then the 100183 outputs the ones complement. External gates are required to generate a "1" to be added to the ones complement to complete the twos complement for the partial product (Figure 7). These external gates generate the rounding bits,  $K_0 \ldots K_n$ , which are input to the Wallace Tree Adder. Figures 4, 6 and 7 show the location. An example of multiplication which has the rounding bits and the hardware wired logic "1s" is shown in Figure 5.

The weighted partial products are added together using 100182, 9-bit Wallace Tree Adders as shown in *Figure 6*. The output is a partial sum and partial carry which can be reduced to the final product using Carry Lookahead and 6-bit adders. See *Figure 8*.

### Hardware Implementation (Continued)