# MLX80002/MLX80004

Enhanced Universal Dual/Quad LIN Transceiver Datasheet

# **1. Features and Benefits**

- LIN 2.x/SAE J2602 and ISO17987-4 compliant

- Dual/Quad enhanced master transceiver function for each channel

- Backward compatible to quad-channel master transceiver MLX80001

- Small footprint QFN4x4 package (wettable flanks) and minimum external component count

- Dual/Quad versions with same package and footprint for cost/space optimized design

- Slew rate selection and High Speed Flash mode

- Wide operating voltage range V<sub>s</sub> = 5 to 27 V

- Fully compatible to 3.3V and 5V devices

- Very low standby current consumption of (typ) 10μA in sleep mode

- WAKE input for local wake-up capability

- Remote and local wake-up source recognition

- Control output INH for external components

- Integrated termination (resistor & decoupling diode) for both LIN master & slave nodes

- TxD dominant time out function in slave configuration

- RxD dominant time out function in master configuration

- Sleep timer

- Low EME (emission) and high EMI (immunity) level

- High impedance LIN pin in case of loss of ground or battery

- Enhanced ESD robustness

- +/- 10kV according to IEC 61000-4-2 for pins LIN, Vs and WAKE

# 2. Ordering Information

| Product Code | Temperature<br>Code | Package Code | Option Code | Packing Form<br>Code |

|--------------|---------------------|--------------|-------------|----------------------|

| MLX80002     | K                   | LW           | CAA-101     | RE                   |

| MLX80004     | K                   | LW           | BAA-101     | RE                   |

#### Legend:

Temperature Code: Package Code: Option Code: Packing Form: Ordering example: K = -40 to 125°C LW = Quad Flat Package (QFN), wettable flanks BAA-101 = Design Revision RE = Reel MLX80004 KLW-BAA-101-RE

# **3. General Description**

The MLX80004(2) is a quad/dual LIN transceiver physical layer device for a single wire data link capable of operating in applications using baud rates up to 20kBd. It is compliant to LIN2.x as well as to the SAE J2602 specifications. The IC furthermore can be used in ISO9141 systems. The MLX80004 is functionally compatible to the MLX80001 quad master LIN transceiver.

The device is flexible for use in LIN – master applications and slave applications as well. Due to the integrated master termination and the high ESD/EMC robustness of the device a minimum space and number of external components is required.

The number of LIN – channels can be easily adapted on the application requirements by combinations of quad and dual channel devices within the same foot print.

Because of the very low power consumption of the MLX80004 while being in sleep mode it's suitable for ECU applications with hard standby current requirements. The implemented high resistive LIN - termination in sleep mode as well as the RxD dominant time-out feature allows a comfortable handling of LIN short circuits to GND.

In order to reduce the power consumption in case of failure modes, the integrated sleep timer takes care for switching the IC into the most power saving sleep mode after Power-On or Wake-Up events are not followed by a mode change response of the microcontroller.

The MLX80004/2 has an improved EMI performance and ESD robustness according to the OEM Common Hardware Requirements for LIN in Automotive Applications Rev.1.2.

By using the MODEO/1 pins the application can be easily adapted on the required baud rate in order to optimize the EMC emissions. A high speed Flash Mode with disabled slew rate control is available as well.

To fulfill different OEM requirements, the integrated master termination can be disabled and external master resistors and decoupling diodes can be used. In this mode the MLX80004/2 can be used in slave applications as well.

#### MLX80002/MLX80004 Enhanced Universal Dual/Quad LIN Transceiver Datasheet

# 4. Table of Contents

| 1. Features and Benefits                                      | 1  |

|---------------------------------------------------------------|----|

| 2. Ordering Information                                       | 1  |

| 3. General Description                                        | 2  |

| 4. Table of Contents                                          | 3  |

| 5. Block Diagram                                              | 5  |

| 6. Pin Description                                            | 6  |

| 7. Electrical Specification                                   | 7  |

| 7.1. Operating Conditions                                     | 7  |

| 7.2. Absolute Maximum Ratings                                 | 8  |

| 7.3. Static Characteristics                                   | 9  |

| 7.4. Dynamic Characteristics<br>7.4.1. Duty Cycle Calculation |    |

| 8. Functional Description                                     |    |

| 8.1. Operating Modes                                          | 16 |

| 8.2. Initialization and Standby mode                          |    |

| 8.3. Active Modes                                             |    |

| 8.3.1. High Speed mode                                        |    |

| 8.3.3. Normal speed mode                                      |    |

| 8.4. Sleep Mode                                               |    |

| 8.5. Wake Up                                                  |    |

| 8.6. Wake Up Source Recognition                               |    |

| 8.7. Master / Slave configuration                             | 21 |

| 9. Fail-safe Features                                         | 22 |

| 9.1. Loss of battery                                          |    |

| 9.2. Loss of Ground                                           | 22 |

| 9.3. Short circuit to battery                                 |    |

| 9.4. Ground shift and short circuit to ground                 | 22 |

| 9.5. Thermal overload                                         | 22 |

| 9.6. Undervoltage lock out                                    |    |

| 9.7. Open Circuit protection                                  |    |

| 9.8. TxDx faulty start protection                             | 23 |

| 9.9. RxDx dominant time-out                                   | 23 |

| 9.10. TxDx dominant time-out                                  | 23 |

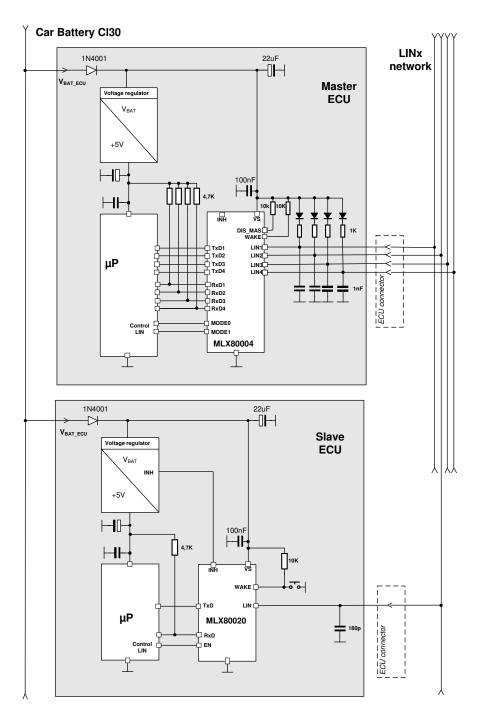

| 10. Application Example                                       | 24 |

| 10.1. Enhanced Master Mode                                    | 24 |

| 10.2. Standard Transceiver Mode                               | 25 |

| 10.3. Application Circuitry for EMC<br>10.3.1. External Circuitry on Supply Lines                          | 26 |

|------------------------------------------------------------------------------------------------------------|----|

| 10.3.1. External Circuitry on Supply Lines                                                                 | 27 |

| 10.3.2. External Circuitry on LIN Lines                                                                    | 27 |

| 10.3.3. External Circuitry on Signal Lines                                                                 | 27 |

| 1. Package Mechanical Specification                                                                        | 28 |

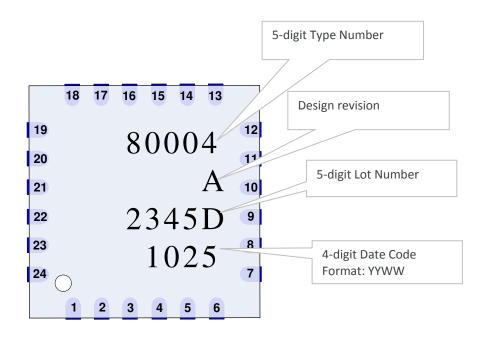

| 2. Package Marking Information                                                                             | 29 |

| 3. Tape and Reel Specification                                                                             | 30 |

| .4. ESD and EMC                                                                                            | 3  |

| 14.1. Automotive Qualification Test Pulses                                                                 | 33 |

| 14.2. Test Pulses On supply Lines                                                                          |    |

| 14.3. Test pulses on Pin LIN                                                                               | 34 |

| 14.4. Test pulses on signal lines                                                                          |    |

| 14.5. Test circuitry for automotive transients                                                             | 35 |

| 14.6. EMC Test pulse definition                                                                            | 36 |

| 5. Standard information regarding manufacturability of Melexis products with different soldering processes | 8  |

| .6. Disclaimer                                                                                             | 39 |

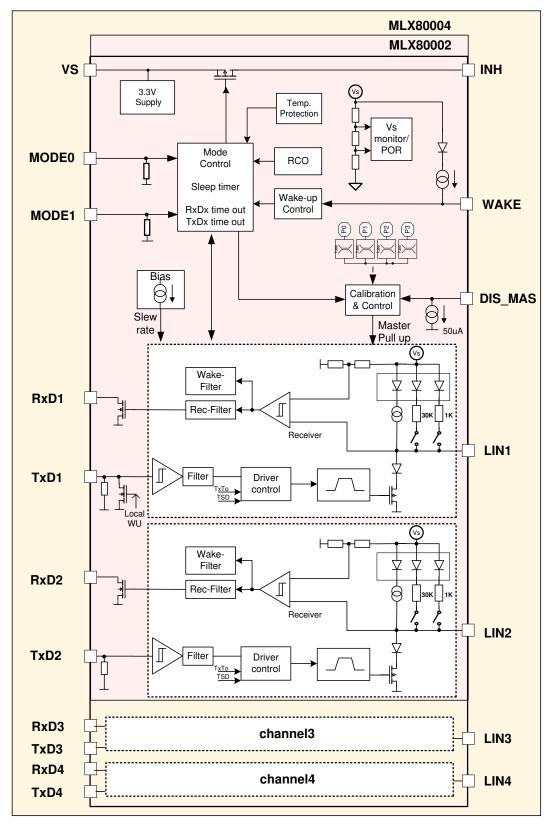

# 5. Block Diagram

#### Figure 1: Block Diagram MLX80004/2.

# 6. Pin Description

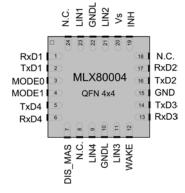

Figure 2: Pinout MLX80004 QFN4x4 24L

N.C. LIN1 GNDL Vs INH 23 22 21 21 21 RxD1 N.C. TxD1 RxD2 MLX80002 MODE0 TxD2 GND MODE1 QFN 4x4 N.C. N.C. N.C. N.C. N.C. GNDL N.C. WAKE DIS MAS Ŋ. N

Figure 3: Pinout MLX80002 QFN4x4 24L

#### Table 1: Pin List

| Pin  | MLX80004 | MLX80002    | I/O-Type | Description                                             |

|------|----------|-------------|----------|---------------------------------------------------------|

| 1    | Rx       | D1          | 0        | Receive Data LIN Ch1, open drain                        |

| 2    | Tx       | D1          | I        | Transmit Data LIN Ch1 (+ local WU-Flag)                 |

| 3    | MOI      | DE0         | I        | Operating Mode Selection Input 1                        |

| 4    | MOI      | DE1         | I        | Operating Mode Selection Input 2                        |

| 5    | TxD4     | N.C.        | I        | Transmit Data LIN Ch4                                   |

| 6    | RxD4     | N.C.        | 0        | Receive Data LIN Ch4, open drain                        |

| 7    | DIS_     | MAS         | I        | disable integrated master resistor                      |

| 8    | N.       | C.          |          |                                                         |

| 9    | LIN4     | N.C.        | I/O      | LIN Bus Ch4                                             |

| 10   | GN       | DL          | G        | Ground LIN                                              |

| 11   | LIN3     | N.C.        | I/O      | LIN Bus Ch3                                             |

| 12   | WA       | KE          | I        | local wake up input, low active                         |

| 13   | RxD3     | N.C.        | 0        | Receive Data LIN Ch3, open drain                        |

| 14   | TxD3     | N.C.        | I        | Transmit Data LIN Ch3                                   |

| 15   | GN       | ND          | G        | Ground                                                  |

| 16   | Tx       | D2          | I        | Transmit Data LIN Ch2                                   |

| 17   | Rx       | D2          | 0        | Receive Data LIN Ch2, open drain                        |

| 18   | N.       | C.          |          |                                                         |

| 19   | IN       | IH          | 0        | HV High Side Control Pin                                |

| 20   | V        | /S P Batter |          | Battery Voltage                                         |

| 21   | LI       | N2          | I/O      | LIN Bus Ch2                                             |

| 22   | GN       | DL          | G        | Ground LIN                                              |

| 23   | LI       | N1          | I/O      | LIN Bus Ch1                                             |

| 24   | N.       | C.          |          |                                                         |

| EPad | GND /    | GNDL        | G        | Exposed Pad of Package (grounded heatsink) <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup> For enhanced thermal and electrical performance, the exposed pad of the QFN package should be soldered to the board ground plane (and not to any other voltage level).

# 7. Electrical Specification

All voltages are referenced to ground (GND). Positive currents flow into the IC.

The absolute maximum ratings (in accordance with IEC 60 134) given in the table below are limiting values that do not lead to a permanent damage of the device but exceeding any of these limits may do so. Long term exposure to limiting values may affect the reliability of the device.

# 7.1. Operating Conditions

| Nr. | Parameter                                      | Symbol               | Min  | Max  | Unit | Remark                       |

|-----|------------------------------------------------|----------------------|------|------|------|------------------------------|

| 101 | Battery supply voltage [1] [2]                 | Vs                   | 5    | 27   | V    |                              |

| 102 | Extended battery supply voltage                | Vs_NON_OP            | 5    | 40   | V    | Parameter deviations allowed |

| 103 | Operating ambient temperature                  | T <sub>amb</sub>     | -40  | +125 | °C   |                              |

| 104 | Voltage on low voltage I/Os (RxDx, TxDx, MODEx | RxDx, TxDx,<br>MODEx | -0.3 | 5.5  | V    |                              |

Table 2: Operating Conditions

<sup>[1]</sup> Vs is the IC supply voltage including voltage drop of reverse battery protection diode, V<sub>DROP</sub> = 0.4 to 1V,

<sup>[2]</sup> Operating voltage range of the LIN2.x/SAE J2602 plug & play specification is 7V...18V

# 7.2. Absolute Maximum Ratings

Table 3: Absolute Maximum Ratings

| Nr. | Parameter                                               | Symbol                                        | Condition                                                                     | Min        | Max                  | Unit |

|-----|---------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------|------------|----------------------|------|

| 201 | Battery Supply Voltage                                  | Vs                                            | Respective to GND                                                             | -0.3       | 40                   | V    |

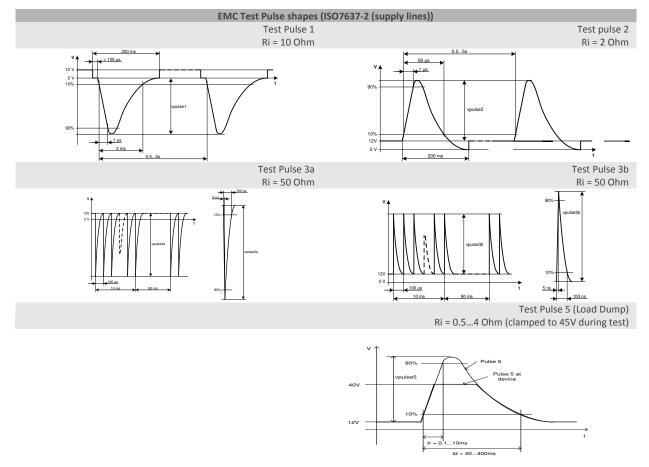

| 202 | Transients at battery supply voltage                    | V <sub>VS.tr1</sub>                           | ISO 7637/2 pulse 1 <sup>[1]</sup>                                             | -100       |                      | V    |

| 203 | Transients at battery supply voltage                    | V <sub>VS.tr2</sub>                           | ISO 7637/2 pulse 2 <sup>[1]</sup>                                             |            | 75                   | V    |

| 204 | Transients at high voltage signal pins                  | V <sub>LINtr1</sub>                           | ISO 7637/3 pulses 1 <sup>[2]</sup>                                            | -30        |                      | V    |

| 205 | Transients at high voltage signal pins                  | V <sub>LINtr2</sub>                           | ISO 7637/3 pulses 2 <sup>[2]</sup>                                            |            | 30                   | V    |

| 206 | Transients at high voltage signal and power supply pins | V <sub>HVtr3</sub>                            | ISO 7637/2 pulses 3A, 3B [3]                                                  | -150       | 100                  | V    |

| 207 | DC voltage LINx                                         | V <sub>LIN_DC</sub>                           | Respective to GND and Vs<br>Loss of Ground(V <sub>GND</sub> =V <sub>S</sub> ) | -20<br>-30 | 40<br>40             | V    |

| 208 | DC voltage WAKE                                         | V <sub>WAKE_DC</sub>                          | Respective to GND and Vs<br>Loss of Ground(V <sub>GND</sub> =V <sub>S</sub> ) | -20<br>-30 | 40<br>40             | v    |

| 209 | DC voltage INH, DIS_MAS                                 | V <sub>INH_DC</sub><br>V <sub>DISMAS_DC</sub> |                                                                               | -0.3       | V <sub>S</sub> + 0.3 | v    |

| 210 | DC voltage low voltage I/O's (RxDx,TxDx,MODEx)          | V <sub>Iv_DC</sub>                            |                                                                               | -0.3       | 7                    | V    |

| 211 | ESD voltage, IEC 61000-4-2 <sup>[4]</sup>               | V <sub>ESD</sub>                              | Pin LIN, VS, WAKE                                                             | -10        | 10                   | kV   |

| 212 | ESD voltage, HBM (CDF-AEC-Q100-002)                     | VESD                                          | Pin LIN, V <sub>s.</sub> WAKE, INH<br>vs GND                                  | -8         | 8                    | kV   |

| 212 | ESD Vollage, HBIVI (CDF-AEC-Q100-002)                   | VESD                                          | All other pins                                                                | -3         | 3                    | kV   |

| 213 | ESD voltage, CDM (CDF-AEC-Q100-011)                     | V <sub>ESD</sub>                              |                                                                               | -1000      | 1000                 | V    |

| 214 | Maximum latch - up free current at any Pin              | Ilatch                                        |                                                                               | -500       | 500                  | mA   |

| 215 | Thermal impedance                                       | Θja                                           | JEDEC 1s2p board                                                              |            | 50                   | K/W  |

| 216 | Storage temperature                                     | T <sub>stg</sub>                              |                                                                               | -55        | 150                  | °C   |

| 217 | Junction temperature                                    | T <sub>vj</sub>                               |                                                                               | -40        | 150                  | °C   |

ISO 7637/2 test pulses are applied to VS via a reverse polarity diode and >10  $\mu$  blocking capacitor. [1]

[2] [3] ISO 7637/3 test pulses are applied to LIN via a coupling capacitance of 100nF.

ISO 7637/3 test pulses are applied to LIN via a coupling capacitance of 1nF. ISO 7637/2 test pulses are applied to VS via a reverse polarity diode and >10uF blocking capacitor

[4] IEC 61000-4-2 validated by external Lab during product qualification (see application examples)

## 7.3. Static Characteristics

#### Table 4: Static Characteristics

Unless otherwise specified all values in the following tables are valid for  $V_s = 5$  to 27V and  $T_j = -40$  to 150°C. All voltages are referenced to ground (GND), positive currents flow into the IC.

| Nr.     | Parameter                                                                       | Symbol                   | Condition                                                                                                                                                                   | Min    | Тур  | Max    | Unit |  |

|---------|---------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--------|------|--|

| PIN VS  |                                                                                 |                          |                                                                                                                                                                             |        |      |        |      |  |

| 301     | Undervoltage lockout                                                            | Vs_uv                    |                                                                                                                                                                             | 2.4    |      | 4.8    | V    |  |

| 302     | Undervoltage lockout hysteresis <sup>[1]</sup>                                  | Vs_Uv_hys                |                                                                                                                                                                             | 0.1    | 0.3  | 0.7    | V    |  |

| 303     | Supply current, sleep mode                                                      | I <sub>Ssi</sub>         | $V_{MODEx} = 0V, Tj \le 85C$ $V_{WAKE} = V_{LINx} = V_S \le 14V$                                                                                                            |        | 9    | 15     | μA   |  |

|         |                                                                                 | 00                       | $V_{MODex} = 0V, Tj \le 125C$<br>$V_{WAKE} = V_{LINx} = V_S \le 18V$                                                                                                        |        |      | 20     | μA   |  |

| 304     | Supply current standby mode                                                     | Isby                     | V <sub>M0Dex</sub> = 0V,<br>after POR or WU                                                                                                                                 | 100    | 200  | 400    | μA   |  |

| 305     | Supply current active mode, dominant                                            | I <sub>Sd slave</sub>    | $V_{M0Dex} = 5V, V_{TxD1-4} = 0V$<br>DIS_MAS = Vs (80004)                                                                                                                   |        | 12   | 15     | mA   |  |

|         | Standard transceiver mode                                                       |                          | $V_{M0Dex} = 5V, V_{TxD1-2} = 0V$<br>DIS_MAS = Vs (80002)                                                                                                                   |        | 7    | 9      |      |  |

| 306     | Supply current active mode, dominant                                            | I <sub>Sd master</sub>   | $V_{M0Dex} = 5V, V_{TxD1-4} = 0V$<br>DIS_MAS = 0V (80004)                                                                                                                   |        | 100  | 125    | mA   |  |

| 500     | Enhanced master mode                                                            | ISo_master               | $V_{M0Dex} = 5V, V_{TxD1-2} = 0V$<br>DIS_MAS = 0V (80002)                                                                                                                   |        | 50   | 65     | mA   |  |

| 307     | Supply current active mode, recessive                                           | I <sub>Sr</sub>          | $V_{\text{M0Dex}} = 5V, V_{\text{TxD1-4}} = 5V$                                                                                                                             |        | 3    | 5      | mA   |  |

| PIN LIN | lx – Transmitter                                                                |                          |                                                                                                                                                                             |        |      |        |      |  |

| 310     | Transmitter internal capacitance <sup>[1]</sup>                                 | CLIN                     | Capacitance on pins LINx to GND                                                                                                                                             |        | 30   | 40     | pF   |  |

| 311     | Short circuit bus current                                                       | I <sub>BUS_LIM</sub>     | $\label{eq:VLIN} \begin{split} V_{\text{LIN}} &= V_{\text{S}}, \\ V_{\text{MODex}} &= 5V, V_{\text{TxDx}} = 0V \end{split}$                                                 | 40     | 100  | 200    | mA   |  |

| 312     | Pull up resistance bus, normal & standby mode                                   | R <sub>SLAVE</sub>       | $V_{\text{DIS}_{MAS}} = V_{S}$                                                                                                                                              | 20     | 30   | 60     | kΏ   |  |

| 313     | Pull up resistance bus, normal & standby mode                                   | R <sub>Master</sub>      | $V_{\text{DIS}\_\text{MAS}} = 0V$                                                                                                                                           | 900    | 1000 | 1100   | Ω    |  |

| 314     | Pull up current bus, sleep mode                                                 | I <sub>SLAVE_SLEEP</sub> | $\label{eq:VLINx} \begin{split} V_{\text{LINx}} &= 0V, \ V_{\text{S}} = 12V, \\ V_{\text{M0Dex}} &= 0V, \\ V_{\text{TxDx}} = 5V \end{split}$                                | -100   | -60  | -20    | μA   |  |

| 315     | Voltage drop at int. diode in pull up path<br>R <sub>SLAVE</sub> <sup>[1]</sup> | V <sub>SerDiode</sub>    |                                                                                                                                                                             | 0.4    |      | 1      | V    |  |

| 316     | Receiver dominant input leakage current including pull up resistor              | IBUS_PAS_dom             | $\label{eq:VLINx} \begin{array}{l} V_{LINx} = \! 0V, \ V_S = \! 12V, \\ V_{M0Dex} = 5V, V_{TxDx} = 5V, \\ V_{DIS\_MAS} = V_S \end{array}$                                   | -400   |      |        | μA   |  |

| 317     | Receiver recessive input leakage current                                        | IBUS_PAS_rec             | $\label{eq:VLINx} \begin{split} V_{\text{LINx}} = 18V, V_{\text{S}} = 5V, \\ V_{\text{M0Dex}} = 5V, V_{\text{TxDx}} = 5V, \\ \text{Tamb} < 125^{\circ}\text{C} \end{split}$ |        |      | 20     | μA   |  |

| 318     | Bus reverse current loss of battery [2]                                         | I <sub>BUS_NO_BAT</sub>  | V <sub>S</sub> = 0V,<br>0V < V <sub>LIN x</sub> < 18V<br>Tamb<125°C                                                                                                         |        |      | 20     | μA   |  |

| 319     | Bus current during loss of ground [2]                                           | I <sub>BUS_NO_GND</sub>  | $\label{eq:VS} \begin{split} V_S &= V_{GND} = 12V, \\ 0 &< V_{LINx} < 18V \end{split}$                                                                                      | -10    |      | 50     | μA   |  |

| 320     | Transmitter dominant voltage [2]                                                | Volue                    | Rload = 500 $\Omega$ , V <sub>S</sub> = 5V                                                                                                                                  | 0      |      | 1.2    | v    |  |

| 320     |                                                                                 | Vol <sub>BUS</sub>       | Rload = 500 $\Omega$ , V <sub>S</sub> >= 7V                                                                                                                                 | 0      |      | 0.2×Vs | v    |  |

| 321     | Transmitter recessive voltage [2]                                               | Voh <sub>BUS</sub>       | $V_{\text{M0Dex}} = 0/5V, V_{\text{TxDx}} = 5V$                                                                                                                             | 0.8×Vs |      | 1×Vs   | V    |  |

#### MLX80002/MLX80004

#### Enhanced Universal Dual/Quad LIN Transceiver Datasheet

| Me | lexis       |

|----|-------------|

|    | ENGINEERING |

| Nr.     | Parameter                          | Symbol                  | Condition                                                          | Min      | Тур    | Max                  | Unit |

|---------|------------------------------------|-------------------------|--------------------------------------------------------------------|----------|--------|----------------------|------|

| PIN LIN | x – Receiver                       |                         |                                                                    |          |        |                      |      |

| 322     | Receiver dominant voltage          | V <sub>BUSdom</sub>     |                                                                    |          |        | 0.4×Vs               | V    |

| 323     | Receiver recessive voltage         | V <sub>BUSrec</sub>     |                                                                    | 0.6×Vs   |        |                      | V    |

| 324     | Center point of receiver threshold | V <sub>BUS_CNT</sub>    | $V_{BUS_{cnt}} = (V_{BUSdom} + V_{BUSrec})/2$                      | 0.475×Vs | 0.5×Vs | 0.525×V <sub>s</sub> | V    |

| 325     | Receiver hysteresis                | V <sub>HYS</sub>        | $V_{HYS} = (V_{BUSrec} - V_{BUSdom})$                              |          |        | 0.175×Vs             | V    |

| PIN MO  | DE0/1, TxD2/3/4                    |                         |                                                                    |          |        |                      |      |

| 331     | High level input voltage           | V <sub>ih_xx</sub>      | Rising edge                                                        | 2        |        |                      | V    |

| 332     | Low level input voltage            | V <sub>il_xx</sub>      | Falling edge                                                       |          |        | 0.8                  | V    |

| 333     | pull down resistor                 | R <sub>pd_xx</sub>      | V <sub>ih_xx</sub> = 5V                                            | 200      | 350    | 600                  | kΩ   |

| 334     | Leakage Current                    | l <sub>leak_xx</sub>    | V <sub>il_xx</sub> = 0V                                            | -5       |        | 5                    | μA   |

| PIN TxE | D1                                 |                         |                                                                    |          |        |                      |      |

| 341     | High level input voltage           | V <sub>ih_TxD1</sub>    | Rising edge                                                        | 2        |        |                      | V    |

| 342     | Low level input voltage            | V <sub>il_TxD1</sub>    | Falling edge                                                       |          |        | 0.8                  | V    |

| 343     | pull down resistor                 | R <sub>pd_TxD1</sub>    | V <sub>TxD1</sub> = 5V                                             | 200      | 350    | 600                  | kΩ   |

| 344     | Low level output voltage           | Vol_txd1                | I <sub>TxD1</sub> = 2mA<br>Local WU flag                           |          |        | 0.6                  | V    |

| 345     | Leakage Current                    | I <sub>leak_TxD1</sub>  | $V_{TxD1} = 0V$                                                    | -5       |        | 5                    | μA   |

| PIN Rx[ | Лх                                 |                         | <u> </u>                                                           |          |        |                      |      |

| 351     | Low level output voltage           | V <sub>ol_rxdx</sub>    | I <sub>RxDx</sub> = 2mA                                            |          |        | 0.6                  | V    |

| 352     | Leakage Current high               | l <sub>leakh_rxdx</sub> | $V_{\text{RxDx}} = 5V, V_{\text{TxDx}} = 5V, V_{\text{M0/1}} = 5V$ | -5       |        | 5                    | μA   |

| 353     | Leakage Current low                | l <sub>leakl_rxdx</sub> | $V_{RxDx} = 0V, V_{TxDx} = 5V, V_{M0Dex}$<br>= 5V                  | -5       |        | 5                    | μA   |

| PIN INH | 1                                  | I                       |                                                                    | I        |        | <u> </u>             |      |

| 361     | On resistance INH                  | Ron_INH                 | V <sub>S</sub> =12V, T <sub>j</sub> ≤125°C                         |          | 20     | 50                   | Ω    |

| 362     | Leakage current INH high           | Ileakh_inh              | $V_{M0Dex} = 0V, V_{INH} = 27V$                                    | -5       |        | 5                    | μA   |

| 363     | Leakage current INH low            | lleakl_inh              | $V_{\text{MODex}} = V_{\text{INH}} = 0V,$                          | -5       |        | 5                    | μA   |

| PIN WA  | PIN WAKE                           |                         |                                                                    |          |        |                      |      |

| 371     | High level input voltage           | Vih_WAKE                | Sleep mode                                                         | Vs-1V    |        |                      | V    |

| 372     | Low level input voltage            | V <sub>II_WAKE</sub>    | Sleep mode                                                         |          |        | V <sub>S</sub> -3.3V | V    |

| 373     | Pull up current WAKE               | I <sub>WAKE_PU</sub>    | V <sub>WAKE</sub> = 0                                              | -30      | -10    | -1                   | μA   |

| 374     | Leakage current WAKEhigh           | Iwake_ik                | V <sub>WAKE</sub> = V <sub>S</sub> =27V                            | -5       |        | 5                    | μA   |

#### MLX80002/MLX80004

#### Enhanced Universal Dual/Quad LIN Transceiver Datasheet

| Nr.        | Parameter                         | Symbol                   | Condition                                 | Min | Тур | Max                  | Unit |

|------------|-----------------------------------|--------------------------|-------------------------------------------|-----|-----|----------------------|------|

| PIN DIS    | S_MAS                             |                          |                                           |     |     |                      |      |

| 381        | High level input voltage          | Vih_DIS_MAS              | Active modes                              | 4   |     | V <sub>S</sub> +0.3V | V    |

| 382        | Low level input voltage           | Vil_dis_mas              | Active modes                              |     |     | 1.9                  | V    |

| 383        | Pull down current DIS_MAS         | Idis_mas_pd              | Active modes                              |     | 50  | 60                   | μA   |

| 384        | Leakage current DIS_MAS_low       | I <sub>DIS_MAS_IKI</sub> | $V_{DIS_{MAS}} = 0V$                      | -5  |     | 5                    | μA   |

| 385        | Leakage current DIS_MAS_high      | IDIS_MAS_lkh             | V <sub>DIS_MAS</sub> = 27V,<br>sleep mode | -5  |     | 5                    | μA   |

| Therma     | al Protection                     |                          |                                           |     |     |                      |      |

| 391        | Thermal shutdown <sup>[1]</sup>   | T <sub>sd</sub>          |                                           | 155 | 170 | 190                  | °C   |

| 392        | Thermal hysteresis <sup>[1]</sup> | T <sub>hys</sub>         |                                           |     | 10  | 30                   | °C   |

| [1]<br>[2] |                                   |                          |                                           |     |     |                      |      |

# 7.4. Dynamic Characteristics

#### Table 5: Dynamic Characteristics

Unless otherwise specified all values in the following table are valid for  $V_{S}$  = 5 to 27V and  $T_{j}$  = -40 to  $150^{o}C.$

| Nr. | Parameter                                           | Symbol                   | Condition                                                        | Min   | Тур | Max   | Unit |

|-----|-----------------------------------------------------|--------------------------|------------------------------------------------------------------|-------|-----|-------|------|

| 401 | Propagation delay receiver [1]                      | trx_pdf                  | $C_{RxD} = 25 pF$ falling edge                                   |       |     | 6     | μs   |

| 402 | Propagation delay receiver [1]                      | t <sub>rx_pdr</sub>      | $C_{RxD}$ =25pF rising edge                                      |       |     | 6     | μs   |

| 403 | Propagation delay receiver symmetry                 | t <sub>rx_sym</sub>      | Calculate trx_pdf - trx_pdr                                      | -2    |     | 2     | μs   |

| 404 | Receiver debounce time [2]                          | t <sub>rx_deb</sub>      | LIN rising & falling edge                                        | 0.5   |     | 4     | μs   |

| 411 | LIN duty cycle 1 [2] [3] [5]                        | D1                       | 20kbps operation,<br>normal mode<br>Vs = 7 to 18V                | 0.396 |     |       |      |

| 412 | LIN duty cycle 2 [2] [3] [5]                        | D2                       | 20kbps operation,<br>normal mode<br>Vs = 7 to 18V                |       |     | 0.581 |      |

| 413 | LIN duty cycle 3 <sup>[2] [3] [5]</sup>             | D3                       | 10.4kbs operation,<br>low speed mode<br>Vs = 7 to 18V            | 0.417 |     |       |      |

| 414 | LIN duty cycle 4 [2] [3] [5]                        | D4                       | 10.4kbs operation,<br>low speed mode<br>Vs = 7 to 18V            |       |     | 0.590 |      |

| 415 | trec(max) — t <sub>DOM(MIN)</sub> <sup>[4][5]</sup> | ∆t3                      | 10.4kbs operation,<br>low speed mode                             |       |     | 15.9  | μs   |

| 416 | tdom(max) - trec(min) <sup>[4]</sup> [5]            | ∆t4                      | 10.4kbs operation,<br>low speed mode                             |       |     | 17.28 | μs   |

| 421 | Remote Wake-up filter time                          | t <sub>wux_remote</sub>  | sleep mode,<br>LIN dominant time before<br>rising edge           | 30    |     | 150   | μs   |

| 422 | Local Wake-up filter time                           | t <sub>wu_local</sub>    | sleep mode,<br>WAKE falling edge                                 | 10    |     | 50    | μs   |

| 431 | Delay from Standby to Sleep Mode                    | t <sub>dsleep</sub>      | V <sub>MODEx</sub> = 0                                           | 150   |     | 500   | ms   |

| 432 | TxDx dominant time out time                         | t <sub>TxDx_to</sub>     | active modes,<br>V <sub>TxDx</sub> = 0                           | 27    |     | 60    | ms   |

| 433 | RxDx dominant time out time                         | T <sub>RxDx_to</sub>     | active modes,<br>V <sub>LINx</sub> = 0, V <sub>DIS_MAS</sub> = 0 | 27    |     | 60    | ms   |

| 441 | MODEx – debounce time                               | T <sub>MODE_deb</sub>    | active ←> sleep mode<br>transitions                              | 1     | 2   | 5     | μs   |

| 442 | DIS_MAS – debounce time                             | T <sub>DIS_MAS_deb</sub> | master                                                           | 1     | 2   | 5     | μs   |

This parameter is tested by applying a square wave signal to the LIN. The minimum slew rate for the LIN rising and falling edges is 50V/us

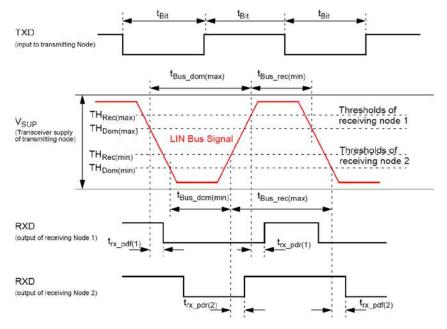

See Figure 4- LIN timing diagram

[3] Standard loads for duty cycle measurements are  $1K\Omega/1nF$ ,  $660\Omega/6.8nF$ ,  $500\Omega/10nF$ , internal master termination disabled

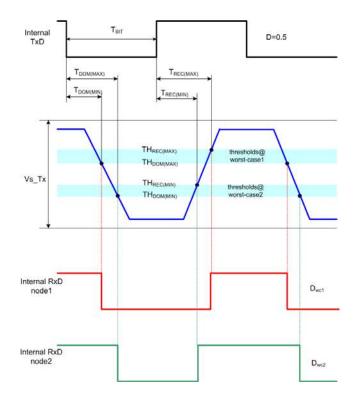

[4] in accordance to SAE J2602, see Figure 5

[5] for supply voltage ranges Vs=5...7V and Vs=18...27V parametric deviations are possible

## 7.4.1. Duty Cycle Calculation

Figure 4: LIN timing diagram (reference LIN2.1 specification)

Figure 4: LIN timing diagram, relation between propagation delay and duty cycle (reference SAE J2602 specification)

As shown in Figure 4, both worst case duty cycles can be calculated as follows :

```

\begin{aligned} D_{wc1} &= t_{BUS\_rec(min)} \, / \, (2 \, t_{Bit}) \\ D_{wc2} &= t_{BUS\_rec(max)} \, / \, (2 \, t_{Bit}) \end{aligned}

```

Thresholds for duty cycle calculation for the plug & play specification in accordance to LIN2.0 / SAE J2602:

| Baud rate              | 20kBd                     | 10.4kBd                   |

|------------------------|---------------------------|---------------------------|

| T <sub>BIT</sub>       | 50µs                      | 96µs                      |

| D <sub>wc1</sub>       | D1                        | D3                        |

| D <sub>wc2</sub>       | D2                        | D4                        |

| TH <sub>REC(MAX)</sub> | $0.744 \times V_{S_TX}$   | $0.778 \times V_{S_TX}$   |

| TH <sub>DOM(MAX)</sub> | 0.581 × V <sub>S_TX</sub> | 0.616 × V <sub>S_TX</sub> |

| TH <sub>REC(MIN)</sub> | 0.422 × V <sub>S_TX</sub> | 0.389 × V <sub>S_TX</sub> |

| TH <sub>DOM(MIN)</sub> | $0.284 \times V_{S_TX}$   | $0.251 \times V_{S_TX}$   |

Table 6: Data Transmission Rates

# 8. Functional Description

The MLX80004/2 is the physical layer interface between the master/slave microcontroller and the single wire LIN bus network.

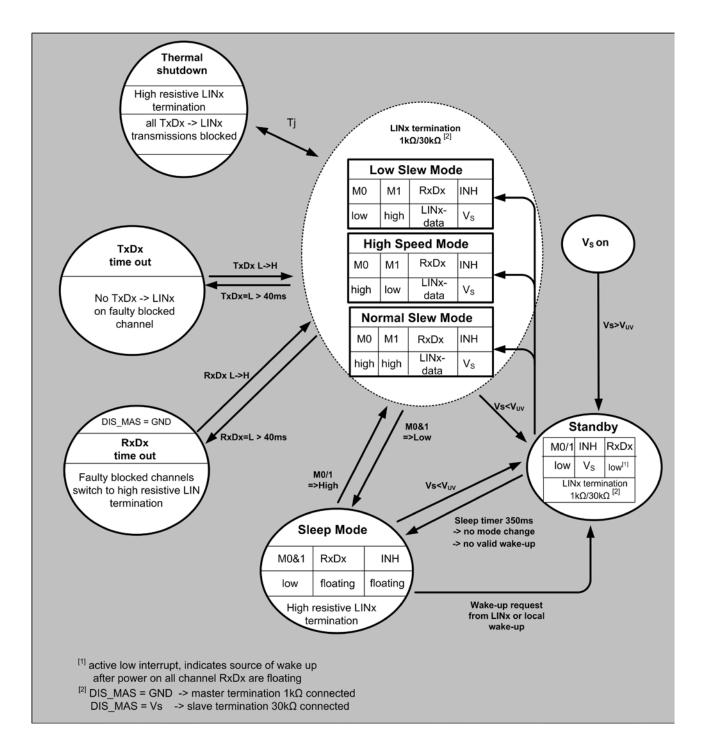

*Figure 5: State Diagram of the MLX80004/2*

# 8.1. Operating Modes

#### Table 7: Operating Modes

| Mode    | MODE0       | MODE1       | TxDx                                             | RxDx                                | INH      | LIN transceiver   |

|---------|-------------|-------------|--------------------------------------------------|-------------------------------------|----------|-------------------|

| Standby | 0           | 0           | weak pulldown/ active low [1]                    | floating/ active low <sup>[2]</sup> | Vs       | Off               |

| Active  | 1<br>1<br>0 | 1<br>0<br>1 | weak pulldown/ input<br>for transmit data stream | output for LIN data stream          | Vs       | On<br>[3] [4] [5] |

| Sleep   | 0           | 0           | weak pull down                                   | floating                            | floating | Off               |

[1] Indicates the wake up flag in case of local wake up

[2] After power on RxDx is floating. If any wake up(local or remote) occurs it will be indicated by active low

[3] Active low interrupt at pin RxD will be removed when entering normal mode

[4] Wake up source flag at pin TxD1 will be removed when entering normal mode

[5] Active modes will be entered by a low -> high transition on pin MODEx. When recessive level (high) on pin TxDx is present the transmit path will be enabled

## 8.2. Initialization and Standby mode

When the battery supply voltage Vs exceeds the specified threshold  $V_{S_{UV}}$ , the MLX80004/2 automatically enters an intermediate standby mode. The INH output becomes HIGH (Vs) and can be used for a battery driven interrupt or to switch on an external ECU – voltage regulator. The pins RxDx are floating and the integrated master (slave) pull up resistor with decoupling diode pulls the pin LIN. The transmitter and the receiver are disabled.

If no mode change occurs to any active mode via a MODEO/1 LOW to HIGH transition within the time stated (typically 350ms), the IC enters the most power saving sleep mode and the INH output will become floating (logic 0).

Furthermore the standby mode will be entered after a valid local or remote wake up event, when the MLX80004/2 is in sleep mode. The entering of the standby mode after wake up will be indicated by an active LOW interrupt on pin RxDx.

The MLX80004/2 enters the standby mode as well in case of a battery under-voltage condition. That happens while being in sleep mode or any active mode.

## 8.3. Active Modes

By entering the active modes the MLX80004/2 can be used as interface between the single wire LIN bus and the microcontroller. The incoming bus traffic is detected by the receiver and transferred via the RxDx output pin to the microcontroller. (see Figure 4, LIN timing diagram)

The active modes can be entered being in sleep or standby mode, when the pin(s) MODE0/1 are driven HIGH.

| MODE0 | MODE1 | Mode                                         |

|-------|-------|----------------------------------------------|

| L     | L     | Sleep Mode                                   |

| н     | L     | High Speed Mode (slew rate control disabled) |

| L     | н     | Low speed mode                               |

| Н     | Н     | Normal Mode                                  |

Table 8: Mode Selection Table

#### 8.3.1. High Speed mode

This mode allows high speed data download up to 100Kbit/s. The slew rate control is disabled. The falling edge is the active driven edge, the speed of the rising edge is determined by the network time constant.

#### 8.3.2. Low speed mode

This mode is the recommended operating mode for J2602 applications with a maximum baud rate of 10.4kBd. The slew rate control of any channel is optimized for minimum radiated noise, especially in the AM band.

#### 8.3.3. Normal speed mode

Transmission bit rate in normal mode is up to 20kbps. The slew rate control of any channel is optimized for maximum allowed bit rate in the LIN specification package 2.x.

## 8.4. Sleep Mode

The most power saving mode of the MLX80004/2 is the sleep mode. The mode change into sleep mode is possible regardless of the voltage levels on the LINx bus, pins WAKE or TxDx. The MLX80004/2 offers two procedures to enter the sleep mode:

- The sleep mode will be entered if both the pins MODE0 and MODE1 are being driven LOW for longer than the specified filter time (t<sub>MODE\_deb</sub>) when in active modes.

- If the MLX80004/2 is in standby mode after power-on or wake-up, a sleep counter is started and switches the transceiver into sleep mode after the specified time (typ. 350ms) if the microcontroller of the ECU will not confirm the active operation by setting MODE0/1 pins to logic HIGH. This feature allows faulty blocked LIN nodes to reach the most power saving sleep mode anyway.

Being in sleep mode the INH pin becomes floating and can be used to switch off the ECU voltage regulator in order to minimize the current consumption of the complete LIN node (preferred feature in slave applications). The transmitters are disabled and the pins RxDx are disconnected from the receive path and become floating. The master(slave) termination resistor (LIN pull up resistor with decoupling diode between pins LIN and Vs) is disconnected, only a weak LIN pull up current of typically 50uA is applied to the LINx bus (see chapter 9 Fail-safe Features)

## 8.5. Wake Up

When in sleep mode the MLX80004/2 offers three wake-up procedures:

- In applications with continuously powered ECU a wake up via mode transition to active modes is possible by setting the MODEx pins to high level. (see chapter 4.3 Active Modes)

- Remote wake-up via LINx bus request

After a falling edge on the LINx bus followed by a dominant voltage level for longer than the specified value(t<sub>wu\_remote</sub>) and a rising edge on pin LINx will cause a remote wake up (see Figure 6 at page 19)

- Local wake-up via a negative edge on pin WAKE

A negative edge on the pin WAKE and a dominant voltage level for longer than the specified time (t<sub>wu\_local</sub>) will cause a local wake-up. The current for an external switch has to be provided by an external pull up resistor R<sub>wK</sub>. For a reverse current limitation in case of a closed external switch and a negative ground shift or an ECU loss of ground a protection resistor R<sub>wK\_prot</sub> between pin WAKE and the switch is recommended. (see Figure 7 at page 20)

The pin WAKE provides a weak pull up current towards the battery voltage that provides a HIGH level on the pin in case of open circuit failures or if no local wake up feature is required. In such applications it is recommended to connect the pin WAKE to pin Vs via a resistor of 10k ohms.

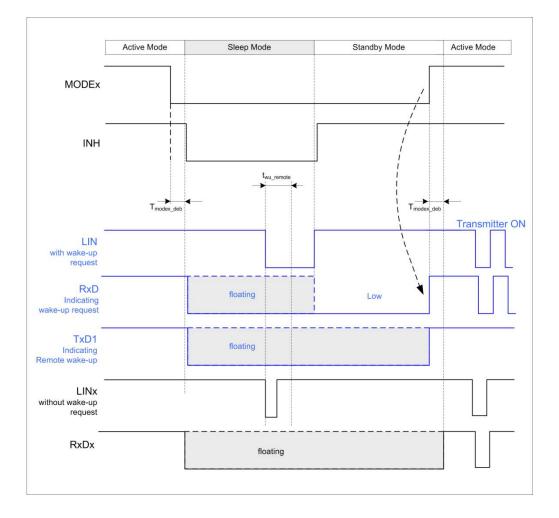

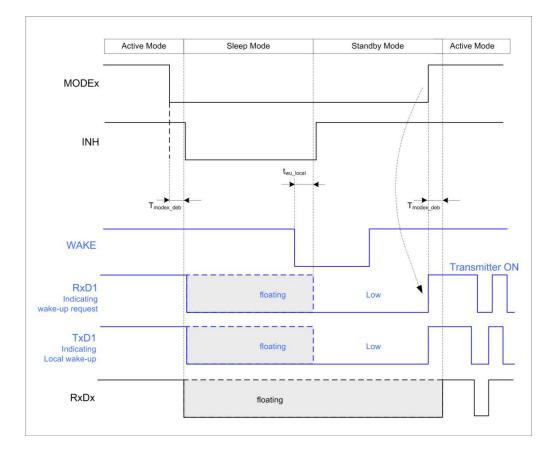

## 8.6. Wake Up Source Recognition

The device can distinguish between a local wake-up event (pin WAKE) and a remote wake-up event in dependence of the requesting LINx bus.

#### Local Wake Up

In case of a local wakeup via WAKE pin, the wake up request is indicated by an active LOW on pin RxD1. The wake-up source flag is set and is indicated by an active LOW on pin TxD1.

The wake-up source flag can be read if an external pull up resistor at TxD1 towards the microcontroller supply voltage has been added and the MLX80004/2 is still in standby mode:

When the microcontroller confirms an active mode operation by setting the pin MODE0/1 to HIGH, both the wake-up request on pin RxD1 as well as the wake-up source flag on pin TxD1 are reset immediately.

#### Remote Wake Up

In case of a remote wake-up via a LINx bus, the source of the wake-up request will be indicated by the RxDx pin that belongs to the LINx pin. (example: LOW level on RxD4 and floating RxD1-3 indicate a wake-up request on LIN4). The wake up source flag at TxD1 remains floating.

This allows following the wake-up request of the requesting LIN bus while remaining the other LIN bus channels in recessive mode (no wake up occurs in these LIN networks).

After a mode transition into any active mode by setting the pin MODE0/1 to HIGH, the active LOW wake-up request on pin RxDx is reset immediately.

If the device is not set into an active mode after a wake up request (either local or remote) then it will return into sleep mode after  $t_{dsleep}$ .

*Figure 6: remote wake up and wake-up source recognition*

Figure 7: local wake up and wake-up source recognition

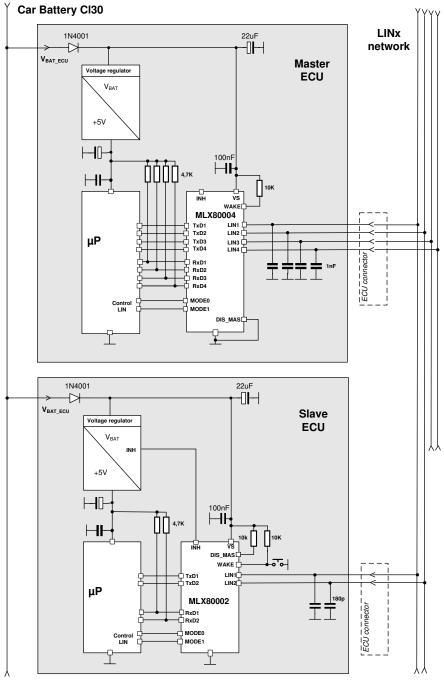

# 8.7. Master / Slave configuration

The target applications of the MLX80004/2 are BCM master modules with multiple LIN channels. In order to be able to use the same module for a wide variety of applications with different stages of extension, a space efficient and cost effective adaptation on the number of LIN channels is desired.

The MLX80004/2 device family offers the combination of quad and dual channel LIN transceiver within the same advanced package and a compatible foot print.

By the integration of the LIN master-termination (decoupling diode and 1K resistor) the external circuitry can be minimized in terms of space as well as BOM (bill of material). The RxD time-out feature allows the handling of a LIN short to ground failure without software support by the microcontroller. This application mode is called enhanced master mode, compatible to the functionality of the quad – LIN transceiver MLX80001.

In case of different BCM requirements it may happen that the *external* master termination is desired only. To cover these applications the pin DIS\_MAS has been introduced:

| DIS_MAS | Mode                         | LIN termination                                                 | Supported fail safe features                                                                                                                                                                         |

|---------|------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND     | Enhanced Master<br>Mode      | Active mode : Diode & $1k\Omega$ sleep mode :Diode & $60\mu A$  | <ul> <li>RxDx time-out, independent disconnect of master termination in case of LINx short to ground</li> <li>TxDx time-out, independent disable of faulty dominant blocked transmit path</li> </ul> |

| Vs      | Standard<br>Transceiver Mode | Active mode : Diode & $30k\Omega$ sleep mode :Diode & $60\mu A$ | <ul> <li>TxDx time-out, independent disable of faulty<br/>dominant blocked transmit path</li> </ul>                                                                                                  |

Table 9: Time Out Modes

In case of externally mounted master termination (standard transceiver mode), the handling of a LIN short to ground is not possible. By using the standard transceiver mode, the MLX80004/2 can be used in slave applications as well. To pull the pin DIS\_MAS to high even in case the external ECU regulator is switched off in sleep mode. The pin shall be connected to Vs via an external resistor. (see Figure 8 at page 24, application example) In the standard transceiver mode, only the TxDx time-out feature is enabled.

# 9. Fail-safe Features

#### 9.1. Loss of battery

If the ECU is disconnected from the battery, the bus pin is in high impedance state. There is no impact to the bus traffic and to the ECU itself. Reverse current is limited to <  $20\mu$ A

## 9.2. Loss of Ground

In case of an interrupted ECU ground connection there is no influence to the bus lines. The current from the ECU to the LINx pins is limited by the weak pull up current of the pin LINx, the integrated master termination (DIS\_MAS = GND) as well as the integrated slave termination (DIS\_MAS =  $V_s$ ) is disconnected in order to fulfill the SAE J2602 requirements for the loss of ground current (<100 $\mu$ A @12V).

## 9.3. Short circuit to battery

The transmitter output currents are limited to the specified value in case of short circuit to battery in order to prevent high current densities and thermal hot spots in the LIN drivers. In dependency of the ambient temperature as well as the battery voltage the junction temperature can exceed the specified value and a thermal overload condition occurs (see chapter 4.5)

### 9.4. Ground shift and short circuit to ground

If the LIN bus wiring is shorted to negative shifted ground levels, there is no current flow from the ECU ground to the LIN bus and no distortion of the bus traffic occurs.

A LIN bus short to ground condition can cause an undesired current flow. The MLX80004/ offers different opportunities to handle the LIN short to ground, see chapter 4.7.

#### 9.5. Thermal overload

The MLX80004 and the MLX80002 is protected against thermal overloads. If the chip junction temperature exceeds the specified value, all transmitters are disabled and the master termination is switched off in order to reduce the power consumption. The receiver is still working during the thermal shutdown state. The pins RxDx indicate the voltage level from the LINx pins also if the circuit is in thermal shut down. The circuit returns automatically to the normal mode after thermal recovery.

## 9.6. Undervoltage lock out

If the battery supply voltage is missing or decreased under the specified value ( $V_{S_{UV}}$ ), all transmitters are disabled to prevent undefined bus traffic.

While in sleep mode, the MLX80004/2 enters the standby mode if Vs drops below the internal power on reset threshold ( $V_{INH} = V_s$ ).

## 9.7. Open Circuit protection

- The pins TxDx provide a weak pull down. The transmitter cannot be enabled.

- The pins MODE0/MODE1 provide a weak pull down to prevent undefined active mode transitions.

- If the battery supply voltage is disconnected, the pins RxDx are floating

- The pin WAKE provides a weak pull up current towards supply voltage Vs to prevent local wake-up requests.

- The pin DIS\_MAS provides a pull down current of 50uA.

## 9.8. TxDx faulty start protection

After power-on or wake-up a dominant level on TxDx will not lead to a dominant LINx level if the IC is being switched into an active mode. Only in case of recessive level before applying the first dominant level the transmit path will be enabled.

## 9.9. RxDx dominant time-out

A dominant LINx level longer than the specified time (typ. 40ms) indicates a faulty blocked bus. The master pull-up resistor of the affected LIN channel will be disconnected from the network in order to prevent thermal overload conditions or failure currents from the battery without any intervention from the microcontroller. Only a weak pull-up current (typ.60uA) is applied on the LIN bus. The RxD time-out will be reset with the next dominant -> recessive transition on the LIN bus if the failure disappears.

The RxDx time-out is only active in the Enhanced Master Mode, while the master termination is enabled.

## 9.10. TxDx dominant time-out

In case of a faulty blocked permanent dominant level on pin TxDx the transmit path will be disabled after the specified time  $t_{TxDx_{to}}$  (typ. 40ms). The data transmission is released again as soon as the failure disappears by the next rising edge of TxDx.

The TxDx time-out is active in both, the *Standard Transceiver* and *Enhanced Master Mode*.

# **10. Application Example**

## 10.1. Enhanced Master Mode

Figure 8:

Application example using enhanced master mode with minimized external components and LIN short to GND feature. <u>Note:</u> All pins of MLX80004/MLX80002 with "N.C." are internally not connected.

# 10.2. Standard Transceiver Mode

Figure 9:

Application example using standard transceiver mode without LIN short to GND feature. <u>Note:</u> All pins of MLX80004/MLX80002 with "N.C." are internally not connected.

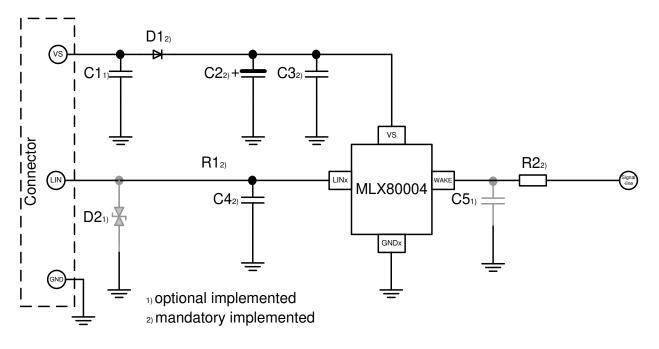

## 10.3. Application Circuitry for EMC

In order to minimize EMC influences, the external application circuitry shall be designed as followed:

Figure 10: Typical Application Circuitry for EMC

#### 10.3.1. External Circuitry on Supply Lines

In order to minimize EMC influences, the external application circuitry shall be designed as followed:

| Name | Mounting    | Min | Recommended | Max | Dim | Comment                                                    |

|------|-------------|-----|-------------|-----|-----|------------------------------------------------------------|

| C1   | recommended | -   | 100         | -   | nF  | Ceramic SMD: 10%, 0805,<br>≥50V;<br>close to the connector |

| D1   | mandatory   |     |             |     |     | Inverse-polarity protection diode                          |

| C2   | mandatory   | 1   | 22          | 100 | μF  | Tantal SMD: 10%, 7343, 35V                                 |

| C3   | mandatory   | -   | 100         | -   | nF  | Ceramic SMD: 10%, 0805,<br>≥50V;<br>close to the pin       |

Table 10: External Components on Supply Lines

#### 10.3.2. External Circuitry on LIN Lines

In order to minimize EMC influences, the external application circuitry shall be designed as followed:

| Name | Mounting  | Min | Recommended | Max | Dim | Comment                                                                                                                                                       |

|------|-----------|-----|-------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D2   | no        | -   | PESD1LIN    | -   |     | ESD protection Diode: SOD323 close to the connector;                                                                                                          |

| C4   | mandatory | -   | 220/1000    | -   | pF  | Ceramic SMD: 10%, 0805, ≥50V;<br>C <sub>Slave</sub> ≤ C <sub>D2</sub> +C <sub>4</sub> +C <sub>IC</sub><br>C <sub>Slave</sub> ≤250pF/ C <sub>Master</sub> ≤1nF |

Table 11: External Components on LIN Lines

#### 10.3.3. External Circuitry on Signal Lines

In order to minimize EMC influences, the external application circuitry shall be designed as followed:

| N | lame | Mounting  | Min | Recommended | Max  | Dim | Comment                       |

|---|------|-----------|-----|-------------|------|-----|-------------------------------|

|   | C5   | no        | 0.1 | 1           | 100  | nF  | Ceramic SMD: 10%, 0805, ≥50V; |

|   | R2   | mandatory | 5k  | 10k         | 100k | Ω   | Serial resistor: 0805         |

Table 12: External Components on Signal Lines

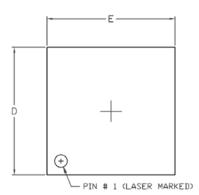

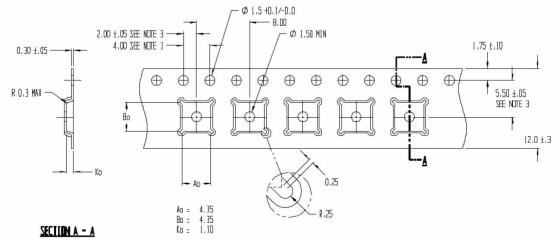

# **11. Package Mechanical Specification**

The devices are assembled in a QFN4x4 24L package with wettable flanks.

A

COMMON DIMENSIONS AND TOLERANCES

| S                | ALL DIMENSION ARE IN MILLIMETERS |             |         |  |  |  |  |  |

|------------------|----------------------------------|-------------|---------|--|--|--|--|--|

| M<br>B<br>O<br>L | MINIMUM                          | NOMINAL     | MAXIMUM |  |  |  |  |  |

| A                | 0.80                             | 0.90        | 1.00    |  |  |  |  |  |

| A1               | 0                                | 0 0.02 0.05 |         |  |  |  |  |  |

| A3               | 0.20 REF                         |             |         |  |  |  |  |  |

| D                | 3.90                             | 4.00        | 4.10    |  |  |  |  |  |

| E                | 3.90                             | 4.00        | 4.10    |  |  |  |  |  |

| D2               | 2.35                             | 2.45        | 2.55    |  |  |  |  |  |

| E2               | 2.35                             | 2.45        | 2.55    |  |  |  |  |  |

| L                | 0.30                             | 0.40        | 0.50    |  |  |  |  |  |

| К                | 0.20                             |             |         |  |  |  |  |  |

| b                | 0.18                             | 0.25        | 0.30    |  |  |  |  |  |

| e                | 0.50 BSC                         |             |         |  |  |  |  |  |

#### NOTE : 1. EXPOSED TIE BAR SHOULD BE KEPT FREE FROM SOLDER. 2. (OPTIONAL) SIDE WALL IMMERSION TIN PLATING MIN 1um THICK.

*Figure 11: Package outline drawing and dimensions*

| Package | ⊖jc [°C/W] | Oja [°C/W]<br>(JEDEC 1s0p board) | ⊖ja [°C/W]<br>(JEDEC 1s2p board) |

|---------|------------|----------------------------------|----------------------------------|

| QFN4x4  | 16         | 154                              | 50                               |

Table 13: Thermal resistance values of package

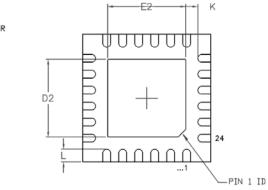

# **12. Package Marking Information**

Figure 12: Package marking, example for MLX80004 in QFN4x4 24L

#### MLX80002/MLX80004 **Enhanced Universal Dual/Quad LIN Transceiver**

Datasheet

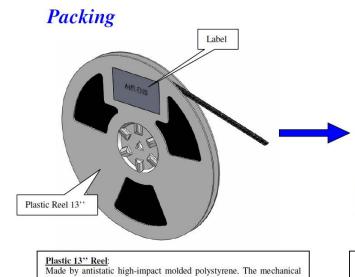

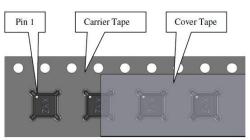

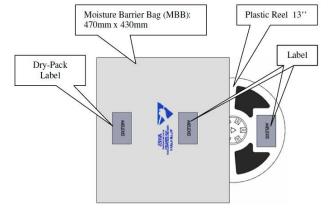

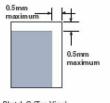

# **13. Tape and Reel Specification**

Remark: Pay attention to the marking orientation because it is used for component (pin1) orientation. Some devices may have different marking orientation, so please consult your Melexis contact person for more information.

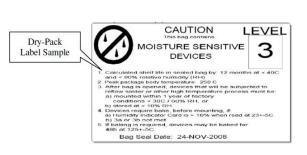

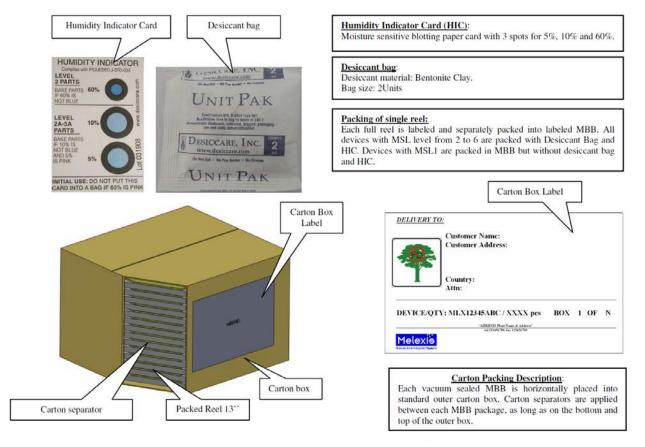

#### Packing Materials:

#### Embossed Plastic Carrier Tape:

Made by Tri-Laminate PS+C material (polystyrene with carbon). Typical carrier tape material thickness 0,21mm.

(11)Lot: A12345X1

#### Cover Tape:

Label Sample

All Cover Tapes used by Melexis are Heat Activated and antistatic. The main ABX type of Cover Tape is constructed in two layers, a 0.0254mm thick polyester base film covered by a 0.0279mm thick heatactivated adhesive coating layer.

MSL 3/245

Melexis

oc

#### Moisture Barrier Bag (MBB):

integrity of the reel is not affected by humidity.

Made in 5 different layers with total thickness of 0.18mm. At the core is a layer of polyester sandwiched between aluminum shields. The outside layer: dissipative polyester, innermost layer: static dissipative polyethylene.

Note: that the above mentioned labels are just examples which represent the label layout!

Enhanced Universal Dual/Quad LIN Transceiver Datasheet

| Parameter<br>Box Size (mm) | Carton pack     | ing type E02    |

|----------------------------|-----------------|-----------------|

|                            | Carton Box A    | Carton Box B*   |

| Box Size (mm)              | 450 x 420 x 260 | 450 x 420 x 160 |

| QTY/Reel                   | 5000pcs         | 5000pcs         |

| Reel Size                  | 13''            | 13''            |

| Reels/Box                  | 11pcs           | 6pcs            |

| QTY/Box                    | 55 000pcs       | 30 000pcs       |

| Weight/Box<br>(kg)         | 8               | 6               |

$\ensuremath{^{\circ}}$  Carton box B is used as last box in shipment, or when the shipping reel quantity is lower, or equal than 6 reels.

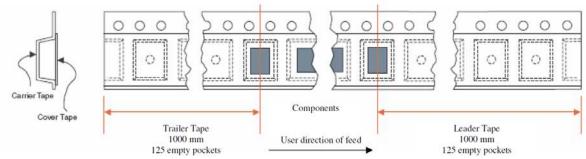

#### Leader and Trailer

## **Carrier Tape Data**

### **Component Rotation and Lateral Movement**

Sketch A (Side or Front Sectional View) Component Rotation

Sketch C (Top View) Component lateral movement

#### Plastic Reel Data

# 14. ESD and EMC

In order to minimize EMC influences, the PCB has to be designed according to EMC guidelines. The products MLX80004/2 are ESD sensitive devices and have to be handled according to the rules in IEC61340-5-2.

The products MLX80004/2 are evaluated according AEC-Q100-002 (HBM) and AEC-Q100-011 (CDM).

The extended ESD/EMC tests (acc. to IEC 61000-4-2, LIN Conf. Test Specification Package for LIN2.1, OEM hardware requirements for LIN, CAN and FlexRay Interfaces in automotive applications – Audi, BMW, Daimler, Porsche, Volkswagen - Rev. 1.3/2012) have been tested by external certificated test houses. The test reports are available on request.

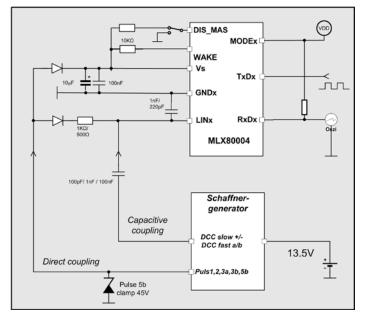

### 14.1. Automotive Qualification Test Pulses

Automotive test pulses are applied on the module in the application environment and not on the naked IC. Therefore attention must be taken, that only protected pins (protection by means of the IC itself or by means of external components) are wired to a module connector. In the recommended application diagrams, the reverse polarity diode together with the capacitors on supply pins, the protection resistors in several lines and the load dump protected IC itself will protect the module against the below listed automotive test pulses. The exact value of the capacitors for the application has to be figured out during design-in of the product according to the automotive requirements.

For the LIN pin the specification "LIN Physical Layer Spec 2.1 (Nov. 24, 2006)" is valid.

Supply Pin VS is protected via the reverse polarity diode and the supply capacitors. No damage will occur for defined test pulses. A deviation of characteristics is allowed during pulse 1 and 2; but the module will recover to the normal function after the pulse without any additional action. During test pulse 3a, 3b, 5 the module will work within characteristic limits.

## 14.2. Test Pulses On supply Lines

| Parameter                                                                                                                                                                                                                                          | Symbol                                                                                  | Min                  | Max                  | Dim | Coupling | test condition,<br>functional status                                                                                    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------|----------------------|-----|----------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Transient test pulses in accordance to ISO7637-2 (supply lines) &, VS=13.5V, TA=(23 ± 5)°C<br>& (Document: "Hardware Requirements for LIN, CAN and FlexRay Interfaces in Automotive Applications"; Audi, BMW, Daimler,<br>Porsche, VW; 2009-12-02) |                                                                                         |                      |                      |     |          |                                                                                                                         |  |  |  |

| Test pulse #1                                                                                                                                                                                                                                      | vpulse1                                                                                 | -100                 |                      | V   | Direct   | 5000 pulses,<br>functional state C                                                                                      |  |  |  |

| Test pulse #2                                                                                                                                                                                                                                      | vpulse2                                                                                 |                      | 75                   | V   | Direct   | 5000 pulses,<br>functional state A                                                                                      |  |  |  |

| Test pulse #3a                                                                                                                                                                                                                                     | vpulse3a                                                                                | -150                 |                      | V   | Direct   | 1h,functional state A                                                                                                   |  |  |  |

| Test pulse #3b                                                                                                                                                                                                                                     | vpulse3b                                                                                |                      | 100                  | V   | Direct   | 1h,functional state A                                                                                                   |  |  |  |

| Load dump test puls                                                                                                                                                                                                                                | Load dump test pulse in accordance to ISO7637-2 (supply lines), VS=13.0V, TA=(23 ± 5)°C |                      |                      |     |          |                                                                                                                         |  |  |  |

| Test pulse #5b                                                                                                                                                                                                                                     | vpulse5b                                                                                | 65<br>(+13V<br>(VS)) | 87<br>(+13V<br>(VS)) | V   | Direct   | 1 pulse clamped to 27V (+13V<br>(VS)),<br>(32V (+13V (VS))for<br>applications for north America),<br>functional state C |  |  |  |

Table 14: Test pulses Supply Line

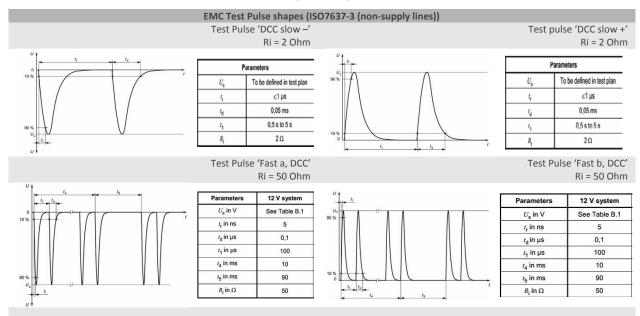

## 14.3. Test pulses on Pin LIN

| Parameter               | Symbol                                                                                                                                                                                                                            | Min  | Max | Dim | Coupling                               | test<br>condition,<br>functional<br>status |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|----------------------------------------|--------------------------------------------|--|--|--|

|                         | Transient test pulses in accordance to ISO7637-3, VS=13.5V, TA=(23 ± 5)°C<br>& (Document: "Hardware Requirements for LIN, CAN and FlexRay Interfaces in Automotive Applications"; Audi, BMW, Daimler,<br>Porsche, VW: 2009-12-02) |      |     |     |                                        |                                            |  |  |  |

| Test pulse 'DCC slow'   | Vpulse_<br>slow+                                                                                                                                                                                                                  | -100 |     | V   | Direct capacitive<br>coupled:<br>1nF   | 1000<br>pulses,<br>functional<br>state D   |  |  |  |

| Test pulse 'DCC slow +' | Vpulse_<br>slow-                                                                                                                                                                                                                  |      | 75  | V   | Direct capacitive<br>coupled:<br>1nF   | 1000<br>pulses,<br>functional<br>state D   |  |  |  |

| Test pulse 'DCC fast a' | Vpulse_<br>fast_a                                                                                                                                                                                                                 | -150 |     | V   | Direct capacitive<br>coupled:<br>100pF | 10 min,<br>functional<br>state D           |  |  |  |

| Test pulse 'DCC fast b' | Vpulse_<br>fast_b                                                                                                                                                                                                                 |      | 100 | V   | Direct capacitive<br>coupled:<br>100pF | 10 min,<br>functional<br>state D           |  |  |  |

Table 15: Test pulses LIN

## 14.4. Test pulses on signal lines

| Parameter                     | Symbol                                                                                   | Mi<br>n | Max | Dim | Coupling                           | test condition,<br>functional status |  |  |

|-------------------------------|------------------------------------------------------------------------------------------|---------|-----|-----|------------------------------------|--------------------------------------|--|--|

| Transient test pulses in acco | Transient test pulses in accordance to ISO7637-3 (signal lines). VS=13.5V, TA=(23 ± 5)°C |         |     |     |                                    |                                      |  |  |

| Test pulse 'DCC slow –'       | Vpulse_<br>slow+                                                                         | -30     | -8  | V   | Direct capacitive<br>coupled:100nF | 1000 pulses,<br>functional state C   |  |  |

| Test pulse 'DCC slow +'       | Vpulse_<br>slow-                                                                         | +8      | +30 | V   | Direct capacitive<br>coupled:100nF | 1000 pulses,<br>functional state A   |  |  |

| Test pulse 'DCC fast a'       | Vpulse_<br>fast_a                                                                        | -60     | -10 | V   | Direct capacitive<br>coupled:100pF | 10 min,<br>functional state A        |  |  |

| Test pulse 'DCC fast b'       | Vpulse_<br>fast_b                                                                        | 10      | 40  | V   | Direct capacitive<br>coupled:100pF | 10 min,<br>functional state A        |  |  |

Table 16: Test pulses signal lines

#### Description of functional state

- A: All functions of the module are performed as designed during and after the disturbance.

- B: All functions of the module are performed as designed during the disturbance:

One or more functions can violate the specified tolerances. All functions return automatically to within their normal limits after the disturbance is removed. Memory functions shall remain class A.

- C: A function of the module does not perform as designed during the disturbance but returns automatically to the normal operation after the disturbance is removed.

- D: A function of the module does not perform as designed during the disturbance and does not return automatically to the normal operation after the disturbances is removed.

The device needs to be reset by a simple operation/action to return to the specified limits/function.

## 14.5. Test circuitry for automotive transients

Figure 13: Test circuit for automotive transients

Figure 13 shows the general requirement on the test circuitry for applying automotive transient test pulses. In order to represent the most critical network impedance, the LINx pins has to be connected via 1kOhm / decoupling diode to the Schaffner test generator. Including the integrated master termination of 1kOhm, the minimum network resistance of 500Ohm can be simulated by adding an external 1Kohm resistor.

In slave application mode (DIS\_MAS = Vs), the external coupling has to be applied via 5000hm resistor.

# 14.6. EMC Test pulse definition