# SCR

The 2N1595 series of Silicon Controlled Rectifiers are planar-passivated, all-diffused, three junction, reverse blocking triode thyristors for low power switching and control applications. The 2N2322 series, which is also available, offers additional maximum specified electrical parameters.

- Painted external surface for maximum heat dissipation

- Single-ended package, ideal for printed circuit applications

- All-welded construction

- All-diffused, planar passivated

- Glass-to-metal seals

### MAXIMUM ALLOWABLE RATINGS

| ТҮРЕ   | REPETITIVE PEAK OFF-STATE VOLTAGE, $V_{\mathrm{DRM}}(1)$   | PEAK POSITIVE<br>ANODE VOLTAGE<br>PFV | REPETITIVE PEAK REVERSE VOLTAGE, V <sub>RRM</sub> |  |  |  |  |

|--------|------------------------------------------------------------|---------------------------------------|---------------------------------------------------|--|--|--|--|

|        | $T_{\rm c} = -65^{\circ}\text{C to} + 125^{\circ}\text{C}$ |                                       |                                                   |  |  |  |  |

| 2N1595 | 50 Volts*                                                  | 500 Volts                             | 50 Volts*                                         |  |  |  |  |

| 2N1596 | 100 Volts*                                                 | 500 Volts                             | 100 Volts*                                        |  |  |  |  |

| 2N1597 | 200 Volts*                                                 | 500 Volts                             | 200 Volts *                                       |  |  |  |  |

| 2N1598 | 300 Volts*                                                 | 500 Volts                             | 300 Volts*                                        |  |  |  |  |

| 2N1599 | 400 Volts*                                                 | 500 Volts                             | 400 Volts*                                        |  |  |  |  |

(1) Applies for 1000 ohms maximum, connected gate-to-cathode.

| RMS On-State Current, I <sub>T(RMS)</sub>                         | . 1.6 Amperes (all conduction angles)                                                                                |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

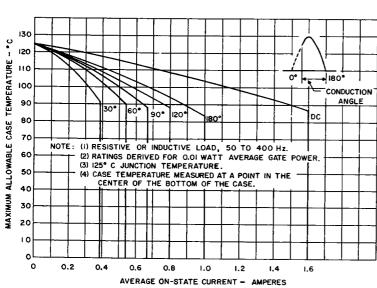

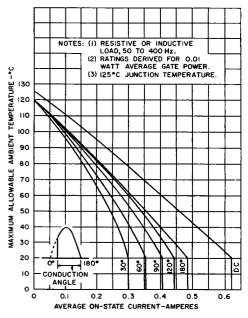

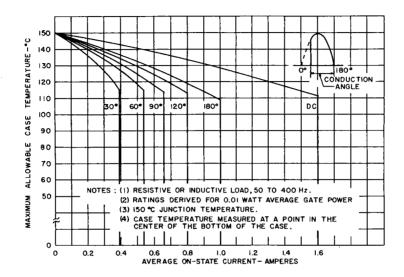

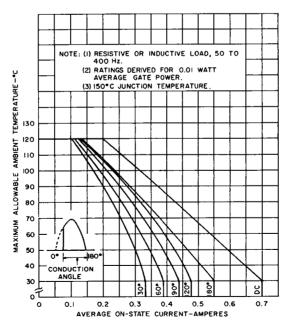

| Average On-State Current, I <sub>T(AV)</sub>                      | Depends on conduction angle                                                                                          |

|                                                                   | (see Charts 3, 4, 5 and 6)                                                                                           |

| Peak One-Cycle Surge (Non-rep) On-State Current, I <sub>TSM</sub> | 15 Amperes*                                                                                                          |

| Peak Gate Power Dissipation, P <sub>GM</sub>                      | 0.1 Watts                                                                                                            |

| Average Gate Power Dissipation, $P_{G(AV)}$                       | 0.01 Watts                                                                                                           |

| Peak Positive Gate Current, I <sub>GM</sub>                       | 0.1 Amperes                                                                                                          |

| Peak Positive Gate Voltage, V <sub>GM</sub>                       | 6 Volts                                                                                                              |

| Peak Negative Gate Voltage, V <sub>GM</sub>                       | $\dots \dots $ |

| Storage Temperature, T <sub>STG</sub>                             | $-65$ °C to $+150$ °C*                                                                                               |

| Operating Temperature, $T_J$                                      | $\dots \dots -65^{\circ}C$ to $+150^{\circ}C$                                                                        |

<sup>\*</sup> Indicates data included in JEDEC type number registration.

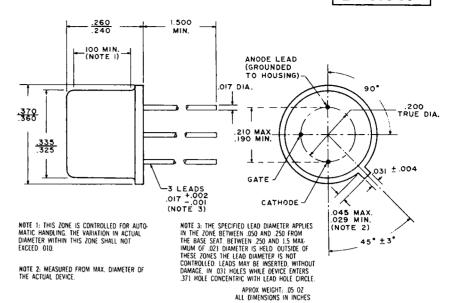

#### OUTLINE DRAWING (Conforms to JEDEC TO-5 Package Outline)

2N1595-99

| TEST                                     | SYMBOL                                                              | MIN. | TYP.       | MAX.        | UNITS       | TEST CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------|---------------------------------------------------------------------|------|------------|-------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

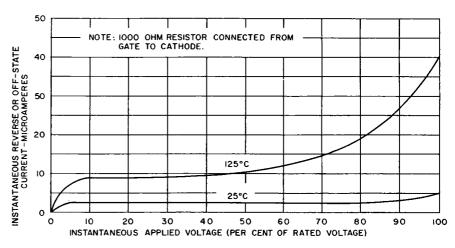

| Peak Off-State<br>and<br>Reverse Current | $egin{array}{c} I_{ m DRM} & \& & & & & & & & & & & & & & & & & & $ |      | 2.0<br>100 | 10<br>1000* | $\mu {f A}$ | $V_{\mathrm{DRM}} = V_{\mathrm{RRM}} = \mathrm{Rated}$ volts peak, $R_{\mathrm{GK}} = 1000$ ohms. $T_{\mathrm{C}} = +25^{\circ}\mathrm{C}$ $T_{\mathrm{C}} = +125^{\circ}\mathrm{C}$                                                                                                                                                                                                                                                                                                                                                                                                           |

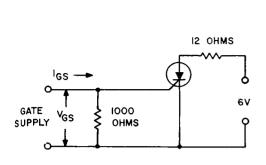

| D.C. Gate Trigger<br>Current             | I <sub>GS</sub> <sup>(1)</sup>                                      |      | 0.9        | 10*         | mAdc        | $T_{\rm C} = +25$ °C, $V_{\rm D} = 6$ Vdc, $R_{\rm L} = 12$ ohms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| D.C. Gate Trigger<br>Voltage             | $V_{GT}$                                                            | _    | 0.6        | 3.0*        | Vdc         | $T_{\rm C} = +25^{\circ}{ m C}, V_{\rm D} = 6  { m Vdc}, R_{\rm L} = 12  { m ohms}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Peak On-State<br>Voltage                 | $V_{TM}$                                                            |      | 1.25       | 2.0 *       | Volts       | $T_{\rm C} = +25 {\rm ^{\circ}C}$ , $I_{\rm TM} = 1.0$ A peak, 1 msec. wide pulse. Duty cycle $\leq 2\%$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Holding Current                          | I <sub>H</sub>                                                      |      | 1.0        |             | mAdc        | $T_{\rm C}=+25^{\circ}{ m C},  { m Anode  Source  Voltage}=12$ Vdc, $R_{ m GK}=1000  { m ohms}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Circuit<br>Commutated<br>Turn-Off Time   | $^{ m t_q}$                                                         |      | 40         |             | μsec        | $T_{\rm C} = +125  ^{\circ}{\rm C}$ , $I_{\rm TM} = 1.0$ A peak. Rectangular current pulse, $50~\mu{\rm sec}$ duration. Rate of rise of current $< 10  {\rm A}/\mu{\rm sec}$ . Commutation rate $\le 5  {\rm A}/\mu{\rm sec}$ . Peak reverse voltage = Rated $V_{\rm RRM}$ volts max. Reverse voltage at end of turn-off time interval 15 volts. Repetition rate = $60~{\rm pps}$ . Rate of rise of re-applied off-state voltage (dv/dt) = $20~V/\mu{\rm sec}$ . Off-state voltage = Rated $V_{\rm DRM}$ volts. Gate bias during turn-off time interval = $0~{\rm volts}$ , $100~{\rm ohms}$ . |

| Turn-On<br>Time                          | t <sub>a</sub> + t <sub>r</sub>                                     |      | 1.2        | _           | μsec        | $T_{\rm C}=+25{\rm ^{\circ}C}, V_{\rm D}={ m Rated}~V_{ m DRM}$ value.<br>$I_{ m TM}=1.0~{ m A}.$<br>Gate trigger pulse = 6 volts, 300 ohms, 5<br>$\mu{ m sec}~{ m wide}, 0.1~\mu{ m sec}~{ m rise}~{ m time}.$<br>Gate bias = 0 volts, 300 ohms.                                                                                                                                                                                                                                                                                                                                              |

<sup>\*</sup> Indicates data included in JEDEC type number registration. NOTE: (1)  $I_{GS}$  is defined in the circuit below:

#### 2. TYPICAL OFF-STATE AND REVERSE BLOCKING CHARACTERISTICS

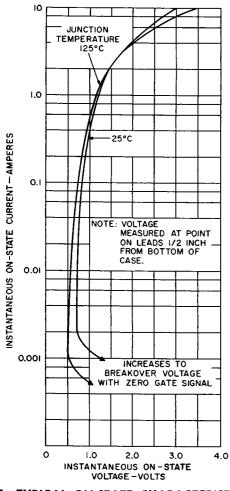

#### 1. TYPICAL ON-STATE CHARACTERISTICS

3. MAXIMUM ALLOWABLE CASE TEMPERATURE (150°C Junction Temp.)

4. MAXIMUM ALLOWABLE AMBIENT TEMPERATURE (125°C Junction Temp.)

Charts 5 and 6 apply to latching applications where SCR need not block off-state voltage after being turned on, since the  $V_{\rm DRM}$  specification does not apply above + 125°C junction temperature. SCR will again block rated off-state voltage after junction temperature drops below + 125°C.

## 5. MAXIMUM ALLOWABLE CASE TEMPERATURE (125°C Junction Temp.)

6. MAXIMUM ALLOWABLE AMBIENT TEMPERATURE (150°C Junction Temp.)