# **Intel® Agilex™ I-Series FPGA Development Kit User Guide**

Version: 2022.09.22

ID: 683288

UG-20338 V

# **Contents**

| 1. Ov  | erview                                                              | 4  |

|--------|---------------------------------------------------------------------|----|

|        | 1.1. Block Diagram                                                  |    |

|        | 1.2. Box Contents                                                   |    |

|        | 1.3. Operating Conditions                                           | 7  |

| 2. Get | tting Started                                                       | s  |

|        | 2.1. About Intel Quartus Prime Software                             |    |

|        | 2.1.1. Activating Your License                                      |    |

|        | 2.2. Development Board Package                                      |    |

|        | 2.3. Installing the Intel FPGA Download Cable II Driver             |    |

|        | -                                                                   |    |

| 3. De  | velopment Board Setup                                               |    |

|        | 3.1. Applying Power to the Development Board                        |    |

|        | 3.2. Default Switch and Jumper Settings                             |    |

|        | 3.2.1. Default Setting                                              |    |

|        | 3.2.2. Perform Board Restore through Intel Quartus Prime Programmer |    |

|        | 3.3. How to Generate a POF Image to Program the Flash               |    |

|        | 3.4. How to Program the Generated POF Image                         |    |

|        | 3.5. The Required SmartVID QSF Assignments to Compile a Design      |    |

| 4. Bo  | ard Test System                                                     | 22 |

|        | 4.1. Set Up BTS GUI Running Environment                             | 22 |

|        | 4.1.1. Download OpenJDK                                             | 23 |

|        | 4.1.2. Download OpenJFX                                             |    |

|        | 4.1.3. Install OpenJDK and OpenJFX                                  | 24 |

|        | 4.1.4. Run BTS GUI                                                  |    |

|        | 4.2. Test the Functionality of the Development Kit                  |    |

|        | 4.2.1. The Bottom Info Bar                                          |    |

|        | 4.2.2. The Configure Menu                                           |    |

|        | 4.2.3. The Sys Info Tab                                             |    |

|        | 4.2.4. The GPIO Tab                                                 |    |

|        | 4.2.5. The XCVR Tab                                                 |    |

|        | 4.2.6. The RAM Tab                                                  |    |

|        | 4.3. Control On-board Clock through Clock Controller GUI            |    |

|        | 4.4. Monitor On-board Power Regulator through Power Monitor GUI     |    |

|        | 4.5. BTS Test Areas                                                 |    |

|        | 4.6. Identify Test Pass or Fail-based on BTS GUI Test Status        | 37 |

| 5. Rev | vision History                                                      | 39 |

| A Do   | velopment Kits Components                                           |    |

| A. De  | ·                                                                   |    |

|        | A.1. Board Overview                                                 |    |

|        | A.2. Intel Agilex I-Series FPGA                                     |    |

|        | A.3. PCIe and CXL Interfaces                                        |    |

|        | A.4. MCIO Connector                                                 |    |

|        | A.6. Network Interfaces                                             |    |

|        | A.7. Port Controller                                                |    |

|        | A.8. FPGA Configuration                                             |    |

|        | A.G. Tran Configuration                                             | 40 |

#### Contents

|       | A.9. Supported Configuration Modes     | 47 |

|-------|----------------------------------------|----|

|       | A.10. Memory Interfaces                | 48 |

|       | A.11. I2C                              | 49 |

|       | A.12. Clock Circuits                   |    |

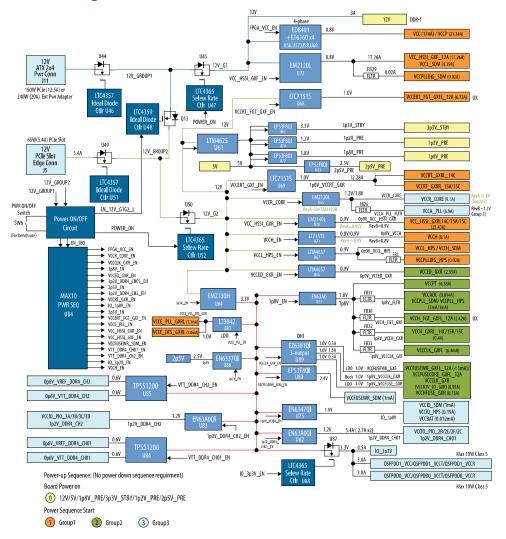

|       | A.13. System Power                     | 50 |

|       | A.13.1. Power Guidelines               | 51 |

|       | A.13.2. Power Distribution System      | 52 |

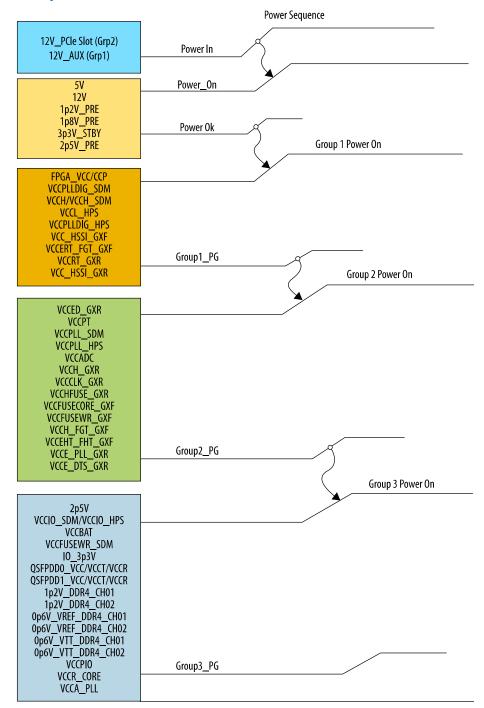

|       | A.13.3. Power Sequence                 |    |

|       | A.13.4. Power Measurement              |    |

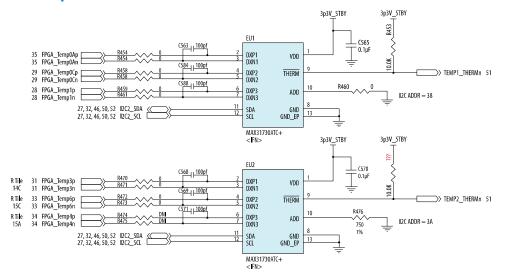

|       | A.14. Temperature Monitoring           |    |

|       | A.15. Mechanical Requirements          | 55 |

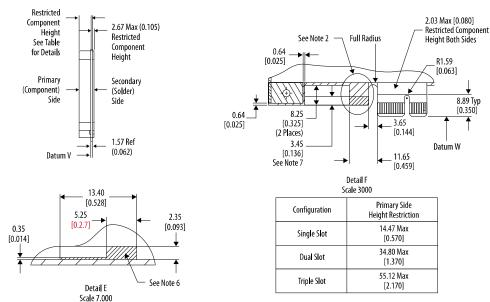

|       | A.16. Board Thermal Requirements       |    |

|       | A.17. Board Operating Conditions       |    |

|       | A.18. Over Temperature Warning LED     |    |

| D A 4 | ditional Information                   | EO |

| b. Ad |                                        |    |

|       | B.1. Safety and Regulatory Information | 58 |

|       | B.1.1. Safety Warnings                 | 59 |

|       | B.1.2. Safety Cautions                 | 60 |

|       | B.2. Compliance Information            |    |

# 1. Overview

This user guide describes the design features and the usage of the Intel<sup>®</sup> Agilex<sup>T</sup> I-Series FPGA Development Kit board.

Table 1. Intel Agilex I-Series FPGA Development Kit Ordering Information

| Ordering Code      | Device Part Number |  |  |

|--------------------|--------------------|--|--|

| DK-DEV-AGI027RES   | AGIB027R29A1E2VR0  |  |  |

| DK-DEV-AGI027R1BES | AGIB027R29A1E2VR3  |  |  |

For the board and FPGA capabilities, refer to the Intel Agilex FPGA and SoC page on the Intel website.

For more information about the *Intel Agilex Device Errata Sheet and User Guidelines* (ES-1069) and *Intel Agilex Known Issue List*, contact Intel Premier Support and quote ID #15011992053.

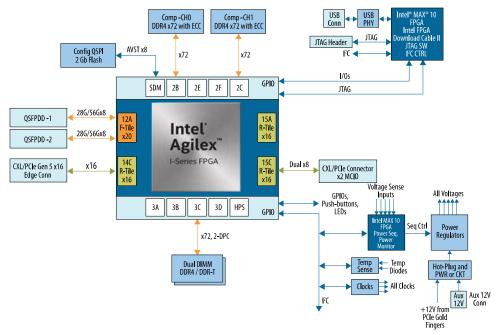

# 1.1. Block Diagram

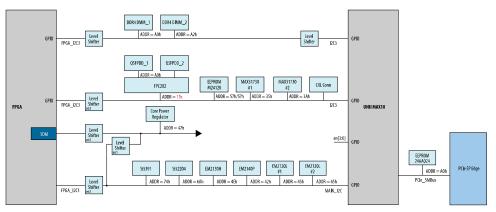

The demonstration board showcases the features of the Intel Agilex I-Series device in the F2957 FBGA package. These devices feature R-tile transceivers with PCIe\* Gen5 x16 and  $CXL^{(1)}$  interfaces and F-tile transceivers with 28G x8 or 56G x8 QSFPDD interfaces. The board supports two on-board DDR4 x72 with ECC channels. The board also features a dual DIMM memory channel for DDR4 and DDR-T.

<sup>(1)</sup> To activate the CXL hard IP and receive CXL soft R-Tile Wrapper and Soft Support logic, purchase or activation of a separate CXL IP license is required for proper use with the Intel Quartus<sup>®</sup> Prime Design Software. Contact your local Intel sales representative for pricing details. To activate a free-of-charge 30- or 60-days trial IP license, please contact your local Intel sales representative.

Figure 1. Intel Agilex I-Series FPGA Development Kit Board Diagram

#### **Feature Summary**

- Intel Agilex I-Series (AGIB027) device in the 2957A BGA package

- 0.8 VID-adjustable VCC core

- R-tile transceivers supporting PCIe Gen5/CXL<sup>(1)</sup>

- F-tile transceivers supporting 56 Gbps NRZ

- FPGA configuration

- Partial reconfiguration support

- Configuration via Protocol (CvP) configuration support

- 2 Gb QSPI flash

- Storage for two configuration images in flash (factory and user)

- JTAG header for device programming

- Built-in Intel FPGA Download Cable II for device programming

- Programmable clock sources

- 156.25 MHz differential LVDS for F-tile (QSFPDD)

- 100.000 MHz HCSL for PCIe and CXL (R-tile)

- 33.33 MHz differential LVDS for memory

- 125 MHz configuration clock

- 100 MHz differential LVDS for I/O banks

#### Transceiver interfaces

- PCIe x16 interface supporting the Gen5 end-point mode connected to a x16

PCIe edge connector (gold edge fingers)

- 2x standard QSFPDD optical module interfaces connected to the F-tile transceivers

- 1x PCIe/CXL<sup>(1)</sup> interface supporting CXL x16 or PCIe x16 at 32 Gbps via MCIO connectors

#### · Memory interfaces

- Two on-board independent single rank DDR4 x72 (ECC) channels operating at 1200 MHz (DDR4-2400)

- Two DIMM sockets supporting dual DIMM for DDR4

#### Communication ports

- 2x QSFPDD optical interface port

- JTAG header

- USB (Micro USB) on-board Intel FPGA Download Cable II

- System I2C header

- Buttons, switches, and LEDs

- System reset push button

- CPU reset push button

- PCIe reset push button

- Four dedicated user LEDs

- Link LED of each QSFP28 port to indicate the link and data transceiver

- Two dedicated configuration status LEDs

#### · Heatsink and Fan

- Air-cooled heatsink assembly

- Red over-temperature warning LED indicator

#### Power

- PCIe input power including required 2x4 auxiliary power connector

- Blue power-on LED

- On/off slide power switch for benchtop operation

- On board power and temperature measurement circuitry

#### Mechanical

- PCIe standard height form factor (full height, 3/4 length, dual-width)

- 4.376" x 10.0" board size

- 2 slots height with heatsink

- Operating environment

- Maximum ambient temperature of 0–35°C

## 1.2. Box Contents

Intel Agilex I-Series FPGA Development board, DDR4 DIMM module, USB2.0 Micro-USB cable, 240W power adapter, and NA/EU/JP/UK cords.

Note: Intel provides only one DIMM module with each development kit.

# 1.3. Operating Conditions

# **Table 2.** Recommended Operating Conditions

| Operating Condition                                       | Range       |

|-----------------------------------------------------------|-------------|

| Recommended ambient operating temperature range           | 0°C to 35°C |

| Maximum ICC load current                                  | 198 A       |

| Maximum ICC load transient percentage                     | 30%         |

| Maximum FPGA power supported by the supplied heatsink/fan | 180 W       |

#### **Handling Precautions**

When handling the board, observe static discharge precautions.

Caution: Without proper anti static handling, the board can be damaged. Therefore, use anti-

static handling precautions when touching the board.

**Caution:** This development kit should not be operated in a vibration environment.

# 2. Getting Started

# 2.1. About Intel Quartus Prime Software

The new Intel Quartus Prime Design Suite design software includes everything needed to design for Intel FPGAs, SoCs, and CPLDs from design entry and synthesis to optimization, verification, and simulation. The Intel Quartus Prime Design Suite software includes an additional Spectra- $Q^{\otimes}$  engine that is optimized for future devices. The Spectra-Q engine enables new levels of design productivity for next generation programmable devices with a set of faster and more scalable algorithms, a hierarchical database infrastructure, and a unified compiler technology.

The Intel Agilex I-Series FPGA Development Kit is supported by the Intel Quartus Prime Pro Edition.

Intel Quartus Prime Pro Edition: The Intel Quartus Prime Pro Edition is optimized to support the advanced features in Intel's next generation FPGAs and SoCs, starting with the Intel Arria<sup>®</sup> 10 device family and requires a paid license.

Included in the Intel Quartus Prime Pro Edition are the Intel Quartus Prime software, Nios<sup>®</sup> II EDS, and the MegaCore IP Library. To install Intel's development tools, download the Intel Quartus Prime Pro Edition software from the Intel Quartus Prime Pro Edition page in the Download Center of Intel's website.

## 2.1.1. Activating Your License

Before using the Intel Quartus Prime software, you must activate your license, identify specific users and computers, and obtain and install license file. If you already have a licensed version of the Intel Quartus Prime Standard Edition or Intel Quartus Prime Pro Edition, you can use that license file with this kit. If not, follow these steps:

- 1. Log on at the My Intel Account Sign In web page and click Sign In.

- 2. On the My Intel Home web page, click the Self-Service Licensing Center link.

- 3. Locate the serial number printed on the side of the development kit box below the bottom bar code. The number consists of alphanumeric characters and does not contain hyphens.

- 4. On the Self-Service Licensing Center web page, click the **Find it with your** License Activation Code link.

- 5. In the **Find/Activate Products** dialog box, enter your development kit serial number and click **Search**.

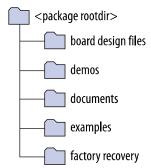

# 2.2. Development Board Package

Download the Intel Agilex I-Series FPGA Development Kit package from the Intel Agilex FPGA Development Kit page of the Intel website.

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2015 Registered

Unzip the Intel Agilex I-Series FPGA Development Kit package.

Figure 2. Installed Development Kit Directory Structure

**Table 3.** Installed Development Kit Directory Description

| Directory Name     | Description of Directory Contents                                                                                                                    |  |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| board_design_files | Contains schematic, layout, assembly, and bill of material board design files. Use these files as a starting point for a new prototype board design. |  |  |

| demos              | Contains demonstration applications when available.                                                                                                  |  |  |

| documents          | Contains documentation.                                                                                                                              |  |  |

| examples           | Contains sample design files for this board.                                                                                                         |  |  |

| factory_recovery   | Contains the original data programmed onto the board before shipment. Use this data to restore the board with its original factory content.          |  |  |

#### **Related Information**

Intel® Agilex™ I-Series FPGA Development Kit

# 2.3. Installing the Intel FPGA Download Cable II Driver

The development board includes integrated Intel FPGA Download Cable II circuits for FPGA programming. However, for the host computer and board to communicate, you must install the on-board Intel FPGA Download Cable II driver on the host computer.

Installation instructions for the on-board Intel FPGA Download Cable II driver for your operating system are available on the Intel website.

On the Cable and Adapter Drivers Information web page of the Intel website, locate the table entry for your configuration and click the link to access the instructions.

# 3. Development Board Setup

This chapter describes how to apply power to the development board and provides default switch and jumper settings.

# 3.1. Applying Power to the Development Board

This development kit is designed to operate in two modes:

#### As a PCIe Add-In Card

When operating the card as a PCIe system, insert the card into an available PCIe slot and connect a 2x4 pin PCIe power cable from the system to power connectors at **J11** of the board.

Note:

When operating as a PCIe add-in card, the board will not power on unless power is supplied to **J11**.

#### **In Bench-Top Mode**

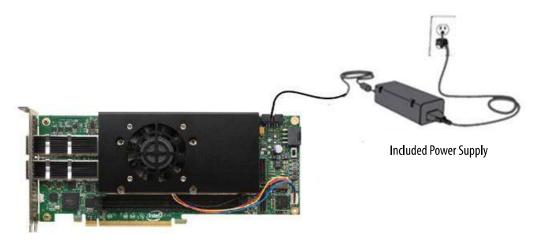

In bench-top mode, you must supply the board with the provided power 240 W power supply connected to the power connector **J11**. The following describes the operation in bench-top mode.

This development board ships with its switches preconfigured to support the design examples in the kit.

If you suspect that your board may not be correctly configured with the default settings, follow the instructions in the Default Switch and Jumper Settings on page 11.

1. Connect the supplied power supply to an outlet and the DC Power Jack (**J11**) on the FPGA board.

*Note:* Use only the supplied power supply. Power regulation circuits on the board can be damaged by power supplies with greater voltage.

2. Set the power switch (SW6) to the ON position.

When the board powers up, the blue power LED illuminates and the board is ready for use.

The blue LED (D6) illuminates to indicate that all the power rails on the board are good. If the POWER GOOD LED (D6) is not illuminated, it indicates that the power supply malfunctioned, and the board will not power up.

### Caution:

The standby powers are always present as soon as the Aux power is applied to **J11**. Use power switch **SW6** to start the board.

# 3.2. Default Switch and Jumper Settings

This section guides you how to restore the default factory settings and provides their functions.

## 3.2.1. Default Setting

The Intel Agilex I-Series FPGA Development Kit ships with its board switches preconfigured to support the design examples in the kit. If you suspect your board might not be correctly configured with the default settings, follow the instructions in the Table 4 on page 11 to return to its factory settings before proceeding.

## **Table 4. Factory Default Switch Settings**

Note: X refers to Don't Care in this table.

For more information, refer to Figure 29 on page 41.

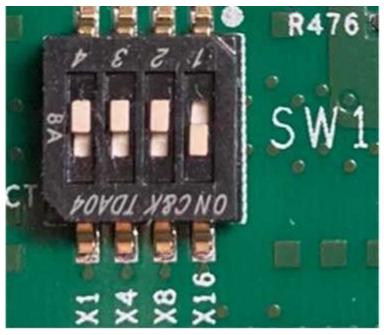

| Switch   | Default Position | Function                                              |       |                            |                      |        |                   |                     |            |        |      |

|----------|------------------|-------------------------------------------------------|-------|----------------------------|----------------------|--------|-------------------|---------------------|------------|--------|------|

| SW1[1:4] | ON/OFF/OFF/OFF   | PCIe PRSNT $x1/x4/x8/x16$ settings. Default = $x16$ . |       |                            |                      |        |                   |                     |            |        |      |

|          |                  | PCIe PRSNT x16 PCIe                                   |       | PRSNT x8 PCIe F            |                      | PCIe P | CIe PRSNT x4      |                     | PCIe PRS   | NT ×1  |      |

|          |                  | ON                                                    |       | OFF                        |                      |        | OFF               |                     |            | OFF    |      |

| SW2[1:4] | ON/OFF/OFF/X     | Configuration mode setting bits.                      |       |                            |                      |        |                   |                     |            |        |      |

|          |                  | Mode                                                  | MS    | MSEL0 MSEL1                |                      |        | MSE               | L2                  | Rese       | rved   |      |

|          |                  | JTAG                                                  | OF    | F                          |                      | OFF    |                   | OFF                 |            | Х      |      |

|          |                  | AVST x8                                               | 01    | ı                          |                      | OFF    |                   | OFF                 |            | х      |      |

|          |                  |                                                       |       |                            | •                    |        |                   | •                   |            | •      |      |

| SW3[1:4] | OFF/ON/ON/OFF    | Туре                                                  |       | ON (Close)                 |                      |        | OFF (Open)        |                     |            |        |      |

|          |                  | 1: Si5391 Clock<br>Enable                             |       | Disable all clocks         |                      |        | Enable all Clocks |                     | cks        |        |      |

|          |                  | 2: CXL REFCLK Select                                  |       | CLK from CXL<br>Connector  |                      |        | On-board REFCLK   |                     | CLK        |        |      |

|          |                  | 3: PCIe REFCLK Select                                 |       | CLK from PCIe<br>Connector |                      |        | On-board REFCLK   |                     | CLK        |        |      |

|          |                  | 4: Si52204 (<br>Enable                                | Clock |                            | Disable all clocks   |        |                   | Enable all Clocks   |            | cks    |      |

|          |                  |                                                       |       |                            |                      |        |                   |                     |            |        |      |

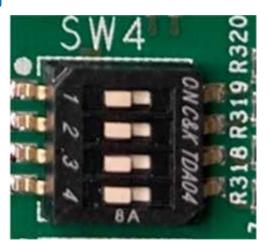

| SW4      | OFF/OFF/OFF      | Туре                                                  |       |                            | ON (Close)           |        |                   |                     | OFF (Open) |        |      |

|          |                  | 1: FPGA I2C Enable                                    |       | le                         | MAIN I2C bus disable |        | ble               | MAIN_I2C bus enable |            | s      |      |

|          |                  |                                                       |       |                            |                      |        |                   |                     |            | contir | nued |

| Switch   | Default Position | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |                                             |  |  |

|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------------|--|--|

|          |                  | 2: FPGA I2C_2 Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                | I2C2 Bus disable            | I2C2 Bus enable                             |  |  |

|          |                  | 3: Main PMBUS Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                | CORE PMBUS disable          | CORE PMBUS enable                           |  |  |

|          |                  | 4: FPGA PMBUS<br>Enable                                                                                                                                                                                                                                                                                                                                                                                                                                             | SDM_I2C Bus disable         | SDM_I2C Bus<br>enable                       |  |  |

| SW5[1:4] | OFF/OFF/OFF/X    | On-board Intel FPGA Download Cable II is the JTAG host when the external JTAG header ( <b>J10</b> ) is unoccupied.                                                                                                                                                                                                                                                                                                                                                  |                             |                                             |  |  |

|          |                  | Туре                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ON                          | OFF                                         |  |  |

|          |                  | 1: JTAG input source                                                                                                                                                                                                                                                                                                                                                                                                                                                | PCIe EP Edge<br>connector   | On-Board Intel<br>FPGA Download<br>Cable II |  |  |

|          |                  | 2: FPGA Bypass                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bypass FPGA                 | FPGA in JTAG chain                          |  |  |

|          |                  | 3: Intel MAX® 10<br>JTAG Select                                                                                                                                                                                                                                                                                                                                                                                                                                     | Intel MAX 10 JTAG<br>Enable | Intel MAX 10 JTAG<br>Disable                |  |  |

|          |                  | 4: Not used                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Х                           | x                                           |  |  |

| SW6      | ON/OFF           | When the board is not in a PCIe slot, it must be powered by an external power supply. The SW6 switch turns on the power of the board when it is at the ON position and turns off the power when it is at the OFF position.  When the board is in a PCIe slot, the external and auxiliary power supplies must still be connected. The SW6 switch can be left at either the ON or OFF position. The board can only be powered on when both power sources are present. |                             |                                             |  |  |

Figure 3. SW1[1:4] Switch Setting

Figure 4. SW2[1:4] Switch Setting

Figure 5. SW3[1:4] Switch Setting

Figure 6. SW4 Switch Setting

Figure 7. SW5[1:4] Switch Setting

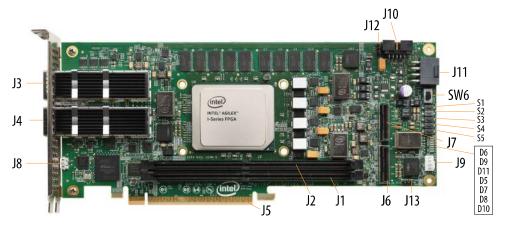

**Table 5.** Connectors on the Development Kit

| Board Reference | Туре                      | Description                                                              |

|-----------------|---------------------------|--------------------------------------------------------------------------|

| J11             | Auxiliary power connector | For the external 12V auxiliary power supply or power adapter             |

| J12             | I2C/PMBus connector       | For accessing core power controller                                      |

| J13             | I2C connector             | For accessing to the main I2C1 bus                                       |

| J3              | QSFPDD_0 connector        | _                                                                        |

| ]4              | QSFPDD_1 connector        | _                                                                        |

| J8              | USB connector             | For programming the FPGA using on-<br>board Intel FPGA Download Cable II |

| J10             | External JTAG header      | For use with the external download cable                                 |

| J1              | DIMM A connector          | DDR4/DDRT Dual DIMM A                                                    |

| J2              | DIMM B connector          | DDR4/DDRT Dual DIMM B                                                    |

| J5              | PCIe x16 Gold Finger      | _                                                                        |

| J6, J7          | CXL/PCIe connectors       | For connecting the external CXL/PCIe MCIO cables                         |

| J24             | Fan connector             | For connecting to the heatsink cooling fan                               |

Table 6. LEDs on the Development Kit

| <b>Board Reference</b> | Туре                                    | Description                                           |

|------------------------|-----------------------------------------|-------------------------------------------------------|

| D1                     | QSFPDD_0 Link/Activity LED              | Green LED - User defined                              |

| D2                     | QSFPDD_0 Link/Activity LED (Dual color) | Yellow LED – User defined<br>Green LED - User defined |

| D3                     | QSFPDD_1 Link/Activity LED              | Green LED - User defined                              |

| D4                     | QSFPDD_1 Link/Activity LED (Dual color) | Yellow LED – User defined<br>Green LED - User defined |

| D5                     | USER LED 0                              | Green LED for USER LED 0                              |

|                        |                                         | continued                                             |

| Board Reference | Туре            | Description                                                                   |

|-----------------|-----------------|-------------------------------------------------------------------------------|

| D7              | USER LED 1      | Green LED for USER LED 1                                                      |

| D8              | USER LED 2      | Green LED for USER LED 2                                                      |

| D10             | USER LED 3      | Green LED for USER LED 3                                                      |

| D6              | POWER GOOD LED  | Blue LED:  ON: All powers are good.  OFF: Power failure                       |

| D11             | CONFIG DONE LED | Green LED:  ON: FPGA configuration successful  OFF: FPGA configuration failed |

| D9              | Over Temp LED   | Red LED:  ON: FPGA over temperature condition                                 |

#### Table 7. Push-Buttons on the Development Kit

| Board Reference | Туре           | Description                                           |

|-----------------|----------------|-------------------------------------------------------|

| S1              | CPU Reset      | Push to reset FPGA                                    |

| S2              | PCIe Reset     | Push to reset PCIe bus on MCIO connectors (J6 and J7) |

| S3              | CXL Reset      | Push to reset CXL bus on MCIO connectors (J6 and J7)  |

| S4              | USB PHY Reset  | Push to reset on-board USB PHY                        |

| S5              | QSFPDD_1 Reset | Push to reset F-tile for QSFPDD_1 port                |

# 3.2.2. Perform Board Restore through Intel Quartus Prime Programmer

The development kit ships with FPGA design examples stored in the QSPI flash device and system Intel MAX 10 pre-programmed. If you want to restore board QSPI flash with factory default image, follow these steps:

- 1. Connect the USB cable between **J8** USB connector and your computer.

- 2. Open Intel Quartus Prime Programmer GUI, detect the JTAG chain, attach the factory default image on system Intel MAX 10 device.

- 3. Select programming options and click the program button.

# 3.3. How to Generate a POF Image to Program the Flash

Note: If you already have the Programmer Object File (.pof), you can skip this section.

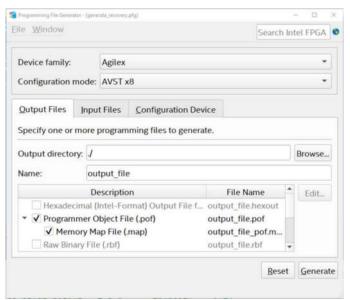

To generate a POF image to program the flash on the development kit, follow these steps:

- Open the Intel Quartus Prime Pro Edition software and click on File >

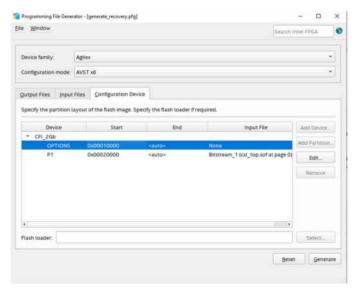

Programming File Generator to launch the Programming File Generator too.

- 2. In the **Device family** list, select **Agilex**, and in the **Configuration mode** list, select **AVST x8** to specify the device and configuration mode.

- 3. In the **Output directory** tab, click **Browse** to specify the output directory for .pof file.

4. In the **Description** column, select the **Programmer Object File (.pof)** and **Memory Map File (.map)** options.

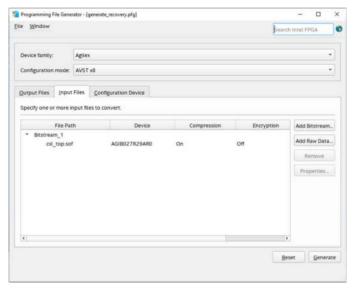

5. Click on the **Input Files > Add Bitstream** tab to specify a .sof that contains the configuration bitstream.

6. Click on the **Configuration Device > Add Device** to specify the flash device. In the **Device** list of the pop-up window, select **CFI\_2Gb** for the configuration flash device.

- 7. Click on the **OPTIONS** row, and the click on the **Edit** option to modify the start address. In the **Address Mode** list of the pop-up window, select **Start**. In the **Start address** list, input **0x00010000**.

- Click on the CFI\_2Gb row, and then click the Add Partition option. In the Input file list of pop-up window, select Bitstream (input\_sof\_file.sof). In the Address Mode list of pop-up window, select Start. In the Start address list, input 0x00020000.

9. Click **Generate** to generate the .pof file.

# 3.4. How to Program the Generated POF Image

To program the generated POF image, follow these steps:

- 1. Plug in the USB cable to the USB port **J8** or **J10** (when using J10, DIPSWITCH SW5.3 should be off).

- 2. Set the DIPSWITCH SW2 to [on:off:off:X] (don't care the 4th bit).

- 3. Power on the board.

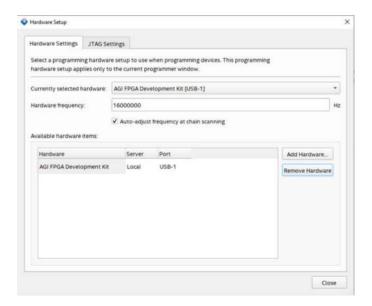

- Open the Intel Quartus Prime Pro Edition software and click on Tools > Programmer to launch the Programmer tool.

- 5. In the Hardware Setup page, select AGI FPGA Development Kit, and in the Hardware frequency column, input 16000000 Hz.

6. In the **Programmer** page, click **Auto Detect** to scan the JTAG devices.

7. Right click the **VTAP10** device, **Edit > Change Device**, change it to **MAX 10 > 10M50DAF256**.

- 8. Right click the 10M50DAF256 device, Edit > Attach Flash Device, select Quad SPI Flash Memory QSPI\_2Gb.

- In the Programmer page, click QSPI\_2Gb > Change File to select the .pof file.

10. Start the Programmer.

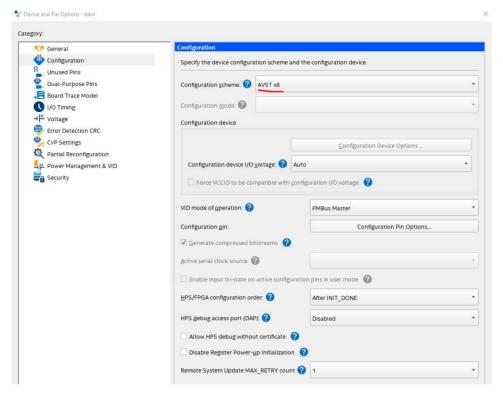

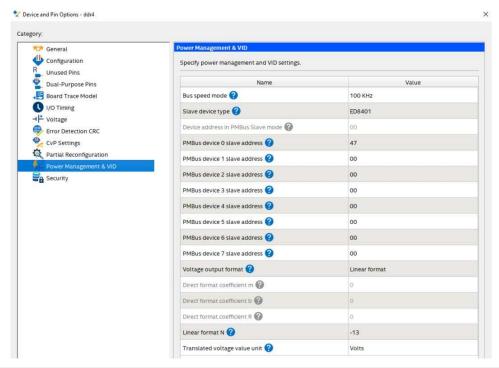

# 3.5. The Required SmartVID QSF Assignments to Compile a Design

If you are creating your own design and want to generate programming SRAM object file (.sof), you must add the correct SmartVID setting into the Intel Quartus Prime project for the Intel Agilex FPGA development kit to configure successfully. Before you add the following SmartVID setting into the Quartus settings file (.qsf), you must change the configuration scheme to Avalon® streaming interface x8 (AVST x8) for your project. You can also extract the SmartVID setting from the Golden Top file.

#### Figure 8. Selecting the Configuration Scheme

#### Figure 9. Power Management & VID Settings

# 4. Board Test System

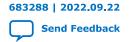

The Intel Agilex I-Series FPGA Development Kit includes design examples and the board test system (BTS) GUI to test the functionality of this board. The BTS provides an easy-to-use interface to alter functional settings and observe results. You can use the BTS to test board components, modify functional parameters, observe performance, and measure power usage.

While using the BTS, you reconfigure the FPGA several times with test designs specific to the functionality that you are testing. The BTS is also useful as a reference for designing systems. The BTS communicates over the JTAG bus to a test design running in the Intel Agilex I-Series FPGA device.

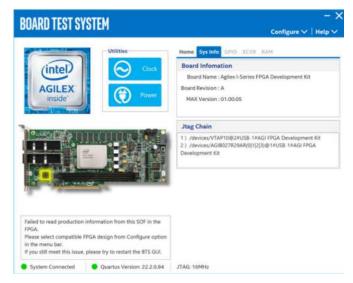

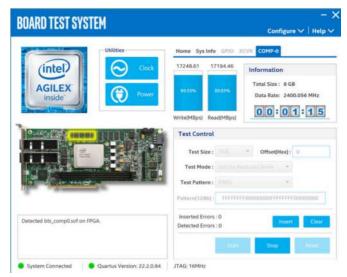

Figure 10 on page 22 shows the graphical user interface (GUI) of a board that is in factory configuration.

Figure 10. BTS GUI

# 4.1. Set Up BTS GUI Running Environment

To run BTS GUI, including Power Monitor and Clock Controller GUI, you need to download and install Java runtime including OpenJDK and OpenJFX on your systems and set up the running environment. This is a one-time procedure, so if you have already completed it before, you do not need to do it again unless the Java version upgrade is needed.

# 4.1.1. Download OpenJDK

To download the Temurin OpenJDK, follow these steps:

- Download the Temurin OpenJDK using this link: https://adoptium.net/ releases.html.

- 2. Select Architecture x64, package type JRE, and version 11.

## Figure 11. OpenJDK Version

- 3. On **Windows** system, choose the JRE zip format file.

- 4. On **Linux** system, choose the JRE tar.gz format file.

Note: The JDK version can be updated, download the latest version.

# 4.1.2. Download OpenJFX

To download the OpenJFX, follow these steps:

- 1. Download the OpenJFX using this link: https://gluonhq.com/products/javafx/.

- 2. Select the JavaFX version 17.0.2.

- 3. For **Windows** system, download the JavaFX Windows x64 SDK.

- 4. For **Linux** system, download the JavaFX Linux x64 SDK.

Figure 12. JavaFX Version

## 4.1.3. Install OpenJDK and OpenJFX

You have two downloaded zip files, follow these steps to install them.

1. On **Windows** system, Intel recommends you to unzip the files and put them in the following directory:

C:\Program Files\Java\jre

C:\Program Files\Java\jfx

Note: The unzipped folder name of JRE is jdk-11.0.xx+x-jre (for example jdk-11.0.15+10-jre), you must rename it to jre. The unzipped folder name of JFX is javafxsdk-17.0.2, you must rename it to jfx.

2. On **Linux** system, Intel recommends you to unzip the files and rename the folders using the following commands:

```

# unzip openjfx-17.0.2_linux-x64_bin-sdk.zip -d /opt/Java/

# tar zxvf OpenJDK11U-jre_x64_linux_hotspot_11.0.15_10.tar.gz -C /opt/Java/

# cd /opt/Java

# mv javafx-sdk-17.0.2 jfx

# mv jdk-11.0.15+10-jre jre

```

You have the following two directories on your **Linux** system:

/opt/Java/jre

/opt/Java/jfx

#### 4.1.4. Run BTS GUI

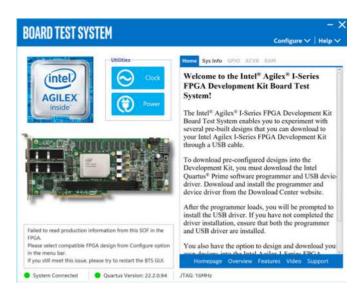

The BTS release folder always include the following files.

Figure 13. BTS Folder

You can run BTS GUI easily with the following scripts.

On Windows system, double click the .bat files to run BTS, Clock Controller, or Power Monitor GUI.

#### Figure 14. Windows Console

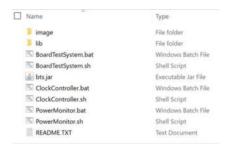

2. On **Linux** system, you need to run the shell script with root privilege.

#### Figure 15. Linux Console

Note:

The .bat or shell script will check the Java environment settings, copy necessary files, and give some prompts if the environment is not set up correctly.

# 4.2. Test the Functionality of the Development Kit

This section describes each control in the BTS.

### 4.2.1. The Bottom Info Bar

The bottom information bar shows the status of the system connection, Intel Quartus Prime version and the JTAG clock.

- **System Connected/Disconnected**: Shows if the board is connected to the system. The green sign turns gray if the board becomes disconnected.

- **Intel Quartus Prime Version**: Displays the current Intel Quartus Prime version installed and active on your system. The text turns red if your version is older than the required version. Change the QUARTUS\_ROOTDIR environment variable if you have installed the right version but the active version doesn't meet the requirement.

- JTAG: Displays the JTAG clock frequency.

## 4.2.2. The Configure Menu

Use the Configure Menu to select the design you want to use. Each design example tests different functionality that corresponds to one or more application tabs.

Figure 16. The Configure Menu

To configure the FPGA with a test system design, follow these steps:

- 1. On the **Configure** menu, click the **Configure** command that corresponds to the functionality you wish to test.

- 2. In the dialog box that appears, click **Configure** to download the corresponding design's SRAM Object File (.sof) to the FPGA. The download process usually takes less than a minute.

- 3. When configuration finishes, the design begins running in the FPGA. The corresponding GUI application tabs that interface with the design are now enabled. If you use the Intel Quartus Prime Programmer for configuration, instead of the BTS GUI, you might need to restart the GUI.

# 4.2.3. The Sys Info Tab

The **Sys Info** tab shows information about the board's current configuration. The tab displays the board information, JTAG Chain devices and other details stored on the board.

Figure 17. The Sys Info Tab

The following sections describe the controls on the System Info tab.

#### **Board Information**

The board information control displays static information about your board.

- Board Name: Indicates the official name of the board given by the BTS.

- Board Revision: Indicates the revision of the board.

- MAX Version: Indicates the version of the system max.

#### **JTAG Chain**

The JTAG chain control shows all the devices currently in the JTAG chain.

Note:

Change the settings of **SW5** to bypass or enable power for Intel MAX 10 and Intel Agilex FPGA. System Intel MAX 10 and FPGA should all be in the JTAG chain when configured and running the BTS GUI.

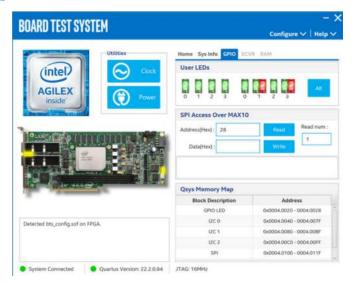

#### 4.2.4. The GPIO Tab

The **GPIO** tab allows you to interact with all the general-purpose user I/O components on your board. You can turn LEDs on or off and read or write data with SPI access.

Figure 18. The GPIO Tab

The following sections describe the controls on the GPIO tab.

#### **User LEDs**

The User LEDs control displays the current state of the user LEDs. Toggle the LED buttons to turn the board LEDs on and off.

#### **SPI Access Over MAX10**

SPI Access Over MAX10 allows you to read and write the data at the address you specify.

#### **Qsys Memory Map**

The Qsys Memory Map control shows the memory map of **bts\_config.sof** design running on your board.

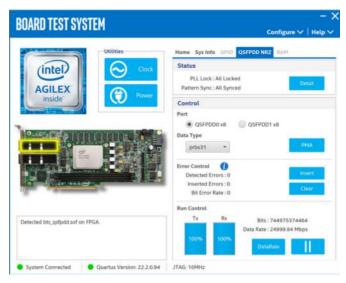

#### 4.2.5. The XCVR Tab

The **XCVR** tab allows you to run transceivers tests on your board. You can run the QSFPDD test using optical fiber modules.

## 4.2.5.1. The QSFPDD NRZ Tab

#### Figure 19. The QSFPDD NRZ Tab

The following sections describe controls in the QSFPDD NRZ tab.

#### **Status**

The Status control displays the following status information during the loopback test:

- PLL Lock: Shows the PLL locked or unlocked state.

- **Pattern Sync**: Shows the pattern synced or not state. The pattern is considered synced when the start of the data sequence is detected.

- **Detail**: Shows the PLL lock and pattern sync status.

#### **Control**

Use the following controls to select an interface to apply PMA settings, data type, and error control:

- QSFPDD0 x8

- QSFPDD1 x8

#### **PMA Setting**

PMA allows you to make changes to the PMA parameters that affect the active transceiver interface. The following settings are available for analysis:

- **Serial Loopback**: Displays the signal status between the transmitter and the receiver.

- VOD: Specifies the voltage output differential of the transmitter buffer.

- Pre-emphasis tap:

- Pre-tap 1: Specifies the amount of pre-emphasis on the first pre-tap of the transmitter buffer.

- Pre-tap 2: Specifies the amount of pre-emphasis on the second pre-tap of the transmitter buffer.

- Post-tap 1: Specifies the amount of pre-emphasis on the post-tap of the transmitter buffer.

Figure 20. QSFPDD-PMA Setting

#### **Data Type**

The Data Type control specifies the type of data pattern contained in the transactions. Select the following available data types for analysis:

- **PRBS7**: Pseudo-random 7-bit sequences.

- **PRBS15**: Pseudo-random 15-bit sequences.

- PRBS23: Pseudo-random 23-bit sequences.

- PRBS31: Pseudo-random 31-bit sequences (default).

- **High\_freq**: Selects the highest frequency divided-by-2 data pattern 10101010.

- Low\_freq: Selects the lowest frequency divided-by-33 data pattern.

#### **Error Control**

This control displays data errors detected during analysis and allows you to insert errors:

- **Detected Errors**: Displays the number of data errors detected in the received bitstream.

- **Inserted Errors**: Displays the number of errors inserted into the transmit datastream.

- Bit Error Rate: Calculates the bit error rate of the transmit data stream.

- **Insert**: Insert a one-word error into the transmit data stream each time you click the button. Insert error is only enabled during transaction performance analysis.

- Clear: Resets the Detected Errors counter and Inserted Errors counter to zeros.

#### **Run Control**

- **TX and RX performance bars**: Show the percentage of the maximum theoretical data rate that the requested transactions are able to achieve.

- Start: This control initiates the loopback tests.

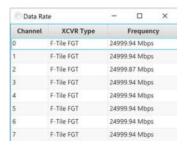

- Data Rate: Displays the XCVR type and data rate of each channel.

#### Figure 21. XCVR-Data Rate

## 4.2.5.2. The QSFPDD PAM4 Tab

#### Figure 22. The QSFPDD PAM4 Tab

Similar control functions with the QSFPDD NRZ tab. According to the F-tile performance, the QSFPDD0 only reserves 4 channels.

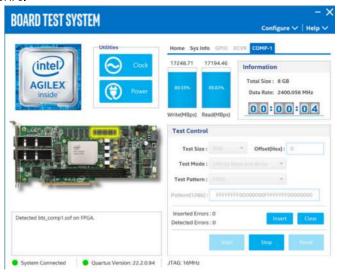

#### 4.2.6. The RAM Tab

This tab allows you to read and write DDR4-COMP0, DDR4-COMP1, and DDR4-RDIMM memory on your board. Download DDR4 designs through BTS Configure.

Figure 23. The COMP-O Tab

The following sections describe controls on this tab.

#### **Start**

Initiates DDR4 memory transaction performance analysis.

#### Stop

Terminates transaction performance analysis.

#### **Performance Indicators**

These controls display current transaction performance analysis information collected since you last clicked **Start**:

- **Write and Read performance bars**: Show the percentage of maximum theoretical data rate that the requested transactions are able to achieve.

- Write (MBps) and Read (MBps): Show the number of bytes analyzed per second.

- **Data Bus**: 72 bits (8 bits ECC) wide, reference clock is 100 MHz, and the frequency is 1066 MHz double data rate 2133 MT/s.

#### **Test Control**

- **Test Size**: You can choose the size of the memory to test. The available options are 64 KB, 256 KB, 1 MB, 4 MB, 16 MB, 64 MB, 256 MB, 1 GB, 4 GB, and 8 GB (default).

- Offset (Hex): You can define the memory start address to test.

- **Test Mode**: Infinite Read and Write (default), Single Read and Write.

- Test Pattern: PRBS (default), User Defined Constant, Walking '0', Walking '1'.

#### **Error Control**

This control displays data errors detected during analysis and allows you to insert errors:

- Detected Errors: Displays the number of data errors detected in the hardware.

- **Inserted Errors**: Displays the number of errors inserted into the transaction stream.

- Bit Error Rate: Calculates the bit error rate of the transmit data stream.

- **Insert**: Insert a one-word error into the transaction stream each time you click the button. Insert error is only enabled during transaction performance analysis.

- Clear: Resets the Detected Errors counter and Inserted Errors counter to zeros.

## Figure 24. The COMP-1 Tab

Same with DDR4-COMP0.

Figure 25. The DDR4-RDIMM Tab

Same with DDR4-COMP0.

# 4.3. Control On-board Clock through Clock Controller GUI

The Clock Controller GUI can change on-board Si5391 programmable PLLs to any customized frequency between 100 Hz and 712.5 MHz.

The instructions to run Clock Controller GUI are stated in the Run BTS GUI on page 24. It can also be started with the BTS GUI icon "Clock".

The Clock Controller communicates with the System Intel MAX 10 device through either USB port  $\bf J8$  or 10-pin JTAG header  $\bf J10$ . Then System Intel MAX 10 controls these programmable clock parts through a 2-wire  $\bf I^2C$  bus.

Note:

You cannot run the stand-alone Clock Controller GUI application when the BTS or Power Monitor GUI is running at the same time.

Figure 26. Clock Controller GUI

The following sections describe the Clock Controller buttons.

#### Read

Reads the current frequency setting for the oscillator associated with the active tab.

#### **Default**

Sets the frequency for the oscillator associated with the active tab back to its default value. This can also be accomplished by power cycling the board.

#### Set

Sets the programmable oscillator frequency for the selected clock to the value in the  $\mathtt{OUTx}$  output controls for the Si5391. Frequency changes might take several milliseconds to take effect. You might see glitches on the clock during this time. Intel recommends resetting the FPGA logic after changing frequencies.

#### **Import**

Si5391 has a two-time writable non-volatile memory (NVM). You can generate the register list from the Clockbuilder Pro tool and import it into Si5391 to update the settings of the NVM. Register changes are volatile after power cycling. Clockbuilder Pro Software on Skyworks website

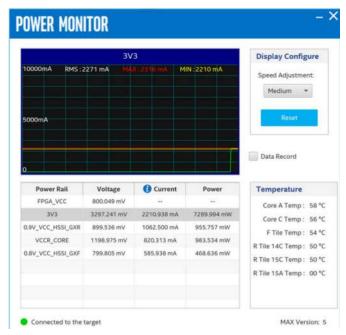

# 4.4. Monitor On-board Power Regulator through Power Monitor GUI

The Power Monitor GUI reports most power rails' voltage, current, and power information on the board. It also collects temperature from FPGA die, power modules, and diodes assembled on PCB.

Power Monitor GUI communicates with System Intel MAX 10 through either USB port **J8** or 10-pin JTAG header **J10**. System Intel MAX 10 monitors and controls power regulator, temperature/voltage/current sensing chips through a 2-wire I<sup>2</sup>C bus.

The instructions to run Power Monitor GUI are stated in the Run BTS GUI on page 24. It can also be started with the BTS GUI icon "Power".

Note: You cannot run the stand-alone Power Monitor GUI when the BTS or the Clock Controller GUI is running at the same time.

Figure 27. Power Monitor GUI

The following sections describe the details of the Power Monitor GUI.

#### **Display Configure**

- Speed Adjustment: Adjusts the update rate of the current curve.

- · Reset: Regenerates the graph.

#### **Data Record**

When the box is checked, the telemetry data of the selected power rail can be recorded. The data will be saved into a .csv file in the log directory.

### **Temperature**

Core A Temp/Core C Temp/F Tile Temp/R Tile 14C Temp/R Tile 15C Temp/R Tile 15A Temp: FPGA die internal temperature sense diodes.

## 4.5. BTS Test Areas

BTS checks for hardware fault before you can use the board. If one or more BTS test items fail, it implies either a wrong hardware setting or hardware fault on specific interface.

# 4.6. Identify Test Pass or Fail-based on BTS GUI Test Status

## **DDR4 DIMMs**

Plug the DDR4 DIMM module which is shipped alone with this development kit in **J1/J2**. BTS GUI only supports fabric memory interfaces namely DDR4 Comp-CH0, Comp-CH1, and DIMM.

# QSFPDD0/QSFPDD1

Plug QSFPDD0/QSFPDD1 loopback module in  ${\bf J3/J4}$  before you configure QSFPDD NRZ example build through BTS GUI.

# 5. Revision History

Table 8. **Revision History of the Intel Agilex I-Series FPGA Development Kit User** Guide

| Document<br>Version | <b>Changes</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Added the Additional Information section.  Added The XCVR Tab section.  Added The QSFPDD PAM4 Tab section.  Added Figure: The QSFPDD PAM4 Tab.  Updated the Overview section.  Updated the Block Diagram section to include details about the CXL IP license.  Updated the Block Diagram section to include details about the CXL IP license.  Updated the About Intel Quartus Prime Software section.  Updated the section title from Perform Board Restore through Board Test System (BTS) GUI to Perform Board Restore through Intel Quartus Prime Programmer.  Updated the Download OpenJDK section.  Updated the Download OpenJDK section.  Updated The Sys Info Tab section.  Updated The QSFPDD NRZ Tab section.  Updated the Intel Agilex I-Series FPGA section.  Updated the Intel Agilex I-Series FPGA section.  Updated the PCIe and CXL Interfaces section.  Updated the description of J6 and J7 in Table: Connectors on the Development Kit.  Updated He description of S2 and S3 in Table: Push-Buttons on the Development Kit.  Updated Figure: BTS GUI.  Updated Figure: BTS GUI.  Updated Figure: JavaFX Version.  Updated Figure: JavaFX Version.  Updated Figure: BTS Folder.  Updated Figure: Windows Console.  Updated Figure: The Configure Menu.  Updated Figure: The COMP-0 Tab.  Updated Figure: The COMP-0 Tab.  Updated Figure: The COMP-1 Tab. |

|                     | <ul> <li>Updated Figure: The DDR4-RDIMM Tab.</li> <li>Updated Figure: Clock Controller GUI.</li> <li>Updated Figure: Power Monitor GUI.</li> <li>Removed Figure: Windows OpenJDK Version.</li> <li>Removed Figure: Linux OpenJDK Version.</li> <li>Removed support for Intel Optane™.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2022.03.30          | Updated the MCIO Cable Assembly Information section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services. \*Other names and brands may be claimed as the property of others.

ISO 9001:2015 Registered

| Document<br>Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2022.02.11          | <ul> <li>Added the Board Test System section.</li> <li>Added the How to Generate a POF Image to Program the Flash section.</li> <li>Added the How to Program the Generated POF Image section.</li> <li>Added The Required SmartVID QSF Assignments to Compile a Design section.</li> <li>Added Figure: SW1[1:4] Switch Setting.</li> <li>Added Figure: SW2[1:4] Switch Setting.</li> <li>Added Figure: SW3[1:4] Switch Setting.</li> <li>Added Figure: SW4 Switch Setting.</li> <li>Added Figure: SW5[1:4] Switch Setting.</li> <li>Updated the PCIe and CXL Interfaces section.</li> <li>Updated Figure: Intel Agilex I-Series FPGA Development Board Image—Front.</li> <li>Updated Table: Factory Default Switch Settings.</li> <li>Removed the Factory Reset section.</li> <li>Minor editorial updates.</li> </ul> |  |

| 2021.11.17          | Updated the PCIe REFCLK Select function in the SW3[1:4] switch row in Table: Factory Default Switch Settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 2021.09.24          | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

# **A.** Development Kits Components

This chapter introduces all the major components on the development board. A complete set of schematics, a physical layout database, and GERBER files for the development board reside in the development kit documents directory.

## A.1. Board Overview

Images of the Intel Agilex I-Series FPGA development board are shown below.

Figure 28. Intel Agilex I-Series FPGA Development Board Image—Front

Figure 29. Intel Agilex I-Series FPGA Development Board Image—Back

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

# A.2. Intel Agilex I-Series FPGA

Intel Agilex I-Series FPGA 56 mm x 45 mm package:

- Part Number: AGIB027R29A1E2VR0 or AGIB027R29A1E2VR3

- 2957-Ball FBGA Package

- 2.7M LEs

- 8528 digital signal processing (DSP) blocks

- 17056 18x19 Multipliers

- LVDS pairs supporting 1.6 Gbps

- 3x R-tile supporting PCIe Gen5 x16 (32Gb/s) or CXL<sup>(2)</sup> x16

- 1x F tile transceiver supporting 56Gbps NRZ

## A.3. PCIe and CXL Interfaces

The Intel Agilex I-Series FPGA Development Kit supports two PCIe/CXL Gen5 x16 interfaces using two out of the FPGA's three R-tiles, refer to Figure 1 on page 5.

- 1. One R-tile (14C) supports PCIe/CXL x16 connecting to the development kit's PCIe edge connector. This interface supports x1, x4, x8, and x16 PCIe Endpoint or CXL Endpoint.

- 2. One R-tile (15C) connects to two 74-pin MCIO connectors that can be used as CXL or PCIe x16 interface in the Endpoint or Root Port mode. The MCIO connectors also carry SMBus/I2C, clock, and GPIO signals.

Note:

To activate the CXL hard IP and receive CXL soft R-Tile Wrapper and Soft Support logic, purchase or activation of a separate CXL IP license is required for proper use with the Intel Quartus Prime Design Software. Contact your local Intel sales representative for pricing details. To activate a free-of-charge 30- or 60-days trial IP license, please contact your local Intel sales representative.

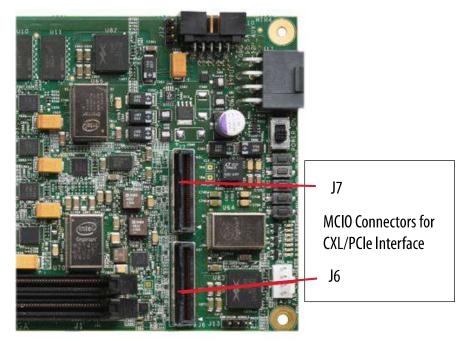

## A.4. MCIO Connector

The CXL or PCIe interface is connected to two 74-pin MCIO connectors for 16 channels of transmit and receive signals of the R-tile (15C). Cables are used to connect this CXL or PCIe link from the development kit to the host board or application-specific daughter cards.

<sup>(2)</sup> To activate the CXL hard IP and receive CXL soft R-Tile Wrapper and Soft Support logic, purchase or activation of a separate CXL IP license is required for proper use with the Intel Quartus Prime Design Software. Contact your local Intel sales representative for pricing details. To activate a free-of-charge 30- or 60-days trial IP license, please contact your local Intel sales representative.

Figure 30. MCIO Connector

Figure 31. MCIO Connector Circuit

# A.5. MCIO Cable Assembly Information

The cable is not provided with the development kit. For more information, contact Intel Premier Support and quote ID #14016163317.

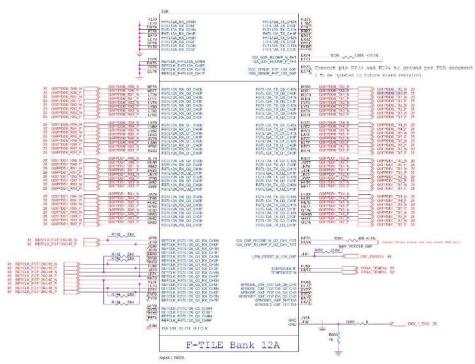

## A.6. Network Interfaces

The development kit supports two QSFPDD connectors each, connecting to the Intel Agilex's F-tile (12A) transceivers. Each port can operate at 4x 58G or 8x 28G. These two ports support ZQSFP56 SR optical modules as well as the 3M DAC electrical cables. A Texas Instruments FPC202 dual-port controller serves as the low-speed signal aggregator that makes up the Dual 100Gpbs Ethernet interfaces. The FPC202 aggregates all low speed and I2C signals across two ports and presents it as a single management interface to the host.

683288 | 2022.09.22

The F-tile (12A) of the FPGA provides 16 general-purpose (FGT) transceiver channels, each 8-channel group is routed to one QSFPDD. The transceiver bank requires 156.25 MHz clocks for the 28 Gbps NRZ and 325.50 MHz clocks for the 56 Gbps PAM4. These clocks must have RPM jitter <250fs.

Figure 32. F-Tile Bank 12A Circuit

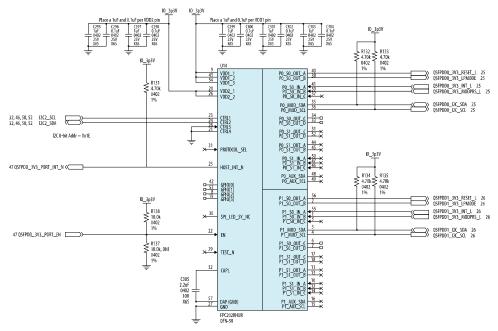

# A.7. Port Controller

A Texas Instrument FPC202 dual-port controller serves as the low-speed signal aggregator for the two QSFP ports.

Figure 33. Port Controller Circuit

# A.8. FPGA Configuration

You can use the Intel Quartus Prime Programmer to configure the FPGA with your SRAM Object File (.sof).

## **FPGA Configuration Setup**

#### Ensure the following:

- The Intel Quartus Prime Programmer and the Intel FPGA Download Cable II driver are installed on the host computer.

- The micro-USB cable is connected to the FPGA development board.

- Power to the board is ON, and no other applications that use the JTAG chain are running.

#### Follow these steps:

- 1. Start the Intel Quartus Prime Programmer.

- 2. Click **Auto Detect** to display the devices in the JTAG chain.

- 3. Click **Change File** and select the path to the desired **.sof**.

- 4. Turn on the **Program/Configure** option for the added file.

- 5. Click **Start** to download the selected file to the FPGA. Configuration is complete when the progress bar reaches 100%.

Using the Intel Quartus Prime Programmer to configure a device on the board causes other JTAG-based applications such as the Board Test System and the Power Monitor to lose their connection to the board. Restart those applications after configuration is complete.

#### Programming the FPGA over Intel FPGA Download Cable II

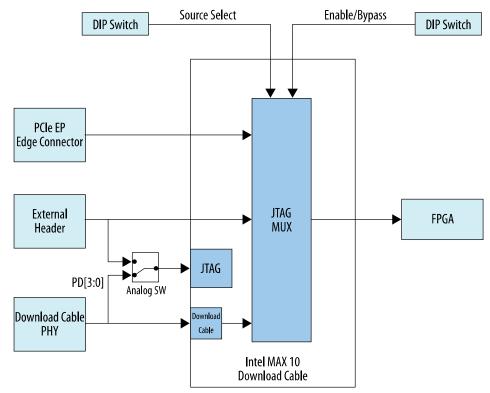

Figure 34 on page 48 shows the high-level conceptual block diagram for programming the FPGA over the embedded Intel FPGA Download Cable II or external download cable.

# A.9. Supported Configuration Modes

- The development board supports two configuration modes: Avalon-ST (AVST) x8 and JTAG.

- The default configuration is AVST x8 using a 2Gb QSPI flash device.

- JTAG configuration is supported by using either the embedded Intel FPGA Download Cable II or the Intel FPGA Download Cable II dongle.

#### Avalon-ST (AVST) x8 Mode

The SDM block in the Intel Agilex device controls the configuration process and interface. The Intel MAX 10 System Controller (U34) interfaces to the Intel Agilex FPGA in the AVST x8 mode. The Intel MAX 10 also interfaces to the QSPI flash in the active serial (AS) x4 mode. For the AS x4 mode, MSEL[2:0] configuration pin strapping (SW2) must be set to [110]. The flash device is Micron Technology 1.8V core, 1.8V I/O 2 Gigabit CFI NOR-type device (P/N: MT25QL02GBB8E12-0).

### **JTAG Configuration Mode**

The JTAG switch implemented in the Intel MAX 10 System Controller (U34) allows the selection of devices to be included in the JTAG chain. It is done by the settings of the DIP switch SW5. The embedded Intel FPGA Download Cable II (or external download cable) or PCIe JTAG can be selected as the source for programming the devices on the chain. The embedded Intel FPGA Download Cable II is the default setting for this configuration mode.

Figure 34. JTAG Block Diagram

The on-board Intel FPGA Download Cable II is implemented in an Intel MAX 10 device. A micro-USB connector connects to a CY7C68013A USB2 PHY provides the data to Intel MAX 10. This allows configuration of the FPGA using a USB cable directly connected to a PC running the Intel Quartus Prime software without requiring the external download cable dongle. An external download cable dongle can also be used on J12 to configure the FPGA.

# **A.10.** Memory Interfaces

Three independent memory interfaces are supported: Two independent on-board DDR4 and one dual DIMM sockets for DDR4 or DDR-T.

- The on-board DDR4 uses five 16Gb DDR4 single rank devices connecting to Bank 2B, 2E for memory component channel 0 and bank 2C, 2F for memory component channel 1. The total memory size of each channel is 16GB running at 1200MHz.

- The two 288-pin DIMM sockets interface to bank 3C, 3D for Dual DIMM memory. These sockets accept DDR4 module. These DIMM will support dual rank at frequency 1200MHZ 16GB per channel, and will support single rank at 1200MHZ 8GB per channel.

- Some board re-work is required for using DIMM sockets in 2-DPC configuration or different kinds of DDR4 modules. For more details of the resistor connections required to be present for the type of configuration used, refer to board schematic table.

# A.11. I2C

I2C supports communication between integrated circuits on a board. It is a simple two-wire bus that consists of a serial data line (SDA) and a serial clock (SCL). The Intel MAX 10 and the Intel Agilex devices use the I2C for reading and writing to the various components on the board such as programmable clock generators, VID regulators, analog-to-digital converters (ADC), and temperature sensors.

You can use the Intel Agilex or Intel MAX 10 as the I2C host to access these devices, change clock frequencies or get status information of the board such as voltage and temperature readings.

Table 9. I2C Device Address

| Туре                     | Bus             | Address   | Device     |

|--------------------------|-----------------|-----------|------------|

| FPGA/Intel MAX 10 I2C    | I2C1            | 0x74      | Si5391     |

| Address                  |                 | 0x6A      | Si52204    |

|                          |                 | 0x4E      | EM2130H    |

|                          |                 | 0x42      | EM2140P    |

|                          |                 | 0x45      | EM2120L    |

|                          |                 | 0x46      | EM2120L    |

|                          | I2C2            | 0x1E      | FPC202     |

|                          |                 | 0x57/0x5F | M24128     |

|                          |                 | 0x38      | MAX31730   |

|                          |                 | 0x3A      | MAX31730   |

|                          |                 | 0xA0      | QSFPDD_0   |

|                          |                 | 0xA0      | QSFPDD_1   |

|                          | I2C3            | 0xA0      | DDR4_DIMM0 |

|                          | PCIE_EP_3V3_I2C | 0xA2      | DDR4_DIMM1 |

| Intel MAX 10 I2C Address | AVS_I2C         | 0x47      | ED8401     |

Figure 35. I2C Chain

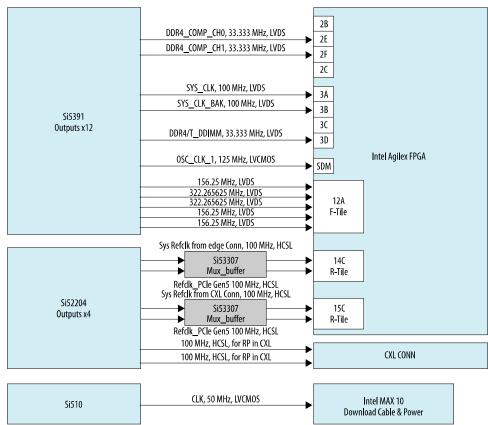

## A.12. Clock Circuits

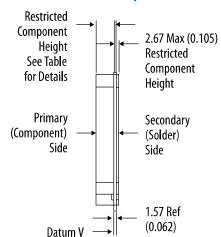

All clocks are supplied by three on-board low-jitter programmable clock generator circuits. The following is the clock connection diagram to the Intel Agilex FPGA. For detailed clock connections, refer to the schematic.