# FAIRCHILD

SEMICONDUCTOR

# DM74AS640 3-STATE Octal Bus Transceiver

#### **General Description**

This advanced Schottky device contains 8 pairs of 3-STATE logic elements configured as octal bus transceiver. This circuit is designed for use in memory, microprocessor systems and in asynchronous bidirectional data buses. This device transmits data from the A bus to the B bus, or vice versa, depending upon the logic level of the direction control input (DIR). The enable input ( $\overline{G}$ ) can be used to disable the devices, effecting isolation of buses A and B.

The 3-STATE circuitry also contains a protection feature that prevents these transceivers from glitching the bus during power-up or power-down.

#### Features

- Switching specifications at 50 pF

- $\blacksquare$  Switching specifications guaranteed over full temperature and  $V_{CC}$  range

- Advanced oxide-isolated, ion-implanted Schottky TTL process

- Functionally and pin for pin compatible with Schottky, low power Schottky, and advanced low power Schottky TTL counterpart

- Improved AC performance over Schottky, low power Schottky, and advanced low power Schottky counterparts

- 3-STATE outputs independently controlled on A and B buses

- Low output impedance drive to drive terminated transmission lines to 133Ω

- Specified to interface with CMOS at V<sub>OH</sub> = V<sub>CC</sub> 2V

#### **Ordering Code:**

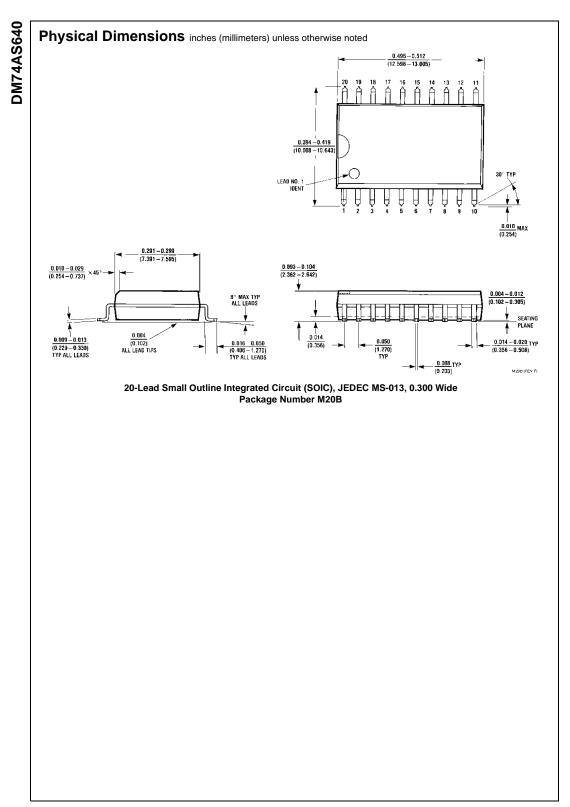

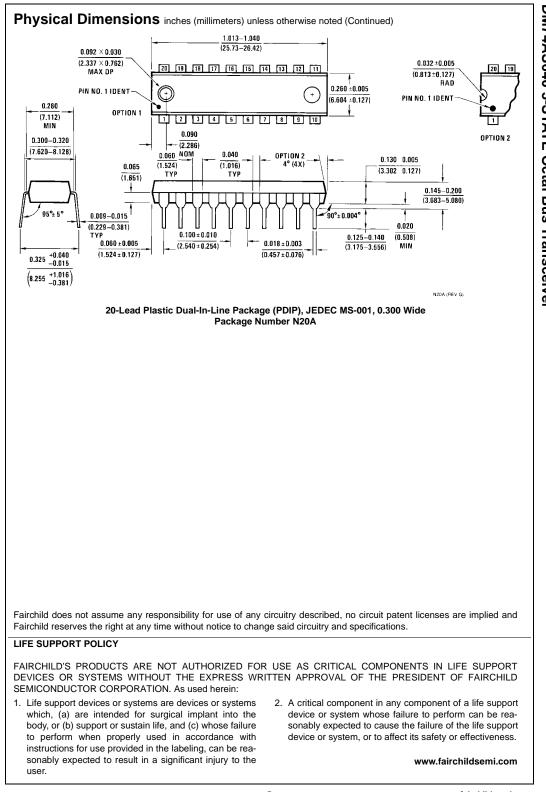

| Order Number | Package Number | Package Description                                                       |

|--------------|----------------|---------------------------------------------------------------------------|

| DM74AS640WM  | M20B           | 20-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-013, 0.300 Wide |

| DM74AS640N   | N20A           | 20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide     |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

#### **Connection Diagram** ENABLE B2 **B**3 85 R4 **B**6 16 8 TRANSCEIVERS DISABLE B DISABLE A DIR A2 A3 A4 Α5 A6 Δ7 A8 GND A1 **Top View**

### Function Table

| Contro | l Inputs | Operation       |  |  |  |

|--------|----------|-----------------|--|--|--|

| G      | DIR      | Operation       |  |  |  |

| L      | L        | B Data to A Bus |  |  |  |

| L      | н        | A Data to B Bus |  |  |  |

| Н      | Х        | Isolation       |  |  |  |

H = HIGH Logic Level L = LOW Logic Level X = Immaterial

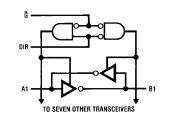

### Logic Diagram

© 2000 Fairchild Semiconductor Corporation DS006708

## Absolute Maximum Ratings(Note 1)

Note 1: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

## **Recommended Operating Conditions**

| Symbol          | Parameter                      | Min | Тур | Max | Units |

|-----------------|--------------------------------|-----|-----|-----|-------|

| V <sub>CC</sub> | Supply Voltage                 | 4.5 | 5   | 5.5 | V     |

| V <sub>IH</sub> | HIGH Level Input Voltage       | 2   |     |     | V     |

| V <sub>IL</sub> | LOW Level Input Voltage        |     |     | 0.8 | V     |

| I <sub>ОН</sub> | HIGH Level Output Current      |     |     | -15 | mA    |

| I <sub>OL</sub> | LOW Level Output Current       |     |     | 64  | mA    |

| T <sub>A</sub>  | Free Air Operating Temperature | 0   |     | 70  | °C    |

#### **Electrical Characteristics**

over recommended operating free air temperature range (unless otherwise noted)

| Symbol           | Parameter                        | Conditions                                   |                | Min                 | Typ<br>(Note 2) | Max   | Units |

|------------------|----------------------------------|----------------------------------------------|----------------|---------------------|-----------------|-------|-------|

| VI               | Input Clamp Voltage              | $V_{CC} = Min, I_I = -18 \text{ mA}$         |                |                     |                 | -1.2  | V     |

| V <sub>OH</sub>  | HIGH Level                       | $V_{CC} = 4.5V$ to 5.5V, $I_{OH} = -2$ mA    |                | V <sub>CC</sub> – 2 |                 |       | V     |

|                  | Output Voltage                   | $V_{CC} = 4.5V, I_{OH} = -3 \text{ mA}$      |                | 2.4                 |                 |       | V     |

|                  |                                  | $V_{CC} = 4.5 V$ , $I_{OH} = Max$            |                | 2.4                 |                 |       | V     |

| V <sub>OL</sub>  | LOW Level Output Voltage         | V <sub>CC</sub> = Min, I <sub>OL</sub> = Max |                |                     | 0.35            | 0.55  | V     |

| l <sub>l</sub>   | Input Current at Max             | $V_{CC} = Max, V_I = 7V,$                    |                |                     |                 | 0.4   |       |

|                  | Input Voltage                    | (V <sub>I</sub> = 5.5V for A or B Ports)     |                |                     |                 | 0.1   | mA    |

| IIH              | HIGH Level                       | V <sub>CC</sub> = Max                        | Control Inputs |                     |                 | 20    |       |

|                  | Input Current                    | V <sub>I</sub> = 2.7V (Note 3)               | A or B Ports   |                     |                 | 70    | μA    |

| IIL              | LOW Level                        | V <sub>CC</sub> = Max,                       | Control Inputs |                     |                 | -0.5  |       |

|                  | Input Current                    | V <sub>I</sub> = 0.4V (Note 3)               | A or B Ports   |                     |                 | -0.75 | mA    |

| I <sub>O</sub>   | Output Drive Current             | $V_{CC} = Max, V_O = 2.25V$                  |                | -50                 |                 | -150  | mA    |

| I <sub>CCH</sub> | Supply Current with Outputs HIGH | V <sub>CC</sub> = Max                        |                |                     | 37              | 58    | mA    |

| ICCL             | Supply Current with Outputs LOW  | 1                                            |                |                     | 78              | 123   | mA    |

| I <sub>CCZ</sub> | Supply Current with Outputs      | 1                                            |                |                     | 54              | 00    | A     |

|                  | in 3-STATE                       |                                              |                |                     | 51              | 80    | mA    |

Note 2: All typicals are at  $V_{CC} = 5.0V$ ,  $T_A = 25^{\circ}C$ .

Note 3: For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the OFF-State output current, I<sub>OZH</sub> and I<sub>OZL</sub>.

| Symbol           | Parameter                                          | From<br>(Input) | To<br>(Output) | $V_{CC} = Min \text{ to } Max,$<br>$C_1 = 50 \text{ pF}, R_1 = R_2 = 500\Omega$ |     | Units |

|------------------|----------------------------------------------------|-----------------|----------------|---------------------------------------------------------------------------------|-----|-------|

|                  |                                                    |                 |                | Min                                                                             | Max |       |

| t <sub>PLH</sub> | Propagation Delay Time<br>LOW-to-HIGH Level Output | A or B          | B or A         | 2                                                                               | 7   | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>HIGH-to-LOW Level Output | A or B          | B or A         | 2                                                                               | 6   | ns    |

| t <sub>PZH</sub> | Output Enable Time to<br>HIGH Level Output         | G               | A or B         | 2                                                                               | 8   | ns    |

| t <sub>PZL</sub> | Output Enable Time to<br>LOW Level Output          | G               | A or B         | 2                                                                               | 10  | ns    |

| t <sub>PHZ</sub> | Output Disable Time from<br>HIGH Level Output      | G               | A or B         | 2                                                                               | 8   | ns    |

| t <sub>PLZ</sub> | Output Disable Time from<br>LOW Level Output       | G               | A or B         | 2                                                                               | 13  | ns    |

DM74AS640

DM74AS640 3-STATE Octal Bus Transceive