### **General Description**

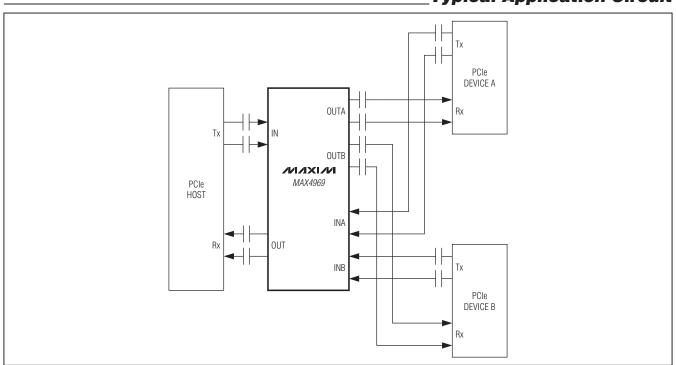

The MAX4969 active 2:1 and 1:2 multiplexer equalizes and redrives PCIe® signals up to 5.0GT/s (Gigatransfers per second) and operates from a single +3.3V supply.

The MAX4969 features PCIe-required electrical idle and receiver detection on each channel, and improves signal integrity at the receiver through independent programmable input equalization and output deemphasis.

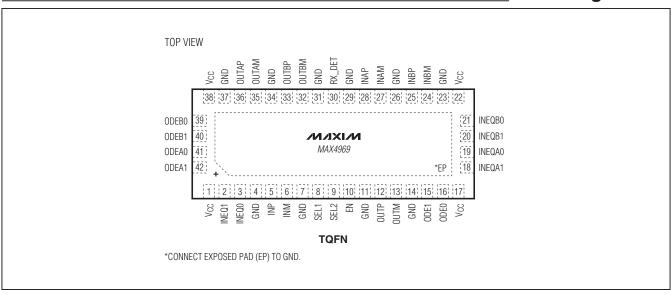

The MAX4969 is available in a small, 42-pin (3.5mm x 9.0mm) TQFN package optimal for simplified layout and space-saving requirements. The MAX4969 is specified over the 0°C to +70°C commercial operating temperature range.

### **Applications**

**Blade Servers**

Workstations

Communications Switches

Test Equipment

Storage Area Network

### **Features**

- ♦ Single +3.3V Supply Operation

- ◆ PCIe Gen 1 (2.5GT/s) and Gen 2 (5.0GT/s) Return Loss  $\geq$  8dB (1.25GHz  $\leq$  f  $\leq$  2.5GHz)

- ◆ Independent Input Equalization

- ◆ Independent Output Deemphasis

- Independent Output Level Selection **Reduced Power and EMI**

- ♦ On-Chip 50Ω Input/Output Terminations

- ♦ Inline Signal Traces for Simplified Layout

- ◆ Space-Saving, 3.5mm x 9.0mm TQFN Package

## **Ordering Information**

| PART        | TEMP RANGE   | PIN-PACKAGE |  |

|-------------|--------------|-------------|--|

| MAX4969CTO+ | 0°C to +70°C | 42 TQFN-EP* |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# Pin Configuration

PCIe is a registered trademark of PCI-SIG Corp.

<sup>\*</sup>EP = Exposed pad.

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to GND.)             |                      |

|-------------------------------------------|----------------------|

| Vcc                                       | 0.3V to +4.0V        |

| All Other Pins (Note 1)                   | 0.3V to (VCC + 0.3V) |

| Continuous Current, IN_P, IN_M, OUT_      | P, OUT_M ±30mA       |

| Peak Current, IN_P, IN_M, OUT_P,          |                      |

| OUT_M (for 10kHz, 1% duty cycle)          | ±100mA               |

| Continuous Power Dissipation ( $T_A = +7$ | 70°C)                |

| 42-Pin TQFN (derate 34.5mW/°C abo         | ove +70°C) 2758mW    |

| Junction-to-Case Thermal Resistance    |                |

|----------------------------------------|----------------|

| θ <sub>JC</sub> (Note 2)               | +2°C/W         |

| Junction-to-Ambient Thermal Resistance |                |

| θJA (Note 2)                           | +29°C/W        |

| Operating Temperature Range            | 0°C to +70°C   |

| Junction Temperature Range             | 40°C to +150°C |

| Storage Temperature Range              | 65°C to +150°C |

| Lead Temperature (soldering, 10s)      | +300°C         |

|                                        |                |

Note 1: All I/O pins are clamped by internal diodes.

**Note 2:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maxim-ic.com/thermal-tutorial">www.maxim-ic.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, C_{CL} = 75 \text{nF coupling capacitor on each output}, R_L = 50\Omega \text{ on each output}, T_A = 0^{\circ}\text{C} \text{ to } +70^{\circ}\text{C}, \text{ unless otherwise noted}.$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25^{\circ}\text{C}$ .) (Note 3)

| PARAMETER                                                       | SYMBOL                              | С                                                  | ONDITIONS          | MIN  | TYP | MAX  | UNITS |

|-----------------------------------------------------------------|-------------------------------------|----------------------------------------------------|--------------------|------|-----|------|-------|

| DC PERFORMANCE                                                  | DC PERFORMANCE                      |                                                    |                    |      |     |      |       |

| Power-Supply Range                                              | Vcc                                 |                                                    |                    | 3.0  |     | 3.6  | V     |

|                                                                 |                                     | EN Voc                                             | INEQ_ = ODE_ = GND |      | 120 | 150  |       |

| Supply Current                                                  | Icc                                 | EN = VCC                                           | INEQ_ = ODE_ = VCC |      | 160 | 200  | mA    |

|                                                                 |                                     | EN = GND                                           |                    |      | 50  |      |       |

| Input Impedance, Differential                                   | ZRX-DIFF-DC                         | DC                                                 |                    | 80   | 100 | 120  | Ω     |

| Output Impedance, Differential                                  | Z <sub>TX-DIFF-DC</sub>             | DC                                                 |                    | 80   | 100 | 120  | Ω     |

| Common-Mode Resistance to GND, Input Terminations Not           | ZRX-HIGH-IMP-<br>DC-POS             | VIN_P = VIN_M                                      | = 0 to 200mV       | 50   |     |      | kΩ    |

| Powered                                                         | ZRX-HIGH-IMP-<br>DC-NEG             | VIN_P = VIN_M                                      | = -150mV to 0V     | 1    |     |      | kΩ    |

| Common-Mode Resistance<br>to GND, Input Terminations<br>Powered | Z <sub>RX-DC</sub>                  | DC                                                 |                    | 40   | 50  | 60   | Ω     |

| Output Short-Circuit Current                                    | ITX-SHORT                           | Single-ended (Note 4)                              |                    |      |     | 90   | mA    |

| Common-Mode Delta, Between Active and Idle States               | VTX-CM-DC-<br>ACTIVE-IDLE-<br>DELTA |                                                    |                    | -100 |     | +100 | mV    |

| DC Output Offset, During<br>Active State                        | VTX-CM-DC-<br>LINE-DELTA            | Difference between DC average of VOUT_P and VOUT_M |                    | -25  |     | +25  | mV    |

| DC Output Offset, During<br>Electrical Idle                     | VTX-IDLE-DIFF-<br>DC                | ABS(V <sub>OUT_P</sub> - V <sub>OUT_M</sub> )      |                    | -10  |     | +10  | mV    |

| AC PERFORMANCE                                                  | AC PERFORMANCE                      |                                                    |                    |      |     |      |       |

| Input Return Loss, Differential                                 | DI DV DIES                          | 0.05GHz < f ≤                                      | 1.25GHz (Note 4)   | 10   |     |      | dB    |

| input neturn Loss, Dinerential                                  | RLRX-DIFF                           | 1.25GHz < f ≤ 2.5GHz (Note 4)                      |                    | 8    |     |      | dB    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, C_{CL} = 75 \text{nF} \text{ coupling capacitor on each output, } R_L = 50 \Omega \text{ on each output, } T_A = 0 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25 ^{\circ}\text{C}$ .) (Note 3)

| PARAMETER                                                 | SYMBOL                                | CONDITIONS                                                                                                              | MIN | TYP  | MAX  | UNITS             |

|-----------------------------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|------|-------------------|

| Input Return Loss, Common Mode                            | RL <sub>RX</sub> -CM                  | 0.05GHz < f ≤ 2.5GHz (Note 4)                                                                                           | 6   |      |      | dB                |

| Output Datum Laga Differential                            | DI = = . = =                          | 0.05GHz < f ≤ 1.25GHz (Note 4)                                                                                          | 10  |      |      | dB                |

| Output Return Loss, Differential                          | RLTX-DIFF                             | 1.25GHz < f ≤ 2.5GHz (Note 4)                                                                                           | 8   |      |      | dB                |

| Output Return Loss, Common<br>Mode                        | RLTX-CM                               | 0.05GHz < f ≤ 2.5GHz (Note 4)                                                                                           | 6   |      |      | dB                |

| Differential Input Signal Range,<br>Redriver Operation    | VRX-DIFF-PP                           | 0.05GHz < f ≤ 2.5GHz                                                                                                    | 150 |      | 1200 | mV <sub>P-P</sub> |

| Differential Output Voltage, Full<br>Swing, No Deemphasis | VTX-DIFF-PP                           | 2 x ABS(V <sub>OUT_P</sub> - V <sub>OUT_M</sub> ),<br>ODE_1 = GND, ODE_0 = V <sub>CC</sub><br>(see Table 1), f = 500MHz | 800 | 1000 | 1200 | mV <sub>P-P</sub> |

| Differential Output Voltage, Low<br>Swing, No Deemphasis  | VTX-DIFF-PP-<br>LOW                   | 2 x ABS(V <sub>OUT_P</sub> - V <sub>OUT_M</sub> ),<br>ODE_1 = ODE_0 = GND (see Table 1),<br>f = 500MHz                  | 600 | 750  | 900  | mVp-p             |

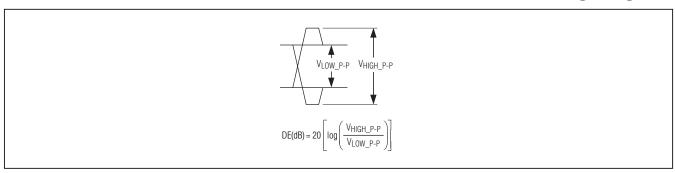

| Output Deemphasis Ratio, 0dB                              | VTX-DE-RATIO-<br>0dB                  | f = 2.5GHz, ODE_1 = GND, ODE_0 = V <sub>CC</sub> or GND, Figure 1 (see Table 1)                                         |     | 0    |      | dB                |

| Output Deemphasis Ratio, 3.5dB                            | VTX-DE-RATIO-<br>3.5dB                | f = 2.5GHz, ODE_1 = VCC,<br>ODE_0 = GND, Figure 1 (see Table 1)                                                         |     | 3.5  |      | dB                |

| Output Deemphasis Ratio, 6dB                              | VTX-DE-RATIO-<br>6dB                  | f = 2.5GHz, ODE_1 = V <sub>CC</sub> ,<br>ODE_0 = V <sub>CC</sub> , Figure 1 (see Table 1)                               |     | 6    |      | dB                |

| Input Equalization, 0dB                                   | VRX-EQ-0dB                            | f = 2.5GHz, INEQ_1 = GND,<br>INEQ_0 = GND or V <sub>CC</sub> (see Table 2)                                              |     | 0    |      | dB                |

| Input Equalization, 3.5dB                                 | VRX-EQ-3.5dB                          | f = 2.5GHz, INEQ_1 = V <sub>CC</sub> ,<br>INEQ_0 = GND (see Table 2)                                                    |     | 3.5  |      | dB                |

| Input Equalization, 6dB                                   | VRX-EQ-6dB                            | f = 2.5GHz, INEQ_1 = V <sub>CC</sub> , INEQ_0 = V <sub>CC</sub> (see Table 2)                                           |     | 6    |      | dB                |

| Output Common-Mode Voltage                                | VTX-CM-AC-PP                          | MAX(V <sub>OUT_P</sub> + V <sub>OUT_M</sub> )/2 -<br>MIN(V <sub>OUT_P</sub> + V <sub>OUT_M</sub> )/2 (Note 4)           |     |      | 100  | mV <sub>P-P</sub> |

| Propagation Delay                                         | TPD                                   | (Note 4)                                                                                                                | 160 | 280  | 400  | ps                |

| Rise/Fall Time                                            | TTX-RISE-FALL                         | (Notes 4, 5)                                                                                                            | 30  |      |      | ps                |

| Rise/Fall Time Mismatch                                   | T <sub>TX-RF-</sub><br>MISMATCH       | (Notes 4, 5)                                                                                                            |     |      | 20   | ps                |

| Output Skew Same Pair                                     | Tsk                                   | (Note 4)                                                                                                                |     | 10   | 15   | ps                |

| Deterministic Jitter                                      | T <sub>TX-DJ-DD</sub>                 | $K28.5 \le$ pattern, AC-coupled, $R_L = 50\Omega$ , effects of deemphasis deembedded (Note 4), 5GT/s                    |     | 20   |      | psp-p             |

| Random Jitter                                             | T <sub>TX-RJ-DD</sub>                 | D10.2 pattern, f > 1.5MHz                                                                                               |     | 0.5  | 1.4  | psRMS             |

| Electrical Idle Entry Delay                               | TTX-IDLE-SET-<br>TO-IDLE              | From input to output                                                                                                    |     | 15   |      | ns                |

| Electrical Idle Exit Delay                                | T <sub>TX-IDLE-TO-</sub><br>DIFF-DATA | From input to output                                                                                                    |     | 8    |      | ns                |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, C_{CL} = 75 \text{nF coupling capacitor on each output}, R_L = 50 \Omega$  on each output,  $T_A = 0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3 \text{V}$  and  $T_A = +25^{\circ}\text{C}$ .) (Note 3)

| PARAMETER                                     | SYMBOL                 | CONDITIONS                                    | MIN  | TYP | MAX | UNITS |

|-----------------------------------------------|------------------------|-----------------------------------------------|------|-----|-----|-------|

| Electrical Idle Detect Threshold              | VTX-IDLE-<br>THRESH    |                                               | 65   | 100 | 120 | mVp-p |

| Output Voltage During<br>Electrical Idle (AC) | VTX-IDLE-DIFF-<br>AC-P | ABS(Vout_p - Vout_m)                          |      |     | 35  | mVp-p |

| Receiver Detect Pulse<br>Amplitude            | VTX-RCV-<br>DETECT     | Voltage change in positive direction (Note 4) |      |     | 600 | mV    |

| Receiver Detect Pulse Width                   |                        |                                               |      | 100 |     | ns    |

| Receiver Detect Retry Period                  |                        |                                               |      | 200 |     | ns    |

| CONTROL LOGIC                                 |                        |                                               |      |     |     |       |

| Input Logic-Level Low                         | VIL                    |                                               |      |     | 0.6 | V     |

| Input Logic-Level High                        | VIH                    |                                               | 1.4  |     |     | V     |

| Input Logic Hysteresis                        | VHYST                  |                                               |      | 130 |     | mV    |

| Input Pulldown Resistor                       | RDOWN                  |                                               | 37.5 | 60  | 150 | kΩ    |

Note 3: All devices are 100% production tested at  $T_A = +70^{\circ}C$ . Specifications for all temperature limits are guaranteed by design.

Note 4: Guaranteed by design.

Note 5: Rise and fall times are measured using 20% and 80% levels.

## Timing Diagram

Figure 1. Illustration of Output Deemphasis

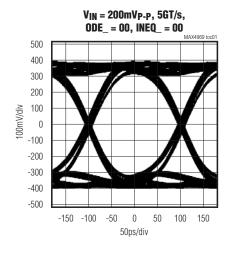

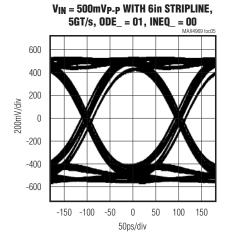

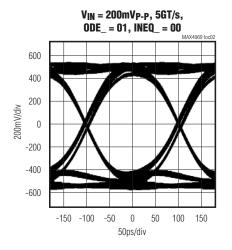

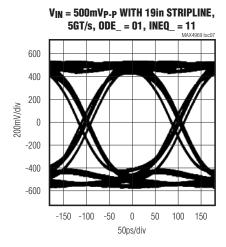

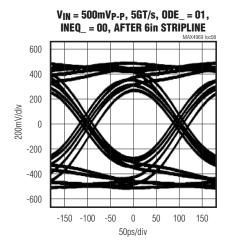

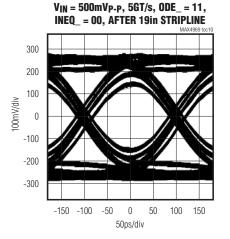

**Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

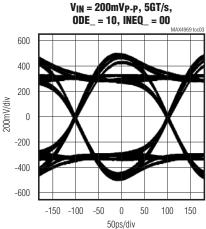

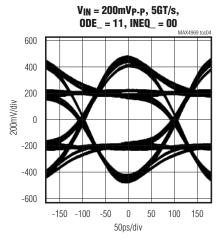

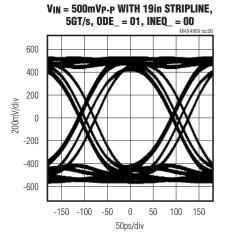

Typical Operating Characteristics (continued)

$(VCC = +3.3V, TA = +25^{\circ}C, unless otherwise noted.)$

# \_Pin Description

| PIN                                        | NAME   | FUNCTION                                                                                                                                                                             |

|--------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 17, 22,<br>38                           | Vcc    | Power-Supply Input. Bypass VCC to GND with 1µF and 0.01µF capacitors in parallel as close to the device as possible, recommended on each VCC pin.                                    |

| 2                                          | INEQ1  | Channel 1 Input Equalization Control MSB. See Table 2. INEQ1 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                              |

| 3                                          | INEQ0  | Channel 1 Input Equalization Control LSB. See Table 2. INEQ0 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                              |

| 4, 7, 11, 14,<br>23, 26, 29,<br>31, 34, 37 | GND    | Ground                                                                                                                                                                               |

| 5                                          | INP    | Channel 1 Noninverting Input                                                                                                                                                         |

| 6                                          | INM    | Channel 1 Inverting Input                                                                                                                                                            |

| 8                                          | SEL1   | Channel 1 Active Output Selection Input. Drive SEL1 low to activate A outputs. Drive SEL high to activate B outputs. SEL1 is internally pulled down by a $60k\Omega$ (typ) resistor. |

| 9                                          | SEL2   | Channel 2 Active Input Selection Input. Drive SEL2 low to activate A inputs. Drive SEL high to activate B inputs. SEL2 is internally pulled down by a $60k\Omega$ (typ) resistor.    |

| 10                                         | EN     | Enable Input. Drive EN low for reduced power standby mode. Drive EN high for normal operation. EN is internally pulled down by a $60k\Omega$ (typ) resistor.                         |

| 12                                         | OUTP   | Channel 2 Noninverting Output                                                                                                                                                        |

| 13                                         | OUTM   | Channel 2 Inverting Output                                                                                                                                                           |

| 15                                         | ODE1   | Channel 2 Output Deemphasis Control MSB. See Table 1. ODE1 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                                |

| 16                                         | ODE0   | Channel 2 Output Deemphasis Control LSB. See Table 1. ODE0 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                                |

| 18                                         | INEQA1 | Channel 2 Input A Equalization Control MSB. See Table 2. INEQA1 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                           |

| 19                                         | INEQA0 | Channel 2 Input A Equalization Control LSB. See Table 2. INEQA0 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                           |

| 20                                         | INEQB1 | Channel 2 Input B Equalization Control MSB. See Table 2. INEQB1 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                           |

| 21                                         | INEQB0 | Channel 2 Input B Equalization Control LSB. See Table 2. INEQB0 is internally pulled down by a $60 \text{k}\Omega$ (typ) resistor.                                                   |

| 24                                         | INBM   | Channel 2 Inverting Input B                                                                                                                                                          |

| 25                                         | INBP   | Channel 2 Noninverting Input B                                                                                                                                                       |

| 27                                         | INAM   | Channel 2 Inverting Input A                                                                                                                                                          |

| 28                                         | INAP   | Channel 2 Noninverting Input A                                                                                                                                                       |

| 30                                         | RX_DET | Receiver Detection Control Bit. Toggle RX_DET to initiate receiver detection. RX_DET is internally pulled down by a $60k\Omega$ (typ) resistor.                                      |

| 32                                         | OUTBM  | Channel 1 Inverting Output B                                                                                                                                                         |

| 33                                         | OUTBP  | Channel 1 Noninverting Output B                                                                                                                                                      |

| 35                                         | OUTAM  | Channel 1 Inverting Output A                                                                                                                                                         |

| 36                                         | OUTAP  | Channel 1 Noninverting Output A                                                                                                                                                      |

| 39                                         | ODEB0  | Channel 1 Output B Deemphasis Control LSB. See Table 1. ODEB0 is internally pulled down by a $60k\Omega$ (typ) resistor.                                                             |

# **Pin Description**

| PIN | NAME  | FUNCTION                                                                                                                                                            |

|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40  | ODEB1 | Channel 1 Output B Deemphasis Control MSB. See Table 1. ODEB1 is internally pulled down by a $60k\Omega$ (typ) resistor.                                            |

| 41  | ODEA0 | Channel 1 Output A Deemphasis Control LSB. See Table 1. ODEA0 is internally pulled down by a $60k\Omega$ (typ) resistor.                                            |

| 42  | ODEA1 | Channel 1 Output A Deemphasis Control MSB. See Table 1. ODEA1 is internally pulled down by a $60k\Omega$ (typ) resistor.                                            |

| _   | EP    | Exposed Pad. Internally connected to GND. Connect EP to a large ground plane to maximize thermal performance. EP is not intended as an electrical connection point. |

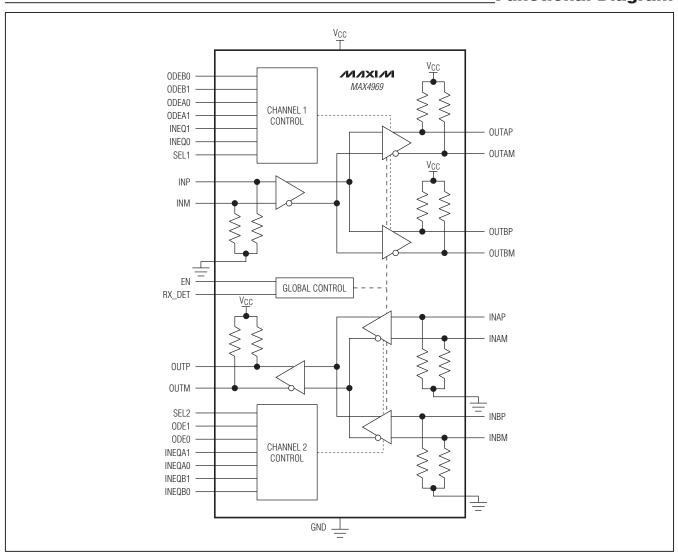

# **Functional Diagram**

## **Detailed Description**

The MAX4969 is an active 2:1/1:2 multiplexer designed to equalize and redrive PCle signals up to 5.0GT/s. The MAX4969 features PCle-required electrical idle and receiver detection on each channel, and improves signal integrity at the receiver through independent programmable input equalization and output deemphasis.

### **Enable Input (EN)**

The MAX4969 features an active-high enable input (EN). EN has an internal pulldown resistor of  $60k\Omega$  (typ). When EN is driven low or left unconnected, the MAX4969 enters reduced power standby mode and the redrivers are disabled. Drive EN high for normal operation.

#### **Active Input/Output Select (SEL1, SEL2)**

SEL1 selects the active output for channel 1 and SEL2 selects the active input for channel 2. Drive SEL1 or SEL2 low or leave unconnected to activate A inputs or outputs. Drive SEL1 or SEL2 high to activate B inputs or outputs. SEL1 and SEL2 have internal pulldown resistors of  $60k\Omega$  (typ).

**Table 1. Output Deemphasis**

| ODE_1 | ODE_0 | OUTPUT DEEMPHASIS<br>(dB) |

|-------|-------|---------------------------|

| 0     | 0     | 0, low swing              |

| 0     | 1     | 0, full swing             |

| 1     | 0     | 3.5, full swing           |

| 1     | 1     | 6, full swing             |

**Table 2. Input Equalization**

| INEQ_1 | INEQ_0 | INPUT EQUALIZATION<br>(dB) |

|--------|--------|----------------------------|

| 0      | X      | 0                          |

| 1      | 0      | 3.5                        |

| 1      | 1      | 6                          |

X = Don't Care

# Programmable Output Deemphasis (ODE\_0, ODE\_1)

The MAX4969 features independent programmable output deemphasis capable of providing 0dB, 3.5dB, or 6dB deemphasis on any channel. When both ODE\_0 and ODE\_1 are driven low or left unconnected, the output is in low-swing mode (750mV typ) (see Table 1). ODE0, ODE1, ODEA0, ODEA1, ODEB0, and ODEB1 have internal pulldown resistors of  $60k\Omega$  (typ).

# Programmable Input Equalization (INEQ\_0, INEQ\_1)

The MAX4969 features independent programmable input equalization capable of providing 0dB, 3.5dB, or 6dB of high-frequency equalization on any channel (see Table 2.) INEQ0, INEQ1, INEQA0, INEQA1, INEQB0, and INEQB1 have internal pulldown resistors of  $60k\Omega$  (typ).

#### Receiver Detection (RX\_DET)

The MAX4969 features receiver detection on each channel. Receiver detection initializes on the rising edge of EN, or upon initial power-up if EN is high. Receiver detection can also be initiated on a rising or falling edge of the RX\_DET, SEL1, or SEL2 inputs when EN is high. During this time, the part remains in reduced power standby mode and the outputs are squelched, despite the logic-high state of EN. Once started, receiver detection repeats indefinitely on each channel. Once a receiver is detected on one of the channels, up to  $2^{16}$  more attempts are made on the other channel. Upon receiver detection, channel output and electrical idle detection are enabled (see Table 3). RX\_DET has an internal pull-down resistor of  $60\text{k}\Omega$  (typ).

#### **Electrical Idle Detection**

The MAX4969 features electrical idle detection to prevent unwanted noise from being redriven at the output. If the MAX4969 detects that the differential input has fallen below VTX-IDLE-THRESH, the MAX4969 squelches the output. For differential input signals that are above VTX-IDLE-THRESH, the MAX4969 turns on the output and redrives the signal.

| Table | 3 [  | Receiver | <b>Detection</b> |

|-------|------|----------|------------------|

| lable | О. Г | receivei | Detection        |

| RX_DET/<br>SEL1/SEL2   | EN | DESCRIPTION                                                                  |  |

|------------------------|----|------------------------------------------------------------------------------|--|

| X                      | 0  | Receiver detection inactive                                                  |  |

| 0                      | 1  | Following a rising or falling edge; indefinite retry until receiver detected |  |

| Rising or falling edge | 1  | Initiate receiver detection                                                  |  |

| 1                      | 1  | Following a rising or falling edge; indefinite retry until receiver detected |  |

X = Don't Care

## **Typical Application Circuit**

## Applications Information

#### Layout

Circuit board layout and design can significantly affect the performance of the MAX4969. Use good high-frequency design techniques, including minimizing ground inductance and using controlled-impedance transmission lines on data signals. It is recommended to run receive and transmit on different layers to minimize crosstalk and to place 1µF and 0.01µF power-supply bypass capacitors in parallel as close to VCC as possible on each VCC pin. Always connect VCC to a power plane.

#### **Exposed Pad Package**

The exposed-pad, 42-pin TQFN package incorporates features that provide a very low thermal resistance path for heat removal from the IC. The exposed pad on the MAX4969 must be soldered to the circuit board ground plane for proper thermal performance. For more information on exposed-pad packages, refer to Application Note 862: HFAN-08.1: Thermal Considerations of QFN and Other Exposed-Paddle Packages.

#### **Power-Supply Sequencing**

Caution: Do not exceed the absolute maximum ratings because stresses beyond the listed ratings may cause permanent damage to the device.

Proper power-supply sequencing is recommended for all devices. Always apply GND then VCC before applying signals, especially if the signal is not current limited.

**Chip Information**

PROCESS: BICMOS

# \_Package Information

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 42 TQFN-EP   | T423590+1    | <u>21-0181</u> |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

10 Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600