# LMH9126 Evaluation Module

This document outlines the basic steps and functions that are required to ensure the proper operation and quick setup of the LMH9126RRL-EVM. This document also includes a schematic diagram, a bill of materials (BOM), printed-circuit board (PCB) layouts, and test block diagrams. Throughout this document, the abbreviations *EVM*, *LMH9126 EVM* and the term *evaluation module* are synonymous with the LMH9126RRL-EVM, unless otherwise noted.

### Contents

| 1 | Description |                                    |     |  |  |  |  |

|---|-------------|------------------------------------|-----|--|--|--|--|

|   | 1.1         | Features                           | . 2 |  |  |  |  |

|   | 1.2         | General Usage Information          | . 3 |  |  |  |  |

| 2 | EVM         | EVM Overview                       |     |  |  |  |  |

|   | 2.1         | Schematic                          |     |  |  |  |  |

|   | 2.2         | PCB Layers                         | . 5 |  |  |  |  |

|   | 2.3         | LMH9126 EVM Bill of Material       |     |  |  |  |  |

|   | 2.4         | Stack-Up and Material              | . 8 |  |  |  |  |

| 3 | Test        | Test Setup Diagrams                |     |  |  |  |  |

|   | 3.1         | Single-Tone Measurement Test Setup | . 9 |  |  |  |  |

|   | 3.2         | S-Parameter Test Setup             |     |  |  |  |  |

|   | 3.3         | Noise Figure Test Setup            | 11  |  |  |  |  |

|   | 3.4         | Two-Tone OIP3 Test Setup           | 12  |  |  |  |  |

### List of Figures

| 1  | General Test Setup                                                  | 2  |

|----|---------------------------------------------------------------------|----|

| 2  | LMH9126 EVM Schematic                                               | 4  |

| 3  | Top Layer                                                           | 5  |

| 4  | Layer 2                                                             | 5  |

| 5  | Layer 3                                                             | 6  |

| 6  | Bottom Layer                                                        | 6  |

| 7  | LMH9126 EVM Stack-Up (Units in Mils)                                | 8  |

| 8  | Single-Tone Setup for Gain and Output P1dB (1-dB Compression Point) | 9  |

| 9  | S-Parameter Test Setup                                              | 10 |

| 10 | Noise Figure Test Setup                                             | 11 |

| 11 | OIP3 Test Setup                                                     |    |

|    |                                                                     |    |

### List of Tables

1 LMH9126 EVM BOM ...... 7

### Trademarks

Isola is a registered trademark of Isola USA Corporation. All other trademarks are the property of their respective owners.

### Description

### 1 Description

The LMH9126 evaluation module (EVM) is used to evaluate the LMH9126 device, which is a differential input to single-ended output RF gain block amplifier available in a 2 × 2-mm<sup>2</sup>, 12-pin RRL package. The device is well-suited to support requirements for the next generation 5G m-MIMO active antenna system (AAS) while interfacing with the output of transceiver. The EVM is designed to quickly demonstrate the functionality and performance of the LMH9126 device in the 2.2-GHz to 3-GHz transmit frequency band with 400 MHz of 1-dB bandwidth.

By default, the board is set up for 100- $\Omega$  differential input matching and 50- $\Omega$  single-ended output matching for easy interface with 50- $\Omega$  test equipment. The EVM is ready to connect to a +3.3-V power supply, signal source, and test instruments through the use of onboard connectors.

### 1.1 Features

- Operates on single +3.3-V supply

- Designed for differential 100-Ω input matching and 50-Ω single-ended output matching interface

- · Simple interface to the inputs and output through onboard SMA connectors

- Power down option available onboard using jumper connector

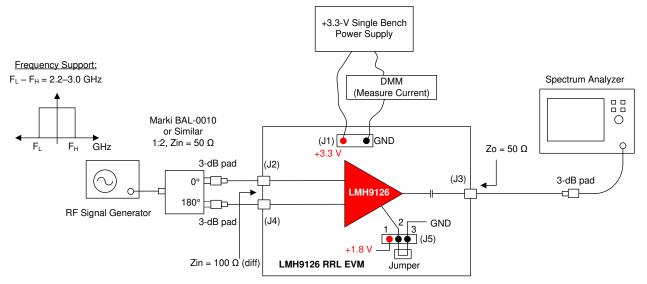

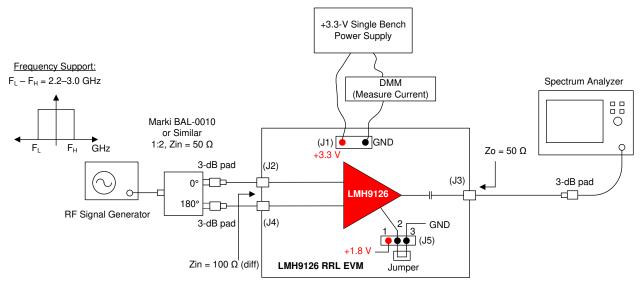

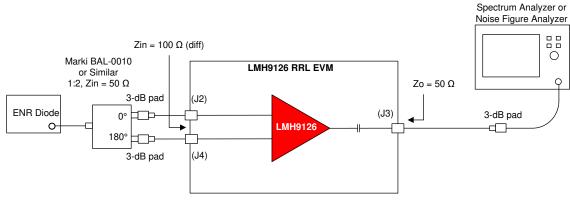

Figure 1. General Test Setup

### 1.2 General Usage Information

This section provides general usage information for the LMH9126 EVM. See Figure 1 for a general singletone setup diagram as a reference point to the following instructions. Some components such as supply bypass capacitors, and power down reference voltage generation are omitted in Figure 1 for clarity.

- 1. Recommended power up sequence:

- a. Before connecting the power-supply cables to the EVM, set the DC output power supply to +3.3 V.

- b. Set the current limit of the DC output power supply at 200 mA.

- c. Making sure the supply is turned off, connect the power supply cables to the J1 connector.

- d. Now turn on the DC power supply of VCC = +3.3 V. The supply current ( $I_Q$ ) drawn from the power supply should be approximately 100 mA.

- e. If the supply current is low, ensure the device is not disabled by shorting the jumper connection for J5 between 2 and 3 header pins.

- 2. Power-down option:

- a. Short terminals 1 and 2 on J5 to put the LMH9126 device in its power down state. The supply current ( $I_{Q}$ ) drawn should be < 15 mA.

3

Description

## 2 EVM Overview

This section includes the schematic diagram, a BOM, PCB layer prints, and EVM stack-up information.

## 2.1 Schematic

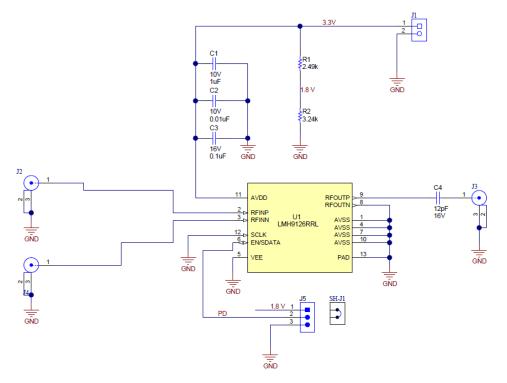

Figure 2 shows the LMH9126 EVM schematic.

Figure 2. LMH9126 EVM Schematic

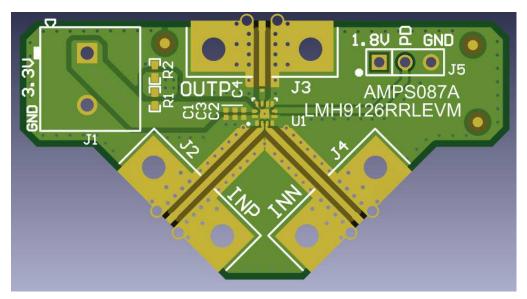

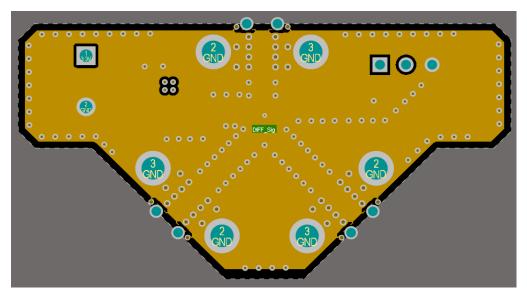

# 2.2 PCB Layers

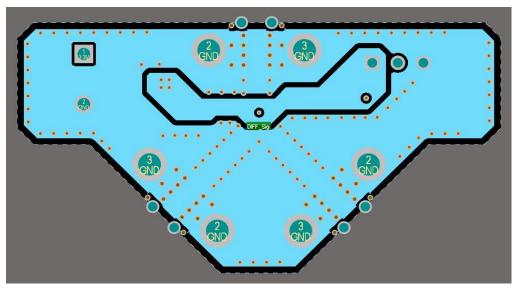

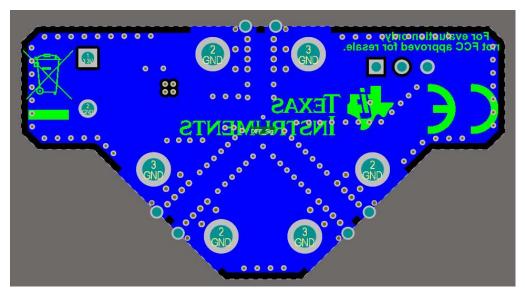

Figure 3 through Figure 6 illustrate the PCB layers for this EVM.

Figure 3. Top Layer

Figure 4. Layer 2

Figure 5. Layer 3

Figure 6. Bottom Layer

# 2.3 LMH9126 EVM Bill of Material

| Item # | Designator          | Qty. | Value  | Description                                                | Footprint                    | PartNumber             | Manufacturer                      | Alternate<br>PartNumber | Alternate<br>Manufacturer |

|--------|---------------------|------|--------|------------------------------------------------------------|------------------------------|------------------------|-----------------------------------|-------------------------|---------------------------|

| 1      | PCB1                | 1    |        | Printed Circuit<br>Board                                   |                              | AMPS087                | Any                               |                         |                           |

| 2      | C1                  | 1    | 1uF    | CAP, CERM, 1 uF,<br>10 V, +/- 20%, X5R,<br>0201            | 0201                         | CL03A105MP3NSN<br>C    | Samsung<br>Electro-<br>Mechanics  |                         |                           |

| 3      | C2                  | 1    | 0.01uF | CAP, CERM, 0.01<br>uF, 10 V, +/- 10%,<br>X7R, 0201         | 0201                         | GRM033R71A103K<br>A01D | MuRata                            |                         |                           |

| 4      | СЗ                  | 1    | 0.1uF  | CAP, CERM, 0.1<br>uF, 16 V, +/- 10%,<br>X5R, 0201          | 0201_033                     | GRM033C71C104K<br>E14D | MuRata                            |                         |                           |

| 5      | C4                  | 1    | 12pF   | CAP, Film, 12 pF,<br>16 V,+/- 2%, 0201<br>SMD              | ACCU_0201                    | 0201YK120GBSTR         | AVX                               |                         |                           |

| 6      | J1                  | 1    |        | Terminal Block,<br>5.08 mm, 2x1, TH                        | PhoenixContact_<br>1715721   | 1715721                | Phoenix Contact                   |                         |                           |

| 7      | J2, J3, J4          | 3    |        | SMA JACK 50<br>OHM, R/A, SMT                               | Rosenberger_32<br>K243-40ML5 | 32K243-40ML5           | Rosenberger                       |                         |                           |

| 8      | J5                  | 1    |        | Header, 100mil,<br>3x1, Tin, TH                            | CONN_PEC03S<br>AAN           | PEC03SAAN              | Sullins<br>Connector<br>Solutions |                         |                           |

| 9      | R1                  | 1    | 2.49k  | RES, 2.49 k, 1%,<br>0.063 W, AEC-<br>Q200 Grade 0,<br>0402 | 0402                         | CRCW04022K49FK<br>ED   | Vishay-Dale                       |                         |                           |

| 10     | R2                  | 1    | 3.24k  | RES, 3.24 k, 1%,<br>0.063 W, AEC-<br>Q200 Grade 0,<br>0402 | 0402                         | CRCW04023K24FK<br>ED   | Vishay-Dale                       |                         |                           |

| 11     | SH-J1               | 1    | 1x2    | Shunt, 100mil, Gold plated, Black                          | SNT-100-BK-G                 | SNT-100-BK-G           | Samtec                            | 969102-0000-<br>DA      | ЗМ                        |

| 12     | U1                  | 1    |        | LMH9126RRL,<br>RRL0012A (WQFN-<br>12)                      | RRL0012A                     | LMH9126RRL             | Texas<br>Instruments              |                         | Texas<br>Instruments      |

| 13     | FID1, FID2,<br>FID3 | 0    |        | Fiducial mark.<br>There is nothing to<br>buy or mount.     | Fiducial10-20                | N/A                    | N/A                               |                         |                           |

### Table 1. LMH9126 EVM BOM

EVM Overview

## 2.4 Stack-Up and Material

The LMH9126 EVM is a 56-mil, 4-layer board whose material type is Isola<sup>®</sup> 370HR. The top layer routes the power, ground, and signals to and from the device. The signal impedance is targeted at 49.9  $\Omega$ . The bottom 3 layers are ground layers.

| Layer  | Stack up      | Туре   | Supplier | Supplier<br>Description | Description  | Base<br>Thickness        | Impedance ID | Mask<br>Thickness | Processed<br>Thickness   | er    |

|--------|---------------|--------|----------|-------------------------|--------------|--------------------------|--------------|-------------------|--------------------------|-------|

| 1      |               | Copper |          |                         | Copper Foil  | 0.579                    | 1, 2, 3      |                   | 1.760                    |       |

|        |               | FR4    | isola    | 370HR                   | PrePreg 2116 | 4.331                    |              |                   | 4.308                    | 4.100 |

|        |               | FR4    | isola    | 370HR                   | PrePreg 2116 | 4.331                    |              |                   | 4.308                    | 4.100 |

|        |               | FR4    | isola    | 370HR                   | PrePreg 1080 | 2.559                    |              |                   | 2.546                    | 3.930 |

| 2<br>3 | +10.00%/      | FR4    | isola    | 370HR                   | Core         | 1.181<br>27.953<br>1.181 |              |                   | 1.181<br>27.953<br>1.181 | 4.360 |

|        |               | FR4    | isola    | 370HR                   | PrePreg 1080 | 2.559                    |              |                   | 2.546                    | 3.930 |

|        | 65 39         | FR4    | isola    | 370HR                   | PrePreg 2116 | 4.331                    |              |                   | 4.308                    | 4.100 |

|        | <sup>60</sup> | FR4    | isola    | 370HR                   | PrePreg 2116 | 4.331                    |              |                   | 4.308                    | 4.100 |

| 4      |               | Copper |          |                         | Copper Foil  | 0.579                    | 4, 5, 6      |                   | 1.760                    |       |

Figure 7. LMH9126 EVM Stack-Up (Units in Mils)

### 3 Test Setup Diagrams

This section includes general recommendations for single-tone, S-parameter, noise figure, and two-tone OIP3 setup while measuring the LMH9126 EVM.

# 3.1 Single-Tone Measurement Test Setup

### Figure 8. Single-Tone Setup for Gain and Output P1dB (1-dB Compression Point)

Use the following guidelines for single-tone measurement:

- 1. The input to the EVM is differential. Differential signal is generated from the single-ended output of the signal generator using an external passive balun such as shown in Figure 8. Use of at least 3-dB attenuator pads are recommended at the differential ports of the balun for better matching with the board.

- 2. The differential signals are fed into connectors J2 and J4.

- 3. The RF signal generator used must support 2.2-GHz to 3-GHz signal frequency for testing out the LMH9126 EVM.

- 4. When measuring the EVM for single-tone distortion products, TI recommends using an RF band pass filter (not shown in Figure 8) between the signal source and the balun.

- 5. The output of the EVM from connector J3 is fed to the spectrum analyzer. An attenuator pad of at least 3 dB is recommended at the output port of the EVM.

- 6. Lastly, it is recommended to properly characterize and account for the insertion loss of RF coaxial (coax) cables, attenuator pads, and passive baluns to measure accurate gain and power levels for the device.

Test Setup Diagrams

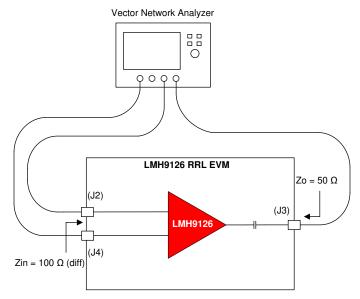

### 3.2 S-Parameter Test Setup

Figure 9. S-Parameter Test Setup

Use the following guidelines for S-parameter measurement:

- 1. S-parameter measurement is typically done using a Vector Network Analyzer (VNA), as Figure 9 shows. For measuring the LMH9126 EVM, a 4-port VNA is recommended which can generate and receive truly differential signals at the input and output ports.

- Before connecting the RF coax cables to the LMH9126 EVM, you must calibrate the VNA along with the cables using a calibration kit. This accounts for any cable losses in the S-parameter calculation at the VNA and helps set reference impedance at the cable ends.

- 3. Make sure the frequency sweep and output power level from the VNA is set within the linear operating range of the LMH9126 devices. The resolution bandwidth (RBW) and dynamic range of the VNA can be adjusted to give optimum sweep time for the measurement.

- 4. The trace + connector loss for the board is about 0.35 dB for the input trace (differential) and about 0.3 dB for the output trace in the middle of the frequency band. This may be accounted for improved accuracy in the measurements.

### 3.3 Noise Figure Test Setup

Figure 10. Noise Figure Test Setup

Use the following guidelines for Noise Figure (NF) measurement:

- 1. The traditional Y-factor method can be used for the NF measurement using a Noise Diode and a spectrum analyzer (or a Noise Figure Analyzer), as Figure 10 shows.

- While doing the measurement, take into account any RF cable losses to the EVM board. Any external input attenuator added for matching will result in proportional NF degradation and must be calibrated out in the measurement.

- 3. Also, onboard losses of the input traces at the device input pin must be factored into the NF measurement.

- 4. If the device output loss is significant, it is important to factor the output loss into the NF measurement.

- 5. Use the *Friis* equation to calculate the combined NF of the measurement setup and then back calculate the individual device noise figure.

Test Setup Diagrams

www.ti.com

### 3.4 Two-Tone OIP3 Test Setup

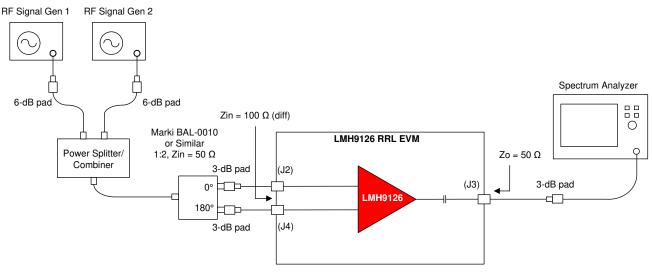

Figure 11. OIP3 Test Setup

Use the following guidelines for two-tone OIP3 measurement:

- 1. As Figure 11 shows, combine two signal generator outputs using an in-phase power splitter / combiner. A 6-dB attenuator is recommended at the signal generator outputs to prevent the generators from coupling to each other and resulting in signal generator IMD3 spurs.

- Set both the signal generator outputs to a power level and frequency spacing such that it would yield the desired output power (P<sub>OUT</sub>) at the device.

- 3. TI recommends that the output power level is within the linear operation range of the LMH9126 device. As a general rule, it is recommended to keep the total output power level approximately 6 dB to 8 dB lower than the 1-dB compression point. For example, if the output 1-dB compression point of the device is 16 dBm, then set the signal generators such that each of the fundamental output power results in 2 dBm per tone.

- 4. For the OIP3 test, the two tones can be spaced at 10 MHz apart from each other and on either side of center frequency.

- 5. TI recommends setting the spectrum analyzer attenuation setting from 20 dB to 26 dB based on its sweet spot and the incoming input power level.

- 6. Keep spectrum analyzer RBW and VBW settings identical for main tone and IM3 products.

- 7. For output IP3 calculation, take into account combined losses at the desired frequency band between the LMH9126 device output to the spectrum analyzer input. The combined power losses include loss due to PCB output trace, RF coax cable, and attenuator pad used for external matching. The calculated OIP3 is given by the following equation:

Output IP3 =  $(P_{IN_SA} - IMD3) / 2 + P_{IN_SA} + P_{LOSS}$

where,

- P<sub>IN\_SA</sub> = Input power per tone into the spectrum analyzer

- P<sub>LOSS</sub> = Power loss from the device output to the spectrum analyzer input

- IMD3 = Higher power of the two inter-modulation distortion products recorded at either 2f1 f2 or 2f2 f1

- 8. Note that  $P_{IN SA} + P_{LOSS} = P_{OUT}$  is the amplifier output power per tone.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated