## P89V52X2

# 8-bit 80C51 low power 8 kB flash microcontroller with 256 B RAM, 192 B data EEPROM

Rev. 03 — 4 May 2009

**Product data sheet**

### 1. General description

The P89V52X2 is an 80C51 microcontroller with 8 kB flash, 256 B of data RAM, and 192 B of data EEPROM. This device is designed to be a drop in and software compatible replacement for the P87C52, P87C52X2, P89C52, and P89C52X2 devices.

### 2. Features

### 2.1 Principal features

- 0 MHz to 40 MHz operating frequency in 12× mode, 20 MHz in 6× mode

- 8 kB of on-chip flash user code memory

- 256 B of RAM

- Enhanced UART

- Three 16-bit timers/counters

- Four 8-bit I/O ports

- Supports 12-clock (default) or 6-clock mode selection via software or In-Circuit Programming (ICP)

- DIP40, PLCC44, and LQFP44 packages

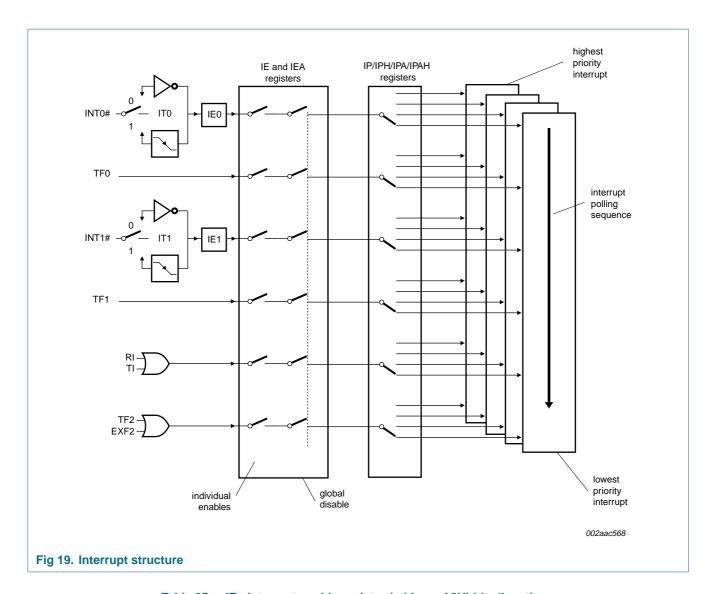

- Six interrupt sources with four priority levels

- Second DPTR register

### 2.2 Additional features

- Very low power

- Low EMI mode (ALE inhibit)

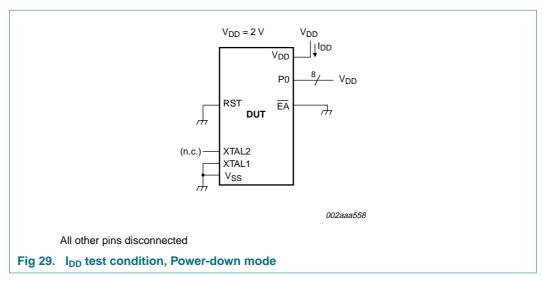

- Power-down mode with external interrupt wake-up

- Idle mode

- Extended temperature range

- Three security bits

- Programmable clock-out pin

### 80C51 with 256 B RAM, 192 B data EEPROM

### 3. Ordering information

Table 1. Ordering information

| Type number | Package | Version                                                                                    |          |

|-------------|---------|--------------------------------------------------------------------------------------------|----------|

|             | Name    | Description                                                                                |          |

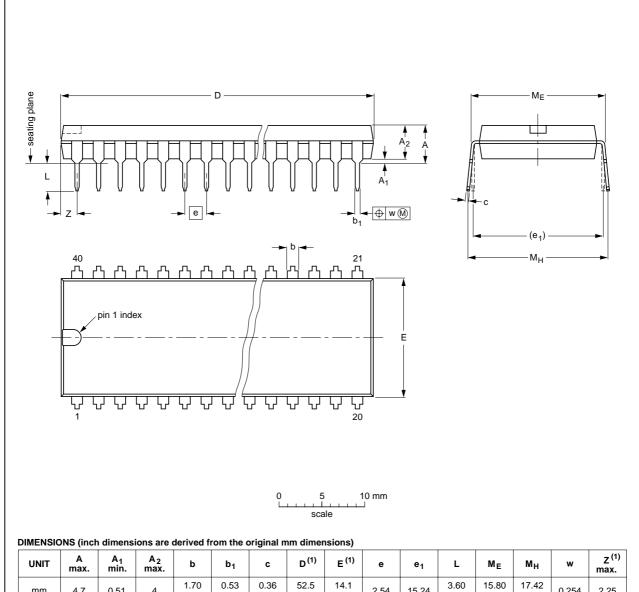

| P89V52X2FN  | DIP40   | plastic dual in-line package; 40 leads (600 mil)                                           | SOT129-1 |

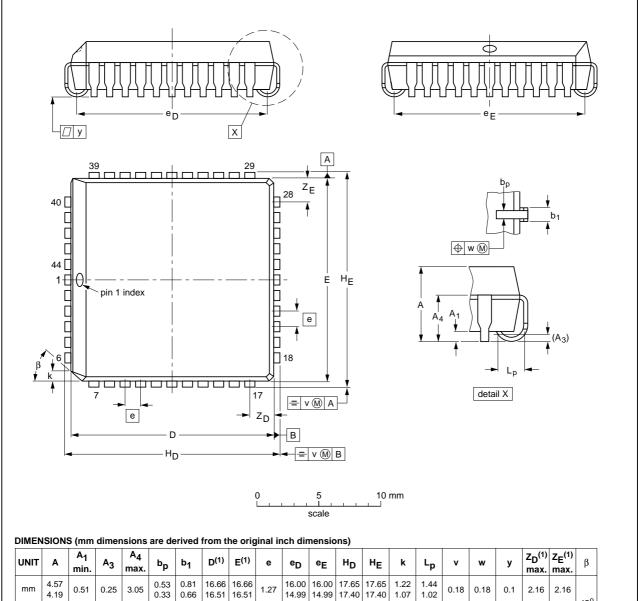

| P89V52X2FBD | LQFP44  | plastic low profile quad flat package; 44 leads; body $10 \times 10 \times 1.4 \text{ mm}$ | SOT389-1 |

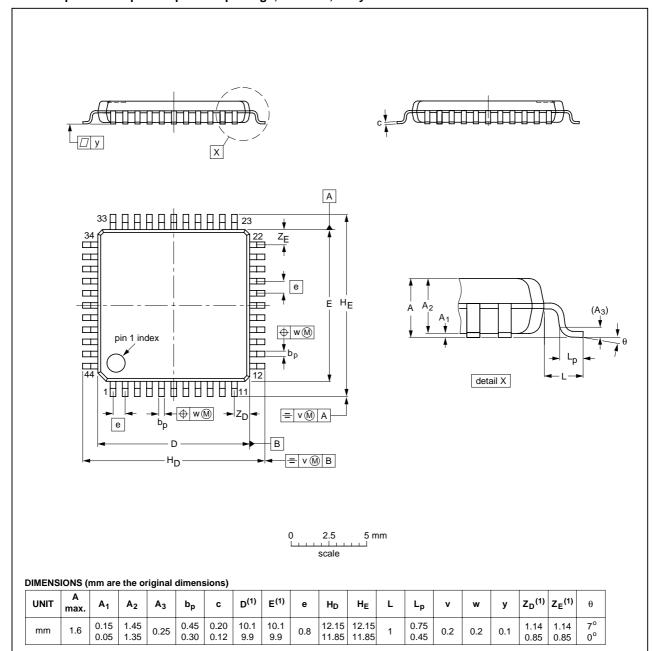

| P89V52X2FA  | PLCC44  | plastic leaded chip carrier; 44 leads                                                      | SOT187-2 |

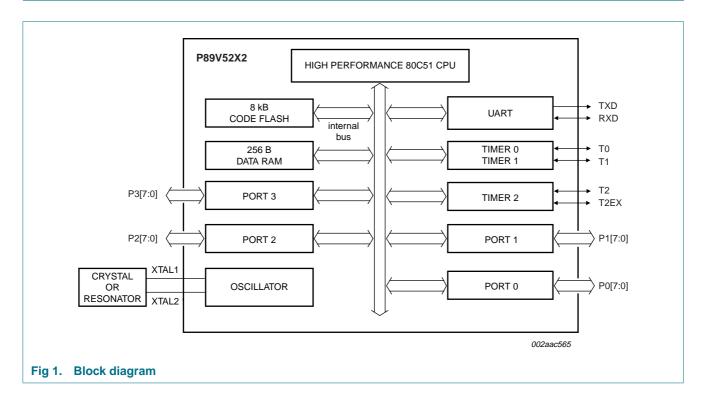

### 4. Block diagram

80C51 with 256 B RAM, 192 B data EEPROM

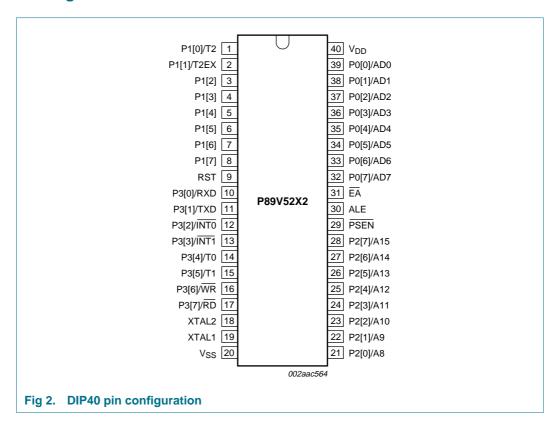

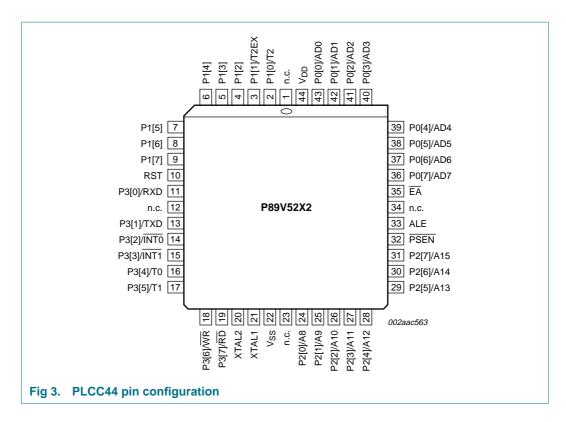

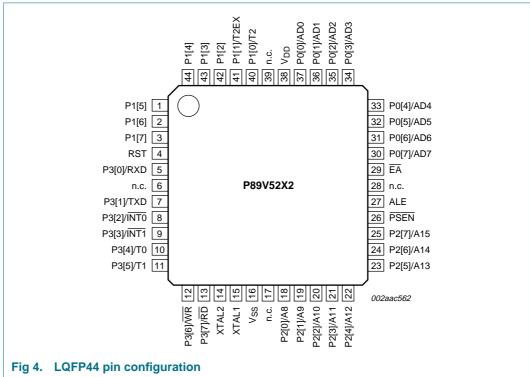

### 5. Pinning information

### 5.1 Pinning

### 80C51 with 256 B RAM, 192 B data EEPROM

### 80C51 with 256 B RAM, 192 B data EEPROM

### 5.2 Pin description

Table 2. Pin description

| Symbol         | Pin   |        |        | Туре                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|-------|--------|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | DIP40 | LQFP44 | PLCC44 |                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P0[0] to P0[7] |       |        |        | I/O                             | Port 0: Port 0 is an 8-bit open-drain bidirectional I/O port. Port 0 pins that have '1's written to them float, and in this state can be used as high-impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external code and data memory. In this application, it uses strong internal pull-ups when transitioning to '1's. External pull-ups are required as a general purpose I/O port. |

| P0[0]/AD0      | 39    | 37     | 43     | I/O                             | <b>P0[0]</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD0 — Address/data bit 0.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[1]/AD1      | 38    | 36     | 42     | I/O                             | <b>P0[1]</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD1 — Address/data bit 1.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[2]/AD2      | 37    | 35     | 41     | I/O                             | <b>P0[2]</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD2 — Address/data bit 2.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[3]/AD3      | 36    | 34     | 40     | I/O                             | <b>P0[3]</b> — Port 0 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD3 — Address/data bit 3.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[4]/AD4      | 35    | 33     | 39     | I/O                             | <b>P0[4]</b> — Port 0 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD4 — Address/data bit 4.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[5]/AD5      | 34    | 32     | 38     | I/O                             | <b>P0[5]</b> — Port 0 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD5 — Address/data bit 5.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[6]/AD6      | 33    | 31     | 37     | I/O                             | <b>P0[6]</b> — Port 0 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD6 — Address/data bit 6.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P0[7]/AD7      | 32    | 30     | 36     | I/O                             | <b>P0[7]</b> — Port 0 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I/O                             | AD7 — Address/data bit 7.                                                                                                                                                                                                                                                                                                                                                                                                               |

| P1[0] to P1[7] |       |        |        | I/O with<br>internal<br>pull-up | <b>Port 1:</b> Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. The Port 1 pins are pulled HIGH by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 1 pins that are externally pulled LOW will source current (I <sub>IL</sub> ) because of the internal pull-ups. P1[5], P1[6], P1[7] have high current drive of 16 mA.                                   |

| P1[0]/T2       | 1     | 40     | 2      | I/O                             | <b>P1[0]</b> — Port 1 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I                               | <b>T2</b> — External count input to Timer/Counter 2 or Clock-out from Timer/Counter 2                                                                                                                                                                                                                                                                                                                                                   |

| P1[1]/T2EX     | 2     | 41     | 3      | I/O                             | <b>P1[1]</b> — Port 1 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |       |        |        | I                               | <b>T2EX</b> : Timer/Counter 2 capture/reload trigger and direction control                                                                                                                                                                                                                                                                                                                                                              |

| P1[2]          | 3     | 42     | 4      | I/O                             | <b>P1[2]</b> — Port 1 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                            |

| P1[3]          | 4     | 43     | 5      | I/O                             | <b>P1[3]</b> — Port 1 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                            |

| P1[4]          | 5     | 44     | 6      | I/O                             | <b>P1[4]</b> — Port 1 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                            |

| P1[5]          | 6     | 1      | 7      | I/O                             | <b>P1[5]</b> — Port 1 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                            |

| P1[6]          | 7     | 2      | 8      | I/O                             | <b>P1[6]</b> — Port 1 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                            |

### 80C51 with 256 B RAM, 192 B data EEPROM

Table 2.

Pin description ...continued

| Symbol         | Pin   |        |        | Туре                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|-------|--------|--------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -              | DIP40 | LQFP44 | PLCC44 |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1[7]          | 8     | 3      | 9      | I/O                                | <b>P1[7]</b> — Port 1 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2[0] to P2[7] |       |        |        | I/O with<br>internal<br>pull-up    | <b>Port 2</b> : Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins are pulled HIGH by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 2 pins that are externally pulled LOW will source current (I <sub>IL</sub> ) because of the internal pull-ups. Port 2 sends the high-order address byte during fetches from external program memory and during accesses to external Data Memory that use 16-bit address (MOVX@DPTR). In this application, it uses strong internal pull-ups when transitioning to '1's. |

| P2[0]/A8       | 21    | 18     | 24     | I/O                                | <b>P2[0]</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A8 — Address bit 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P2[1]/A9       | 22    | 19     | 25     | I/O                                | <b>P2[1]</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | О                                  | A9 — Address bit 9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| P2[2]/A10      | 23    | 20     | 26     | I/O                                | <b>P2[2]</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A10 — Address bit 10.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P2[3]/A11      | 24    | 21     | 27     | I/O                                | <b>P2[3]</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A11 — Address bit 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P2[4]/A12      | 25    | 22     | 28     | I/O                                | <b>P2[4]</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A12 — Address bit 12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P2[5]/A13      | 26    | 23     | 29     | I/O                                | <b>P2[5]</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A13 — Address bit 13.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P2[6]/A14      | 27    | 24     | 30     | I/O                                | <b>P2[6]</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A14 — Address bit 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P2[7]/A15      | 28    | 25     | 31     | I/O                                | <b>P2[7]</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | A15 — Address bit 15.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P3[0] to P3[7] |       |        |        | I/O<br>with<br>internal<br>pull-up | <b>Port 3</b> : Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins are pulled HIGH by the internal pull-ups when '1's are written to them and can be used as inputs in this state. As inputs, Port 3 pins that are externally pulled LOW will source current (I <sub>IL</sub> ) because of the internal pull-ups.                                                                                                                                                                                                                                                         |

| P3[0]/RXD      | 10    | 5      | 11     | I                                  | <b>P3[0]</b> — Port 3 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | I                                  | RXD — Serial input port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3[1]/TXD      | 11    | 7      | 13     | 0                                  | <b>P3[1]</b> — Port 3 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | 0                                  | TXD — Serial output port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P3[2]/INT0     | 12    | 8      | 14     | I                                  | <b>P3[2]</b> — Port 3 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | I                                  | INTO — External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| P3[3]/INT1     | 13    | 9      | 15     | I                                  | <b>P3[3]</b> — Port 3 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | I                                  | INT1 — External interrupt 1 input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P3[4]/T0       | 14    | 10     | 16     | I/O                                | <b>P3[4]</b> — Port 3 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                |       |        |        | I                                  | T0 — External count input to Timer/Counter 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### 80C51 with 256 B RAM, 192 B data EEPROM

Table 2.

Pin description ...continued

| Symbol   | Pin   |        |        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------|--------|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | DIP40 | LQFP44 | PLCC44 |      |                                                                                                                                                                                                                                                                                                                                                                                      |

| P3[5]/T1 | 15    | 11     | 17     | I/O  | <b>P3[5]</b> — Port 3 bit 5.                                                                                                                                                                                                                                                                                                                                                         |

|          |       |        |        | I    | T1 — External count input to Timer/Counter 1                                                                                                                                                                                                                                                                                                                                         |

| P3[6]/WR | 16    | 12     | 18     | 0    | <b>P3[6]</b> — Port 3 bit 6.                                                                                                                                                                                                                                                                                                                                                         |

|          |       |        |        | 0    | WR — External data memory write strobe                                                                                                                                                                                                                                                                                                                                               |

| P3[7]/RD | 17    | 13     | 19     | 0    | <b>P3[7]</b> — Port 3 bit 7.                                                                                                                                                                                                                                                                                                                                                         |

|          |       |        |        | 0    | RD — External data memory read strobe.                                                                                                                                                                                                                                                                                                                                               |

| PSEN     | 29    | 26     | 32     | I/O  | Program Store Enable: PSEN is the read strobe for external program memory. When the device is executing from internal program memory, PSEN is inactive (HIGH). When the device is executing code from external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory.                  |

| RST      | 9     | 4      | 10     | I    | <b>Reset</b> : While the oscillator is running, a HIGH logic state on this pin for two machine cycles will reset the device.                                                                                                                                                                                                                                                         |

| EA       | 31    | 29     | 35     | I    | <b>External Access Enable</b> : $\overline{EA}$ must be connected to $V_{SS}$ in order to enable the device to fetch code from the external program memory. $\overline{EA}$ must be strapped to $V_{DD}$ for internal program execution.                                                                                                                                             |

| ALE      | 30    | 27     | 33     | I/O  | Address Latch Enable: ALE is the output signal for latching the low byte of the address during an access to external memory. Normally the ALE[1] is emitted at a constant rate of 1/6 the crystal frequency[2] and can be used for external timing and clocking. One ALE pulse is skipped during each access to external data memory. However, if AO is set to '1', ALE is disabled. |

| XTAL1    | 19    | 15     | 21     | I    | <b>Crystal 1</b> : Input to the inverting oscillator amplifier and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                   |

| XTAL2    | 18    | 14     | 20     | 0    | Crystal 2: Output from the inverting oscillator amplifier.                                                                                                                                                                                                                                                                                                                           |

| $V_{DD}$ | 40    | 38     | 44     | I    | Power supply                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{SS}$ | 20    | 16     | 22     | I    | Ground                                                                                                                                                                                                                                                                                                                                                                               |

<sup>[1]</sup> ALE loading issue: When ALE pin experiences higher loading (> 30 pF) during the reset, the microcontroller may accidentally enter into modes other than normal working mode. The solution is to add a pull-up resistor of 3 k $\Omega$  to 50 k $\Omega$  to V<sub>DD</sub>, e.g., for ALE pin.

<sup>[2]</sup> For 6-clock mode, ALE is emitted at  $\frac{1}{3}$  of crystal frequency.

### 80C51 with 256 B RAM, 192 B data EEPROM

### 6. Functional description

### 6.1 Special function registers

Remark: SFR accesses are restricted in the following ways:

- User must **not** attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0' or '1' can **only** be written and read as follows:

- '-' Unless otherwise specified, must be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' must be written with '0', and will return a '0' when read.

- '1' must be written with '1', and will return a '1' when read.

NXP

Semiconductors

| Name   | Description                   | SFR         |                 |                 |         |         |            |         |           |         |

|--------|-------------------------------|-------------|-----------------|-----------------|---------|---------|------------|---------|-----------|---------|

|        |                               | addr.       | MSB             |                 |         |         |            |         |           | LSB     |

|        | '                             | Bit address | <b>E</b> 7      | <b>E</b> 6      | E5      | E4      | <b>E</b> 3 | E2      | E1        | E0      |

| ACC*   | Accumulator                   | E0H         | -               | -               | -       | -       | -          | -       | -         | -       |

| AUXR   | Auxiliary function register   | 8EH         | -               | -               | -       | -       | -          | -       | -         | AO      |

| AUXR1  | Auxiliary function register 1 | A2H         | -               | -               | -       |         | GF2        | 0       | -         | DPS     |

|        |                               | Bit address | F7              | F6              | F5      | F4      | F3         | F2      | F1        | F0      |

| B*     | B register                    | F0H         | -               | -               | -       | -       | -          | -       | -         | -       |

| CKCON  | B register                    | 8FH         | -               | -               | -       | -       | -          | -       | -         | X2      |

| DPTR   | Data Pointer (2 B)            |             |                 |                 |         |         |            |         |           |         |

| DPH    | Data Pointer HIGH             | 83H         | -               | -               | -       | -       | -          | -       | -         | -       |

| DPL    | Data Pointer LOW              | 82H         | -               | -               | -       | -       | -          | -       | -         | -       |

| FMCON  | Flash control register (R)    | F4H         | BUSY            | WE              | -       | DAP     | -          | -       | SV        | ERR     |

|        | Flash control register (W)    |             | FMCMD.7         | FMCMD.6         | FMCMD.5 | FMCMD.4 | FMCMD.3    | FMCMD.2 | FMCMD.1   | FMCMD.0 |

| FMDATA | Flash data register           | F5H         | -               | -               | -       | -       | -          | -       | -         | -       |

| FMADRH | Flash memory address HIGH     | F6H         | -               | -               | -       | -       | -          | -       | -         | -       |

| FMADRL | Flash memory address LOW      | F7H         | -               | -               | -       | -       | -          | -       | -         | -       |

|        |                               | Bit address | AF              | AE              | AD      | AC      | AB         | AA      | A9        | A8      |

| IE*    | Interrupt Enable 0            | A8H         | EA              | -               | ET2     | ES      | ET1        | EX1     | ET0       | EX0     |

|        |                               | Bit address | BF              | BE              | BD      | ВС      | BB         | ВА      | B9        | B8      |

| IP*    | Interrupt Priority 0          | B8H         | -               | -               | PT2     | PS      | PT1        | PX1     | PT0       | PX0     |

| IPH    | Interrupt Priority 0 HIGH     | В7Н         | -               | -               | PT2H    | PS0H    | PT1H       | PX1H    | PT0H      | PX0H    |

|        |                               | Bit address | 87              | 86              | 85      | 84      | 83         | 82      | 81        | 80      |

| P0*    | Port 0                        | 80H         | AD7             | AD6             | AD5     | AD4     | AD3        | AD2     | AD1       | AD0     |

|        |                               | Bit address | 97              | 96              | 95      | 94      | 93         | 92      | 91        | 90      |

| P1*    | Port 1                        | 90H         | -               | -               | -       | -       | -          | -       | T2EX      | T2      |

|        |                               | Bit address | A7              | A6              | A5      | A4      | А3         | A2      | <b>A1</b> | Α0      |

| P2*    | Port 2                        | A0H         | AD15            | AD14            | AD13    | AD12    | AD11       | AD10    | AD9       | AD8     |

|        |                               | Bit address | B7              | <b>B6</b>       | B5      | B4      | В3         | B2      | B1        | В0      |

| P3*    | Port 3                        | ВОН         | $\overline{RD}$ | $\overline{WR}$ | T1      | T0      | ĪNT1       | ĪNT0    | TXD       | RXD     |

| PCON   | Power Control Register        | 87H         | SMOD1           | SMOD0           | -       | POF     | GF1        | GF0     | PD        | IDL     |

NXP

Semiconductors

| Name   | Description                     | SFR         |        |       | Ві   | t functions | and addresse | es    |      |        |

|--------|---------------------------------|-------------|--------|-------|------|-------------|--------------|-------|------|--------|

|        |                                 | addr.       | MSB    |       |      |             |              |       |      | LSB    |

|        | '                               | Bit address | D7     | D6    | D5   | D4          | D3           | D2    | D1   | D0     |

| PSW*   | Program Status Word             | D0H         | CY     | AC    | F0   | RS1         | RS0          | OV    | -    | Р      |

| RCAP2H | Timer2 Capture HIGH             | СВН         | -      | -     | -    | -           | -            | -     | -    | -      |

| RCAP2L | Timer2 Capture LOW              | CAH         | -      | -     | -    | -           | -            | -     | -    | -      |

|        |                                 | Bit address | 9F     | 9E    | 9D   | 9C          | 9B           | 9A    | 99   | 98     |

| SCON*  | Serial Port Control             | 98H         | SM0/FE | SM1   | SM2  | REN         | TB8          | RB8   | TI   | RI     |

| SBUF   | Serial Port Data Buffer Registe | er 99H      | -      | -     | -    | -           | -            | -     | -    | -      |

| SADDR  | Serial Port Address Register    | A9H         | -      | -     | -    | -           | -            | -     | -    | -      |

| SADEN  | Serial Port Address Enable      | В9Н         | -      | -     | -    | -           | -            | -     | -    | -      |

| SP     | Stack Pointer                   | 81H         | -      | -     | -    | -           | -            | -     | -    | -      |

|        |                                 | Bit address | 8F     | 8E    | 8D   | 8C          | 8B           | 8A    | 89   | 88     |

| TCON*  | Timer Control Register          | 88H         | TF1    | TR1   | TF0  | TR0         | IE1          | IT1   | IE0  | IT0    |

|        |                                 | Bit address | CF     | CE    | CD   | CC          | СВ           | CA    | C9   | C8     |

| T2CON* | Timer2 Control Register         | C8H         | TF2    | EXF2  | RCLK | TCLK        | EXEN2        | TR2   | C/T2 | CP/RL2 |

| T2MOD  | Timer2 mode Control             | C9H         | -      | -     | -    | -           | -            | -     | T2OE | DCEN   |

| TH0    | Timer 0 HIGH                    | 8CH         | -      | -     | -    | -           | -            | -     | -    | -      |

| TH1    | Timer 1 HIGH                    | 8DH         | -      | -     | -    | -           | -            | -     | -    | -      |

| TH2    | Timer 2 HIGH                    | CDH         | -      | -     | -    | -           | -            | -     | -    | -      |

| TL0    | Timer 0 LOW                     | 8AH         | -      | -     | -    | -           | -            | -     | -    | -      |

| TL1    | Timer 1 LOW                     | 8BH         | -      | -     | -    | -           | -            | -     | -    | -      |

| TL2    | Timer 2 LOW                     | CCH         | -      | -     | -    | -           | -            | -     | -    | -      |

| TMOD   | Timer 0 and 1 mode              | 89H         | T1GATE | T1C/T | T1M1 | T1M0        | T0GATE       | T0C/T | T0M1 | T0M0   |

<sup>[1]</sup> Unimplemented bits in SFRs (labeled '-') are 'X's (unknown) at all times. Unless otherwise specified, '1's should not be written to these bits since they may be used for other purposes in future derivatives. The reset values shown for these bits are '0's although they are unknown when read.

### 80C51 with 256 B RAM, 192 B data EEPROM

### 6.2 Memory organization

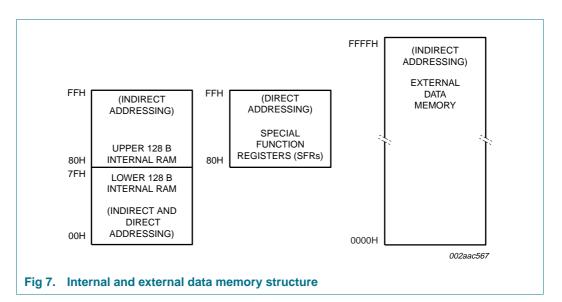

The various P89V52X2 memory spaces are as follows:

#### DATA

128 B of internal data memory space (00H:7FH) accessed via direct or indirect addressing, using instructions other than MOVX and MOVC. All or part of the Stack may be in this area.

### IDATA

Indirect Data. 256 B of internal data memory space (00H:FFH) accessed via indirect addressing using instructions other than MOVX and MOVC. All or part of the Stack may be in this area. This area includes the DATA area and the 128 B immediately above it.

### • SFR

Special Function Registers. Selected CPU registers and peripheral control and status registers, accessible only via direct addressing.

#### CODE

64 kB of Code memory space, accessed as part of program execution and via the MOVC instruction. The P89V52X2 has 8 kB of on-chip Code memory.

### 6.3 System clock and clock options

### 6.3.1 Clock input options and recommended capacitor values for the oscillator

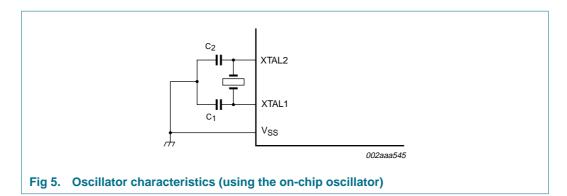

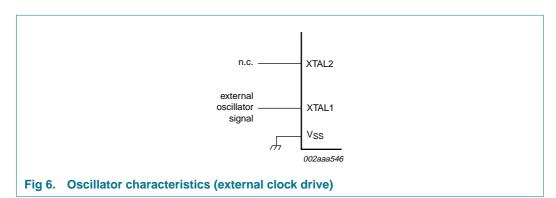

Shown in Figure 5 and Figure 6 are the input and output of an internal inverting amplifier (XTAL1, XTAL2), which can be configured for use as an on-chip oscillator.

When driving the device from an external clock source, XTAL2 should be left disconnected and XTAL1 should be driven. Power consumption can be further reduced by programming the EXTCLK bit (UCFG.0).

At start-up, the external oscillator may encounter a higher capacitive load at XTAL1 due to interaction between the amplifier and its feedback capacitance. However, the capacitance will not exceed 15 pF once the external signal meets the  $V_{IL}$  and  $V_{IH}$  specifications.

Resonator manufacturer, supply voltage, and other factors may cause circuit performance to differ from one application to another.  $C_1$  and  $C_2$  should be adjusted appropriately for each design. Table 4 shows the typical values for  $C_1$  and  $C_2$  vs. resonator type for various frequencies.

Table 4. Recommended values for C<sub>1</sub> and C<sub>2</sub> by crystal type

| Resonator | $C_1 = C_2$    |

|-----------|----------------|

| Quartz    | 20 pF to 30 pF |

| Ceramic   | 40 pF to 50 pF |

### 80C51 with 256 B RAM, 192 B data EEPROM

### 6.3.2 Clock control register (CKCON)

By default, the device runs at twelve clocks per machine cycle. The device may be run in 6 clock per machine cycle mode by programming of either a non-volatile bit (FX2) or an SFR bit (Table 5 "Clock modes"). If the FX2 non-volatile bit is programmed the device will run in 6-clock mode and the X2 SFR bit has no effect. If the FX2 bit is erased, then the clock mode is controlled by the X2 SFR bit.

Table 5. Clock modes

| FX2 clock mode bit (UCFG.1) | X2 bit (CLKCON.0) | CPU clock mode          |

|-----------------------------|-------------------|-------------------------|

| erased                      | 0                 | 12-clock mode (default) |

| erased                      | 1                 | 6-clock mode            |

| programmed                  | Х                 | 6-clock mode            |

### 6.4 ALE control

Table 6. AUXR - Auxiliary register (address 8EH) bit allocation

Not bit addressable; Reset value 00H

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|--------|---|---|---|---|---|---|---|----|

| Symbol | - | - | - | - | - | - | - | AO |

P89V52X2\_3 © NXP B.V. 2009. All rights reserved.

### 80C51 with 256 B RAM, 192 B data EEPROM

| Table 7. AUXR - Auxiliary register (address 8EH) bit descrip |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| Bit    | Symbol | Description                                                                                                                                                                             |

|--------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 1 | -      | Reserved for future use. Should be set to '0' by user programs.                                                                                                                         |

| 0      | AO     | ALE off: disables/enables ALE. AO = 0 results in ALE emitted at a constant rate of $\frac{1}{2}$ the oscillator frequency. In case of AO = 1, ALE is active only during a MOVX or MOVC. |

### 6.5 Dual data pointers

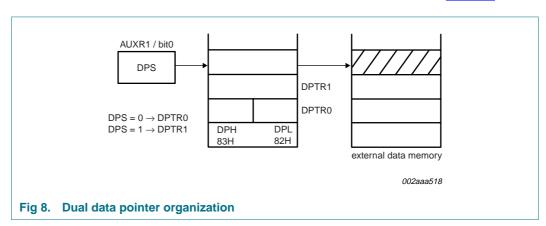

The device has two 16-bit data pointers. The DPTR Select (DPS) bit in AUXR1 determines which of the two data pointers is accessed. When DPS = 0, DPTR0 is selected; when DPS = 1, DPTR1 is selected. Quickly switching between the two data pointers can be accomplished by a single INC instruction on AUXR1 (see Figure 8).

Table 8. AUXR1 - Auxiliary register 1 (address A2H) bit allocation Not bit addressable; Reset value 00H

| Bit    | 7 | 6 | 5 | 4 | 3   | 2 | 1 | 0   |

|--------|---|---|---|---|-----|---|---|-----|

| Symbol | - | - | - | - | GF2 | 0 | - | DPS |

P89V52X2\_3 © NXP B.V. 2009. All rights reserved.

### 80C51 with 256 B RAM, 192 B data EEPROM

| Table 9. | AUAKT - Aua | AUXIT - Auxiliary register 1 (address Azn) bit description                                                                                     |  |  |  |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit      | Symbol      | Description                                                                                                                                    |  |  |  |

| 7 to 4   | -           | Reserved for future use. Should be set to '0' by user programs.                                                                                |  |  |  |

| 3        | GF2         | General purpose user-defined flag.                                                                                                             |  |  |  |

| 2        | 0           | This bit contains a hard-wired '0'. Allows toggling of the DPS bit by incrementing AUXR1, without interfering with other bits in the register. |  |  |  |

| 1        | -           | Reserved for future use. Should be set to '0' by user programs.                                                                                |  |  |  |

| 0        | DPS         | Data pointer select. Chooses one of two Data Pointers for use by the program. See text for details.                                            |  |  |  |

Table 9. AUXR1 - Auxiliary register 1 (address A2H) bit description

### 6.6 Reset

At initial power-up, the port pins will be in a random state until the oscillator has started and the internal reset algorithm has weakly pulled all pins HIGH. Powering up the device without a valid reset could cause the device to start executing instructions from an indeterminate location. Such undefined states may inadvertently corrupt the code in the flash. A system reset will not affect the on-chip RAM while the device is running, however, the contents of the on-chip RAM during power-up are indeterminate.

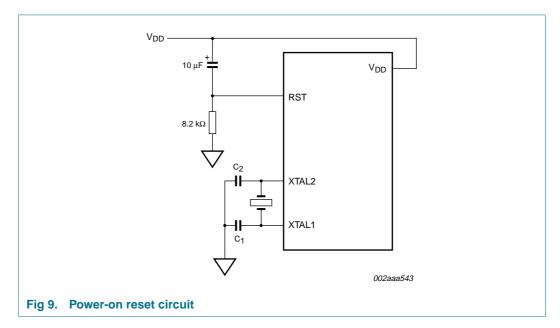

When power is applied to the device, the RST pin must be held HIGH long enough for the oscillator to start-up (usually several milliseconds for a low frequency crystal), in addition to two machine cycles for a valid power-on reset. An example of a method to extend the RST signal is to implement a RC circuit by connecting the RST pin to  $V_{DD}$  through a 10  $\mu F$  capacitor and to  $V_{SS}$  through an 8.2 k $\Omega$  resistor as shown in Figure 9.

During initial power the POF flag in the PCON register is set to indicate an initial power-up condition. The POF flag will remain active until cleared by software.

Following a reset condition, under normal conditions, the device will start executing code from address 0000H in the user's code memory. However if the requirements are met for ICP entry, the device will enter ICP mode.

### 80C51 with 256 B RAM, 192 B data EEPROM

### 6.7 Flash memory

### 6.7.1 Flash organization

The P89V52X2 program memory consists of an 8 kB block of user code. The flash can be read or written in bytes but may only be erased as an entire block. A chip erase function will erase the entire user code memory and its associated security bits. This flash memory can be erased or programmed using a programmer tool that supports ICP.

### 6.7.2 Features

- Flash internal program memory.

- Programming and erase over the full operating voltage range.

- Programming with industry-standard commercial programmers.

- 10000 typical erase/program cycles for each byte.

- 100 year minimum data retention.

### 6.8 Timers/counters 0 and 1

The two 16-bit Timer/Counter registers: Timer 0 and Timer 1 can be configured to operate either as timers or event counters (see <u>Table 10</u> and <u>Table 11</u>).

In the 'Timer' function, the register is incremented every machine cycle. Thus, one can think of it as counting machine cycles. Since a machine cycle consists of six oscillator periods, the count rate is  $\frac{1}{6}$  of the oscillator frequency.

In the 'Counter' function, the register is incremented in response to a 1-to-0 transition at its corresponding external input pin, T0 or T1. In this function, the external input is sampled once every machine cycle.

When the samples show a high in one cycle and a low in the next cycle, the count is incremented. The new count value appears in the register in the machine cycle following the one in which the transition was detected. Since it takes two machine cycles (12 oscillator periods) for 1-to-0 transition to be recognized, the maximum count rate is  $\frac{1}{12}$  of the oscillator frequency. There are no restrictions on the duty cycle of the external input signal, but to ensure that a given level is sampled at least once before it changes, it should be held for at least one full machine cycle. In addition to the 'Timer' or 'Counter' selection, Timer 0 and Timer 1 have four operating modes from which to select.

The 'Timer' or 'Counter' function is selected by control bits C/T in the Special Function Register TMOD. These two Timer/Counters have four operating modes, which are selected by bit-pairs (M1, M0) in TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text.

Table 10. TMOD - Timer/Counter mode control register (address 89H) bit allocation Not bit addressable; Reset value: 0000 0000B; Reset source(s): any source

| Bit    | 7      | 6     | 5    | 4    | 3      | 2     | 1    | 0    |

|--------|--------|-------|------|------|--------|-------|------|------|

| Symbol | T1GATE | T1C/T | T1M1 | T1M0 | T0GATE | T0C/T | T0M1 | T0M0 |

P89V52X2\_3 © NXP B.V. 2009. All rights reserved.

### 80C51 with 256 B RAM, 192 B data EEPROM

Table 11. TMOD - Timer/Counter mode control register (address 89H) bit description

| Bit | Symbol | Description                                                                                                                                                                                      |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | T1GATE | Gating control for Timer 1. When set, Timer/Counter is enabled only while the INT1 pin is HIGH and the TR1 control pin is set. When cleared, Timer 1 is enabled when the TR1 control bit is set. |

| 6   | T1C/T  | Timer or Counter select for Timer 1. Cleared for Timer operation (input from CCLK). Set for Counter operation (input from T1 input pin).                                                         |

| 5   | T1M1   | Mode select for Timer 1.                                                                                                                                                                         |

| 4   | T1M0   |                                                                                                                                                                                                  |

| 3   | T0GATE | Gating control for Timer 0. When set, Timer/Counter is enabled only while the INTO pin is HIGH and the TRO control pin is set. When cleared, Timer 0 is enabled when the TRO control bit is set. |

| 2   | T0C/T  | Timer or Counter select for Timer 0. Cleared for Timer operation (input from CCLK). Set for Counter operation (input from T0 input pin).                                                         |

| 1   | T0M1   | Mode Select for Timer 0.                                                                                                                                                                         |

| 0   | T0M0   |                                                                                                                                                                                                  |

|     |        |                                                                                                                                                                                                  |

Table 12. TMOD - Timer/Counter mode control register (address 89H) M1/M0 operating mode

| M1 | МО | Operatir | ng mode                                                                                                                                                 |

|----|----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0        | 8048 timer 'TLx' serves as 5-bit prescaler                                                                                                              |

| 0  | 1  | 1        | 16-bit Timer/Counter 'THx' and 'TLx' are cascaded; there is no prescaler.                                                                               |

| 1  | 0  | 2        | 8-bit auto-reload Timer/Counter 'THx' holds a value which is to be reloaded into 'TLx' each time it overflows.                                          |

| 1  | 1  | 3        | (Timer 0) TL0 is an 8-bit Timer/Counter controlled by the standard Timer 0 control bits. TH0 is an 8-bit timer only controlled by Timer 1 control bits. |

| 1  | 1  | 3        | (Timer 1) Timer/Counter 1 stopped.                                                                                                                      |

Table 13. TCON - Timer/Counter control register (address 88H) bit allocation

Bit addressable; Reset value: 0000 0000B; Reset source(s): any reset

| Bit    | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| Symbol | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

Table 14. TCON - Timer/Counter control register (address 88H) bit description

| Bit | Symbol | Description                                                                                                                                                    |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1    | Timer 1 overflow flag. Set by hardware on Timer/Counter overflow. Cleared by hardware when the processor vectors to Timer 1 Interrupt routine, or by software. |

| 6   | TR1    | Timer 1 Run control bit. Set/cleared by software to turn Timer/Counter 1 on/off.                                                                               |

| 5   | TF0    | Timer 0 overflow flag. Set by hardware on Timer/Counter overflow. Cleared by hardware when the processor vectors to Timer 0 Interrupt routine, or by software. |

| 4   | TR0    | Timer 0 Run control bit. Set/cleared by software to turn Timer/Counter 0 on/off.                                                                               |

P89V52X2 **NXP Semiconductors**

### 80C51 with 256 B RAM, 192 B data EEPROM

| Table 14. | 1CON - Timer/Counter control register (address 88H) bit descriptioncontinued |                                                                                                                                                                   |  |  |  |

|-----------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Bit       | Symbol                                                                       | Description                                                                                                                                                       |  |  |  |

| 3         | IE1                                                                          | Interrupt 1 Edge flag. Set by hardware when external interrupt 1 edge/LOW-level is detected. Cleared by hardware when the interrupt is processed, or by software. |  |  |  |

| 2         | IT1                                                                          | Interrupt 1 Type control bit. Set/cleared by software to specify falling edge/LOW-level that triggers external interrupt 1.                                       |  |  |  |

| 1         | IE0                                                                          | Interrupt 0 Edge flag. Set by hardware when external interrupt 0 edge/LOW-level is detected. Cleared by hardware when the interrupt is processed, or by software. |  |  |  |

| 0         | IT0                                                                          | Interrupt 0 Type control bit. Set/cleared by software to specify falling edge/LOW-level that triggers external interrupt 0.                                       |  |  |  |

### 6.8.1 Mode 0

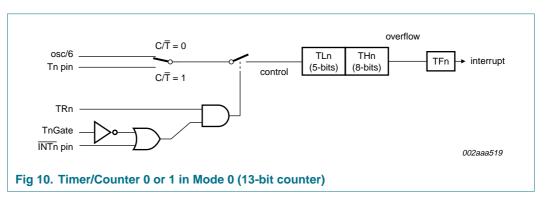

Putting either Timer into Mode 0 makes it look like an 8048 Timer, which is an 8-bit Counter with a fixed divide-by-32 prescaler. Figure 10 shows Mode 0 operation.

In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TFn. The count input is enabled to the Timer when TRn = 1 and either GATE = 0 or INTn = 1. (Setting GATE = 1 allows the Timer to be controlled by external input INTn, to facilitate pulse width measurements). TRn is a control bit in the Special Function Register TCON (Figure 8). The GATE bit is in the TMOD register.

The 13-bit register consists of all 8 bits of THn and the lower 5 bits of TLn. The upper 3 bits of TLn are indeterminate and should be ignored. Setting the run flag (TRn) does not clear the registers.

Mode 0 operation is the same for Timer 0 and Timer 1 (see Figure 10). There are two different GATE bits, one for Timer 1 (TMOD.7) and one for Timer 0 (TMOD.3).

### 6.8.2 Mode 1

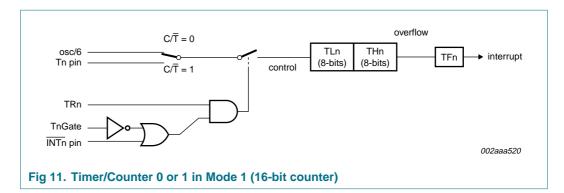

Mode 1 is the same as Mode 0, except that all 16 bits of the timer register (THn and TLn) are used. See Figure 11.

### 80C51 with 256 B RAM, 192 B data EEPROM

#### 6.8.3 Mode 2

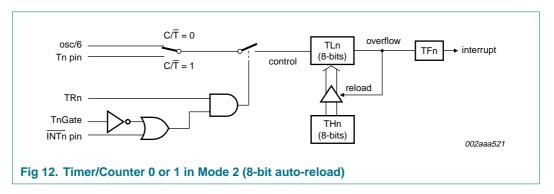

Mode 2 configures the Timer register as an 8-bit Counter (TLn) with automatic reload, as shown in <u>Figure 12</u>. Overflow from TLn not only sets TFn, but also reloads TLn with the contents of THn, which must be preset by software. The reload leaves THn unchanged. Mode 2 operation is the same for Timer 0 and Timer 1.

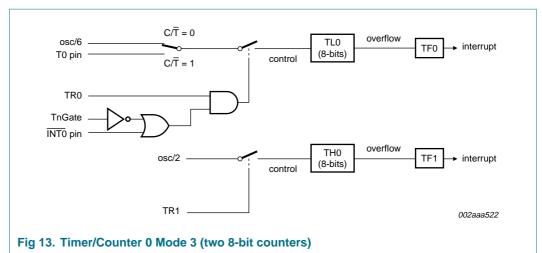

#### 6.8.4 Mode 3

When timer 1 is in Mode 3 it is stopped (holds its count). The effect is the same as setting TR1 = 0.

Timer 0 in Mode 3 establishes TL0 and TH0 as two separate 8-bit counters. The logic for Mode 3 and Timer 0 is shown in <u>Figure 13</u>. TL0 uses the Timer 0 control bits:  $TOC/\overline{T}$ , T0GATE, TR0,  $\overline{INT0}$ , and TF0. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the 'Timer 1' interrupt.

Mode 3 is provided for applications that require an extra 8-bit timer. With Timer 0 in Mode 3, the P89V52X2 can look like it has an additional Timer.

**Note:** When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it into and out of its own Mode 3. It can still be used by the serial port as a baud rate generator, or in any application not requiring an interrupt.

### 80C51 with 256 B RAM, 192 B data EEPROM

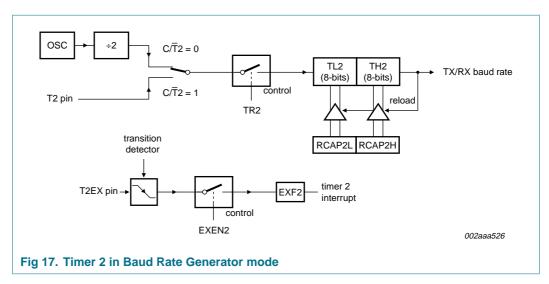

### 6.9 Timer 2

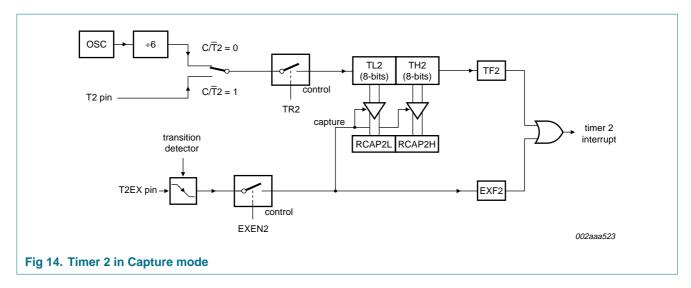

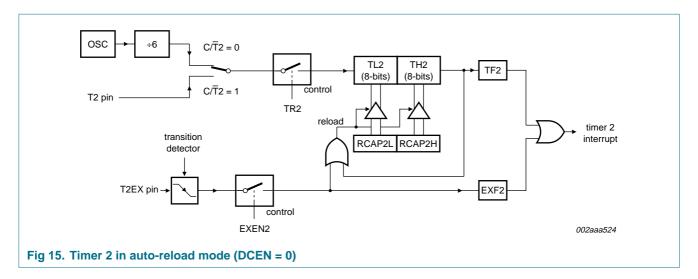

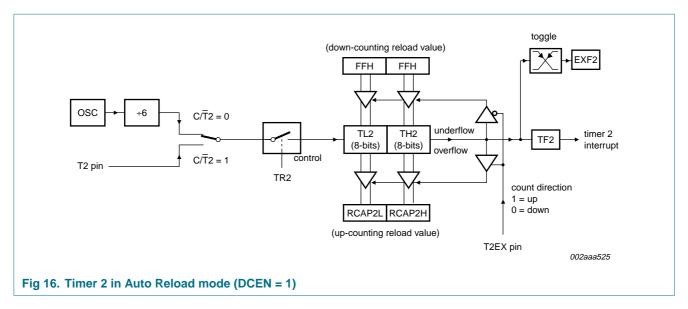

Timer 2 is a 16-bit Timer/Counter which can operate as either an event timer or an event counter, as selected by C/T2 in the special function register T2CON. Timer 2 has four operating modes: Capture, Auto-reload (up or down counting), Clock-out, and Baud Rate Generator which are selected according to <a href="Table 15">Table 15</a> using T2CON (<a href="Table 16">Table 16</a> and <a href="Table 15">Table 16</a>).

Table 15. Timer 2 operating mode

| RCLK+TCLK | CP/RL2 | TR2 | T2OE | Mode                   |

|-----------|--------|-----|------|------------------------|

| 0         | 0      | 1   | 0    | 16-bit auto reload     |

| 0         | 1      | 1   | 0    | 16-bit capture         |

| 0         | 0      | 1   | 1    | Programmable Clock-Out |

| 1         | X      | 1   | 0    | Baud rate generator    |

| X         | X      | 0   | X    | off                    |

Table 16. T2CON - Timer/Counter 2 control register (address C8H) bit allocation Bit addressable; Reset value: 00H

| Bit    | 7   | 6    | 5    | 4    | 3     | 2   | 1    | 0      |

|--------|-----|------|------|------|-------|-----|------|--------|

| Symbol | TF2 | EXF2 | RCLK | TCLK | EXEN2 | TR2 | C/T2 | CP/RL2 |

Table 17. T2CON - Timer/Counter 2 control register (address C8H) bit description