# 82750LH Technical Specifications

September 1992

Order Number: 241344-001

# 82750LH Technical Specifications

| CONTENTS                                       | PAGE    | <b>CONTENTS</b> PAG                    | ЭE   |

|------------------------------------------------|---------|----------------------------------------|------|

| 1.0 PIN DESCRIPTION                            | 1-123   | 2.7.8 POST Address Switch Register1-1  | 40   |

| 1.1 Pinout                                     |         | 2.7.9 Configuration Registers 1-1      |      |

| 1.2 Pin Cross Reference by Name and            |         | 2.7.9.1 I/O Port BASE Address          | 71   |

| Location                                       |         | Determination 1-1                      | 41   |

| 1.3 Pin Descriptions                           | 1-127   | 2.7.9.2 POS0 1-1                       | 42   |

| 2.0 INTERNAL ARCHITECTURE                      | 1-132   | 2.7.9.3 POS1 1-1                       | 142  |

| 2.1 DVI/Host Bus Interface                     | 1-132   | 2.7.9.4 POS2 1-1                       | 142  |

| 2.1.1 DVI Bus Overview                         | 1-132   | 2.7.9.5 POS3 1-1                       | 142  |

| 2.1.2 Expanded Memory Space                    |         | 2.7.9.6 POS4 1-1                       | 142  |

| Host/VRAM Connection                           | 1-132   | 2.7.9.7 POS5 1-1                       | 143  |

| 2.1.3 Host/VRAM FIFO Connection                | 1-132   | 2.7.10 VGA Test Registers 1-1          | 143  |

| 2.1.4 DVI Device Access                        |         | 3.0 HARDWARE INTERFACE 1-1             | 144  |

| 2.2 Power-On-Self-Test ROM                     |         | 3.1 MicroChannel Interface Operation   |      |

| 2.3 DVI Bus Request Arbitration                | 1-133   | and Timing 1-                          |      |

| 2.4 VGA DAC Support                            |         | 3.1.1 I/O Read1-                       |      |

| 2.5 General Purpose Inputs and                 |         | 3.1.2 I/O Write 1-                     |      |

| Outputs                                        | . 1-134 | 3.1.3 Memory Read 1-                   |      |

| 2.6 Interrupt Sharing Hardware                 |         | 3.1.4 Memory Write 1-                  | 144  |

| Support                                        |         | 3.2 ISA Interface Operation and        | 1 40 |

| 2.7 HIGA Registers                             |         | Timing1-                               |      |

| 2.7.1 Page Address Registers                   | . 1-135 | 3.2.1 I/O Read1-                       |      |

| 2.7.2 DVI Device Quick Access Register         | 1 125   | 3.2.2 I/O Write 1-                     |      |

| _                                              |         | 3.2.3 Memory Read 1-                   |      |

| 2.7.3 ROM 8K Select Register                   | . 1-135 | 3.2.4 Memory Write 1-                  | 148  |

| 2.7.4 FIFO Control, Address and Data Registers | . 1-135 | 3.3 VGA Support Operation and Timing1- | 152  |

| 2.7.4.1 32-Bit-Write FIFO                      | 1 105   | 3.3.1 VGA Read 1-                      | 152  |

| Registers2.7.4.2 16-Bit-Write FIFO             | . 1-135 | 3.3.2 VGA Write 1-                     | 152  |

| Registers                                      | . 1-137 | 3.4 DVI Bus Operation and Timing 1-    | 154  |

| 2.7.4.3 32-Bit-Read FIFO<br>Registers          |         | 3.4.1 DVI Device VRAM Access Cycle1-   | 154  |

| 2.7.4.4 16-Bit-Read FIFO                       |         | 3.4.2 Next-Fast VRAM Access            |      |

| Registers                                      | . 1-139 | Cycle1-                                |      |

| 2.7.5 General Status Register                  | . 1-139 | 3.4.3 DVI Device Access Cycle 1-       | 154  |

| 2.7.6 General Control Register                 | . 1-139 | 3.4.4 82750PB Register Access          | 154  |

| 2.7.7.1/O Port Switch Register                 | 1-140   | Cycle1-                                | 104  |

| CONTENTS                                  | PAGE    |

|-------------------------------------------|---------|

| 4.0 PROGRAMMING AND OPERATION             | . 1-159 |

| 4.1 Using the Host/VRAM FIFOs             | . 1-159 |

| 4.1.1 Using the Write FIFOs               | . 1-159 |

| 4.1.2 Using the Read FIFOs                | . 1-159 |

| 4.2 Programming the VRAM Addressing Modes | . 1-160 |

| 4.3 Using the Power-On-Self-Test ROM      | . 1-163 |

| 5.0 ELECTRICAL DATA                       | . 1-163 |

| 5.1 DC Characteristics                    | . 1-163 |

| CONTENTS                                | PAGE    |

|-----------------------------------------|---------|

| 5.2 AC Characteristics                  | . 1-166 |

| 5.2.1 MicroChannel Bus Interface Timing | . 1-166 |

| 5.2.2 ISA Bus Interface Timing          | . 1-171 |

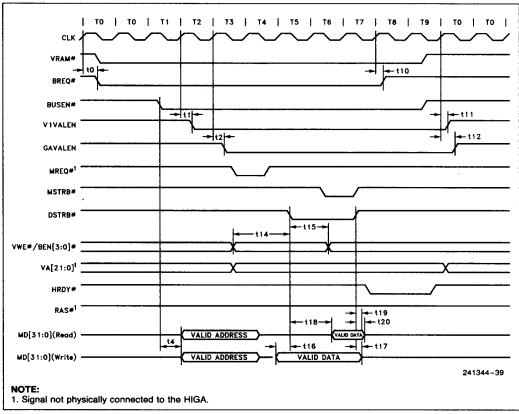

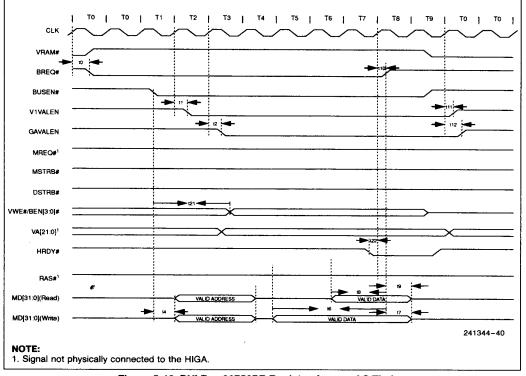

| 5.2.3 DVI Bus Interface Timing          | . 1-177 |

| 6.0 MECHANICAL DATA                     | . 1-182 |

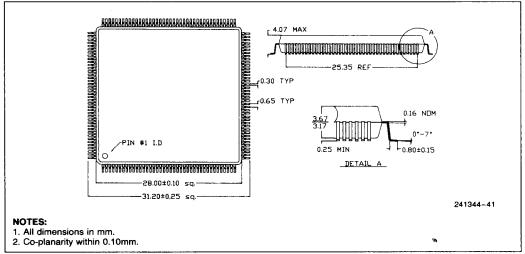

| 6.1 Packaging Outlines and Dimensions   | . 1-182 |

| 6.2 Package Thermal Specifications      | . 1-182 |

|                                         |         |

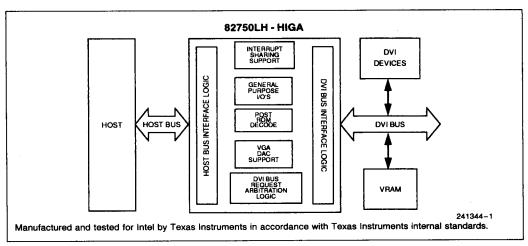

# 82750LH HOST INTERFACE GATE ARRAY

The 82750LH or HIGA is the Host Interface Gate Array for use in DVI® Systems. Its primary function is to interface the host bus (MicroChannel for PS/2-based systems, ISA for AT-based systems) to the DVI bus. The HIGA also serves five secondary func-

tions. It performs Power-On-Self-Test (POST) ROM Decode, DVI Bus Request Arbitration, VGA DAC Support, Interrupt Sharing Hardware Support and provides General Purpose Inputs and Outputs.

The 82750LH is fabricated on a  $1.2\mu$  double metal layer CMOS\* technology and is packaged in a 160-lead PQFP. The 82750LH is designed to run at a maximum frequency of 25 MHz.

### 1.0 PIN DESCRIPTIONS

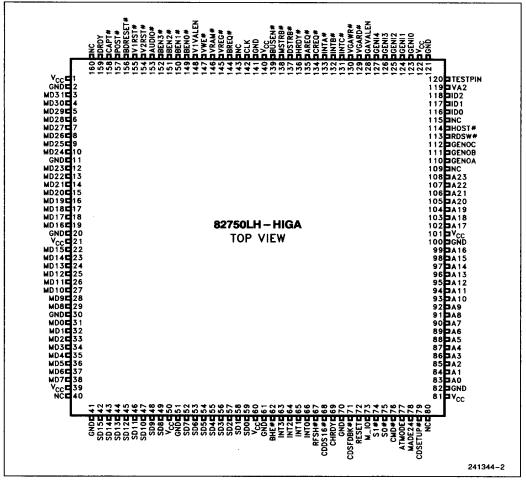

## 1.1 Pinout

Figure 1-1. 82750LH Pinout

# 1.2 Pin Cross Reference by Name and Location

Table 1-1. Pin Cross Reference by Pin Name

| Pin<br>Name | Location |

|-------------|----------|

| A0          | 83       |

| A1          | 84       |

| A2          | 85       |

| A3          | 86       |

| A4          | 87       |

| <b>A</b> 5  | 88       |

| A6          | 89       |

| A7          | 90       |

| A8          | 91       |

| A9          | 92       |

| A10         | 93       |

| A11         | 94       |

| A12         | 95       |

| A13         | 96       |

| A14         | 97       |

| A15         | 98       |

| A16         | 99       |

| A17         | 102      |

| A18         | 103      |

| A19         | 104      |

| A20         | 105      |

| A21         | 106      |

| A22         | 107      |

| A23         | 108      |

| AREQ#       | 135      |

| ATMODE      | 77       |

| AUDIO#      | 153      |

| BDRESET#    | 156      |

| BEN0#       | 149      |

| BEN1#       | 150      |

| BEN2#       | 151      |

| BEN3#       | 152      |

| BHE#        | 62       |

| BREQ#       | 144      |

| BUSEN#      | 139      |

| CAPT#       | 158      |

| CDDS16#     | 68       |

| CDSETUP#    | 79       |

| CDSFDBK#    | 71       |

| CHRDY       | 69       |

| Table 1-1. Pin Cross I |            |  |

|------------------------|------------|--|

| Pin Location           |            |  |

| Name                   | 142        |  |

| CLK<br>CMD#            | 76         |  |

| CREQ#                  |            |  |

| DRDY                   | 134<br>159 |  |

|                        | 137        |  |

| DSTRB# GAVALEN         |            |  |

|                        | 128        |  |

| GENI0                  | 123        |  |

| GENI1                  | 124        |  |

| GENI2                  | 125        |  |

| GENI3                  | 126        |  |

| GENI4                  | 127        |  |

| GENOA                  | 110        |  |

| GENOB                  | 111        |  |

| GENOC                  | 112        |  |

| GND                    | 2          |  |

| GND                    | 11         |  |

| GND                    | 20         |  |

| GND                    | 30         |  |

| GND                    | 41         |  |

| GND                    | 51         |  |

| GND                    | 61         |  |

| GND                    | 70         |  |

| GND                    | 82         |  |

| GND                    | 100        |  |

| GND                    | 121        |  |

| GND                    | 141        |  |

| HOST#                  | 114        |  |

| HRDY#                  | 136        |  |

| ID0                    | 116        |  |

| ID1                    | 117        |  |

| ID2                    | 118        |  |

| INTA#                  | 133        |  |

| INTB#                  | 132        |  |

| INTC#                  | 131        |  |

| INT0                   | 66         |  |

| INT1                   | 65         |  |

| INT2                   | 64         |  |

| INT3                   | 63         |  |

| MADE24                 | 78         |  |

| MD0                    | 31         |  |

|                        |            |  |

| erence by Pin Name |          |  |

|--------------------|----------|--|

| Pin<br>Name        | Location |  |

| MD1                | 32       |  |

| MD2                | 33       |  |

| MD3                | 34       |  |

| MD4                | 35       |  |

| MD5                | 36       |  |

| MD6                | 37       |  |

| MD7                | 38       |  |

| MD8                | 29       |  |

| MD9                | 28       |  |

| MD10               | 27       |  |

| MD11               | 26       |  |

| MD12               | 25       |  |

| MD13               | 24       |  |

| MD14               | 23       |  |

| MD15               | 22       |  |

| MD16               | 19       |  |

| MD17               | 18       |  |

| MD18               | 17       |  |

| MD19               | 16       |  |

| MD20               | 15       |  |

| MD21               | 14       |  |

| MD22               | 13       |  |

| MD23               | 12       |  |

| MD24               | 10       |  |

| MD25               | 9        |  |

| MD26               | 8        |  |

| MD27               | 7        |  |

| MD28               | 6        |  |

| MD29               | 5        |  |

| MD30               | 4        |  |

| MD31               | 3        |  |

| MSTRB#             | 138      |  |

| M_10               | 73       |  |

| NC                 | 40       |  |

| NC                 | 80       |  |

| NC                 | 109      |  |

| NC                 | 115      |  |

| NC NC              | 143      |  |

| NC                 | 160      |  |

| POST#              | 157      |  |

| Pin<br>Name     | Location |

|-----------------|----------|

| RDSW#           | 113      |

| RESET           | 72       |

| RFSH#           | 67       |

| SD0             | 59       |

| SD1             | 58       |

| SD2             | 57       |

| SD3             | 56       |

| SD4             | 55       |

| SD5             | 54       |

| SD6             | 53       |

| SD7             | 52       |

| SD8             | 49       |

| SD9             | 48       |

| SD10            | 47       |

| SD11            | 46       |

| SD12            | 45       |

| SD13            | 44       |

| SD14            | 43       |

| SD15            | 42       |

| S0#             | 75       |

| S1#             | 74       |

| TESTPIN         | 120      |

| VA2             | 119      |

| V <sub>CC</sub> | 1        |

| V <sub>CC</sub> | 21       |

| V <sub>CC</sub> | 39       |

| V <sub>CC</sub> | 50       |

| V <sub>CC</sub> | 60       |

| V <sub>CC</sub> | 81       |

| V <sub>CC</sub> | 101      |

| V <sub>CC</sub> | 122      |

| V <sub>CC</sub> | 140      |

| VGARD#          | 129      |

| VGAWR#          | 130      |

| VRAM#           | 146      |

| VREG#           | 145      |

| VWE#            | 147      |

| V1RST#          | 155      |

| V2RST#          | 154      |

| V1VALEN         | 148      |

Table 1-2. Pin Cross Reference by Pin Number

| Location | Pin<br>Name     |

|----------|-----------------|

| 1        | V <sub>CC</sub> |

| 2        | GND             |

| 3        | MD31            |

| 4        | MD30            |

| 5        | MD29            |

| 6        | MD28            |

| 7        | MD27            |

| 8        | MD26            |

| 9        | MD25            |

| 10       | MD24            |

| 11       | GND             |

| 12       | MD23            |

| 13       | MD22            |

| 14       | MD21            |

| 15       | MD20            |

| 16       | MD19            |

| 17       | MD18            |

| 18       | MD17            |

| 19       | MD16            |

| 20       | GND             |

| 21       | V <sub>CC</sub> |

| 22       | MD15            |

| 23       | MD14            |

| 24       | MD13            |

| 25       | MD12            |

| 26       | MD11            |

| 27       | MD10            |

| 28       | MD9             |

| 29       | MD8             |

| 30       | GND             |

| 31       | MD0             |

| 32       | MD1             |

| 33       | MD2             |

| 34       | MD3             |

| 35       | MD4             |

| 36       | MD5             |

| 37       | MD6             |

| 38       | MD7             |

| 39       | V <sub>CC</sub> |

| 40       | NC              |

| Table 1-2. Pin Cross F |                 |  |

|------------------------|-----------------|--|

| Location               | Pin<br>Name     |  |

| 41                     | GND             |  |

| 42                     | SD15            |  |

| 43                     | SD14            |  |

| 44                     | SD13            |  |

| 45                     | SD12            |  |

| 46                     | SD11            |  |

| 47                     | SD10            |  |

| 48                     | SD9             |  |

| 49                     | SD8             |  |

| 50                     | V <sub>CC</sub> |  |

| 51                     | GND             |  |

| 52                     | SD7             |  |

| 53                     | SD6             |  |

| 54                     | SD5             |  |

| 55                     | SD4             |  |

| 56                     | SD3             |  |

| 57                     | SD2             |  |

| 58                     | SD1             |  |

| 59                     | SD0             |  |

| 60                     | V <sub>CC</sub> |  |

| 61                     | GND             |  |

| 62                     | BHE#            |  |

| 63                     | INT3            |  |

| 64                     | INT2            |  |

| 65                     | INT1            |  |

| 66                     | INT0            |  |

| 67                     | RFSH#           |  |

| 68                     | CDDS16#         |  |

| 69                     | CHRDY           |  |

| 70                     | GND             |  |

| 71                     | CDSFDBK#        |  |

| 72                     | RESET           |  |

| 73                     | M_IO            |  |

| 74                     | S1#             |  |

| 75                     | S0#             |  |

| 76                     | CMD#            |  |

| 77                     | ATMODE          |  |

| 78                     | MADE24          |  |

| 79                     | CDSETUP#        |  |

| 80                     | NC              |  |

|                        |                 |  |

| Location | Pin<br>Name     |

|----------|-----------------|

| 81       | V <sub>CC</sub> |

| 82       | GND             |

| 83       | A0              |

| 84       | A1              |

| 85       | A2              |

| 86       | A3              |

| 87       | A4              |

| 88       | A5              |

| 89       | A6              |

| 90       | A7              |

| 91       | A8              |

| 92       | A9              |

| 93       | A10             |

| 94       | A11             |

| 95       | A12             |

| 96       | A13             |

| 97       | A14             |

| 98       | A15             |

| 99       | A16             |

| 100      | GND             |

| 101      | $V_{CC}$        |

| 102      | A17             |

| 103      | A18             |

| 104      | A19             |

| 105      | A20             |

| 106      | A21             |

| 107      | A22             |

| 108      | A23             |

| 109      | NC              |

| 110      | GENOA           |

| 111      | GENOB           |

| 112      | GENOC           |

| 113      | RDSW#           |

| 114      | HOST#           |

| 115      | NC              |

| 116      | ID0             |

| 117      | ID1             |

| 118      | ID2             |

| 119      | VA2             |

| 120      | TESTPIN         |

|          | _               |

| Location | Pin<br>Name     |

|----------|-----------------|

| 121      | GND             |

| 122      | VCC             |

| 123      | GENI0           |

| 124      | GENI1           |

| 125      | GENI2           |

| 126      | GEBI3           |

| 127      | GENI4           |

| 128      | GAVALEN         |

| 129      | VGARD#          |

| 130      | VGAWR#          |

| 131      | INTC#           |

| 132      | INTB#           |

| 133      | INTA#           |

| 134      | CREQ#           |

| 135      | AREQ#           |

| 136      | HRDY#           |

| 137      | DSTRB#          |

| 138      | MSTRB#          |

| 139      | BUSEN#          |

| 140      | V <sub>CC</sub> |

| 141      | GND             |

| 142      | CLK             |

| 143      | NC              |

| 144      | BREQ#           |

| 145      | VREG#           |

| 146      | VRAM#           |

| 147      | VWE#            |

| 148      | V1VALEN         |

| 149      | BEN0#           |

| 150      | BEN1#           |

| 151      | BEN2#           |

| 152      | BEN3#           |

| 153      | AUDIO#          |

| 154      | V2RST#          |

| 155      | V1RST#          |

| 156      | BDRESET#        |

| 157      | POST#           |

| 158      | CAPT#           |

| 159      | DRDY            |

| 160      | NC              |

|          |                 |

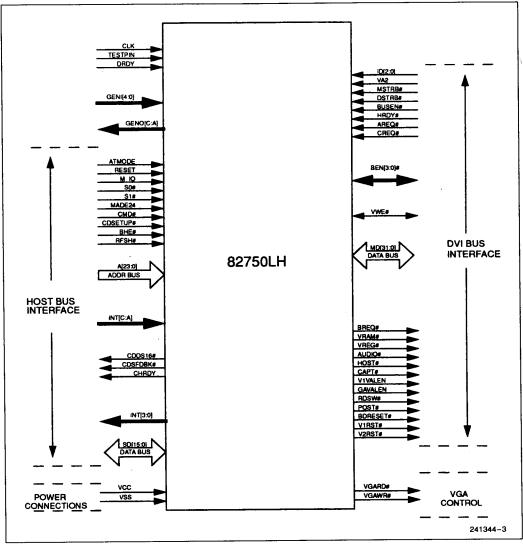

Figure 1-2. 82750LH Functional Signal Groupings

# 1.3 Pin Descriptions

The following tables provide descriptions of 82750LH pins:

Table 1-3. General Use Signal Pin Descriptions

| Symbol  | Туре | Name and Function                                                                                                                                                                                                                                                          |

|---------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TESTPIN | 1    | TESTPIN is used with RESET to force all output pins to their high-impedance state. When TESTPIN and RESET are both high all outputs and all bi-directionals are in their high-impedance state. TESTPIN has an internal pull down resistor of approximately 70 K $\Omega$ . |

| DRDY    | l    | DRDY is a general purpose status signal but is usually used as the Data Ready Status bit from the capture subsystem. The status of DRDY appears in bit 0 of the General Control Register. DRDY has an internal pull up resistor of approximately 70 K $\Omega$ .           |

| GENI0   | _    | GENI0 is a generic input pin whose state can be read through General Status Register bit 4. GENI0 has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                        |

| GENI1   | 1    | GENI1 is a generic input pin whose state can be read through the General Status Register bit 5. GENI1 has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                    |

| GENI2   | 1    | GENI2 is a generic input pin whose state can be read through General Status Register bit 6. GENI2 has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                        |

| GENI3   |      | GENI3 is a generic input pin whose state can be read through the General Status Register bit 7. GENI3 has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                    |

| GENI4   | ı    | GENI4 is a generic input pin whose state can be read through the General Status Register bit 0. GENI4 has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                    |

| GENOA   | 0    | GENOA is a generic output from the HIGA that is controlled by the General Control Register bit 4.                                                                                                                                                                          |

| GENOB   | 0    | GENOB is a generic output from the HIGA that is controlled by the General Control Register bit 5.                                                                                                                                                                          |

| GENOC   | 0    | GENOC is a generic output from the HIGA that is controlled by the General Control Register bit 2.                                                                                                                                                                          |

Table 1-4. DVI Bus Signal Pin Descriptions

| Table 1-4. D41 Das Signal Fill Descriptions |      |                                                                                                                                                                                                                                                                                                                                                                                 |  |

|---------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                                      | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                               |  |

| ID[2:0]                                     | l    | ID0, ID1 and ID2 are the DVI Device ID input pins used by the HIGA to decode the DVI Devices internal to the HIGA. The HIGA uses DVI Device 3 and DVI Device 2 (POST ROM). ID0, ID1 and ID2 have internal pull up resistors of approximately 70 K $\Omega$ .                                                                                                                    |  |

| VA2                                         | ı    | VA2 is used to decode DVI Device 3 into two 32-bit registers.                                                                                                                                                                                                                                                                                                                   |  |

| MSTRB#                                      |      | MSTRB# is the Memory Strobe signal used to indicate the end of a memory cycle. MSTRB# is also used to indicate when data can be read from the DVI Data Bus. The HIGA samples the DVI Data Bus on the rising edge of CLK during MSTRB#. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                                                            |  |

| DSTRB#                                      |      | DSTRB# is the DVI Device Strobe signal used to indicate a DVI Device cycle on the DVI Bus. MSTRB# is still used to indicate when data can be read from the DVI Data Bus, even though the bus cycle is a DVI Device Bus cycle. The HIGA samples DVI Bus data on the rising edge of CLK during MSTRB#. This signal has an internal purp resistor of approximately 70 K $\Omega$ . |  |

| BUSEN#                                      | ı    | BUSEN# is the Bus Enable signal on the DVI Bus. The HIGA uses BUSEN# as an indicator to know when the DVI Bus has been given up by the 82750PB. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                                                                   |  |

Table 1-4. DVI Bus Signal Pin Descriptions (Continued)

| Symbol    | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                            |  |

|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| BREQ#     | 0    | BREQ# is a Bus Cycle Request signal to the 82750PB. The 82750PB responds with a BUSEN# to indicate that the request is being serviced.                                                                                                                                                                                                                       |  |

| HRDY#     | ı    | HRDY# is the Host Ready signal from the 82750PB. The HIGA uses HRDY# to drop the BREQ# signal to the 82750PB. This signal has an internal pull up resisted approximatley 70 K $\Omega$ .                                                                                                                                                                     |  |

| VRAM#     | 0    | VRAM# is the Bus Cycle Type Indicator signal for the 82750PB. When VRAM# is active with a bus request (BREQ#) then the DVI Bus cycle will be a VRAM access or a DVI Device Access (as opposed to an 82750PB register access).                                                                                                                                |  |

| VREG#     | 0    | VREG# is a bus cycle type indicator for the 82750PB. When VREG# is active with a bus request (BREQ#) then the DVI Bus cycle will be an 82750PB register access. The VREG# signal is always the opposite of VRAM#.                                                                                                                                            |  |

| AREQ#     | ı    | AREQ# is the Audio Bus Request signal on the DVI Bus. The HIGA arbitrates the external requests and the internal requests and presents the BREQ# signal to the 82750PB. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                        |  |

| CREQ#     | 1    | CREQ# is the Capture/SCSI Bus Request signal on the DVI Bus. The HIGA arbitrates the external requests and the internal requests and presents the BREQ# signal to the 82750PB. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                 |  |

| AUDIO#    | 0    | AUDIO# is the arbitrated output from the HIGA's internal arbitration logic. The HIGA arbitrates the Audio request, Capture/SCSI request and the HIGA internal requests and decides who should respond to the next DVI Bus cycle with BUSEN# active. AUDIO# active indicates that AREQ# is currently being serviced or will be serviced with the next BUSEN#. |  |

| HOST#     | 0    | HOST# active indicates that an internal request is currently being serviced or will be serviced with the next BUSEN#.                                                                                                                                                                                                                                        |  |

| CAPT#     | 0    | CAPT# active indicates that CREQ# is currently being serviced or will be serviced with the next BUSEN#.                                                                                                                                                                                                                                                      |  |

| CLK       | ı    | CLK is a CMOS compatible clock signal for the HIGA. The HIGA uses CLK to synchronize events on the host bus to events on the DVI Bus. All synchronous events occur on the rising edge of CLK.                                                                                                                                                                |  |

| MD[31:0]  | В    | MD[31:0] are the DVI Bus Data Bus signals used to transfer data between the HIGA and VRAM or other DVI Devices. At the beginning of DVI Bus cycles, the MD[31:0] lines carry the address information. These signals have internal pull up resistors of approximately 70 K $\Omega$ .                                                                         |  |

| V1VALEN   | 0    | V1VALEN is the VRAM Latch Enable signal input to the 82750PB. While V1VALE is high and BUSEN# is low, address information is presented on the MD[31:0] data lines.                                                                                                                                                                                           |  |

| GAVALEN   | 0    | GAVALEN is the VRAM Address Latch Enable signal input to devices on the DVI Bus. GAVALEN's high to low transition lags V1VALEN by one clock period.                                                                                                                                                                                                          |  |

| BEN[3:0]# | В    | BEN0# through BEN3# are the Byte Enable signals on the DVI Bus. They define which byte or bytes are involved in the DVI Bus cycle. BEN0# signals the use of the least significant byte, or data lines MD[7:0]. These signals have internal pull up resistors of approximately 70 K $\Omega$ .                                                                |  |

| VWE#      | В    | VWE# is the read/write direction control for the DVI Bus. When VWE# is low, the bus cycle is a write. This signal has an internal pull up resistor of approximately 70 $\rm K\Omega$ .                                                                                                                                                                       |  |

Table 1-4. DVI Bus Signal Pin Descriptions (Continued)

| Symbol   | Туре | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| RDSW#    | 0    | RDSW# is used to gate the switch information onto the DVI Bus data bus lines MD[31:0]. The trailing edge of RDSW# (low to high) latches the information into the HIGA. MD[7:0] lines are latched into the I/O Port Switch Register while the MD[15:8] lines are latched into the POST Address Switch Register. The HIGA uses this information to configure the I/O Port Address and POST ROM Address while in the ATMODE of operation.                                                                                  |  |

| POST#    | 0    | POST# is the chip select output for the POST ROM on the DVI Bus. POST# is a decode of DVI Device 2, DSTRB# and not VWE#. Since POST is an eight bit device, the HIGA does not return the CDDS16# (or MEMCS16#) signal during POST accesses. Additionally, special steering logic inside the HIGA logically connects the MD[7:0] lines to the SD[7:0] lines regardless of the byte address. Therefore, consecutive byte accesses do not progress from MD[7:0] to MD[15:8 to MD[23:16], etc. when accessing the POST ROM. |  |

| BDRESET# | 0    | BDRESET# is the Board Reset signal controlled by the General Control Registe bit 0. BDRESET# is also applied when the RESET input is active. Besides driving the output pin low, BDRESET# also resets the HIGA internal registers, state machine and FIFO logic. The POS and PAR registers are not affected by Board Reset. BDRESET# should be held low for at least 10 µs to guarantee a full board reset.                                                                                                             |  |

| V1RST#   | 0    | V1RST# is the 82750PB Reset signal controlled by the General Control Register bit 1. V1RST is also applied when the RESET input is active.                                                                                                                                                                                                                                                                                                                                                                              |  |

| V2RST#   | 0    | V2RST# is the 82750DB Reset signal controlled by the General Control Register bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

Table 1-5. Host Bus Signal Pin Descriptions

| Table 1-3. Host bus Signal Fill Descriptions |      |                                                                                                                                                                                                                                                          |  |

|----------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                                       | Туре | Name and Function                                                                                                                                                                                                                                        |  |

| ATMODE                                       | l    | ATMODE configures the HIGA for an AT or ISA type interface for the host bus when high. When low, ATMODE configures the host interface for the MicroChannel type interface. This signal has an internal pull up resistor of approximately 70 K $\Omega$ . |  |

| RESET                                        | I    | RESET is the main reset signal for the HIGA. This signal has an internal pull up esistor of approximately 70 K $\Omega$ .                                                                                                                                |  |

| SD[15:0]                                     | В    | SD[15:0] are the host data bus signals used to transfer data between the host and the HIGA. These signals have internal pull up resistors of approximately 70 K $\Omega$ .                                                                               |  |

| A[23:0]                                      | - 1  | A[23:0] are the host address pins. The address signals are used to access the registers internal to the HIGA as well as the VRAM and DVI Devices on the DVI Bus. These signals have internal pull up resistors of approximately 70 K $\Omega$ .          |  |

| M_IO<br>(IOWRC#)                             | l    | M_IO is the memory or I/O cycle indicator signal on the MicroChannel Bus when the HIGA is in the non-ATMODE. M_IO is the ISA IOWRC# signal when the HIGA is in the ATMODE of operation.                                                                  |  |

| S0#<br>(MRDC#)                               | I    | SO# is the Status 0 signal on the MicroChannel Bus when the HIGA is in the non-ATMODE, S0# is the ISA MRDC# signal when the HIGA is in the ATMODE of operation.                                                                                          |  |

| S1#<br>(MWRC#)                               | 1    | S1# is the Status 1 signal on the MicroChannel Bus when the HIGA is in the non-ATMODE. S0# is the ISA MWRC# signal when the HIGA is in the ATMODE of operation.                                                                                          |  |

| MADE24<br>(IORDC#)                           | ı    | MADE24 is the below 16M memory cycle indicator signal on the MicroChannel Bus when the HIGA is in the non-ATMODE. MADE24 is the ISA IORDC # signal when the HIGA is in the ATMODE of operation.                                                          |  |

Table 1-5. Host Bus Signal Pin Descriptions (Continued)

| Symbol                 | Туре | Name and Function                                                                                                                                                                                                                                                      |  |  |

|------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CMD#<br>(BALE)         | l    | CMD# is the command signal on the MicroChannel Bus when the HIGA is in the non-ATMODE. CMD# is the ISA BALE signal when the HIGA is in the ATMODE of operation. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                          |  |  |

| CDSETUP#<br>(AEN)      | I    | CDSETUP# is the POS setup cycle signal on the MicroChannel Bus when the HIGA is in the non-ATMODE. CDSETUP# is the ISA AEN signal when the HIGA is in the ATMODE of operation. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .           |  |  |

| BHE#                   | ı    | BHE# is the Byte High Enable signal from the host bus. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                                                                                                                                   |  |  |

| RFSH#                  | ı    | RFSH# is the Refresh Cycle indicator signal on the host bus and is used by the HIGA to ignore memory read cycles that occur during host Refresh cycles. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                                  |  |  |

| INTA#                  | l    | INTA# is the Video Interrupt signal on the DVI bus. The INTA# signal can be steered to one of the INT0, INT1, INT2 or INT3 outputs through programming of the POS4 register in the HIGA. This signal has an internal pull up resistor of approximately 70 K $\Omega$ . |  |  |

| INTB#                  | I    | INTB# is the Audio Interrupt signal on the DVI Bus. The INTB# signal can be steered to one of the INT1 or INT2 outputs through programming of the POS4 register in the HIGA. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .             |  |  |

| INTC#                  | I    | INTC# is the Capture/SCSI Interrupt signal on the DVI Bus. INTC# can be steered to one of the INT1 or INT2 outputs through programming of the POS4 register in the HIGA. This signal has an internal pull up resistor of approximately 70 K $\Omega$ .                 |  |  |

| CDDS16#<br>(IOCS16#)   | 0    | CDDS16# is the Card Data Size16 signal on the MicroChannel Bus when the HIGA is in the non-ATMODE of operation. CDDS16# is the ISA IOCS16# signal when the HIGA is in the ATMODE.                                                                                      |  |  |

| CDSFDBK#<br>(MEMCS16#) | 0    | CDSFDBK# is the Card Select Feedback signal on the MicroChannel Bus when the HIGA is in the non-ATMODE of operation. CDSFDBK# is the ISA MEMCS16# signal when the HIGA is in the ATMODE.                                                                               |  |  |

| CHRDY<br>(IOCHRDY)     | 0    | CHRDY is the Channel Ready signal on the MicroChannel Bus when the HIGA is in the non-ATMODE of operation. CHRDY is the ISA IOCHRDY signal when the HIGA is in the ATMODE.                                                                                             |  |  |

| INT[3:0]               | 0    | INTO through INT3 are the four interrupt output pins on the HIGA. In the non-ATMODE of operation the INT outputs are active low, open collector type outputs. In the ATMODE of operation the INT outputs are active high, to                                           |  |  |

# Table 1-6. VGA Support Signal Pin Descriptions

| Symbol                                               | Туре | Name and Function                                                                                                                                                                                                                               |

|------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VGARD#                                               | 0    | VGARD# is the VGA DAC Read signal. VGARD# is active during host reads of the VGA DAC Test Registers. Note that the HIGA does not drive the SD[15:0] lines during VGARD# cycles, but does provide the other host timing necessary for the cycle. |

| VGAWR# O VGAWR# is the VGA DA the VGA DAC Registers. |      | VGAWR# is the VGA DAC Write signal. VGAWR# is active during host writes of the VGA DAC Registers. Note that the HIGA does not accept any data from the SD[15:0] lines during VGAWR# cycles.                                                     |

Table 1-7. Output Pins\*\*

| Tubic 1-7. Output I ilia |                 |  |  |  |

|--------------------------|-----------------|--|--|--|

| Name                     | Active<br>Level |  |  |  |

| INT[3:0]                 | *               |  |  |  |

| CDDS16#                  | Low             |  |  |  |

| CHRDY                    | High            |  |  |  |

| CDSFDBK#                 | Low             |  |  |  |

| GENO[C:A]                | High            |  |  |  |

| RDSW#                    | Low             |  |  |  |

| HOST#                    | Low             |  |  |  |

| GAVALEN                  | High            |  |  |  |

| VGARD#                   | Low             |  |  |  |

| VGAWR#                   | Low             |  |  |  |

| BREQ#                    | Low             |  |  |  |

| VREG#                    | Low             |  |  |  |

| VRAM#                    | Low             |  |  |  |

| V1VALEN                  | High            |  |  |  |

| AUDIO#                   | Low             |  |  |  |

| V2RST#                   | Low             |  |  |  |

| V1RST#                   | Low             |  |  |  |

| BDRESET#                 | Low             |  |  |  |

| POST#                    | Low             |  |  |  |

| CAPT#                    | Low             |  |  |  |

# NOTE:

Table 1-8. Input Pins

| Name      | Active<br>Level | Sync/Async |  |  |

|-----------|-----------------|------------|--|--|

| BHE#      | Low             | Async      |  |  |

| RFSH#     | Low             | Async      |  |  |

| RESET     | High            | Async      |  |  |

| MIO       | High            | Async      |  |  |

| S1#       | Low             | Async      |  |  |

| S0#       | Low             | Async      |  |  |

| CMD#      | Low             | Async      |  |  |

| ATMODE    | High            | Async      |  |  |

| MADE24    | High            | Async      |  |  |

| CDSETUP#  | Low             | Async      |  |  |

| A[23:0]   | High            | Async      |  |  |

| ID[2:0]   | High            | Async      |  |  |

| VA2       | High            | Sync       |  |  |

| GENI[4:0] | High            | Async      |  |  |

| INT[C:A]  | Low             | Async      |  |  |

| CREQ#     | Low             | Async      |  |  |

| AREQ#     | Low             | Async      |  |  |

| HRDY#     | Low             | Sync       |  |  |

| DSTRB#    | Low             | Sync       |  |  |

| MSTRB#    | Low             | Sync       |  |  |

| BUSEN#    | Low             | Sync       |  |  |

| CLK       | High            | Sync       |  |  |

| DRDY#     | Low             | Async      |  |  |

## Table 1-9. Bidirectional Pins

| Name      | Active<br>Level | When Floated**             | Sync/Async |

|-----------|-----------------|----------------------------|------------|

| MD[31:0]  | High            | VRAM Read, DVI Device Read | Sync       |

| SD[15:0]  | High            | Host Reads                 | Async      |

| VWE#      | Low             |                            | Sync       |

| BEN[3:0]# | Low             |                            | Sync       |

#### NOTE:

<sup>\*</sup>Active high in ATMODE.

Active low in non-ATMODE.

<sup>\*\*</sup>All output and bidirectional pins are floated when TESTPIN and RESET are asserted together.

### 2.0 INTERNAL ARCHITECTURE

#### 2.1 DVI/Host Bus Interface

#### 2.1.1 DVI BUS OVERVIEW

The primary function of the HIGA is to interface the host bus (MicroChannel for PS/2-based systems, ISA for AT-based systems) to the DVI Bus. The DVI Bus connects VRAM, the 82750PB, Audio and host together through one common address and data path. The 82750PB normally owns the DVI Bus. The HIGA is designed to run at the same frequency as the 82750PB.

The data bus from the host passes through the HIGA before reaching the DVI Bus and also creates an intermediate path for passing around the HIGA. This allows for two types of accesses to components in the DVI system: accesses that require the use of the DVI Bus and those that do not. The two types of accesses are classified into a Slow Access Group and a Fast Access Group respectively. When the HIGA is running at 25 MHz a Fast Access takes about 400 ns (10 cycles) to complete while a Slow Access can take up to 3000 ns (75 cycles) to complete.

The DVI Bus supports up to 16 Mbytes of address space. The first 15 Mbytes of address space is reserved for RAM while the last 1 Mbyte of address space is reserved for communication between devices on the DVI Bus. The last 1 Mbyte of address space is divided into eight 128 Kbyte areas with each device assigned to one of the eight areas as a DVI Device ID. DVI Device ID 0 is the first 128K area above 15 Mbytes and DVI Device ID 7 is the last 128 Kbyte area. The following DVI Device ID assignments have been made:

Device ID 7 -82750PB Registers via the Host Bus

Device ID 6 — Capture Subsystem Registers

Device ID 5 — Audio Subsystem, Genlock and Keying Registers

Device ID 4 — CDROM Subsystem Registers

Device ID 3 - Reserved

Device ID 2 - Power-On-Self-Test (POST) ROM

Device ID 1 - Reserved

Device ID 0 - Reserved

### 2.1.2 EXPANDED MEMORY SPACE HOST/ VRAM CONNECTION

VRAM is seen by the host in memory space by a method known as EMS or Expanded Memory Space. The EMS method of expanding memory uses a technique in which memory is paged mapped through a "window" of the host's address space.

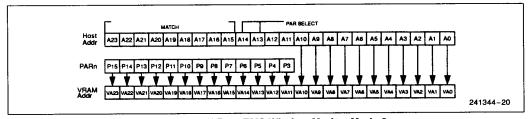

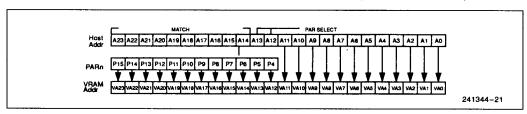

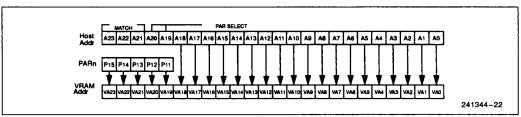

The HIGA supports 13 EMS window options ranging in size from 0 bytes to 16 Mbytes. The EMS window options that are supported are 0 bytes, 8 Kbytes, 16 Kbytes, 32 Kbytes, 64 Kbytes, 128 Kbytes, 256 Kbytes, 512 Kbytes, 1 Mbytes, 2 Mbytes, 4 Mbytes, 8 Mbytes, and 16 Mbytes. The EMS window size and starting window location are established by setting bits in the Configuration Registers.

A window's starting address must be a multiple of its size. As an example, a 128 Kbyte window must start on a 128 Kbyte boundary in the host's memory address space. Each EMS window is divided into four equally sized pages which have corresponding Page Address Registers (PARs). The PARs are used to map the logical (window) address space of the host independently into four pages of physical addresses in VRAM (with page aligned starting addresses).

#### 2.1.3 HOST/VRAM FIFO CONNECTION

There are four FIFOs connecting the host to VRAM in addition to the EMS connection. The FIFOs are in the host's I/O address space whereas the EMS window is in the host's memory address space. The FIFOs are divided into four types and there is one of each type available: a 16-Bit-Read FIFO, a 16-Bit-Write FIFO, a 32-Bit-Read FIFO and a 32-Bit-Write FIFO. A 16-bit FIFO will only access 16-bit words in the VRAM address space and is useful for accessing 82750PB registers. A 32-bit FIFO can access 32-bit words in the VRAM address space and is useful for accessing VRAM in high-performance modes or through Host DMA channels. All FIFOs can be operated in an Auto-increment Mode in which the VRAM address is incremented after each access through the FIFO.

#### 2.1.4 DVI DEVICE ACCESS

In order to allow accesses to DVI Devices (which are memory mapped) or to setup a FIFO without having to change the Page Address Registers, a Quick Access method is provided. The Quick Access method is selected by writing the DVI Device ID to a control register via an I/O operation. In this mode, the next memory access through the PARs (not FIFOs) will have the physical address modified to point to the selected DVI Device. The DVI Device ID must be rewritten for the next access through this path, even if the previous access was to the same DVI Device. This method reduces the overhead for accessing a DVI Device to one Fast Access and one Slow Access operation, without disturbing the PARs. Note that the Quick Access is armed for the next memory access through any of the PARs, regardless of the source of the access (Host or DMA).

# 2.2 Power-On-Self-Test ROM

The HIGA provides support for configuring and enabling/disabling a Power-On-Self-Test ROM. The POST ROM, when installed and enabled, will be executed after the host's POST but before the system boots and may contain a self-test program and any special configuration programs.

# 2.3 DVI Bus Request Arbitration

The HIGA arbitrates all of the requests for the DVI Bus and asserts the acknowledge for the highest priority request. The possible requests are: EMS from the HIGA's EMS logic, FIFO from the HIGA's internal FIFO logic, CAPT from the external CREQ# pin, AUDIO from the external AREQ# pin and V1REQ from DVI Device 3. The FIFO request is an arbitrated request from the FIFO logic which ranks the requests as follows: 32-Bit-Write FIFO, 16-Bit-Write FIFO, 32-Bit-Read FIFO, 16-Bit-Read FIFO. Table 2-1 summarizes the request priorities.

**Table 2-1. Bus Request Priority**

| Priority | Request           |

|----------|-------------------|

| 1        | EMS               |

| 2        | 32-Bit-Write FIFO |

| 3        | 16-Bit-Write FIFO |

| 4        | 32-Bit-Read FIFO  |

| 5        | 16-Bit-Read FIFO  |

| 6        | CAPT              |

| 7        | AUDIO             |

| 8        | V1REQ             |

The arbitration algorithm is such that once requests have been stacked up, the arbitration logic services the stacked up requests before any other requests will be considered. This behavior keeps a high-priority request from monopolizing the DVI Bus. For example, consider a situation where HREQ is asserted. While HREQ is being serviced AREQ is asserted, followed by CREQ. Even though AREQ was asserted first, CREQ will be the next to get attention. This is because when one request is already in the process of being serviced no other requests are considered and they stack up. Then when arbitration continues (after the service is completed) all stacked up requests enter at the same time and the one with the highest priority will be the next to be serviced. Only stacked up requests and requests that become active on the same CLK edge are arbitrated against each other. Otherwise, requests are honored in the order in which they are received.

Another example of the arbitration algorithm is one in which all of the possible requests become active in the opposite order of priority, all separated by one clock period. The first request to be serviced is the lowest priority one since it came in first, followed by the rest of the requests in order of priority or the opposite order in which they arrived. This is because they all stacked up behind the lowest priority request.

# 2.4 VGA DAC Support

The DVI Board may have a VGA type DAC onboard which can be used along with the Video Feature Connector to "copy" the video stream from the system's VGA. The onboard VGA video can then be keyed with 82750DB's output. The final RGB video information is output to a standard VGA monitor and connector. The monitor ID supplied to the monitor connector by the connected monitor can be read by the host.

All I/O writes on the system bus are monitored by the HIGA. When an I/O write falls into the range of 03C6-03C9, hex for the PS/2-based system or X3C6-X3C9 hex for the AT-based system, a VGA write to the onboard VGA DAC is generated, duplicating the data in the system's VGA DAC. I/O reads to 03C6-03C9 are ignored by the DVI Board to prevent two I/O devices from driving data at the same time. Using this eavesdropping programming technique together with the system's Video Feature Bus allows the DVI Board to maintain an RGB video stream identical to the system's VGA RGB creating a VGA compatible mode that is transparent to the programmer or user.

# 2.5 General Purpose Inputs and Outputs

The HIGA provides five General Purpose Inputs (GENI0-GENI4) and three General Purpose Outputs (GENOA, GENOB, and GENOC). Each of the General Purpose Inputs can be read through a bit in the General Status Register. Each of the General Purpose Outputs can be controlled by a bit in the General Control Register. See sections 2.6.5 and 2.6.6 for register bit assignments for each input and output.

# 2.6 Interrupt Sharing Hardware Support

The General Control Register contains the DINT (Disable Interrupt) bit that can be used to reassert

the interrupt levels on the bus in the AT Mode. When sharing interrupt levels within a DVI Board the DINT bit should be set to a one and then back to a zero in the interrupt routine after the system interrupt controller has been reset. If another interrupt was pending on the same level before the system interrupt controller was reset, the interrupt will be reasserted and not lost. The DINT bit does not change the interrupting conditions, it only blocks the signals just before being driven onto the AT bus.

# 2.7 HIGA Registers

All of the registers internal to the HIGA are in the Fast Access Group. These registers are located in the host's I/O space at BASE-BASE+3F hex plus the POS registers through the POS setup mechanism in PS/2-based machines. A register map of the HIGA registers is shown in Table 2-2.

Table 2-2. HIGA Register Map

| PAR0 HIGH                        | PAR0 LOW                   | BASE + 0 |

|----------------------------------|----------------------------|----------|

| PAR1 HIGH                        | PAR1 LOW                   | BASE + 2 |

| PAR2 HIGH                        | PAR2 LOW                   | BASE + 4 |

| PAR3 HIGH                        | PAR3 LOW                   | BASE+6   |

| ROM 8K SELECT REGISTER           | DVI DEVICE QUICK ACCESS    | BASE + 8 |

| 32-BIT-WRITE FIFO DATA HIGH      | 32-BIT-WRITE FIFO DATA LOW | BASE + 2 |

| 32-BIT-WRITE FIFO ADDR CNTR BYTE | 32-BIT-WRITE FIFO CONTROL  | BASE + 2 |

| 16-BIT-WRITE FIFO DATA HIGH      | 16-BIT-WRITE FIFO DATA LOW | BASE+2   |

| 16-BIT-WRITE FIFO ADDR CNTR BYTE | 16-BIT-WRITE FIFO CONTROL  | BASE + 2 |

| 32-BIT-READ FIFO DATA HIGH       | 32-BIT-READ FIFO DATA LOW  | BASE+2   |

| 32-BIT-READ FIFO ADDR CNTR BYTE  | 32-BIT-READ FIFO CONTROL   | BASE+2   |

| 16-BIT-READ FIFO DATA HIGH       | 16-BIT-READ FIFO DATA LOW  | BASE+2   |

| 16-BIT-READ FIFO ADDR CNTR BYTE  | 16-BIT-READ FIFO CONTROL   | BASE+2   |

| GENERAL STATUS REGISTER          | POS0                       | BASE + 3 |

| GENERAL CONTROL REGISTER         | POS1                       | BASE+3   |

| I/O PORT SWITCH REGISTER         | POS2                       | BASE + 3 |

| POST ADDRESS SWITCH REGISTER     | POS3                       | BASE + 3 |

| RESERVED                         | POS4                       | BASE + 3 |

| RESERVED                         | POS5                       | BASE+3   |

| VGA TEST REGISTER 3C9            | VGA TEST REGISTER 3C8      | BASE + 3 |

| VGA TEST REGISTER 3C7            | VGA TEST REGISTER 3C6      | BASE + 3 |

The fast access registers for the FIFO data ports can become slow access registers if the access must cause a DVI Bus cycle in order for it to complete. Reading an empty read FIFO or writing a full write FIFO are the only examples of this condition. All other system registers and VRAM are in the Slow Access Group.

#### 2.7.1 PAGE ADDRESS REGISTERS

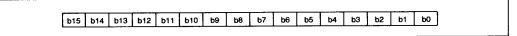

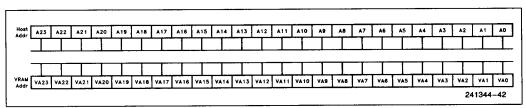

Figure 2-1. PARn

Page Address Registers 0-3 are read/write registers located at BASE+0 hex, BASE+2 hex, BASE+4 hex and BASE+6 hex respectively. The PARs are used to map the logical (window) address space of the host independently into four pages of physical addresses in VRAM. The PARs are 16-bit registers, although only the necessary top PAR bits are used in each EMS Window Mode.

#### 2.7.2 DVI DEVICE QUICK ACCESS REGISTER

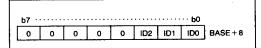

Figure 2-2. DVI Device Quick Access Register

The DVI Device Quick Access Register is a write-only register located at BASE+8 hex. This is an 8-bit register with only the lowest three bits defined. The value of the ID2, ID1 and ID0 taken as a three bit field define a DVI Device ID which is used in conjuction with the Quick Access Method of bypassing the PARs to access a DVI Device Register. The Quick Access Register will be used to force the access to the DVI Device ID contained in this register. The Quick Access is enabled by the writing of the Quick Access Register and lasts for just one access through the EMS Window.

The user is cautioned to keep in mind that the host CPU will turn one 16-bit access at an odd address

into two 8-bit accesses and the Quick Access would be enabled for only the first 8-bit access. The user is also cautioned to keep in mind that the HIGA does not distinguish between host cycles performed by the CPU and those that are performed via DMA.

#### 2.7.3 ROM 8K SELECT REGISTER

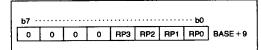

Figure 2-3. ROM 8K Select Register

The ROM 8K Select Register is an 8-bit write-only register located at BASE+9 hex. Only the lowest 4 bits are defined. This register is used to select the 8K page of POST ROM. On RESET the contents of this register is initialized to zero.

# 2.7.4 FIFO CONTROL, ADDRESS AND DATA REGISTERS

There are five registers associated with each of the FIFOs.

#### 2.7.4.1 32-Bit-Write FIFO Registers

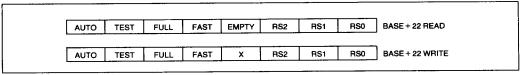

The 32-Bit-Write FIFO Control Register is a read/write register located at BASE+22 hex. Each of the bits in this register is described below.

Figure 2-4. 32-Bit-Write FIFO Control Register

**AUTO** (Bit 7 Read/Write)—The AUTO bit when set to a one will cause the FIFO Address Counter to increment after each DVI Bus cycle.

TEST (Bit 6 Read/Write)—The TEST bit is used for diagnostics and for ensuring a clean initialization of the FIFO. When initializing the FIFO, the first write to the control register should have this bit set to a one.

FULL (Bit 5 Read)—The FULL bit reflects the status of the data holding registers in the FIFO. If the FULL bit is on and data is written to the data ports then the access becomes a Slow Access.

FAST (Bit 4 Read)—The FAST bit allows the FIFO to perform Next-Fast VRAM cycles when the FIFO is full and the FIFO Address Counter is pointing to an even long-word. The Next-Fast VRAM cycle allows the FIFO to deposit two 32-bit words in one DVI Bus cycle, saving the overhead of arbitration and transfer of control for the second 32-bit word.

EMPTY (Bit 3 Read)—The EMPTY bit reflects the status of the data holding registers in the FIFO. A write FIFO should always be empty before any change is made to its FIFO Control Register that may cause a pending data operation to fail. Such operations include a change from AUTO to not AUTO (or the reverse), any change to the FIFO Address Counter and setting the TEST or TCLK bits. The 32-Bit-Write FIFO will try to empty the data registers whenever the most significant byte of a 32-bit word is received from the host. If a transfer from the host ends on the first, second or third byte then the FIFO will not go empty until the host performs a Flush Command. Sending a Flush Command to a FIFO that would have normally gone empty or was already empty does no harm whatsoever.

TCLK (Bit 5 Write)—The TCLK bit should be left as a zero for proper FIFO operation.

RS2-RS0 (Bits 2-0 Read/Write)—The RS2-0 bits are used as a field to select other registers in the FIFO. Table 2-3 indicates which registers are accessed by each combination of RS2-0.

Table 2-3. RS2-0 Register Selection

| RS2 | RS1 | RS0 | Register                                   |

|-----|-----|-----|--------------------------------------------|

| 0   | 0   | 0   | Address Counter Byte 0 (Least Significant) |

| 0   | 0   | 1   | Address Counter Byte 1                     |

| 0   | 1   | 0   | Address Counter Byte 2 (Most Significant)  |

| 0   | 1   | 1   | Test Register                              |

| 1   | 0   | 0   | Reserved                                   |

| 1   | 0   | 1   | Reserved                                   |

| 1   | 1   | 0   | Reserved                                   |

| 1   | 1   | 1   | Reserved                                   |

The 32-Bit-Write FIFO Address Counter Byte Register is a write-only register located at BASE+23 hex. This register holds each byte that is written to the FIFO's Address Counter before an access is initiated. Together the three FIFO Address Counter Bytes hold the 24-bit byte address of the destination of the FIFO data. The FIFO Control Register and the FIFO Address Counter Byte Register can be written with the same 16-bit I/O operation.

| B7 B6 B5 B4 B3 B2 B1 B0 BASE+ |    |

|-------------------------------|----|

|                               | B7 |

Figure 2-5. 32-Bit-Write FIFO Address Counter Byte Register (RS = 0,1,2) 32-Bit-Write FIFO Test Register (RS = 3)

The 32-Bit-Write FIFO Test Register is an 8-bit read/write register located at BASE + 23 hex that is accessed when bits RS[2:0] in the corresponding control register = 3(010). This register is used mainly for Flush Commands and diagnostics, however, it can be useful for gathering the information needed when saving the state of the FIFO for later restoration. When the FIFO Test Register is written, a Flush Command is performed. (The data written is not important.) When the FIFO Test Register is read, it re-

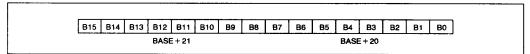

Figure 2-6. 32-Bit-Write FIFO Data Registers

turns some information. B0 will be zero when the first byte has been written to the FIFO Data Register, B1 will be zero when the second byte has been written and so on.

The 32-Bit-Write FIFO Data High and Low Registers are two 8-bit write-only registers located at BASE+20 hex and BASE+21 hex. The FIFO data registers can be written 8 or 16 bits at a time. However, when writing with byte operations, address BASE+21 hex must be written between any writes to BASE+20 hex.

#### 2.7.4.2 16-Bit-Write FIFO Registers

The 16-Bit-Write FIFO registers are identical to that of the 32-Bit-Write FIFO described above except that the FAST bit in the 16-Bit-Write FIFO Control

Register has no meaning. Locations for the 16-Bit-Write FIFO Registers are listed below.

16-Bit-Write FIFO Control Register = BASE+26 hex

16-Bit-Write FIFO Address Counter Byte Register = BASE + 27 hex

16-Bit-Write FIFO Test Register = BASE + 27 hex

16-Bit-Write FIFO Data High Register = BASE + 25 hex

16-Bit-Write FIFO Data Low Register = BASE + 24 hex

### 2.7.4.3 32-Bit-Read FIFO Registers

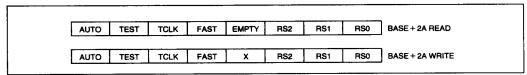

The 32-Bit-Read FIFO Control Register is an 8-bit read/write register located at BASE+2A hex. Each of the bits in this register is described below.

1

Figure 2-7. 32-Bit-Read FIFO Control Register

**AUTO** (Bit 7 Read/Write)—The AUTO bit when set to a one will cause the FIFO Address Counter to increment after each DVI Bus cycle.

**TEST** (Bit 6 Read/Write)—The TEST bit is used for diagnostics and for ensuring a clean initialization of the FIFO. When initializing the FIFO, the first write to the control register should have this bit set to a one.

FULL (Bit 5 Read)—The FULL bit reflects the status of the data holding registers in the FIFO. A read FIFO should always be full before any change is made to its FIFO Control Register that may cause a pending data operation to fail. Such operations include a change from AUTO to not AUTO (or-the reverse), any change to the FIFO Address Counter and setting the TEST or TCLK bits. The 32-Bit-Read FIFO will try to fill the data registers whenever the most significant byte of a 32-bit word is read from the host. If a transfer from the host ends on the first. second or third byte then the FIFO will contain some residual data. When in the AUTO mode the FIFO will always contain some residual data after the transfer is finished. This unwanted data is a by-product of reading ahead and trying to keep the FIFO full.

FAST (Bit 4 Read)—The FAST bit allows the FIFO to perform Next-Fast VRAM cycles when the FIFO is empty and the FIFO Address Counter is pointing to an even long-word. The Next-Fast VRAM cycle allows the FIFO to fetch two 32-bit words in one DVI Bus cycle, saving the overhead of arbitration and transfer of control for the second 32-bit word.

**EMPTY** (Bit 3 Read)—The EMPTY bit reflects the status of the data holding registers in the FIFO. If the EMPTY bit is on and data is read from the data ports then the access becomes a Slow Access.

**TCLK** (Bit 5 Write)—The TCLK bit should be left as a zero for proper FIFO operation.

**RS2-RS0** (Bits 2-0 Read/Write)—The RS2-0 bits are used as a field to select other registers in the FIFO.

Table 2-4. RS2-0 Register Selection

| RS2 | RS1 | RS0 | Register                                   |

|-----|-----|-----|--------------------------------------------|

| 0   | 0   | 0   | Address Counter Byte 0 (Least Significant) |

| 0   | 0   | 1   | Address Counter Byte 1                     |

| 0   | 1   | 0   | Address Counter Byte 2 (Most Significant)  |

| 0   | 1   | 1   | Test Register                              |

| 1   | 0   | 0   | Reserved                                   |

| 1   | 0   | 1   | Reserved                                   |

| 1   | 1   | 0   | Reserved                                   |

| 1   | 1   | 1   | Reserved                                   |

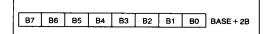

The 32-Bit-Read FIFO Address Counter Byte Register is a write-only register located at BASE+2B hex. This register holds each byte that is written to the FIFO's Address Counter before an access is initiated. Together the three FIFO Address Counter Bytes hold the 24-bit byte address of the source of the FIFO data. The FIFO Control Register and the FIFO Address Counter Byte Register can be written with the same 16-bit I/O operation.

The 32-Bit-Read FiFO Test Register is an 8-bit read/write register located at BASE+2B hex that is accessed when RS[2:0] in the corresponding control register = 3 (011). This register is used for diagnostic purposes only.

Figure 2-8. 32-Bit-Read FIFO Address Counter Byte Register (RS = 0,1,2) 32-Bit-Read FIFO Test Register (RS3)

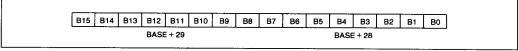

The 32-Bit-Read FIFO Data High and Low Registers are two 8-bit read-only data registers located at BASE+28 hex and BASE+29 hex. The FIFO data registers can be written 8 or 16 bits at a time. However, when writing with byte operations, address BASE+29 hex must be written between any writes to BASE+28 hex.

Figure 2-9. 32-Bit-Read FIFO Data Registers

#### 2.7.4.4 16-Bit-Read FIFO Registers

The Registers for the 16-Bit-Read FIFO are identical to those of the 32-Bit-Read FIFO described above except that the FAST bit in the 16-Bit-Read FIFO Control Register has no meaning. Locations for the 16-Bit-Read FIFO Registers are listed below.

16-Bit-Read FIFO Control Register = BASE+2E hex

16-Bit-Read FIFO Address Counter Byte Register = BASE + 2F hex

16-Bit-Read FIFO Test Register = BASE + 2F hex

16-Bit-Read FIFO Data High Register = BASE + 2D hex

16-Bit-Read FIFO Data Low Register = BASE + 2C hex

#### 2.7.5 GENERAL STATUS REGISTER

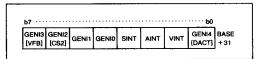

Figure 2-10. General Status Register

The General Status Register is an 8-bit read-only register located at BASE+31 hex. This register contains three dedicated bits that are used to identify interrupt sources and five general purpose input bits (GENIO-4) which correspond directly to the input pins of the same names. In the bit definitions below, the bit names and descriptions shown in brackets ([ ]) are examples of some useful functions that these pins can serve in a typical DVI environment. These bits may, of course, be assigned to any compatible input at the user's discretion.

GENI3 (Bit 7)-General Purpose Input 3.

[VFB (Bit 7)—VFB will be a zero if the DVI Board is connected to a Video Feature Bus.]

GENI2 (Bit 6)—General Purpose Input 2.

[CS2 (Bit 6)—CS2 will be a zero if the DVI Board is hosting a Capture Board.]

GENI1 (Bit 5)-General Purpose Input 1.

GENIO (Bit 4)—General Purpose Input 0.

**SINT** (Bit 3)—SINT (SCSI Interrupt) is a read-only bit that reflects the status of the interrupt signal from the SCSI/Capture Subsystem. The SINT bit will be a one whenever the interrupt signal is active.

**AINT** (Bit 2)—AINT (Audio Interrupt) is a read-only bit that reflects the status of the interrupt signal from the Audio Subsystem. The AINT bit will be a one whenever the interrupt signal is active.

VINT (Bit 1)—VINT (Video Interrupt) is a read-only bit that reflects the status of the interrupt signal from the Video Subsystem (82750PB). The VINT bit will be a one whenever the interrupt signal is active.

GENI4 (Bit 0)-General Purpose Input 4.

[DACT (Bit 0)—DACT (DAC Test) bit is a read-only bit that reflects the status of the RGB signals on the Video Output Connector. The DACT bit will be a zero whenever one of the RGB levels is above the 50% of full scale point.]

### 2.7.6 GENERAL CONTROL REGISTER

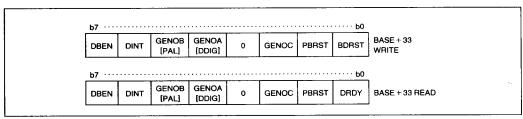

Figure 2-11. General Control Register

The General Control Register is an 8-bit read/write register located at BASE + 33 hex. Bit 0 changes definition depending on whether the register is being read or written. This register is reset to 0 by system reset. Four of the bits in this register are dedicated and three of the bits are General Purpose Output bits which correspond to the output pins of the same names. In the bit definitions shown below the bit names and descriptions show in brackets ([ ]) are examples of some useful functions that these bits can serve in a typical DVI environment. They may, of course, be assigned to any compatible output at the user's discretion.

**DBEN** (Bit 7)—DBEN (82750DB Enable) is used to reset the 82750DB device when it is a zero or to allow the 82750DB to run when it is a one.

**DINT** (Bit 6)—DINT (Disable Interrupt) is used to reassert interrupts at the end of an interrupt routine or to disable all of the interrupts from the DVI Board.

GENOB (Bit 5)—General Purpose Output B.

[PAL (Bit 5)—PAL (PAL/NTSC) selects the PAL Mode when a one, or NTSC Mode when a zero for the Y-C output circuit.]

GENOA (Bit 4)-General Purpose Output A.

[DDIG (Bit 4)—DDIG (Disable 82750DB Digital Outputs) is used to disable the digital video data outputs on the 82750DB device. If the DVI Board uses the analog video data outputs from the 82750DB device, the DDIG bit should be set to a one. The power dissipation of the 82750DB will increase significantly if the DDIG bit is a zero, especially at frequencies above 30 MHz. The 82750DB digital outputs are wired directly to the Ditgital Display Connector when in ATMODE. The DDIG bit must be a zero to enable the use of this connector.]

GENOC (Bit 2)-General Purpose Output C.

PBRST (Bit 1)—PBRST (82750PB Reset) is used to reset the 82750PB device when a one, or to disable it when a zero. The PBRST bit is momentarily set to a one at power on time before being reset and held to a zero, initializing the 82750PB to its reset state. The contents of VRAM cannot be guaranteed after the PBRST bit has been toggled to a one. The PBRST bit, when a one, disables arbitration for the

DVI Bus in the 82750PB device. The only operation that should be attempted when the PBRST bit is a one is the writing of a zero to the PBRST bit.

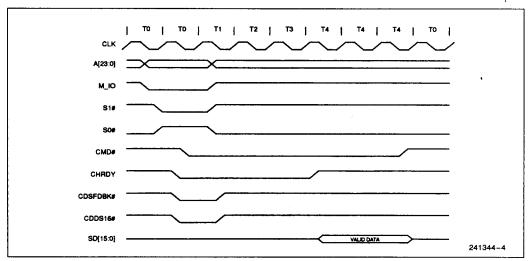

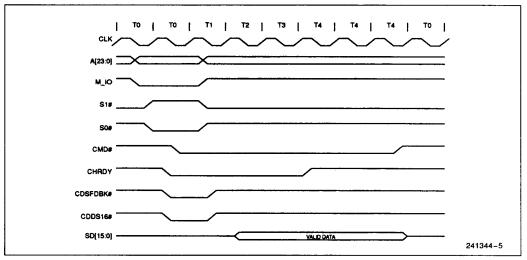

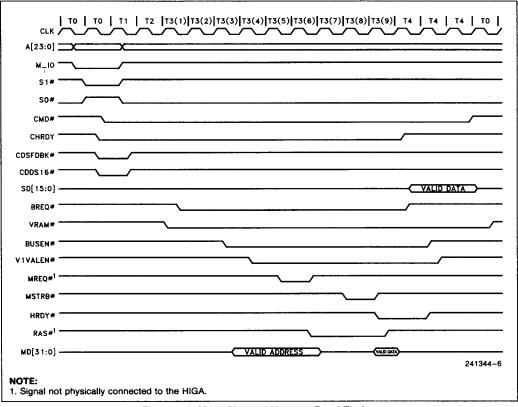

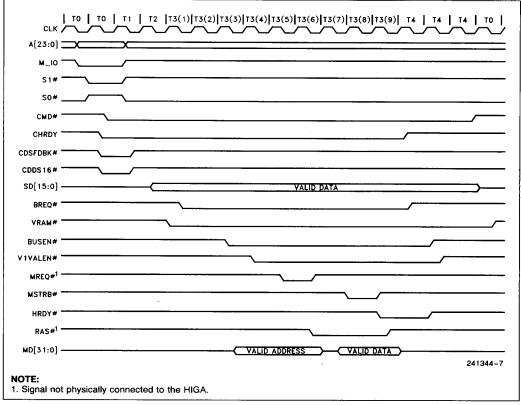

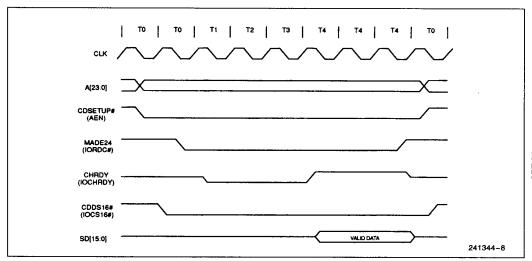

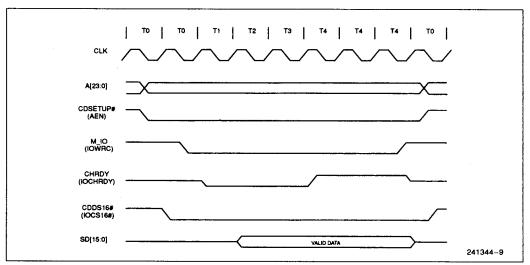

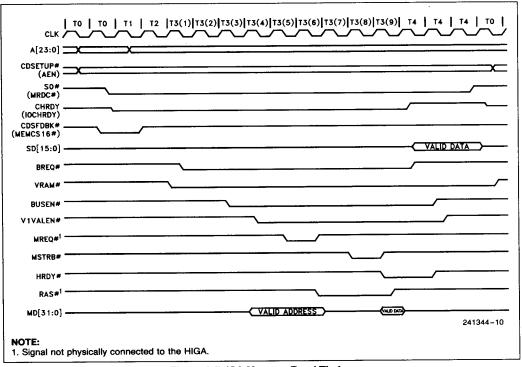

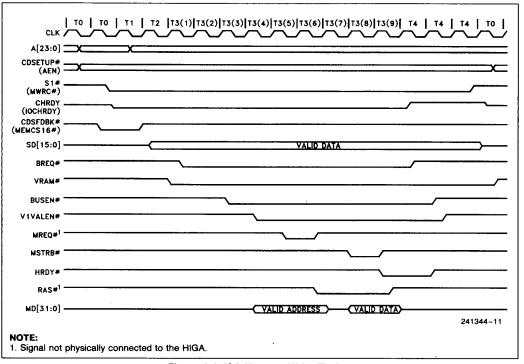

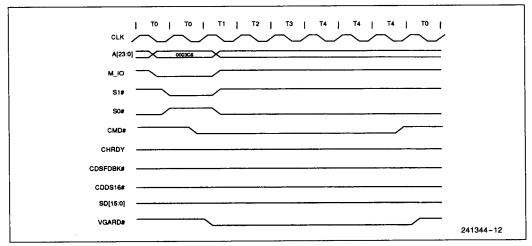

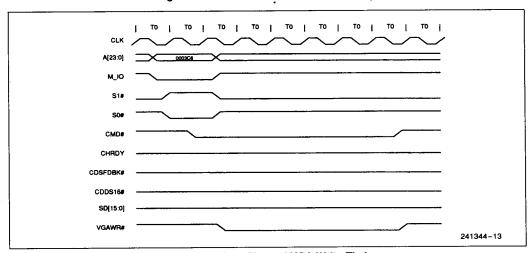

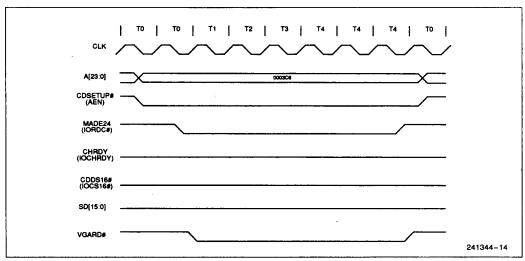

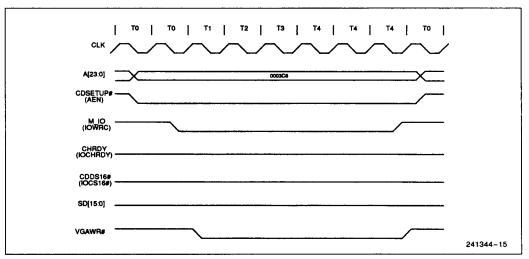

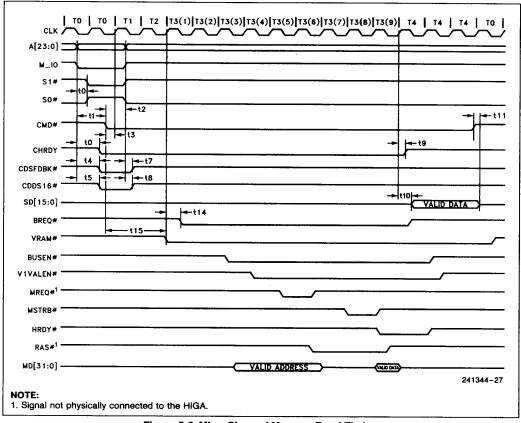

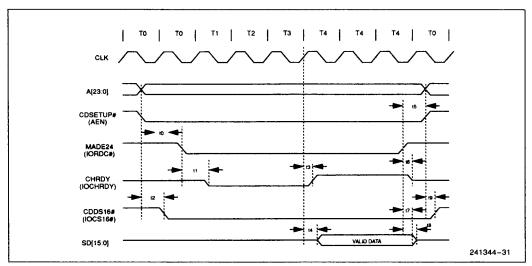

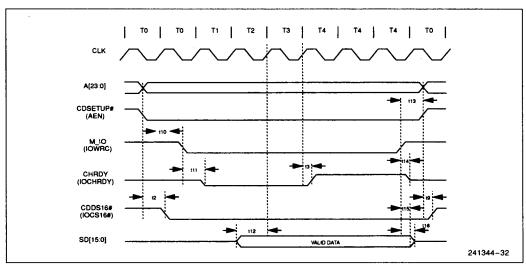

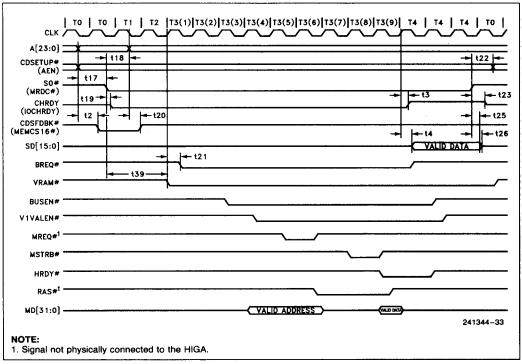

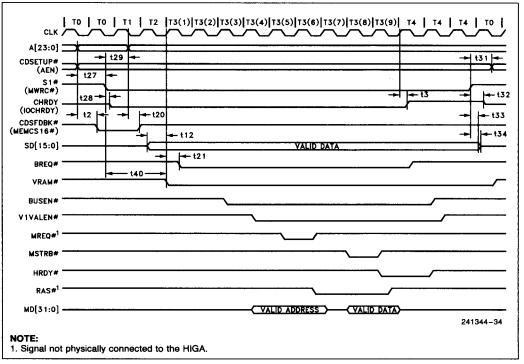

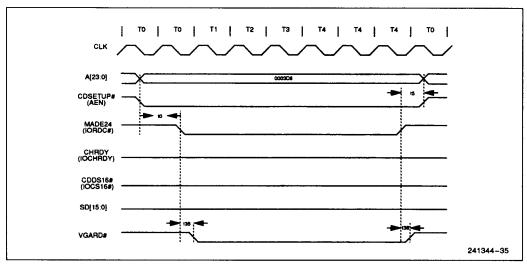

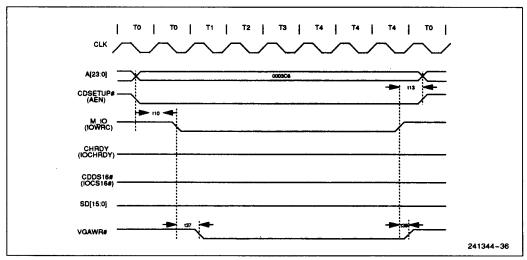

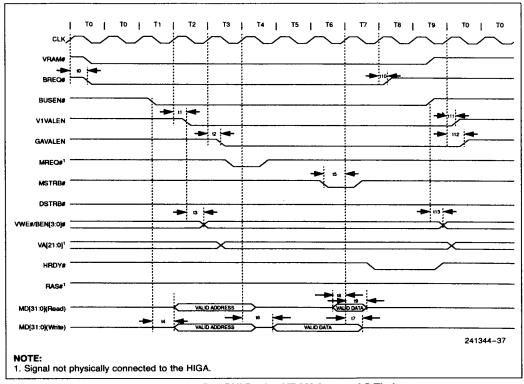

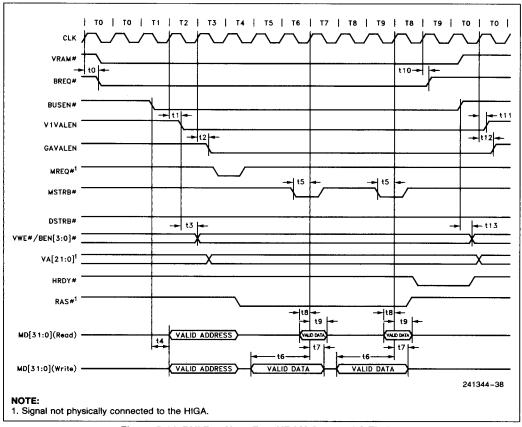

BDRST (Bit 0 Write)-BDRST (Board Reset) is used to reset the entire DVI Board. This reset is so complete that this bit should only be used for debugging purposes. The contents of VRAM cannot be guaranteed after the BDRST bit has been toggled to a one. Setting this bit to a one is the same as a power on reset except that the POS Registers, PAR Registers. 82750PB and the General Control Register itself are not affected. Writing a 03 followed by a 00 to the General Control Register is as complete a reset attainable without powering down. The BDRST bit should be held as a one for at least 10 µs to guarantee a full board reset. Note also that the BDRST bit cannot be read back. The BDRST bit, when a one, disables the DVI Bus. The only operation that should be attempted when the BDRST bit is a one is the writing of a zero to the BDRST bit. In normal operation, the General Control Register should either be 90 hex or B0 hex.