Step-UpConverter with Low I<sub>Q</sub>, 1.1A Switching Current,Output Disconnect and Battery Detection Feature

## DESCRIPTION

The MP3416 is a low quiescent current, step-up converterthat uses peak-currentcontrol and variable frequency architecture to regulate the output voltage. The MP3416 can work with an input voltage as low as 0.86Vto provide an output voltage from 1.8V to 5.5V.

The MP3416 works in peak-current-control modeand provides good transient response. The integrated P-channel synchronous rectifier improves efficiency and eliminates the need for an external Schottky diode.

In light-load condition, the peak current declines to about 350mA, and the device enters pulseskip mode to save power loss. When the MP3416 shuts down, the output is disconnected from the input, allowing the output to draw less than  $0.65\mu$ A in shutdown mode.

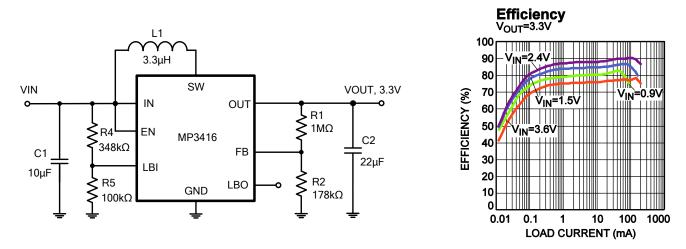

The MP3416 is available in 8-pin TSOT23 and 8-pin QFN (1.5mmx2.0mm) packages.

## FEATURES

- Input Voltage Range: 0.86V to 5.5V

- Start-Up Voltage Range:1.25V to 5.5V

- Output Voltage Range: 1.8V to 5.5V

- 9.5µA Quiescent Current

- <650nA Shutdown Current</li>

- Up to 80% Efficiency at 100µA-200µA Light-Load Condition

- Output Disconnect in Shutdown

- DownMode When VIN> VOUT

- Adjustable Low Battery Detection

- Internal Synchronous Rectifier

- Over-Temperature Protection(OTP) withThermal Shutdown at 155°C

- Available in TSOT23-8 and QFN-8 (1.5mmx2.0mm) Packages

## APPLICATIONS

- Medical Devices

- Digital Retail Displays

- Gaming Controllers

- Remote Controllers

- Battery-Powered Products

- Handheld Computers and Smart Phones

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

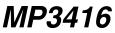

# TYPICAL APPLICATION

MP3416 Rev.1.0 12/14/2016

## **ORDERING INFORMATION**

| Part Number | Package             | Top Marking |

|-------------|---------------------|-------------|

| MP3416GJ*   | TSOT23-8            | See Below   |

| MP3416GQH** | QFN-8 (1.5mmx2.0mm) | See Below   |

\* For Tape & Reel, add suffix-Z(e.g. MP3416GJ-Z) \*\* For Tape & Reel, add suffix-Z(e.g. MP3416GQH-Z)

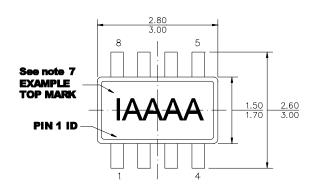

## **TOP MARKING (MP3416GJ)**

## |AHTY

AHT: Product code of MP3416GJ Y: Year code

## **TOP MARKING (MP3416GQH)**

FK

LL

FK: Product code of MP3416GQH LL:Lot number

## PACKAGE REFERENCE

## **ABSOLUTE MAXIMUM RATINGS (1)**

| SW0.3V to+6.5V (<br>All other pins                     |                |

|--------------------------------------------------------|----------------|

| Continuous power dissipation(T <sub>A</sub> = TSOT23-8 | ,              |

| QFN-8<br>Junction temperature<br>Lead temperature      | 1.14W<br>150°C |

| Storage temperature                                    |                |

### Recommended Operating Conditions <sup>(3)</sup>

| Start-upvoltage (Vst) | 1.25V to 5.5V                       |

|-----------------------|-------------------------------------|

|                       | <sub>N</sub> ) 0.86V to 5.5V        |

| V <sub>OUT</sub>      | 1.8V to 5.5V                        |

| Operating junctionte  | mp. (T <sub>J</sub> )40°C to +125°C |

#### Thermal Resistance <sup>(4)</sup> θ<sub>JA</sub> θ<sub>JC</sub> TSOT23-8 100 55 °C/W

|                     | 100       |

|---------------------|-----------|

| QFN-8 (1.5mmx2.0mm) | 11055°C/W |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J (MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$ =  $V_{EN}$ =1.8V,  $V_{OUT}$  = 3.3V,  $T_{J}$ = -40°C to +125°C,typical value is tested at  $T_{J}$ = +25°C. The limit over temperature is guaranteed by characterization unless otherwise noted.

| Parameters                                 | Symbol               | Condition                                                                                                                                               | Min  | Тур  | Max  | Units    |

|--------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|----------|

| Input Voltage                              | L.                   |                                                                                                                                                         |      | 1    |      | <u> </u> |

| Minimum start-up voltage                   | Vst                  | R <sub>LOAD</sub> =1000Ω, T <sub>J</sub> =25°C                                                                                                          |      | 1.1  | 1.25 | V        |

| Operating input voltage                    | VIN                  |                                                                                                                                                         | 0.86 |      | 5.5  | V        |

| VIN off under-voltage lockout              | VUVLO                | V <sub>IN</sub> falling                                                                                                                                 |      | 0.7  | 0.86 | V        |

| Output Voltage                             | 1                    | · · · · · ·                                                                                                                                             |      |      |      |          |

|                                            |                      | T <sub>J</sub> =25°C                                                                                                                                    | 494  | 504  | 514  | mV       |

| Feedback voltage                           | VFB                  | $T_{J} = -40^{\circ}C$ to 125°C                                                                                                                         | 491  | 504  | 517  | mV       |

| Feedback input current                     | I <sub>FB</sub>      | V <sub>FB</sub> =0.55V                                                                                                                                  |      | 10   | 70   | nA       |

| Operation Current                          |                      |                                                                                                                                                         |      |      |      |          |

| Quieseent eurreent                         |                      | $\label{eq:VEN} \begin{array}{ll} V_{\text{EN}}{=}V_{\text{IN}}{=}1.8V, & V_{\text{OUT}}{=}3.3V, & \text{no} \\ \text{load,measured on IN} \end{array}$ |      | 0.65 | 1.1  | μA       |

| Quiescent current                          | lα                   | $V_{\text{EN}}=V_{\text{IN}}=1.8V, V_{\text{OUT}}=3.3V,$ no load, measured on OUT                                                                       |      | 9.5  | 12   | μA       |

| Shutdown current                           | Isd                  | V <sub>EN</sub> =V <sub>OUT</sub> =0V, measured on IN                                                                                                   |      | 360  | 650  | nA       |

| Switch MOSFET                              |                      |                                                                                                                                                         |      |      |      |          |

| NMOS on-resistance                         | R <sub>N_ON</sub>    |                                                                                                                                                         |      | 100  |      | mΩ       |

| PMOS on-resistance                         | <b>R</b> P_ON        |                                                                                                                                                         |      | 800  |      | mΩ       |

| NMOC ourrent limit                         | Isw_limit            | T <sub>J</sub> =25°C, duty=50%                                                                                                                          | 900  | 1100 | 1300 | mA       |

| NMOS current limit                         |                      | $T_{J} = -40^{\circ}C$ to 125°C, duty=50%                                                                                                               | 790  | 1100 | 1410 | mA       |

| NMOS max on period                         | T <sub>ON_MAX</sub>  |                                                                                                                                                         |      | 10   |      | μs       |

| EN Control                                 |                      |                                                                                                                                                         |      |      |      |          |

| EN input high level                        | V <sub>EN_H</sub>    |                                                                                                                                                         | 0.7  |      |      | V        |

| EN input low level                         | $V_{\text{EN}_{L}}$  |                                                                                                                                                         |      |      | 0.2  | V        |

| EN input current                           | I <sub>EN</sub>      | Connect to V <sub>IN</sub>                                                                                                                              |      |      | 100  | nA       |

| LBI Detection                              |                      |                                                                                                                                                         |      |      |      |          |

| Low battery threshold                      | VLBI                 | Falling edge                                                                                                                                            |      | 0.4  |      | V        |

| LBI hysteresis                             | V <sub>LBI-HYS</sub> |                                                                                                                                                         |      | 70   |      | mV       |

| LBI input leakage current                  | I <sub>LBI</sub>     | Connect to V <sub>IN</sub>                                                                                                                              |      |      | 100  | nA       |

| LBO low voltage level                      | VLBO                 | ILBO =1mA                                                                                                                                               |      | 20   | 50   | mV       |

| LBO input leakage current                  | I <sub>LBO</sub>     | Connect to VOUT, LBO logic high                                                                                                                         |      |      | 100  | nA       |

| Thermal Protection                         |                      |                                                                                                                                                         |      |      |      |          |

| Thermal shutdown <sup>(5)</sup>            |                      |                                                                                                                                                         |      | 155  |      | °C       |

| Thermal shutdown hysteresis <sup>(5)</sup> |                      |                                                                                                                                                         |      | 20   |      | °C       |

NOTE:

5) Guaranteed by characterization, not production tested.

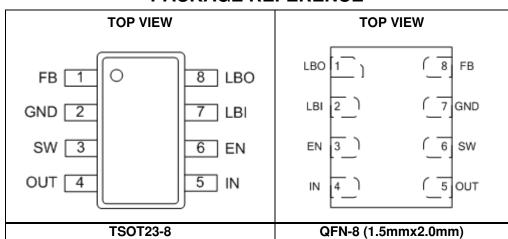

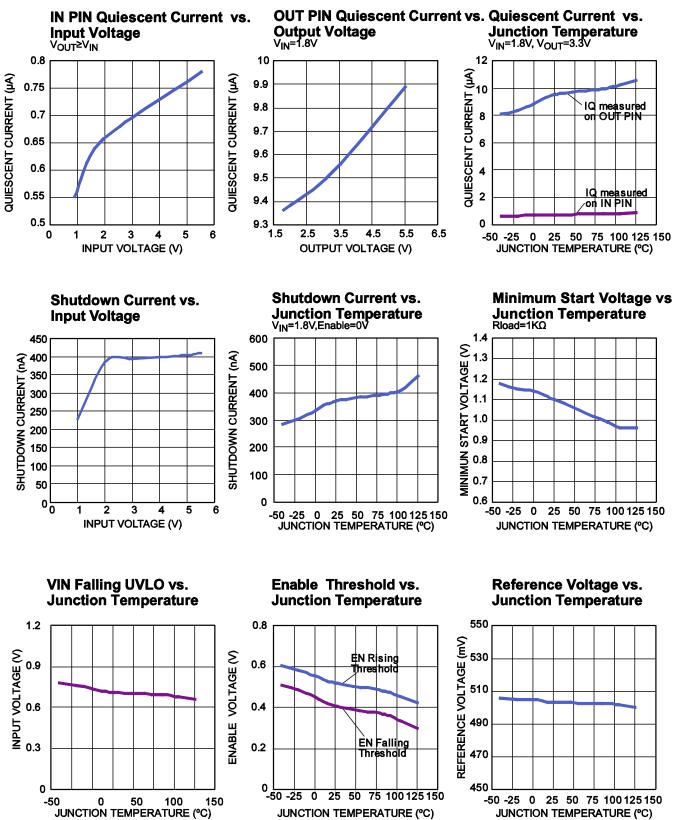

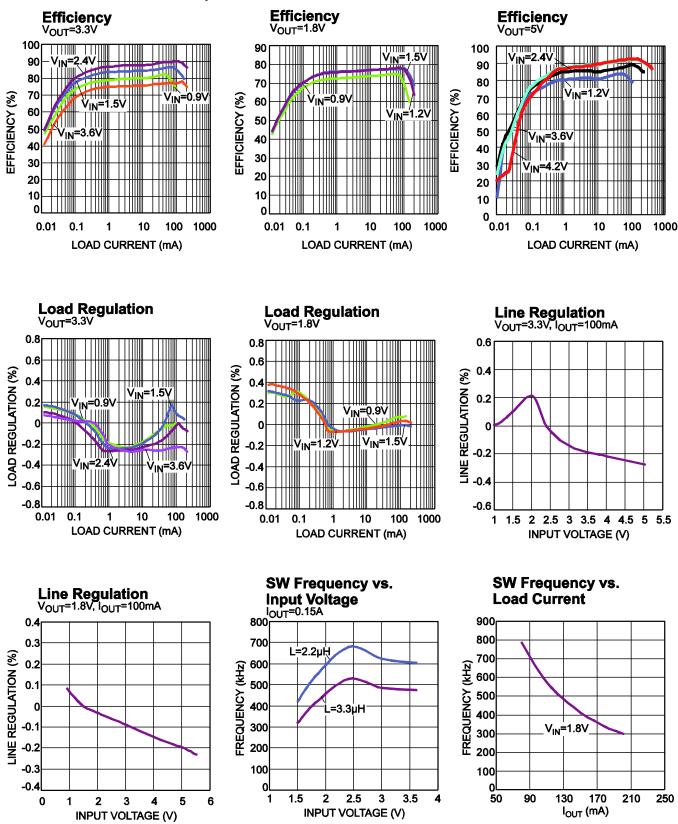

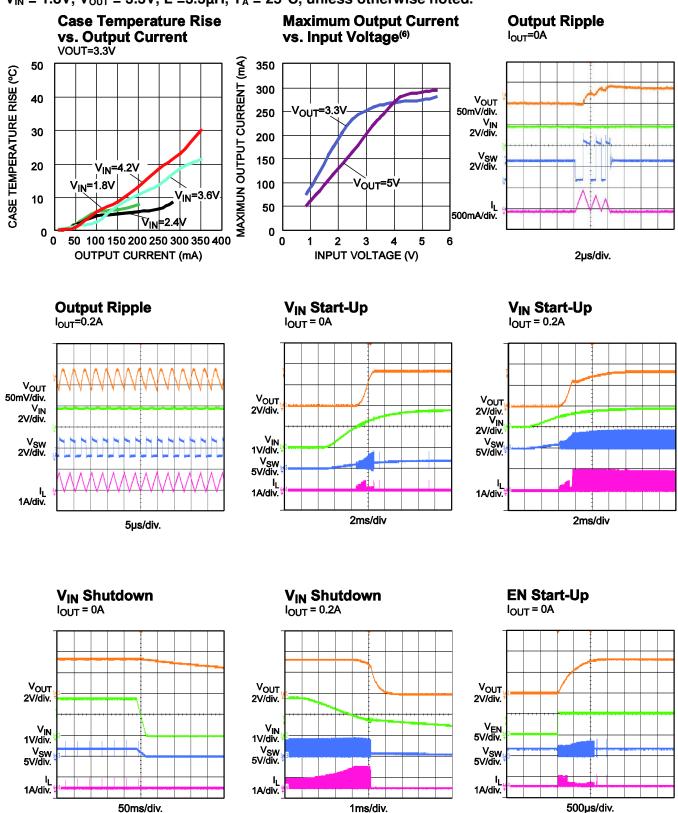

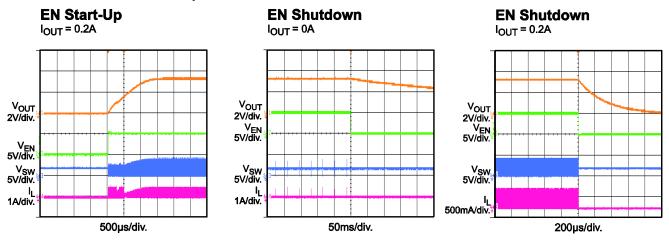

## **TYPICAL CHARACTERISTICS**

$V_{IN}$  = 1.8V,  $V_{OUT}$  = 3.3V, L = 3.3µH, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

#### $V_{IN} = 1.8V$ , $V_{OUT} = 3.3V$ , L = $3.3\mu$ H, T<sub>A</sub> = $25^{\circ}$ C, unless otherwise noted. **Current Limit vs. Duty Cycle Current Limit vs.** FBI Falling Threshold & **Junction Temperature** Hysteresis Voltage vs. **Junction Temperature** 1.4 0.45 1.4 త 0.4 CURRENT LIMIT (A) 1.1 1 1 1 1.3 FBI Falling Threshold Voltage CURRENT LIMIT (A) 1.2 1.1 1 FBI HysteresVoltage 0.9 0.9 0.8 0.8\_50 -25 0 25 50 75 100 125 150 0 0 10 20 30 40 50 60 70 80 -50 0 50 100 150 DUTY CYCLE (%) JUNCTION TEMPERATURE(°C) JUNCTION TEMPERATURE(°C)

## TYPICAL CHARACTERISTICS(continued)

## **TYPICAL PERFORMANCE CHARACTERISTICS**

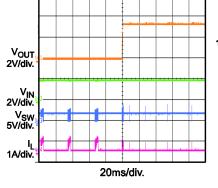

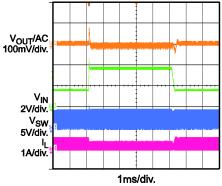

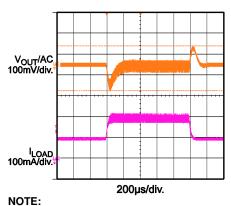

$V_{\text{IN}}$  = 1.8V,  $V_{\text{OUT}}$  = 3.3V, L =3.3  $\mu\text{H},$  T\_A = 25 °C, unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS**(continued)

$V_{IN} = 1.8V$ ,  $V_{OUT} = 3.3V$ , L =3.3 $\mu$ H, T<sub>A</sub> = 25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

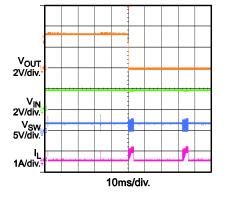

## **TYPICAL PERFORMANCE CHARACTERISTICS**(continued)

$V_{IN} = 1.8V$ ,  $V_{OUT} = 3.3V$ , L =3.3 $\mu$ H, T<sub>A</sub> = 25°C, unless otherwise noted.

**SCP Enter**

**SCP Recover**

Line Transient V<sub>IN</sub> = 1.8V to 3.6V, I<sub>OUT</sub> = 0.1A

6) Tested under a 0.79A switching current limit. The test schematic is the same as Figure 5 when VOUT is 3.3V and the same as Figure 6 when VOUT is 5V.

## **PIN FUNCTIONS**

| Pin #<br>TSOT23-8 | Pin #<br>QFN-8 | Name | Description                                                                                                                                                                                                                                                                                |  |

|-------------------|----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1                 | 8              | FB   | Feedback input for the error amplifier.Connect the resistor divider tap to FB.                                                                                                                                                                                                             |  |

| 2                 | 7              | GND  | Ground.GND is the reference ground of the regulated output voltage.                                                                                                                                                                                                                        |  |

| 3                 | 6              | SW   | <b>Output switch node.</b> Connect the inductor to SW to complete the step-up converter.                                                                                                                                                                                                   |  |

| 4                 | 5              | OUT  | <b>Output node.</b> OUT is the source of the internal synchronous rectifier. Place the putput capacitor between OUT and GND.                                                                                                                                                               |  |

| 5                 | 4              | IN   | Input supply. INrequires a bypass capacitor.                                                                                                                                                                                                                                               |  |

| 6                 | 3              | EN   | <b>Enable input.</b> ENturns the regulator on or off. Logic high (>0.7V) turns on the regulator; logic low(<0.2V) turns off the regulator. It is not recommended to leave EN floating.                                                                                                     |  |

| 7                 | 2              | LBI  | <b>Low battery detection input.</b> Do not leave LBI floating. Connect LBI to VII through a resistor divider to detect a low battery condition. The divided LE voltage should be higher than 0.2V during application.Pull LBI up to V <sub>IN</sub> if the LE function is not used.        |  |

| 8                 | 1              | LBO  | <b>Low battery detection output.</b> The output of LBOis an open-drain signal. LBO requires a pull-up resistor to a DC voltage to indicate high if the input voltage is higher than the threshold of the low battery detection voltage. LBO maintains a high impedance when the IC is off. |  |

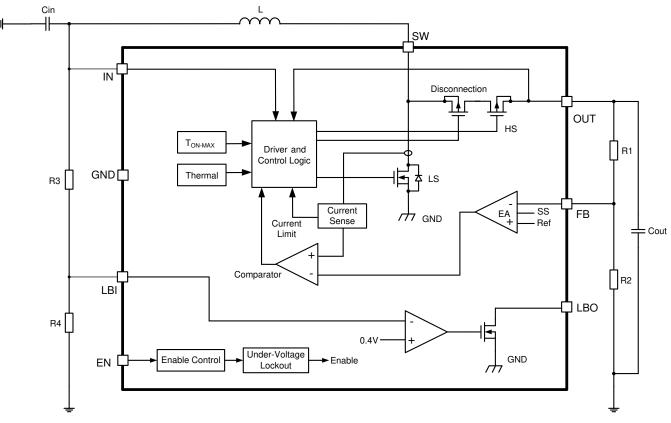

## **BLOCKDIAGRAM**

Figure 1: Functional Block Diagram

## OPERATION

The MP3416 is a peak-currentmode, step-up converter in a compact TSOT23-8 or QFN-8 package with true output disconnect. The MP3416 can operate at input voltages as low as 0.86Vand features peak current and boundary conduction mode (BCM) control for exceptional line and load regulation. Internal softstart and loop compensation simplify the design process and minimize external components. The internal lowR<sub>DS(ON)</sub> MOSFETs combined with power-save mode (PSM) operation enable the device to maintain high efficiency over a wide currentload range.

### **PWM Operation**

The MP3416 utilizes a peak-currentcontrol scheme. The output voltage is monitored by FB,which is connected to the internal error amplifier (EA).The error amplifier compares the feedback voltage and reference voltage, and the EA output voltage controls the peak-inductor current.

At the beginning of each cycle, the low-side MOSFET (LS-FET) turns on, the inductor current rises up to the peak current which is decided by the EA output, and then the LS-FET turns off, and the high-side MOSFET (HS-FET) turns on. The inductor current charges the output capacitor while the HS-FET is on. After the inductor current reduces to zero, the LS-FET initiates one new cycle to raise the inductor current.

Inlight load, the EA output drops and limits the peak inductor current at about 350mA.lf the EA output voltage continues decreasing due to a high V<sub>OUT</sub>, the LS-FET locks and does not turn on again until the EA output rises up to a 350mA peak inductor current. This allows the device to work in PSM smoothly to achieve high efficiency in light-load condition. While the load current increases and transfers more energy to the output.

#### Down Mode (V<sub>IN</sub>>V<sub>OUT</sub>)

The MP3416 integrates one disconnection MOSFET (DIS-FET) for down-mode condition. When V<sub>IN</sub> is lower than V<sub>OUT</sub>-0.2V, the DIS-FET is on and does not differ from a normal converter's operation. While V<sub>IN</sub> rises higher, the gate of the DIS-FET is connected to a voltage level of V<sub>IN</sub>-0.4V. In this condition, the SW voltage is charged high by the inductor current. The DIS-FET no longer acts as a low-impedance path, but only turns on when the SW voltage is charged high by the inductor current. If the inductor current is zero, the SW voltage is equal to V<sub>IN</sub>, so the DIS-FET does not turn on. In shutdown, the LS-FET never turns on to setup the inductor current, so the DIS-FET can disconnect the output terminal from the input to prevent battery discharge.

#### Start-Up

There are three steps for start-up. Firstly, after the input voltage rises up to the minimum startup voltage, the MP3416 enters open-loop work mode. In this mode, the switching ontime is constant, and the output voltage is charged high by increasing the switching frequency. When V<sub>OUT</sub>rises to about 1.7V, the MP3416 switches to close-loop work mode with soft-start control. In this second stage, the inductor peak current is controlled by the internal COMP voltage (V<sub>COMP</sub>), and the minimum peak current is not limited, so the switching frequency may be high, and the rising output voltage has a very small voltage ripple. Finally, when the output voltage is close to its set value, the MP3416 enters BCM close-loop mode, whilethe minimum peak inductor current is limited above 350mA.Due to the 350mA minimum peak current, the MP3416 may enter pulse-skipmode in steady state if the load is light. The loop is powered by the input before V<sub>OUT</sub>rises up to 1.7V. It is then powered by the output after  $V_{OUT}$  is higher than 1.7V.

### Enable Control (EN)

The device operates when EN is high (>0.7V). In shutdown mode with a low EN voltage, the regulator stops switching and halts all internal control circuitry, and the DIS-FET turns off as well. This isolates the load from the input, so the output voltage can drop below the input voltage during shutdown.

#### **Current Limit**

The MP3416 usescurrent limit to prevent aninductor current runaway. If the inductor current triggersthe current limit, the LS-FET is turned off immediately. When the load current increases, the inductor current triggersthe limit level and limits the output energy. To prevent the LS-FET from running away, the max turn on time is limited to 10µs.

#### **Short-Circuit and Overload Protection**

Unlike most step-up converters, the MP3416 allows for short circuits on the output. In the event of a short circuit, the MP3416 enters hiccup protection. During an overload,  $V_{OUT}$  may drop to about 1.6V.If the load continues increasing, the MP3416 enters hiccup protection. If overload is defined as  $V_{OUT}$  higher than 1.6V but still smaller than  $V_{IN}$ +0.2V,the MP3416 treatsthis as down mode operation with current limit. The internal temperature of the MP3416 may rise, causing the device to enter OTP.

#### Low Battery Detection

The MP3416 includes one LBI pin to detect the battery voltage, andthe function is active only when the device is enabled. LBI is connected to  $V_{IN}$  through the external resistor divider. If the LBI voltage is lower than 0.4V, LBO goes low to indicate the power failure. During application, the LBI voltage should always be higher than 0.2V;otherwise, the LBO function may indicate falsely.

#### **Thermal Protection**

The device has an internal temperature monitor. If the die temperature exceeds 155°C, the part stop working and restartswhen the die temperature drops below 135°C.

## **APPLICATION INFORMATION**

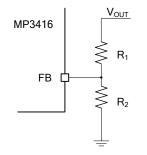

#### Setting the Output Voltage

The external resistor divider sets the output voltage (see the Typical Application schematic on page 1). The feedback resistor ( $R_1$ ) must account for both stability and dynamic response and should therefore be chosen carefully. Choose  $R_1$ , and then calculate  $R_2$  with Equation (1):

$$R_2 = \frac{V_{FB}}{V_{OUT} - V_{FB}} \times R_1$$

(1)

Where V<sub>FB</sub>=0.504V.

The feedback circuit is shown in Figure 2.

Figure 2: Feedback Network

Table 1 lists the recommended resistor values for common output voltages.

Table 1: Resistor Values for Common Output Voltages

|                      | •                   |        |

|----------------------|---------------------|--------|

| V <sub>OUT</sub> (V) | R <sub>1</sub> (kΩ) | R₂(kΩ) |

| 1.8                  | 1000                | 383    |

| 3                    | 1000                | 200    |

| 3.3                  | 1000                | 178    |

| 5                    | 1000                | 113    |

#### Input Capacitor Selection

Low ESR input capacitors reduce input switching noise and peak current drawn from the battery. Ceramic capacitors are recommended for input decoupling and should be located as close to the deviceas possible. A ceramic capacitor  $10\mu$ F or larger is recommended to restrain the V<sub>IN</sub> ripple.

#### Inductor Selection

The MP3416 can apply small surface-mounted chip inductors due to the 1.1A peak current. Because of the peak current and boundary conduction mode (BCM) control method, the values of the inductance affect the switching frequency. A larger inductance causes lower switching frequency and increases output ripple.A smaller inductance causes higher switching frequency and decreases efficiency.

Considering the efficiency and output ripple, a  $1.5\mu$ H to  $3.3\mu$ H inductor is recommended for most applications.

The inductor should have a low DCR to reduce resistive power loss. The saturated current  $(I_{SAT})$  should be large enough to support the peak current.

#### **Output Capacitor Selection**

The output capacitor requires a minimum capacitance value of  $22\mu$ F at the programmed output voltage to ensure stability over the full operating range. A higher capacitance value may be required to lower the output ripple and transient response. Low ESR capacitors such as X5R or X7R type ceramic capacitors are recommended. Supposing that ESR is zero, the minimum output capacitor to support the ripple in the boost mode can be calculated with Equation (2):

$$C_{o} \geq \frac{I_{o} \times (V_{OUT(MAX)} - V_{IN(MIN)})}{V_{OUT(MAX)} \times \Delta V \times f_{S(MIN)}}$$

(2)

Where  $V_{OUT(MAX)}$  is the maximum output voltage,  $V_{IN(MIN)}$  is the minimum input voltage,  $I_O$  is the output current,  $f_{S(MIN)}$  is the minimum switching frequency, and  $\Delta V$  is the acceptable output ripple.

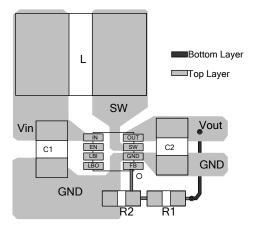

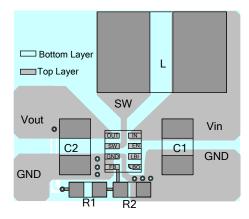

#### **PCB Layout Considerations**

Efficient PCB layout is critical for switching power supplies with a high switching frequency. A poor layout can result in reduced performance, EMI problems, resistive loss, and system instability. For best results, refer to Figure 3 and Figure 4 and follow the guidelines below.

- 1) Place the output capacitor as close to OUT and GND as possible.

- 2) Place the input capacitor and inductor close to the IC.

- 3) Keep the SW trace as short and wide as possible.

- 4) Keep the feedback loop far away from noise sources, such as the SW trace.

- 5) Keep the feedback divider resistor as close to FB and GND as possible.

- 6) Tie the ground return of the input/output capacitor close to GND witha large GND copper area.

- 7) Add GND and vias on the bottom layer if the top layer GND connection between CIN, COUT, and IC-GND is narrow.

Figure 3:Recommended TSOT23 Layout

Figure 4:Recommended QFN Layout

#### Design Example

Table 2is a design example following the application guidelines for the following specifications.

|                  | •                      |

|------------------|------------------------|

| VIN              | 1.25V to 5.5 V         |

| Vout             | 3.3V                   |

| Ι <sub>ουτ</sub> | 0A-0.1A <sup>(7)</sup> |

|                  |                        |

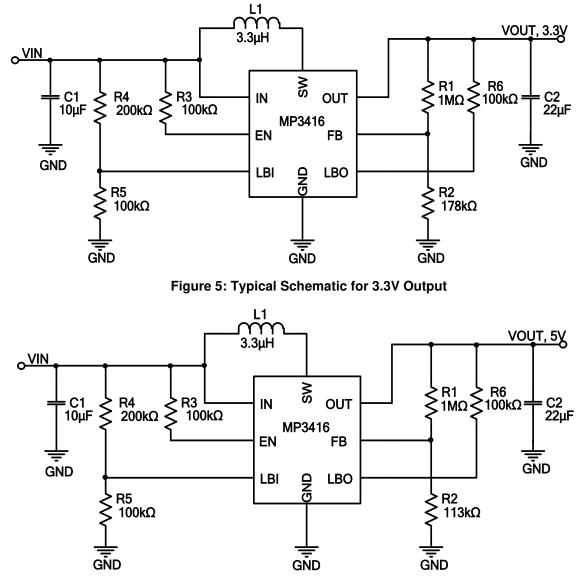

The typical application circuit for  $V_{OUT} = 3.3V$  in Figure 5 shows the detailed application schematic and is the basis for the typical performance waveforms. For more detailed device applications, please refer to the related evaluation board datasheets.

#### NOTE:

7) the load capability is higher when  $V_{IN}$  is relatively high, refer to the Maximum Output Current vs. Input Voltage curveon page 8.

## **TYPICAL APPLICATION CIRCUITS**

Figure 6: Typical Schematic for 5V Output

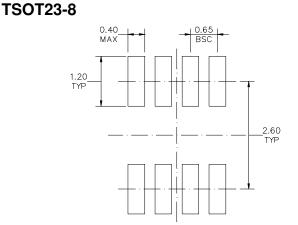

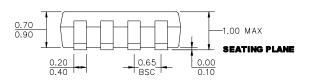

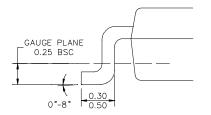

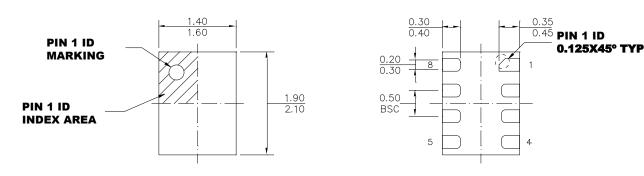

## **PACKAGE INFORMATION**

**TOP VIEW**

#### **RECOMMENDED LAND PATTERN**

**SIDE VIEW**

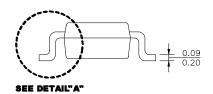

DETAIL "A"

#### NOTE:

1) ALL DIMENSIONS ARE IN MILLIMETERS 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSION OR GATE BURR 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION 4) LEAD COPLANARITY(BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX. 5) JEDEC REFERENCE IS MO193, VARIATION BA 6) DRAWING IS NOT TO SCALE 7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP

7) PIN 1 IS LOWER LEFT PIN WHEN READING TOP MARK FROM LEFT TO RIGHT, (SEE EXAMPLE TOP MARK)

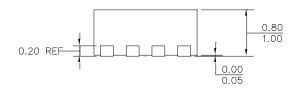

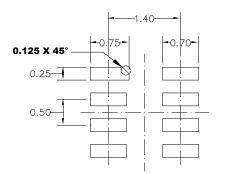

## PACKAGE INFORMATION(continued)

QFN-8 (1.5mmx2.0mm)

TOP VIEW

SIDE VIEW

## RECOMMENDED LAND PATTERN

**BOTTOM VIEW**

ALL DIMENSIONS ARE IN MILLIMETERS.

EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

LEAD COPLANARITY SHALL BE 0.10 MILLIMETERS MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

NOTE: