# **PRELIMINARY**

# **Analog Signal Input Class D Amplifier for Piezo Speaker**

### **■ GENERAL DESCRIPTION**

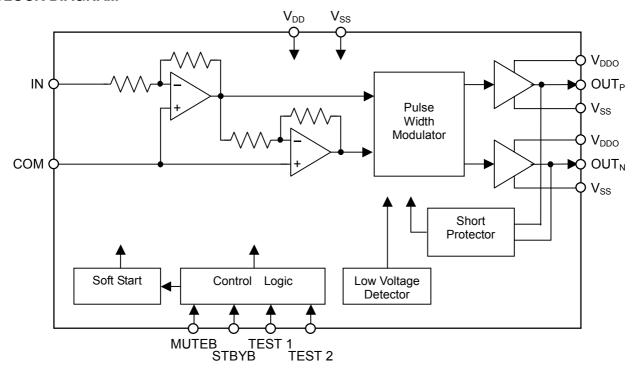

The NJU8752/NJU8752B is an analog signal input monaural class D amplifier for Piezo speaker. The NJU8752/52B includes Inversion operational amplifier input circuit, PWM modulator, an output-short protector and a low voltage detector. Input part operates on 3.3V(TYP) as power supply and Output part operates up to 16.0V(MAX). Therefore, it drives Piezo speaker with louder sound and High efficiency.

The **NJU8752/52B** incorporates BTL amplifier, which eliminate AC coupling capacitors, capable of driving Piezo speaker with simple external LC low-pass filters.

Class D operation achieves lower power operation for Piezo speaker, thus the **NJU8752/52B** is suited for battery powered applications.

### **■ FEATURES**

- Piezo Speaker Driving

- 1-channel Analog Signal Input, 1-channel BTL Output

- Standby(Hi-Z), Mute Control

- Voltage Gain 31dB(NJU8752) 20dB(NJU8752B)

- Built-in Low Voltage Detector

- Built-in Short Protector

- Operating Voltage Input: 2.7 ~ 3.6V (NJU8752)

3.1 ~ 3.6V (NJU8752B)

Output: 6.0 ~ 16.0V

C-MOS Technology

Package Outline SSOP14 (NJU8752 / 52B)

QFN20 / QFN28 (NJU8752B)

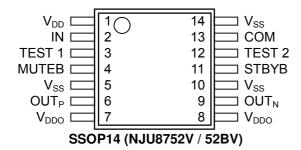

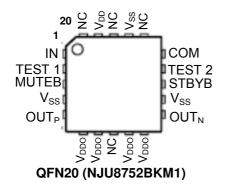

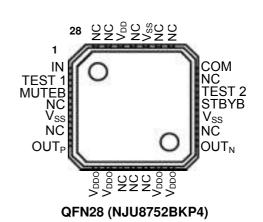

# **■ PIN CONFIGURATION**

### **■ PACKAGE OUTLINE**

NJU8752V / 52BV

NJU8752BKM1

# **■ BLOCK DIAGRAM**

### **■ PIN DESCRIPTION**

| No.     |            |                                                  | SYMBOL    | I/O | Function                                           |  |  |

|---------|------------|--------------------------------------------------|-----------|-----|----------------------------------------------------|--|--|

| SSOP14  | QFN20      | QFN28                                            | STINIDOL  | 1/0 |                                                    |  |  |

| 1       | 19         | 26                                               | $V_{DD}$  | _   | Power Supply: V <sub>DD</sub> =3.3V                |  |  |

| 2       | 1          | 1                                                | IN        | I   | Signal Input                                       |  |  |

| 3       | 2          | 2                                                | TEST 1    | I   | Maker test 1                                       |  |  |

|         |            |                                                  |           |     | This pin must be connected to GND.                 |  |  |

| 4       | 3          | 3                                                | MUTEB     | I   | Mute Control                                       |  |  |

|         |            |                                                  |           |     | Low : Mute ON High : Mute OFF                      |  |  |

| 5,10,14 | 4,12,17    | 5,17,24                                          | $V_{SS}$  | _   | Power GND: V <sub>SS</sub> =0V                     |  |  |

| 6       | 5          | 7                                                | $OUT_P$   | 0   | Positive Output                                    |  |  |

| 7,8     | 6,7,9,10   | 8,9,13,14                                        | $V_{DDO}$ | _   | Output Power Supply : V <sub>DDO</sub> =16.0V max. |  |  |

| 9       | 11         | 15                                               | $OUT_N$   | 0   | Negative Output                                    |  |  |

| 11      | 13         | 18                                               | STBYB     | I   | Standby Control                                    |  |  |

| 11      |            |                                                  |           |     | Low : Standby ON High : Standby OFF                |  |  |

| 12      | 14         | 19                                               | TEST 2    | I   | Maker test 2                                       |  |  |

| 12      |            |                                                  |           |     | This pin must be connected to GND.                 |  |  |

| 13      | 15         | 21                                               | COM       | _   | Analog common                                      |  |  |

| -       | 8,16,18,20 | ,18,20 4,6,10,11,<br>12,16,20,22,<br>23,25,27,28 | NC        | -   | Non connection                                     |  |  |

|         |            |                                                  |           |     |                                                    |  |  |

<sup>\*</sup>V<sub>SS</sub>(SSOP14:Pin No.5,10,14, QFN20:Pin No.4,12,17, QFN28:Pin No.5,17,24) should be connected at a nearest point to the IC.

$<sup>^*</sup>V_{DDO}(SSOP14:Pin No.7,8, QFN20:Pin No.6,7,9,10, QFN28:Pin No.8,9,13,14)$  should be connected at a nearest point to the IC.

<sup>\*</sup>MUTEB(SSOP14: Pin No.4, QFN20, QFN28:Pin No.3) and STBYB(SSOP14:Pin No.11, QFN20:Pin No.13, QFN28:Pin No.18) must be connected to  $V_{DD}$ , when these pins are not used.

### **■ FUNCTIONAL DESCRIPTION**

### (1) Signal Output

The  $OUT_P$  and  $OUT_N$  generate PWM output signals, which will be converted to analog signal via external 2nd-order or higher LC filter. A switching regulator with a high response against a voltage fluctuation is the best selection for the  $V_{DDO}$ , which are the power supply for output drivers. To obtain better THD performance, the stabilization of the power is required.

### (2) Standby

By setting the STBYB pin to "L", the standby mode is enabled. In the standby mode, the entire functions of the **NJU8752/52B** enter a low-power state, and the output pins (OUT<sub>P</sub> and OUT<sub>N</sub>) are high impedance.

#### (3) Mute

By setting the MUTEB pin to "L", the Mute function is enabled. In the Mute mode, the output pins ( $OUT_P$  and  $OUT_N$ ) output square wave (Duty: 50%).

# (4) Low Voltage Detector

When the power supply voltage drops down to below  $V_{DD}$  (MIN), the internal oscillation is halted for prevention to generate unwanted frequency, and the output pins (OUT<sub>P</sub> and OUT<sub>N</sub>) become in high impedance.

### (5) Short Circuit Protection

The short protector, which protects the **NJU8752/52B** against high short-circuit current, turns off the output driver. After about 5 seconds from the protection, the **NJU8752/52B** returns to normal operation. The short protector functions at the following accidents.

- Short between OUT<sub>P</sub> and OUT<sub>N</sub>

- Short between OUT<sub>P</sub> and V<sub>SS</sub>

- Short between OUT<sub>N</sub> and V<sub>SS</sub>

- Note 1) The detectable current and the period for the protection depend on the power supply voltage and ambient temperature.

- Note 2) The short protector is not effective for a long term short-circuit but for an instantaneous accident. Continuous high-current may cause permanent damage to the **NJU8752/52B**.

# ■ ABSOLUTE MAXIMUM RATINGS

(Ta=25°C)

| PARAMETER             |         | SYMBOL             | RATING                      | UNIT        |

|-----------------------|---------|--------------------|-----------------------------|-------------|

| Supply Volt           | age     | $V_{DD}$ $V_{DDO}$ | -0.3 ~ +4.0<br>-0.3 ~ +18.0 | <b>&gt;</b> |

| Input Volta           | ge      | Vin                | -0.3 ~ V <sub>DD</sub> +0.3 | V           |

| Operating Temperature |         | Topr               | -40 ~ +85                   | °C          |

| Storage Tempe         | erature | Tstg               | -40 ~ +125                  | °C          |

| Power Dissipation     | SSOP14  |                    | 450                         |             |

|                       | QFN20   | $P_{D}$            | 620                         | mW          |

|                       | QFN28   |                    | 640                         |             |

<sup>\*:</sup> Mounted on two-layer board of based on the JEDEC.

- Note 1) All voltage are relative to " $V_{\text{SS}}$  =0V" reference.

- Note 2) The LSI must be used inside of the "Absolute maximum ratings". Otherwise, a stress may cause permanent damage to the LSI.

- Note 3) De-coupling capacitors for  $V_{DD}$ - $V_{SS}$  and  $V_{DDO}$ - $V_{SS}$  should be connected for stable operation.

### **■ ELECTRICAL CHARACTERISTICS**

### -NJU8752-

(Ta=25°C,  $V_{DD}$ =3.3V,  $V_{DDO}$ =12.0V,  $V_{SS}$ =0V,Input Signal=1kHz, Input Signal Level=200mVrms, Frequency Band=20Hz~20kHz, Load Impedance=0.8 $\mu$ F, 2nd-order 34kHz LC Filter(Q=0.75))

| PARAMETER                           | SYMBOL          | CONDITIONS                           | MIN                | TYP  | MAX         | UNIT | Note |

|-------------------------------------|-----------------|--------------------------------------|--------------------|------|-------------|------|------|

| V <sub>DD</sub> Supply Voltage      | $V_{DD}$        |                                      | 2.7                | 3.3  | 3.6         | V    |      |

| V <sub>DDO</sub> Supply Voltage     | $V_{DDO}$       |                                      | 6.0                | 12.0 | 16.0        | V    |      |

| Input Impedance                     | Z <sub>IN</sub> | IN pin                               | -                  | 20   | 1           | kΩ   |      |

| Voltage Gain                        | $A_{V}$         |                                      | -                  | 31   | ı           | dB   |      |

| Output THD                          | THD             | Input Signal Level =200mVrms         | -                  | 0.05 | 0.08        | %    | 4    |

| Maximum Output                      | Vo              | Output THD=10%                       | 7                  | 10   | ı           | Vrms |      |

| S/N                                 | SN              | A weight                             | -                  | 80   | 1           | dB   | 4    |

| Dynamic Range                       | Drange          | A weight                             | -                  | 83   | -           | dB   | 4    |

| Maximum Mute Attenuation            | MAT             |                                      | 90                 | ı    | ı           | dB   |      |

| Operating Current(Stanby)           | I <sub>ST</sub> |                                      | -                  | Ī    | 1           | μΑ   |      |

| Operating Current (No signal input) | I <sub>DD</sub> | No-load operating<br>No Signal Input | 1                  | 3.5  | 10          | mA   |      |

| Input Voltage                       | $V_{IH}$        | MUTEB, STBYB pins                    | 0.7V <sub>DD</sub> | •    | $V_{DD}$    | V    |      |

| Input voitage                       | $V_{IL}$        | MUTEB, STBYB pins                    | 0                  | -    | $0.3V_{DD}$ | V    |      |

| Input Leakage Current               | $I_{LK}$        | MUTEB, STBYB pins                    | -                  | -    | ±1.0        | μΑ   |      |

#### -NJU8752B-

(Ta=25°C,  $V_{DD}$ =3.3V,  $V_{DDO}$ =12.0V,  $V_{SS}$ =0V,Input Signal=1kHz, Input Signal Level=700mVrms, Frequency Band=20Hz~20kHz, Load Impedance=0.8 $\mu$ F, 2nd-order 34kHz LC Filter(Q=0.75))

| PARAMETER                           | SYMBOL          | CONDITIONS                           | MIN         | TYP  | MAX         | UNIT | Note |

|-------------------------------------|-----------------|--------------------------------------|-------------|------|-------------|------|------|

| V <sub>DD</sub> Supply Voltage      | $V_{DD}$        |                                      | 3.1         | 3.3  | 3.6         | V    |      |

| V <sub>DDO</sub> Supply Voltage     | $V_{DDO}$       |                                      | 6.0         | 12.0 | 16.0        | V    |      |

| Input Impedance                     | Z <sub>IN</sub> | IN pin                               | -           | 20   | -           | kΩ   |      |

| Voltage Gain                        | $A_{V}$         |                                      | -           | 20   | ı           | dB   |      |

| Output THD                          | THD             | Input Signal Level =700mVrms         | -           | 0.05 | 0.08        | %    | 4    |

| Maximum Output                      | Vo              | Output THD=10%                       | 7           | 10   | -           | Vrms |      |

| S/N                                 | SN              | A weight                             | -           | 80   | -           | dB   | 4    |

| Dynamic Range                       | Drange          | A weight                             | -           | 83   | -           | dB   | 4    |

| Maximum Mute Attenuation            | MAT             |                                      | -           | 90   | 1           | dB   |      |

| Operating Current(Stanby)           | I <sub>ST</sub> |                                      | -           | -    | 1           | μΑ   |      |

| Operating Current (No signal input) | I <sub>DD</sub> | No-load operating<br>No Signal Input | -           | 3.5  | 10          | mA   |      |

| Input Voltage                       | V <sub>IH</sub> | MUTEB, STBYB pins                    | $0.7V_{DD}$ | -    | $V_{DD}$    | V    |      |

| Input Voltage                       | V <sub>IL</sub> | MUTEB, STBYB pins                    | 0           | -    | $0.3V_{DD}$ | V    |      |

| Input Leakage Current               | $I_{LK}$        | MUTEB, STBYB pins                    | -           | -    | ±1.0        | μΑ   |      |

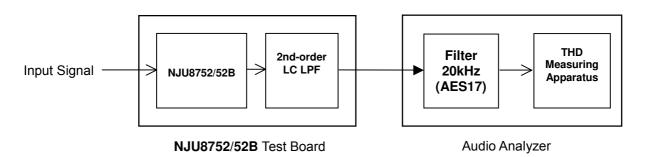

# Note 4) Test system of the output THD, S/N and Dynamic Range

The output THD, S/N and dynamic range are tested in the system shown in Figure 1, where a 2nd-order LC LPF and another filter incorporated in an audio analyzer are used.

Figure 1. Output THD, S/N and Dynamic Range Test System

2nd-order LPF : Refer to "Typical Application Circuit". Filters : 22Hz HPF + 20kHz LPF(AES17)

(with the A-Weight filter for S/N and Dynamic-range tests)

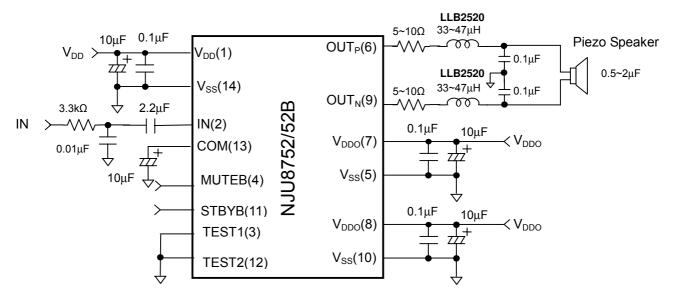

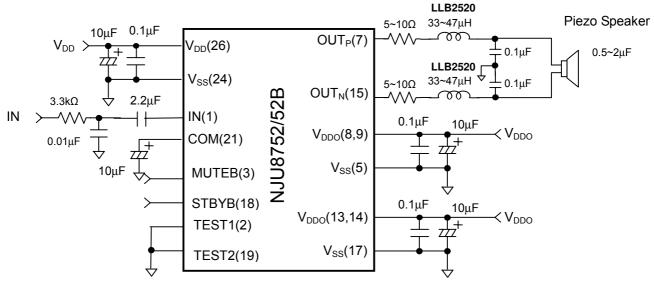

# **■ TYPICAL APPLICATION CIRCUIT**

•LLB2520 is manufactured by TOKO, INC. For detail information, please refer its technical papers.

Figure 2.1 Application Circuit example (SSOP14)

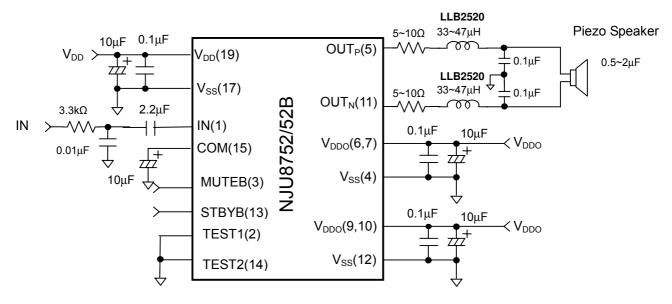

Figure 2.2 Application Circuit example (QFN20)

•LLB2520 is manufactured by TOKO, INC. For detail information, please refer its technical papers.

Figure 2.3 Application Circuit example (QFN28)

- Note 5) De-coupling capacitors must be connected between each power supply pin and GND.

The capacity value should be adjusted on the application circuit and the operation temperature. It may malfunction if capacity value is small.

- Note 6) The power supply for  $V_{DDO}$  require fast driving response performance such as a switching regulator for better THD.

- THD performance becomes worse by ripple if the capacity of De-coupling capacitors is small.

- Note 7) The above circuit shows only application example and does not guarantee the any electrical characteristics. Therefore, please test the circuit carefully to fit your application.

- The cutoff frequency of the LC filter influences the quality of sound.

- The Q factor of the LC filter must be less than "1". Otherwise, the operating current increase when the frequency of input signal is closed to the cutoff frequency.

- Note 8) The transition time for MUTEB and STBYB signals must be less than  $100\mu s$ . Otherwise, a malfunction may be occurred.

- Note 9) (1)-(26) indicates pin number.

#### [CAUTION]

The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.