#### PI6ULS5V9511A

#### Hot Swappable I2C Bus/SMBus Buffer

## Features

- ➔ Bidirectional Buffer for SDA and SCL Lines Increases Fan Out

- ➔ Prevents SDA and SCL Corruption During Live Board Insertion and Removal from Backplane

- → Isolates Input SDA and SCL Lines From Output

- → Compatible with I2C, I2C Fast Mode, and SMBus Standards (up to 400kHz Operation)

- → Built-in Rise-Time Accelerators on all SDA and SCL

- → Wide Supply Voltage Range: 2.7V to 5.5V

- → Active HIGH ENABLE Input

- → Active HIGH READY Open-Drain Output

- → High-Impedance SDA and SCL pins for VCC = 0V

- → 1.1V Pre-Charge on all SDA and SCL Lines

- ➔ Supporting Clock Stretching and Multiple Master Arbitration/Synchronization

- → ESD Protection Exceeds 4000V HBM per JESD22-A114

- ➔ Packages Offered: MSOP-8(U), UDFN-8(ZW), and SOIC-8(W)

- → Totally Lead-Free & Fully RoHS Compliant (Notes 1 & 2)

- → Halogen and Antimony Free. "Green" Device (Note 3)

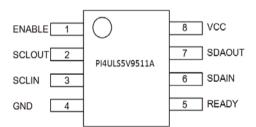

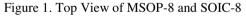

## **Pin Configuration**

Figure 2. Top View of UDFN 2x3-8

### Description

The PI6ULS5V9511A is a hot-swappable I2C-bus and SMBus buffer that allows I/O card insertion into a live backplane without corrupting the data and clock buses. Control circuitry prevents the backplane from connecting to the card until a stop command or bus idle occurs on the backplane without bus contention on the card.

When the connection is made, the PI6ULS5V-9511A provides bidirectional buffering, which keeps the backplane and card capacitances isolated.

The PI6ULS5V9511A rise-time accelerator circuitry allows the use of weaker DC pullup currents while still meeting rise-time requirements. The PI6ULS5V9511A incorporates a digital ENABLE input pin, which enables the device when asserted HIGH and forces the device into a low-current mode when asserted LOW, and an open-drain READY output pin, which indicates that the backplane and card sides are connected together (HIGH) or not (LOW).

During insertion, the PI6ULS5V9511A SDA and SCL lines are pre-charged to 1.1V to minimize the current required to charge the parasitic capacitance of the chip.

| Pin Name | Pin No. | Description                                                                                                                  |

|----------|---------|------------------------------------------------------------------------------------------------------------------------------|

| ENABLE   | 1       | Chip enable.                                                                                                                 |

| SCLOUT   | 2       | Serial clock output to and from the SCL bus on the card                                                                      |

| SCLIN    | 3       | Serial clock input to and from the SCL bus on the backplane                                                                  |

| GND      | 4       | Ground. Connect this pin to a ground plane for best results.                                                                 |

| READY    | 5       | Open-drain output .<br>Goes LOW when SDA/SCL<br>channels are disconnected.<br>Goes HIGH when the two sides<br>are connected. |

| SDAIN    | 6       | Serial data input to and from the SDA bus on the backplane.                                                                  |

| SDAOUT   | 7       | Serial data output to and from the SDA bus on the card.                                                                      |

| VCC      | 8       | Power supply.                                                                                                                |

## Pin Description

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

- 2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

- 3. Halogen- and Antimony-free "Green" products are defined as those which contain <900ppm bromine, <900ppm chlorine (<1500ppm total Br + Cl) and <1000ppm antimony compounds.

A Product Line of Diodes Incorporated

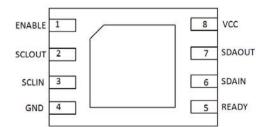

# **Block Diagram**

Figure 3: Block Diagram

## **Maximum Ratings**

| Supply Voltage                         | 0.5V to +6.0V  |

|----------------------------------------|----------------|

| DC Input Voltage                       | –0.5V to +6V   |

| Control Input Voltage (EN)             | –0.5V to +6V   |

| Total Power Dissipation <sup>(1)</sup> | 100mW          |

| Input/Output Current (Port 0 & 1)      | 0mA            |

| Input Current (EN, VCC, GND)           | 50mA           |

| ESD: HBM Mode                          | 4000V          |

| Storage Temperature                    | 55°C to +125°C |

Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Recommended Operating Conditions**

VCC = 2.7V to 5.5V; GND = 0V; Tamb=-40°C to +85°C; unless otherwise specified

| Symbol              | Parameter                     | CONDITIONS                                    | Min. | ТҮР | Max. | Unit |

|---------------------|-------------------------------|-----------------------------------------------|------|-----|------|------|

| $V_{CC}^{[1]}$      | Supply Voltage Port B         | —                                             | 2.7  | _   | 5.5  | V    |

| I <sub>CC</sub>     | Supply Current                | VCC = 5.5V;<br>VSDAIN = VSCLIN = 0V           | _    | 2.8 | 6    | mA   |

| I <sub>CC(sd)</sub> | Shut-Down Mode Supply Current | VENABLE = 0V;<br>All Other pins at VCC or GND |      | 0.1 |      | μΑ   |

Note: 1. This specification applies over the full operating temperature range.

#### **Electrical Characteristics**

2.7 V to 5.5 V: GND = 0.V: Tomb=  $40^{\circ}$ C to  $\pm 85^{\circ}$ C: unless otherwise specified

| Parameter                              | Description                               | Test Conditions                             | Min                 | Тур.                | Max                 | Unit |

|----------------------------------------|-------------------------------------------|---------------------------------------------|---------------------|---------------------|---------------------|------|

| Startup Circo                          | uitry                                     |                                             |                     |                     |                     |      |

| V <sub>pch</sub> <sup>[1]</sup>        | Pre-Charge Voltage                        | SDA, SCL Floating                           | 0.8                 | 1.1                 | 1.2                 | V    |

| V <sub>IH(ENABLE)</sub>                | HIGH-Level Input Voltage on<br>pin ENABLE |                                             | _                   | $0.5 \times V_{CC}$ | $0.7 \times V_{CC}$ | V    |

| V <sub>IL(ENABLE)</sub>                | LOW-Level Input Voltage on<br>pin ENABLE  | _                                           | $0.3 \times V_{CC}$ | $0.5 \times V_{CC}$ | —                   | V    |

| I <sub>I(ENABLE)</sub>                 | Input Current on pin ENABLE               | $V_{\text{ENABLE}} = 0V$ to $V_{\text{CC}}$ | —                   | ±0.1                | ±1                  | μA   |

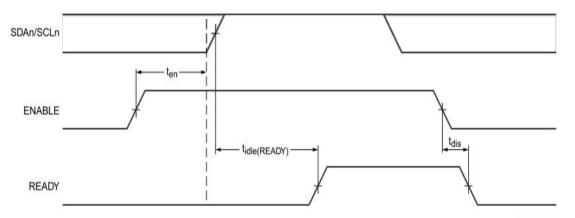

| t <sub>en</sub> <sup>[2]</sup>         | Enable Time                               | —                                           | _                   | 110                 |                     | μs   |

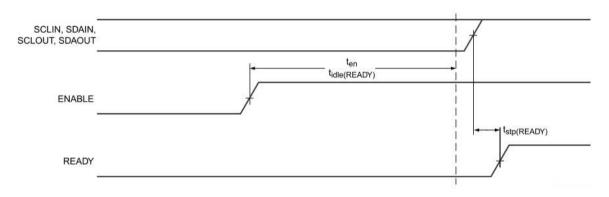

| $t_{idle(READY)}^{[1]}$                | Bus Idle Time to READY<br>Active          |                                             | 50                  | 105                 | 200                 | μs   |

| t <sub>dis(EN-RDY)</sub>               | Disable Time (ENABLE to READY)            | _                                           | _                   | 30                  | —                   | ns   |

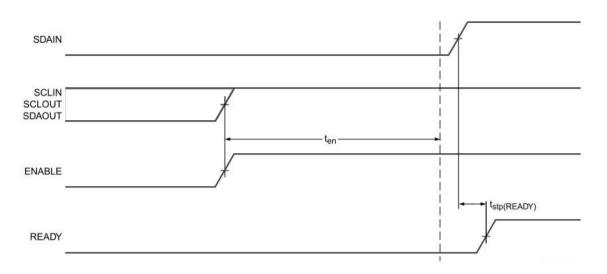

| t <sub>stp(READY)</sub> <sup>[3]</sup> | SDAIN to READY Delay After<br>STOP        |                                             | _                   | 1.2                 | _                   | μs   |

| t <sub>READY</sub> <sup>[3]</sup>      | SCLOUT/SDAOUT to<br>READY delay           | _                                           | _                   | 0.8                 |                     | μs   |

| I <sub>LZ(READY)</sub>                 | Off-State Leakage Current<br>on pin READY | $V_{ENABLE} = V_{CC}$                       | _                   | ±0.3                |                     | μA   |

| $C_{i(ENABLE)}^{\  \  [4]}$            | Input Capacitance on pin<br>ENABLE        | $VI = V_{CC}$ or GND                        | _                   | 1.9                 | 4.0                 | pF   |

| C <sub>o(READY)</sub> <sup>[4]</sup>   | LOW-Level Output Voltage                  | $VI = V_{CC}$ or GND                        | —                   | 2.5                 | 4.0                 | pF   |

| V <sub>OL(READY)</sub> <sup>[1]</sup>  | LOW-Level Output Voltage on<br>pin READY  | Ipu = 3mA;<br>$V_{ENABLE} = V_{CC}$         | _                   |                     | 0.4                 | V    |

1. This specification applies over the full operating temperature range. Note:

2. The enable time can slow considerably for some parts when temperature is  $< -20^{\circ}$ C.

3. Delays that can occur after ENABLE and/or idle times have passed.

4. Guaranteed by design, not production tested.

5. Itrt(pu) varies with temperature and VCC voltage.

6. Input pullup voltage must not exceed power supply voltage in operating mode because the rise time accelerator will clamp the voltage to the positive supply rail.

7. The connection circuitry always regulates its output to a higher voltage than its input. 8. Force  $V_{SDAIN} = V_{SCLIN} = 0.1V$ , tie SDAOUT and SCLOUT through 10kΩ resistor to VCC and measure the SDAOUT and SCLOUT output.

A Product Line of Diodes Incorporated

PI6ULS5V9511A

#### Electrical Characteristics (continued)

$V_{CC} = 2.7 \text{ V}$  to 5.5 V; GND = 0 V; Tamb=-40°C to +85°C; unless otherwise specified

| Parameter                                | Description                         | Test Conditions                                                                                    | Min | Typ. | Max | Unit |

|------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Rise Time A                              | ccelerators                         |                                                                                                    |     |      |     |      |

| I <sub>trt(pu)</sub> [5][6]              | Transient Boosted Pullup<br>Current | Positive Transition on SDA,<br>SCL; $V_{CC} = 2.7V$ ;<br>Slew Rate = $1.25V/\mu s$                 | 1   | 2    |     | V    |

| Input-Outpu                              | t Connection                        |                                                                                                    |     |      |     |      |

| V <sub>offset</sub> <sup>[1][7][8]</sup> | Offset Voltage                      | 10kΩ to V <sub>CC</sub> on SDA, SCL;<br>V <sub>CC</sub> = $3.3$ V                                  | _   | 110  | 175 | mV   |

| t <sub>PLH</sub>                         | LOW to HIGH<br>Propagation Delay    | SCL to SCL and SDA to SDA;<br>$10k\Omega$ to V <sub>CC</sub> ;<br>C <sub>L</sub> = 100pF Each Side | _   | 0    | _   | ns   |

| t <sub>PHL</sub>                         | HIGH to LOW<br>Propagation Delay    | SCL to SCL and SDA to SDA;<br>$10k\Omega$ to V <sub>CC</sub> ;<br>C <sub>L</sub> = 100pF Each Side | _   | 70   | _   | ns   |

| $C_{i(SCL/SDA)}^{[4]}$                   | SCL and SDA Input<br>Capacitance    | _                                                                                                  | _   | 5    | 7   | pF   |

| $V_{OL}^{[1]}$                           | LOW-Level Output Voltage            | $V_I = 0V$ ; SDAn, SCLn pins;<br>$I_{sink} = 3mA$ ; $V_{CC} = 2.7V$                                | 0   |      | 0.4 | V    |

| I <sub>LI</sub>                          | Input Leakage Current               | SDAn, SCLn pins; $V_{CC} = 5.5V$                                                                   | -1  | —    | +1  | μA   |

Note: 1. This specification applies over the full operating temperature range.

2. The enable time can slow considerably for some parts when temperature is  $< -20^{\circ}$ C.

3. Delays can occur after ENABLE and/or idle times have passed.

4. Guaranteed by design, not production tested.

5. Itrt(pu) varies with temperature and VCC voltage.

6. Input pullup voltage must not exceed power supply voltage in operating mode because the rise time accelerator will clamp the voltage to the positive supply rail.

supply ran. 7. The connection circuitry always regulates its output to a higher voltage than its input. 8. Force  $V_{SDAIN} = V_{SCLIN} = 0.1V$ , tie SDAOUT and SCLOUT through 10kΩ resistor to VCC and measure the SDAOUT and SCLOUT output.

PI6ULS5V9511A

## **I2C Interface Timing Requirements**

| Symbol              | Parameter                                                                        |       | Standard Mode I2C<br>Bus |                  | Fast Mode I2C Bus |     |

|---------------------|----------------------------------------------------------------------------------|-------|--------------------------|------------------|-------------------|-----|

| •                   |                                                                                  | Min   | Max                      | Min              | Max               |     |

| fscl                | I2C Clock Frequency                                                              | 0     | 100                      | 0                | 400               | kHz |

| t <sub>Low</sub>    | I2C Clock High Time                                                              | 4.7   |                          | 1.3              |                   | μs  |

| t <sub>High</sub>   | I2C Clock Low Time                                                               | 4     |                          | 0.6              |                   | μs  |

| t <sub>SP</sub>     | I2C Spike Time                                                                   | _     | 50                       |                  | 50                | ns  |

| t <sub>SU:DAT</sub> | I2C Serial-Data Setup Time                                                       | 250   | _                        | 100              |                   | ns  |

| t <sub>HD:DAT</sub> | I2C Serial-Data Hold Time                                                        | 0 [1] |                          | 0 <sup>[1]</sup> |                   | μs  |

| tr                  | I2C Input Rise Time                                                              | _     | 1000                     | _                | 300               | ns  |

| tf                  | I2C Input Fall Time                                                              | _     | 300                      |                  | 300               | ns  |

| t <sub>BUF</sub>    | I2C Bus Free Time Between Stop and Start                                         | 4.7   |                          | 1.3              |                   | μs  |

| t <sub>SU:STA</sub> | I2C Start or Repeated Start Condition Setup                                      | 4.7   | _                        | 0.6              |                   | μs  |

| t <sub>HD:STA</sub> | I2C Start or Repeated Start Condition Hold                                       | 4     | _                        | 0.6              |                   | μs  |

| t <sub>SU:STO</sub> | I2C Stop Condition Setup                                                         | 4     |                          | 0.6              |                   | μs  |

|                     | Valid-Data Time (High to Low) <sup>[2]</sup><br>SCL Low to SDA Output Low Valid  | _     | 1                        |                  | 1                 | μs  |

| t <sub>VD:DAT</sub> | Valid-Data Time (Low to High) <sup>[2]</sup><br>SCL Low to SDA Output High Valid | _     | 0.6                      |                  | 0.6               | μs  |

| t <sub>VD:ACK</sub> | Valid-Data Time of ACK Condition<br>ACK Signal From SCL Low to SDA Output Low    | —     | 1                        |                  | 1                 | μs  |

| Cb                  | I2C Bus Capacitive Load                                                          | _     | 400                      | _                | 400               | pF  |

A device internally must provide a hold time of at least 300ns for the SDA signal (referred to as the VIH min of the SCL signal) in order to bridge the undefined region of the falling edge of SCL.

Data taken using a 1kΩ pullup resistor and 50pF load notes Notes:

Figure 4. Timing for  $t_{en},\,t_{idle(READY)}$  and  $t_{dis}$

t<sub>stp(READY)</sub> is only applicable after the t<sub>en</sub> delay.

Figure 5.  $t_{stp(READY)}$  that can Occur After  $t_{en}$

$t_{\text{stp}(\text{READY})}$  is only applicable after the  $t_{\text{en}}$  delay.

Figure 6.  $t_{stp(READY)}$  Delay that can Occur After Ten and  $t_{idle(READY)}$

$R_L$  = load resistor; 1.35 k $\Omega$

C<sub>L</sub> = load capacitance includes jig and probe capacitance; 50 pF

$R_T$  = termination resistance should be equal to  $Z_0$  of pulse generators

Figure 7: Test Circuitry for Switching Times

## **Function Description**

#### Startup

An undervoltage/initialization circuit holds the parts in a disconnected state, which presents high-impedance to all SDA and SCL pins during power-up. A LOW on the ENABLE pin also forces the parts into the low-current disconnected state when the ICC is essentially zero. When the power supply is brought up, and the ENABLE is HIGH, or when the part is powered and the ENABLE is taken from LOW to HIGH, the device enters an initialization state where the internal references are stabilized, and the pre-charge circuit is enabled.

At the end of the initialization state, the *Stop Bit And Bus Idle* detect circuit is enabled. SDAIN is connected to SDAOUT, and SCLIN is connected to SCLOUT when the ENABLE pin is HIGH long enough to complete the initialization state (ten) and remains HIGH while all of the SDA and SCL pins are HIGH for the bus idle time or when all pins are HIGH, and a STOP condition is on the SDAIN and SCLIN pins.

The 1V pre-charge circuitry is activated during the initialization and is deactivated when the connection is made. The pre-charge circuitry pulls up the SDA and SCL pins to 1V through individual  $100k\Omega$  nominal resistors. This pre-charges the pins to 1V to minimize the worst-case disturbances that result from inserting a card into the backplane where the backplane and the card are at opposite logic levels.

#### **Connect Circuitry**

Once the connection circuitry is activated, the behavior of SDAIN and SDAOUT as well as SCLIN and SCLOUT become identical with each pin acting as a bidirectional buffer that isolates the input capacitance from the output bus capacitance while communicating the logic levels.

A LOW forced on either SDAIN or SDAOUT causes the other pin to be driven to a LOW by the part. The same is also true for the SCL pins. Noise between 0.7VCC and VCC is generally ignored because a falling edge is only recognized when it falls below 0.7VCC with a slew rate of at least  $1.25 \text{ V/}\mu\text{s}$ . When a falling edge is on one pin, the other pin in the pair turns on a pulldown driver that is referenced to a small voltage above the falling pin. The driver pulls the pin down at a slew rate initially determined by the driver and the load because the driver does not start until the first falling pin is below 0.7VCC. The first falling pin can have a fast or slow slew rate. If the falling pin is faster than the pulldown slew rate, the initial pulldown rate continues. If the first falling pin has a slow slew rate, the second pin is pulled down at its initial slew rate until it is just above the first pin's voltage then both pins continue down at the slew rate of the first pin.

When both sides are LOW, they remain LOW until all of the external drivers stop driving LOWs. If both sides are driven LOW to the same value—for instance, 10 mV—by external drivers, which is the case for clock stretching and is typically the case for acknowledge, one side external driver stops driving that pin and rises until the internal driver pulls it down to the offset voltage. When the last external driver stops driving a LOW, the pin rises up and settles out just above the other pin as both rise together with a slew rate determined by the internal slew rate control and the RC time constant. As long as the slew rate is at least 1.25V/µs when the pin voltage exceeds 0.6V for the PI6ULS5V9511A, the rise-time accelerator's circuits turn on, and the pulldown driver turns off.

#### Maximum Number of Devices in Series

Each buffer adds about 0.1V dynamic level offset at 25°C with the offset larger at higher temperatures. Maximum offset ( $V_{offset}$ ) is 0.150V with a 10k $\Omega$  pullup resistor. The LOW level at the signal origination end (master) is dependent upon the load, and the only specification point is that the I2C-bus specification of 3mA produces  $V_{OL} < 0.4V$ ; although if lightly loaded, the  $V_{OL}$  may be ~0.1V. Assuming  $V_{OL} = 0.1V$  and  $V_{offset} = 0.1V$ , the level after four buffers is 0.5 V, which is only about 0.1V below the threshold of the rising edge accelerator (about 0.6V). With great care a system with four buffers can work, but as the  $V_{OL}$  moves up from 0.1V, noise or bounces on the line results in firing the rising edge accelerator thus introducing false clock edges. Generally it is recommended to limit the number of buffers in series to two and to keep the load light to minimize the offset.

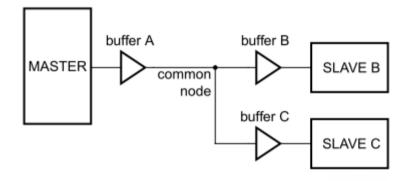

Figure 8: System with Three Buffers Connected to Common Node

Consider a system with three buffers connected to a common node and where communication between the Master and Slave B are connected at either end of buffer A and buffer B in series as shown in Figure 8. Consider if the VOL at the input of buffer A is 0.3V, and the VOL of Slave B (when acknowledging) is 0.4V with the direction changing from Master to Slave B and then from Slave B to Master. Before the direction change, VIL at the input of buffer A is 0.3V, and its output, the common node, is ~0.4V. The output of buffer B and buffer C is ~0.5 V, but Slave B drives 0.4V, so the voltage at Slave B is 0.4V. The output of buffer C is ~0.5V.

When the Master pulldown turns off, the input of buffer A rises and so does its output, the common node, because it is the only part driving the node. The common node rises to 0.5V before buffer B's output turns on; if the pullup is strong, the node can bounce. If the bounce goes above the threshold for the rising edge accelerator ~0.6V, the accelerators on both buffer A and buffer C fire contending with the output of buffer B. The node on the input of buffer A will go HIGH as will the input node of buffer C. After the common node voltage is stable for a while, the rising edge accelerators turn off, and the common node returns to ~0.5V because the buffer B is still on. The voltage at both the Master and Slave C nodes fall to ~0.6V until Slave B turns off. This does not cause a failure on the data line as long as the return to 0.5V on the common node (~0.6V at the Master and Slave C) occurs before the data setup time. If this were the SCL line, the parts on buffer A and buffer C can detect a false clock rather than a stretched clock, which causes a system error.

#### **Propagation Delays**

The delay for a rising edge is determined by the combined pullup current from the bus resistors and the rise time accelerator current source and the effective capacitance on the lines. If the pullup currents are the same, any difference in rise time is directly proportional to the difference in capacitance between the two sides. The  $t_{PLH}$  can be negative if the output capacitance is less than the input capacitance and is positive if the output capacitance is larger than the input capacitance when the currents are the same. The  $t_{PHL}$  is never negative because the output does not start to fall until the input is below 0.7VCC, the output turn on has a non-zero delay, and the output has a limited maximum slew rate. Even if the input slew rate is slow enough that the output catches up, it still lags the falling voltage of the input by the offset voltage. The maximum  $t_{PHL}$  occurs when the input is driven LOW with zero delay, and the output is still limited by its turn-on delay and the falling edge slew rate. The output falling edge slew rate is a function of the internal maximum slew rate, which is a function of temperature, VCC, and process as well as the load current and the load capacitance.

#### **Rise Time Accelerators**

During positive bus transitions, a 2mA current source switches on to quickly slew the SDA and SCL lines HIGH once the input level of 0.6V for the PI6ULS5V9511A is exceeded. The rising edge rate must be at least  $1.25V/\mu s$  to guarantee turnon of the accelerators.

The built-in  $\Delta V/\Delta t$  rise-time accelerators on all SDA and SCL lines require the bus pullup voltage and supply voltage (VCC) to be the same.

#### **READY Digital Output**

This pin provides a digital flag, which is LOW when either ENABLE is LOW, or the start-up sequence described earlier in this section is not complete. READY goes HIGH when ENABLE is HIGH, and startup is complete. The pin is driven by an open-drain pulldown capable of sinking 3mA while holding 0.4V on the pin. Connect a resistor of  $10k\Omega$  to VCC to provide the pullup.

#### **ENABLE Low-Current Disable**

Grounding the ENABLE pin disconnects the backplane side from the card side, disables the rise-time accelerators, drives READY LOW, disables the bus pre-charge circuitry, and puts the part in a low-current state. When the pin voltage drives all the way to VCC, the part waits for data transactions on both the backplane and card sides to be complete before reconnecting the two sides.

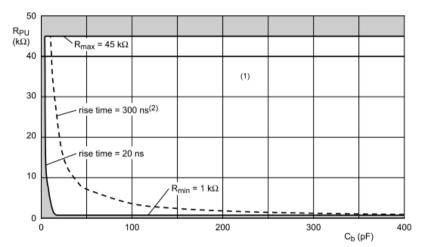

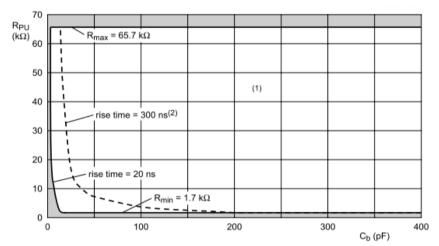

#### **Resistor Pullup Value Selection**

In order to activate the boost pullup currents during rising edges, the system pullup resistors must be strong enough to provide a positive slew rate of 1.25V/µs on the SDA and SCL pins.. Choose a maximum resistor value using the following equation.

$$R \le 800 \times 10^3 (\frac{VCC(\min) - 0.6}{C})$$

Where:

- R is the pullup resistor value in  $\Omega$

- VCC(min) is the minimum VCC voltage in V

- C is the equivalent bus capacitance in pF)

In addition regardless of the bus capacitance, always choose  $R \le 65.7 k\Omega$  for VCC = 5.5V maximum and  $R \le 45 k\Omega$  for VCC = 3.6V maximum. The startup circuitry requires logic HIGH voltages on SDAOUT and SCLOUT to connect the backplane to the card. These pullup values are required to overcome the pre-charge voltage.

Notes:1. Unshaded area indicates recommended pullup, for rise time < 300 ns, with PI6ULS5V9511A.</th>2. Rise time without PI6ULS5V9511A.

Figure 9. Bus Requirements for 3.3V Systems

Notes: 1. Unshaded area indicates recommended pullup, for rise time < 300 ns, with PI6ULS5V9511A. 2. Rise time without PI6ULS5V9511A.

Figure 10. Bus Requirements for 5V Systems

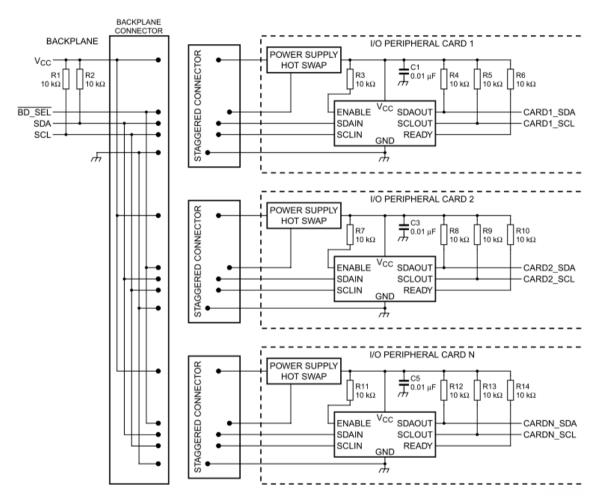

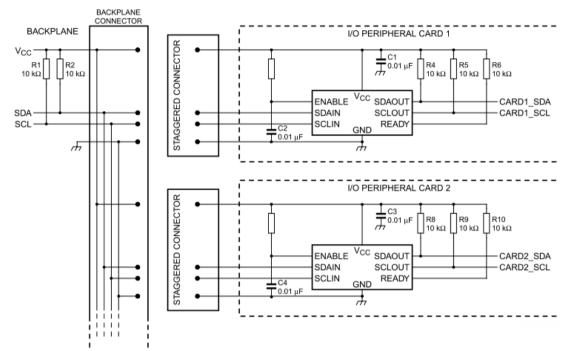

#### Hot-Swapping and Capacitance Buffering Application

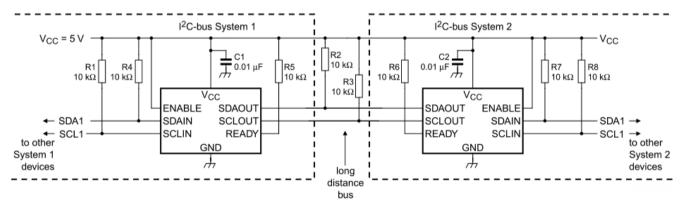

Figure 11 through Figure 14 illustrate the usage of the PI6ULS5V9511A in applications that take advantage of both its hotswapping and capacitance buffering features. In all of these applications, note if the I/O cards are plugged directly into the backplane, all of the backplane and card capacitances add directly together, which makes rise-time and fall-time requirements difficult to meet. However, placing a bus buffer on the edge of each card isolates the card capacitance from the backplane. For a given I/O card, the PI6ULS5V9511A drives the capacitance of everything on the card, and the backplane must drive only the capacitance of the bus buffer, which is less than 10pF, the connector, trace, and all additional cards on the backplane.

Note: The PI6ULS5V9511A can be used in any combination depending on the number of rise-time accelerators that are required by the system. Normally only one PI6ULS5V9511A is required per bus.

Figure 11. Hot Swapping Multiple I/O Cards into a Backplane Using the PI6ULS5V9511A in a cPCI, VME, and Advanced TCA System

A Product Line of Diodes Incorporated

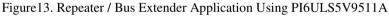

$V_{CC} > V_{CC_LOW}$

R<sub>drop</sub> is the line loss of V<sub>CC</sub> in the backplane.

Figure 14. System with Disparate  $V_{CC}$  Voltages

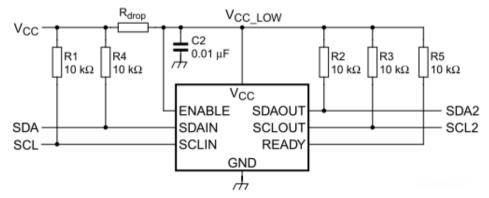

Figure 15. Typical A

# **Part Marking**

Z: Die Rev YW: Year & Work week 1st X: Assembly Code 2nd X: Wafer Fab site Code

Z: Die Rev YW: Year & Work week 1st X: Assembly Code 2nd X: Wafer Fab site Code ZW Package

Z: Die Rev YW: Year & Work week 1st X: Assembly Code 2nd X: Wafer Fab site Code

A Product Line of Diodes Incorporated

## **Packaging Mechanical**

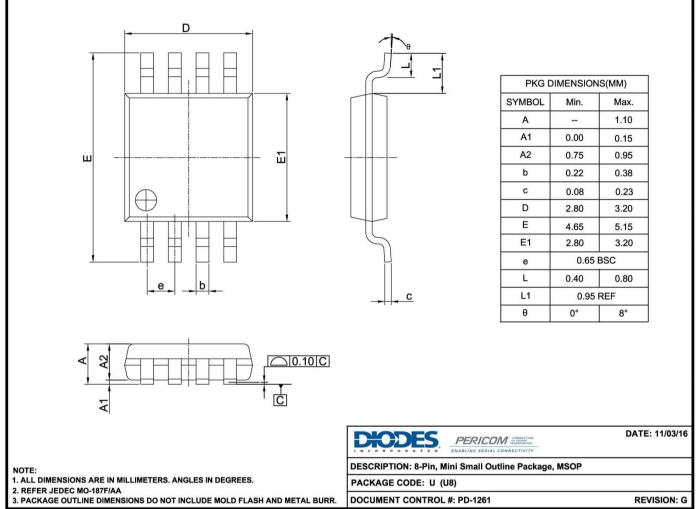

MSOP-8 (U)

16-0242

A Product Line of Diodes Incorporated

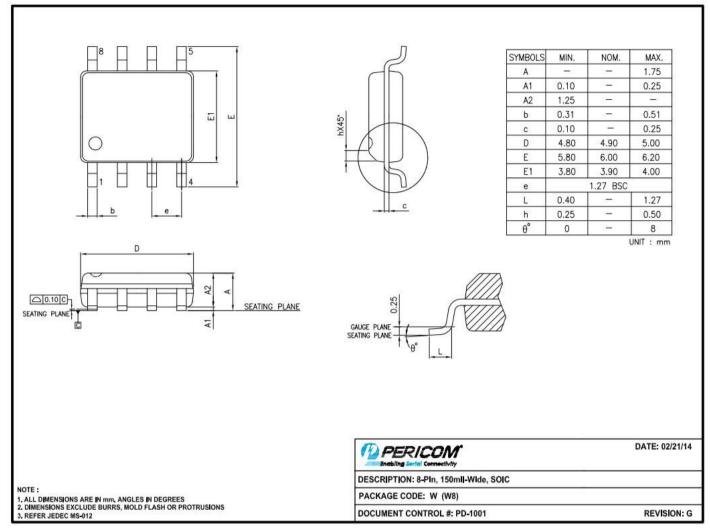

### SOIC-8 (W)

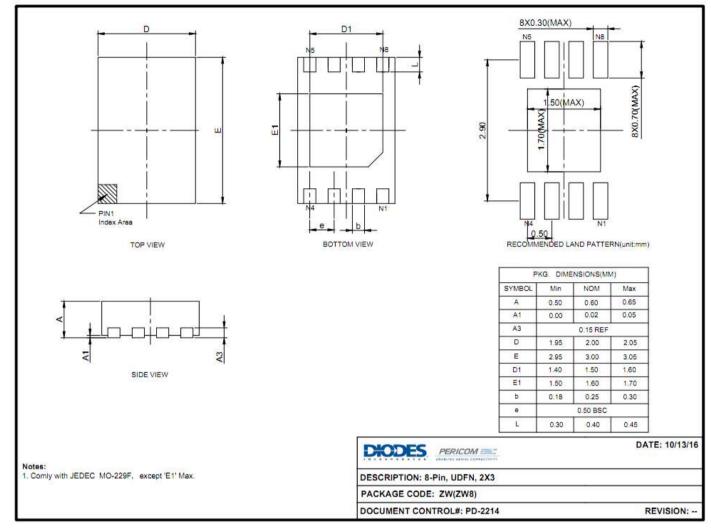

#### UDFN-8 (ZW)

#### For latest package information:

Please see http://www.diodes.com/design/support/packaging/pericom-packaging/packaging-mechanicals-and-thermal-characteristics/.

## **Ordering Information**

| Part Numbers      | Package Code | Package                                  |

|-------------------|--------------|------------------------------------------|

| PI6ULS5V9511AUEX  | U            | 8-Pin, Mini Small Outline Package (MSOP) |

| PI6ULS5V9511AWEX  | W            | 8-Pin, 150mil-Wide (SOIC)                |

| PI6ULS5V9511AZWEX | ZW           | 8-Pin, 2x3 (UDFN)                        |

Notes: 1. No purposely added lead. Fully EU Directive 2002/95/EC (RoHS), 2011/65/EU (RoHS 2) & 2015/863/EU (RoHS 3) compliant.

2. See https://www.diodes.com/quality/lead-free/ for more information about Diodes Incorporated's definitions of Halogen- and Antimony-free, "Green" and Lead-free.

3. Halogen- and Antimony-free "Green" products are defined as those which contain  $\leq$ 900ppm bromine,  $\leq$ 900ppm chlorine ( $\leq$ 1500ppm total Br + Cl) and  $\leq$ 1000ppm antimony compounds.

4. E = Pb-free and Green

5. X suffix = Tape/Reel

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated www.diodes.com