# Headset Detection Interface with Send/End Detect

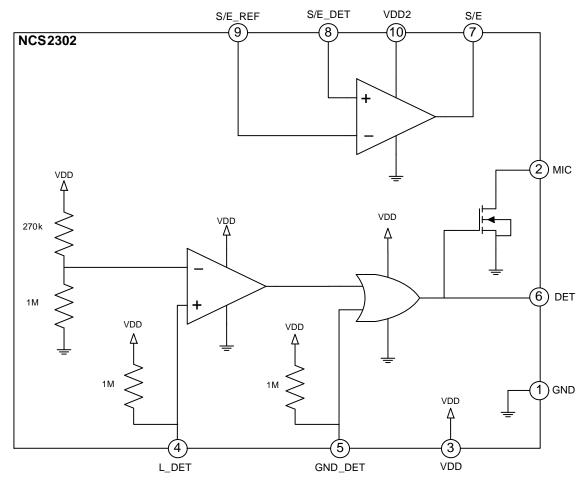

The NCS2302 is a compact and cost effective headset detection interface IC. It integrates several circuit blocks to detect the presence of a stereo headset with a microphone and whether the send/end button has been pressed. The NMOS transistor on the MIC pin mutes the signal when the headset is not present. The built in resistor divider provides the reference voltage for detecting the left audio channel. When L\_DET and GND\_DET are pulled low, the logic low output of the OR gate indicates the headset has been connected properly and the MIC pull–down is disabled. A comparator is integrated for detecting the send/end button press. The NCS2302 comes in a space–saving UQFN10 package (1.4 x 1.8 mm).

#### **Features**

- Wide Supply Voltage Ranges:

- For Headset Detection Circuit:  $V_{DD}$  = 1.6 V to 2.5 V For S/E Comparator Circuit:  $V_{DD2}$  = 1.6 V to 2.8 V

- Low Quiescent Supply Current: 17 µA typical

- Space Saving UQFN10 Package

- These Devices are Pb–Free, Halogen Free/BFR Free and are RoHS Compliant

### **Typical Applications**

- Cell Phones, Smartphones

- Tablets

- Notebooks

# ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAM

AQ = Specific Device Code

M = Date Code

= Pb-Free Package

(Note: Microdot may be in either location)

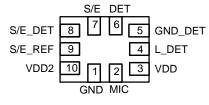

#### **PIN DIAGRAM**

#### Top View

#### **ORDERING INFORMATION**

| Device       | Package             | Shipping <sup>†</sup> |

|--------------|---------------------|-----------------------|

| NCS2302MUTAG | UQFN10<br>(Pb-Free) | 3000 / Tape &<br>Reel |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

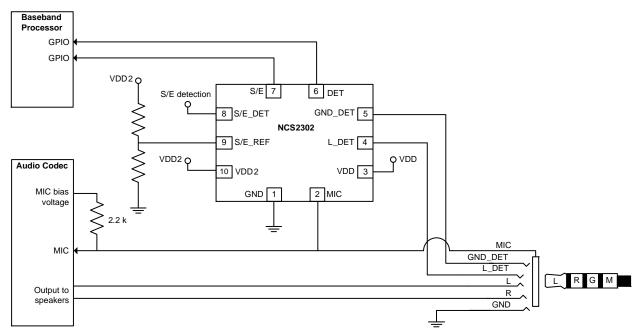

Figure 1. Simplified Application Schematic

Figure 2. Block Diagram

**Table 1. OUTPUT LOGIC**

| Inp                 | uts |     | Outputs              |              |

|---------------------|-----|-----|----------------------|--------------|

| L_detect GND_detect |     | DET | MIC                  | Headset      |

| 0                   | 0 0 |     | 1 (external pull-up) | Detected     |

| 0                   | 1   | 1   | 0                    |              |

| 1                   | 0   | 1   | 0                    | Not Detected |

| 1                   | 1   | 1   | 0                    |              |

**Table 2. PIN DESCRIPTION**

| Pin | Name    | Туре   | Description                                                                                                                                                                                                                                  |

|-----|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND     | Power  | Connects to system ground.                                                                                                                                                                                                                   |

| 2   | MIC     | Output | The open drain MIC pin is connected to the audio jack MIC pin. The MIC pin will pull low when the headset is not connected. When the headset is detected, the internal pull–down is disabled and the external pull–up biases the microphone. |

| 3   | VDD     | Power  | Supply voltage pin for headset detection circuit. A bypass capacitor of 0.1 $\mu F$ is recommended as close as possible to this pin.                                                                                                         |

| 4   | L_DET   | Input  | Connect to audio jack L_DET. This pin is pulled low when the headset is present.                                                                                                                                                             |

| 5   | GND_DET | Input  | Connect to audio jack GND_DET. This pin is pulled low when the headset is present.                                                                                                                                                           |

| 6   | DET     | Output | Indicates whether headset has been detected. Headset is detected when DET is low.                                                                                                                                                            |

| 7   | S/E     | Output | Indicates whether send/end button press has been detected. Button press is detected when S/E is low.                                                                                                                                         |

| 8   | S/E_DET | Input  | Non-inverting input of the comparator detects whether the send/end button has been pressed.                                                                                                                                                  |

| 9   | S/E_REF | Input  | Inverting input of the comparator sets a voltage reference with an external resistor divider                                                                                                                                                 |

| 10  | VDD2    | Power  | Supply voltage pin for S/E detection comparator. A bypass capacitor of 0.1 $\mu\text{F}$ is recommended as close as possible to this pin.                                                                                                    |

Table 3. ABSOLUTE MAXIMUM RATINGS (Note 1)

| Rating                                              | Symbol           | Value                                    | Unit |

|-----------------------------------------------------|------------------|------------------------------------------|------|

| Supply Voltage Range of Headset Detection Circuit   | V <sub>DD</sub>  | 0 to 2.75                                | V    |

| Supply Voltage Range of S/E Detection Comparator    | $V_{DD2}$        | 0 to 2.95                                | V    |

| Input Pin Voltage Range (L_DET, GND_DET)            | V <sub>IN</sub>  | -0.1 to V <sub>DD</sub> + 0.1            | V    |

| Input Pin Voltage Range (S/E_REF, S/E_DET) (Note 4) | V <sub>IN</sub>  | -0.1 to min(V <sub>DD2</sub> + 0.6, 3.3) | V    |

| MIC Output Pin Voltage Range                        | V <sub>MIC</sub> | 0 to 6.0                                 | V    |

| Max Current on MIC Pin                              | I <sub>MIC</sub> | 2                                        | mA   |

| Maximum Junction Temperature                        | $T_{J(max)}$     | +125                                     | °C   |

| Storage Temperature Range                           | T <sub>stg</sub> | -65 to +150                              | °C   |

| Latch-up Current (Note 2)                           | I <sub>LU</sub>  | 800                                      | mA   |

| Moisture Sensitivity Level (Note 3)                 | MSL              | Level 1                                  |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. Refer to ELECTRICAL CHĂRACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- Latch-up Current tested per JEDEC standard: JESD78

Moisture Sensitivity Level tested per IPC/JEDEC standard: J-STD-020A

The maximum voltage on the S/E\_REF and S/E\_DET pins must be the lesser of V<sub>DD2</sub> + 0.6 and 3.3 V.

**Table 4. RECOMMENDED OPERATING RANGES**

| Rating                             | Conditions                | Symbol           | Min | Тур | Max       | Unit |

|------------------------------------|---------------------------|------------------|-----|-----|-----------|------|

| Power Supply Voltage               | Headset Detection Circuit | $V_{DD}$         | 1.6 | 1.8 | 2.5       | V    |

|                                    | S/E Detection Comparator  | $V_{DD2}$        | 1.6 |     | 2.8       | V    |

| Input Voltage                      | L_DET, GND_DET            | V <sub>IN</sub>  | 0   |     | $V_{DD}$  | V    |

|                                    | S/E_DET, S/E_REF          |                  | 0   |     | $V_{DD2}$ | V    |

| Input Transition Rise or Fall Rate | GND_DET pin               | Δt / ΔV          | 0   |     | 10        | ns/V |

| MIC Bias Voltage                   |                           | V <sub>MIC</sub> | 0   |     | 2.95      | V    |

| Ambient Temperature                |                           | T <sub>A</sub>   | -40 |     | 85        | °C   |

| Junction Temperature               |                           | $T_J$            | -40 |     | 125       | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

**Table 5. ELECTRICAL CHARACTERISTICS** Typical values are referenced to  $T_A = 25^{\circ}\text{C}$ ,  $V_{DD} = 1.8 \text{ V}$ ,  $V_{DD2} = 2.1 \text{ V}$ , unless otherwise noted. Min/max values apply from  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ , unless otherwise noted. (Notes 5, 6)

| Parameter                            | Test Conditions                                                                                                                                                             | Symbol                              | Min  | Тур | Max  | Units |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| SUPPLY CHARACTERISTICS               |                                                                                                                                                                             |                                     |      |     |      |       |

| Quiescent Supply Current             | Headset Detection Circuit,<br>V <sub>GND_DET</sub> = 1.8 V, V <sub>L_DET</sub> = 1.8 V                                                                                      | I <sub>DD</sub>                     |      | 7   | 8.5  | μΑ    |

|                                      | S/E Detection Comparator,<br>V <sub>SE_REF</sub> = 0 V, V <sub>SE_DET</sub> = 2.1 V                                                                                         | I <sub>DD2</sub>                    |      | 10  | 12.5 | μΑ    |

| INPUT CHARACTERISTICS OF L_DE        | г                                                                                                                                                                           |                                     |      |     |      |       |

| Voltage Input Low                    |                                                                                                                                                                             | V <sub>IL</sub>                     |      |     | 1.33 | V     |

| Voltage Input High                   |                                                                                                                                                                             | V <sub>IH</sub>                     | 1.5  |     |      | V     |

| Propagation Delay to DET             | C <sub>out</sub> = 15 pF, GND_DET = 0 V,<br>L_DET = 1.31 V to 1.52 V                                                                                                        | t <sub>pLH</sub> , t <sub>pHL</sub> |      | 45  |      | ns    |

| Low to High Propagation Delay to MIC | $C_{out} = 15 \text{ pF}, \text{ GND\_DET} = 0 \text{ V}, \\ L\_DET = 1.31 \text{ V to } 1.52 \text{ V}, \\ R_{PU} = 2.2 \text{ k}\Omega, \text{ MIC bias} = 2.3 \text{ V}$ | t <sub>pLH</sub>                    |      | 230 |      | ns    |

| High to Low Propagation Delay to MIC | $C_{out} = 15 \text{ pF}, \text{ GND\_DET} = 0 \text{ V}, \\ L\_DET = 1.31 \text{ V to } 1.52 \text{ V}, \\ R_{PU} = 2.2 \text{ k}\Omega, \text{ MIC bias} = 2.3 \text{ V}$ | t <sub>pHL</sub>                    |      | 30  |      | ns    |

| Low Voltage Input Bias Current       | V <sub>L_DET</sub> = 0 V                                                                                                                                                    | I <sub>IL</sub>                     |      | 1.8 |      | μΑ    |

| High Voltage Input Leakage           | V <sub>L_DET</sub> = 1.8 V                                                                                                                                                  | I <sub>IH</sub>                     |      | 2.4 |      | nA    |

| Input Capacitance                    | f = 1 MHz                                                                                                                                                                   | C <sub>IN</sub>                     |      | 3   |      | pF    |

| INPUT CHARACTERISTICS OF GND_        | DET                                                                                                                                                                         |                                     |      |     |      |       |

| Voltage Input Low                    |                                                                                                                                                                             | V <sub>IL</sub>                     |      |     | 0.63 | V     |

| Voltage Input High                   |                                                                                                                                                                             | V <sub>IH</sub>                     | 1.17 |     |      | V     |

| Low to High Propagation Delay to DET | $C_{out}$ = 15 pF, R <sub>L</sub> = 1 M $\Omega$ , L_detect = 0 V, GND_detect = 1.8 to 0 V                                                                                  | t <sub>pLH</sub>                    |      | 30  |      | ns    |

| High to Low Propagation Delay to DET | $C_{out}$ = 15 pF, $R_L$ = 1 M $\Omega$ , L_detect = 0 V, GND_detect = 0 to 1.8 V                                                                                           | t <sub>pHL</sub>                    |      | 16  |      | ns    |

| Low Voltage Input Bias Current       | V <sub>GND_detect</sub> = 0 V                                                                                                                                               | I <sub>IL</sub>                     |      | 1.8 |      | μΑ    |

| High Voltage Input Leakage           | V <sub>GND_detect</sub> = 1.8 V                                                                                                                                             | I <sub>IH</sub>                     |      | 2.7 |      | nA    |

| Input Capacitance                    | f = 1 MHz                                                                                                                                                                   | C <sub>IN</sub>                     |      | 3   |      | pF    |

<sup>5.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

<sup>6.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

**Table 5. ELECTRICAL CHARACTERISTICS** Typical values are referenced to  $T_A = 25^{\circ}C$ ,  $V_{DD} = 1.8$  V,  $V_{DD2} = 2.1$  V, unless otherwise noted. Min/max values apply from  $T_A = -40^{\circ}C$  to  $85^{\circ}C$ , unless otherwise noted. (Notes 5, 6)

| Parameter                          | Test Conditions                                                          | Symbol                              | Min | Тур  | Max | Units |

|------------------------------------|--------------------------------------------------------------------------|-------------------------------------|-----|------|-----|-------|

| OUTPUT CHARACTERISTICS OF DET      |                                                                          |                                     |     |      |     |       |

| Voltage Output Low                 | I <sub>OH</sub> = 0.1 mA                                                 | $V_{OL}$                            |     |      | 0.1 | V     |

| Voltage Output High                | $I_{OH} = -0.1 \text{ mA}$                                               | V <sub>OH</sub>                     | 1.6 |      |     | V     |

| Rise Time                          | $C_{OUT}$ = 15 pF, $R_L$ = 1 M $\Omega$                                  | t <sub>rise</sub>                   |     | 50   |     | ns    |

| Fall Time                          | $C_{OUT}$ = 15 pF, $R_L$ = 1 M $\Omega$                                  | t <sub>fall</sub>                   |     | 28   |     | ns    |

| INPUT CHARACTERISTICS OF S/E_R     | EF AND S/E_DET                                                           |                                     |     |      |     |       |

| Propagation Delay to S/E           | C <sub>out</sub> = 15 pF, V <sub>CM</sub> = mid–supply, 100 mV overdrive | t <sub>pLH</sub> , t <sub>pHL</sub> |     | 50   |     | ns    |

| Input Leakage                      | V <sub>CM</sub> = 0.9 V                                                  | I <sub>I</sub> Γ                    |     | 150  |     | pА    |

| Input Capacitance                  | S/E_DET, f = 1 MHz                                                       | C <sub>IN</sub>                     |     | 3    |     | pF    |

|                                    | S/E_REF, f = 1 MHz                                                       | 1                                   |     | 11   |     | 1     |

| OUTPUT CHARACTERISTICS OF S/E      |                                                                          |                                     |     |      |     |       |

| Voltage Output Low                 | I <sub>OH</sub> = 0.1 mA                                                 | $V_{OL}$                            |     |      | 0.1 | V     |

| Voltage Output High                | $I_{OH} = -0.1 \text{ mA}$                                               | V <sub>OH</sub>                     | 1.9 |      |     | V     |

| Rise Time                          | $C_{OUT}$ = 15 pF, $R_L$ = 1 M $\Omega$                                  | t <sub>rise</sub>                   |     | 30   |     | ns    |

| Fall Time                          | $C_{OUT}$ = 15 pF, $R_L$ = 1 M $\Omega$                                  | t <sub>fall</sub>                   |     | 18   |     | ns    |

| CHARACTERISTICS OF MIC             |                                                                          | •                                   |     |      |     |       |

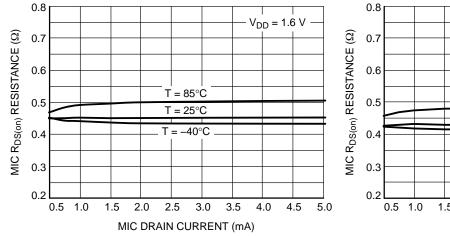

| Drain-Source On Resistance of NMOS | I <sub>MIC</sub> = 1 mA                                                  | R <sub>DS(ON)</sub>                 |     | 0.45 | 1.2 | Ω     |

<sup>5.</sup> Refer to ABSOLUTE MAXIMUM RATINGS and APPLICATION INFORMATION for Safe Operating Area.

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

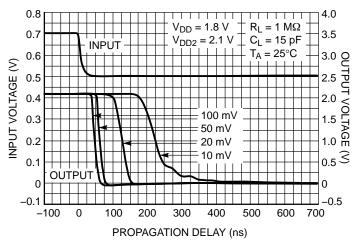

# **TYPICAL CHARACTERISTICS**

Figure 3. MIC On Resistance vs. Drain Current at  $V_{DD} = 1.6 \text{ V}$

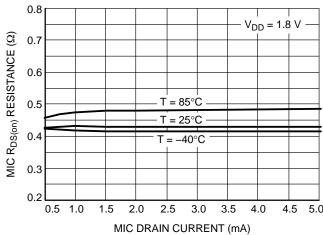

Figure 4. MIC On Resistance vs. Drain Current at V<sub>DD</sub> = 1.8 V

<sup>6.</sup> Performance guaranteed over the indicated operating temperature range by design and/or characterization.

### **TYPICAL CHARACTERISTICS**

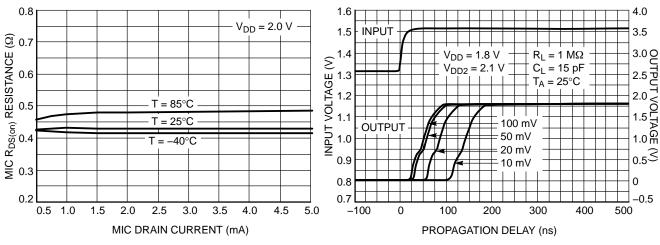

Figure 5. MIC On Resistance vs. Drain Current at  $V_{DD}$  = 2.0 V

Figure 6. Low to High Propagation to DET with Changing Input Overdrive of L\_DET

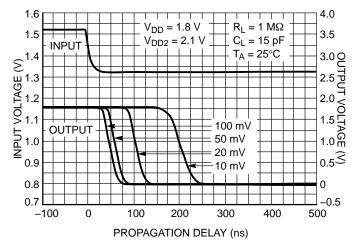

Figure 7. High to Low Propagation to DET with Changing Input Overdrive of L\_DET

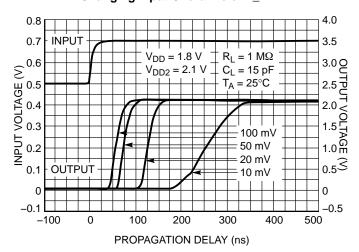

Figure 8. Low to High Propagation to SE with Changing Input Overdrive of SE\_DET

#### TYPICAL CHARACTERISTICS

Figure 9. High to Low Propagation to SE with Changing Input Overdrive of SE\_DET

#### **APPLICATIONS INFORMATION**

#### **Supply Voltages**

The NCS2302 works with a wide range of supply voltages. The main headset detection circuitry power supply can range from  $V_{DD}=1.6~V$  to 2.5 V. The send/end button press detection circuit can be powered from  $V_{DD2}=1.6$  to 2.8 V.  $V_{DD}$  should be powered up before  $V_{DD2}$ . The send/end detection comparator will not be functional unless  $V_{DD}$  and  $V_{DD2}$  are both applied.  $V_{DD2}$  can be connected to  $V_{DD}$  or to a separate supply voltage, such as the MIC bias voltage. Decoupling capacitors of 0.1  $\mu$ F should be placed as close as possible to each power supply pin. Since the NCS2302 has built in latch—up immunity up to 800 mA, series resistors are not recommended on VDD or VDD2.

### **Audio Jack Detection**

The NCS2302 is designed to simplify the detection of a stereo audio connector with a microphone contact. When the headset is not connected, the internal pull-up resistors on L\_DET and GND\_DET pull those pins high. When the headset is connected to the switched audio jack, the headset ground and left audio channel trigger L\_DET and GND\_DET to logic low.

The NCS2302 can work with either the CTIA or OMTP standard. In order to support both standards simultaneously, a cross point switch and additional circuitry is necessary to detect and swap the ground and microphone pins.

#### Send/End Button Press Detection

A second integrated comparator allows the send/end signal to be compared with a reference voltage to detect whether the send/end button has been pressed.

#### **MIC Pin Biasing**

The typical application schematic in Figure 1 shows the recommended 2.2  $k\Omega$  pull–up resistor to the MIC bias voltage. The MIC bias voltage can exceed  $V_{DD}$  and can go as high as 2.95 V. When the headset is not detected, the internal NMOS transistor is enabled to mute the MIC signal. In the typical application scenario with a 2.2  $k\Omega$  pull–up to a 2.1 V MIC bias voltage, the MIC pin is pulled to 1 mV when the headset is not present. The internal NMOS transistor is optimized to sink up to 2 mA of current, allowing some flexibility in the selection of the pull–up resistor and MIC bias voltage.

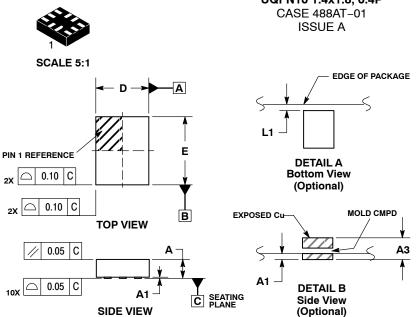

# UQFN10 1.4x1.8, 0.4P

**DATE 01 AUG 2007**

#### NOTES:

- DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS

- 3. DIMENSION b APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM

- FROM TERMINAL.

COPLANARITY APPLIES TO THE EXPOSED PAD

AS WELL AS THE TERMINALS.

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN         | MAX  |  |  |  |

| Α   | 0.45        | 0.60 |  |  |  |

| A1  | 0.00        | 0.05 |  |  |  |

| A3  | 0.127       | REF  |  |  |  |

| b   | 0.15        | 0.25 |  |  |  |

| D   | 1.40        | BSC  |  |  |  |

| E   | 1.80        | BSC  |  |  |  |

| е   | 0.40        | BSC  |  |  |  |

| L   | 0.30        | 0.50 |  |  |  |

| L1  | 0.00        | 0.15 |  |  |  |

| 13  | 0.40        | 0.60 |  |  |  |

## **GENERIC** MARKING DIAGRAM\*

XX = Specific Device Code

= Date Code Μ

= Pb-Free Package

(Note: Microdot may be in either location)

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot " ■", may or may not be present.

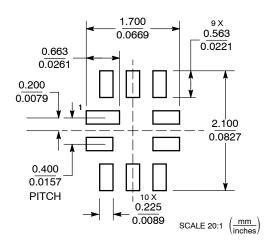

# **MOUNTING FOOTPRINT**

**BOTTOM VIEW**

10 X

Œ 0.05 С

0.10 C A B

| DOCUMENT NUMBER: | 98AON22493D                 | Electronic versions are uncontrolled except when accessed directly from the Document Repository Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | 10 PIN UQFN, 1,4 X 1,8, 0,4 | 1P                                                                                                                                                                              | PAGE 1 OF 1 |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at

www.onsemi.com/support/sales