# Intel® 6702PXH 64-bit PCI Hub

Datasheet

September 2004

Reference Number: 303633-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel® 6702PXH 64-bit PCI Hub may contain design defects or errors known as errata, which may cause the products to deviate from published specifications. Current characterized errata are available upon request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Intel and the Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\* Other brands and names may be claimed as the property of others.

Copyright © 2004, Intel Corporation.

1

2

# int<sub>e</sub>l。 Contents

| Introdu | iction                                                             | 11 |

|---------|--------------------------------------------------------------------|----|

| 1.1     | Related Documents                                                  | 11 |

| 1.2     | Intel® 6700PXH 64-bit PCI Hub Overview                             | 12 |

|         | 1.2.1 PCI Express* Interface (Primary Bus)                         | 12 |

|         | 1.2.2 PCI/PCI-X Bus Interfaces (Secondary Bus)                     | 12 |

|         | 1.2.3 PCI Standard Hot Plug Controller                             | 12 |

|         | 1.2.4 I/OxAPIC Controller                                          |    |

|         | 1.2.5 SMBus Interface                                              | 13 |

|         | 1.2.6 JTAG                                                         | 13 |

| Signal  | Description                                                        | 15 |

| 2.1     | PCI Express* Interface                                             | 15 |

| 2.2     | PCI/PCI-X Bus Interface                                            | 16 |

| 2.3     | PCI Bus Interface 64-bit Extension                                 |    |

| 2.4     | Interrupt Interface                                                | 18 |

| 2.5     | Hot Plug Interface                                                 |    |

| 2.6     | SMBus Interface                                                    |    |

| 2.7     | Miscellaneous Signals                                              | 24 |

| 2.8     | Power and Ground                                                   |    |

| 2.9     | Pin Straps                                                         |    |

| 2.10    | Intel® 6702PXH 64-bit PCI Hub Pin Strapping                        |    |

| 2.11    | Signal Summary                                                     | 28 |

|         | 2.11.1 Signals, Interfaces and Power Planes                        |    |

|         | 2.11.2 Power Planes                                                | 32 |

|         | 2.11.3 Signals and Default States                                  | 32 |

| 2.12    | PCI/PCI-X Interface                                                | 34 |

|         | 2.12.1 Initialization                                              | 34 |

|         | 2.12.2 Transaction Types                                           | 35 |

|         | 2.12.3 Read Transactions                                           | 37 |

|         | 2.12.4 Configuration Transactions                                  | 37 |

|         | 2.12.5 Transaction Termination                                     | 38 |

|         | 2.12.6 PCI-X Protocol Specifics                                    | 42 |

|         | 2.12.7 LOCK Cycles                                                 | 43 |

| 2.13    | Hot Plug Controllers                                               | 44 |

|         | 2.13.1 Mode Determination                                          | 45 |

|         | 2.13.2 Output Control                                              | 46 |

|         | 2.13.3 Input Control                                               | 46 |

|         | 2.13.4 Serial Mode Operation                                       | 47 |

|         | 2.13.5 Parallel Mode Operation                                     | 49 |

|         | 2.13.6 One-Slot-No-Glue Mode                                       | 50 |

|         | 2.13.7 Initialization                                              |    |

|         | 2.13.8 M66EN Pin Handling                                          | 52 |

|         | 2.13.9 Hot Plug Interrupts                                         |    |

|         | 2.13.10 Error Handling                                             |    |

|         | 2.13.11 Assumptions and Intel® 6700PXH 64-bit PCI Hub Requirements |    |

| 2.14  | Addres  | sing                                                  | 53  |

|-------|---------|-------------------------------------------------------|-----|

|       | 2.14.1  | I/O Window Addressing                                 | 53  |

|       | 2.14.2  | Memory Window Addressing                              |     |

|       | 2.14.3  | VGA Addressing                                        |     |

| 2.15  | Transa  | ction Ordering                                        |     |

|       | 2.15.1  | Intel® 6700PXH 64-bit PCI Hub Transaction Ordering    |     |

| 2.16  | I/OxAP  | PIC Interrupt Controller (Functions 1 and 3)          |     |

|       | 2.16.1  | Interrupt Support                                     |     |

|       | 2.16.2  | PCI Express* Legacy INTx Support and Boot Interrupt   |     |

|       | 2.16.3  | Buffer Flushing                                       |     |

|       | 2.16.4  | EOI Special Cycles                                    |     |

|       | 2.16.5  | Interrupt Delivery                                    |     |

| 2.17  |         | Interface                                             |     |

|       | 2.17.1  | SMBus Commands                                        |     |

|       | 2.17.2  | Initialization Sequence                               |     |

|       | 2.17.3  | Configuration And Memory Reads                        |     |

|       | 2.17.4  | Configuration and Memory Writes                       |     |

|       | 2.17.5  | Error Handling                                        |     |

|       | 2.17.6  | SMBus Interface Reset                                 |     |

|       | 2.17.7  | Configuration Access Arbitration                      |     |

| 2.18  |         | n Setup                                               |     |

|       | 2.18.1  | Clocking                                              |     |

|       | 2.18.2  | Component Reset                                       |     |

| 2.19  | Reliabi | lity, Availability, and Serviceability (RAS)          |     |

|       | 2.19.1  | PCI Express* Error Handling                           |     |

|       | 2.19.2  | PCI Error Protection                                  |     |

|       | 2.19.3  | PCI Standard Hot Plug Controller                      |     |

|       | 2.19.4  | SMBus                                                 |     |

| 2.20  | Error H | landling                                              |     |

|       | 2.20.1  | PCI Express* Errors                                   |     |

|       | 2.20.2  | PCI Errors                                            |     |

|       | 2.20.3  | SHPC Errors                                           |     |

|       | 2.20.4  | Core Errors                                           |     |

|       | 2.20.5  | Global Error Register                                 |     |

|       |         | -                                                     |     |

| Regis |         | ription                                               |     |

| 3.1   |         | onfiguration Registers                                |     |

| 3.2   | Memor   | y-Mapped Registers                                    |     |

| 3.3   |         | Port Registers                                        |     |

| 3.4   |         | er Nomenclature and Access Attributes                 |     |

| 3.5   |         | press*-to-PCI Bridges (D0:F0, F2)                     |     |

|       | 3.5.1   | Configuration Registers                               |     |

| 3.6   |         | press* to PCI Bridges (D0:F0, F2) Enhanced            |     |

|       | 3.6.1   | Configuration Registers                               |     |

|       | 3.6.2   | Power Management Registers                            |     |

| 3.7   |         | Ig Controller Registers                               |     |

|       | 3.7.1   | Configuration Registers                               |     |

|       | 3.7.2   | Offset 24h – 40h: Logical Slot Registers (LSR) 1 to 6 |     |

| 3.8   |         | PIC Interrupt Controller Registers (Function 1 and 3) |     |

|       | 3.8.1   | PCI Configuration Space Registers                     |     |

|       | 3.8.2   | I/OxAPIC Direct Memory Space Registers                |     |

|       | 3.8.3   | Indirect Memory Space Registers                       | 152 |

| 4 | Electrical Characteristics                                                      |

|---|---------------------------------------------------------------------------------|

|   | 4.1 DC Voltage and Current Specifications                                       |

|   | 4.1.1 VCC15 and VCC33 Voltage Requirements                                      |

|   | 4.1.2 VCCEXP and EXP_CLK_N/EXP_CLK_P157                                         |

|   | 4.1.3 Intel® 6700PXH 64-bit PCI Hub DC Specifications                           |

|   | 4.1.4 Input Characteristic Signal Association                                   |

|   | 4.1.5 DC Input Characteristics                                                  |

|   | 4.1.6 DC Characteristic Output Signal Association                               |

|   | 4.1.7 DC Output Characteristics                                                 |

|   | 4.2 AC Specifications                                                           |

|   | 4.2.1 PCI and PCI-X AC Characteristics168                                       |

|   | 4.3 Timing Specifications170                                                    |

|   | 4.3.1 PCI Express* Interface Timing170                                          |

|   | 4.3.2 PCI and PCI-X Interface Timing172                                         |

|   | 4.3.3 PCI and PCI-X Clock Specification176                                      |

| 5 | Component Ballout179                                                            |

|   | 5.1 Intel® 6700PXH 64-bit PCI Hub179                                            |

|   | 5.2 Intel® 6702PXH 64-bit PCI Hub Ballout181                                    |

| 6 | Signal Lists                                                                    |

|   | 6.1 Intel® 6700PXH 64-bit PCI Hub Signal List (Sorted by Signal Name)           |

|   | 6.2 Intel® 6702PXH 64-bit PCI Hub Signal List (Sorted by Signal Name)           |

|   | 6.3 Intel® 6700PXH/6702PXH 64-bit PCI Hub Signal List (Sorted by Pin Number)214 |

| 7 | Mechanical Specifications                                                       |

| 0 |                                                                                 |

| 8 | Testability                                                                     |

### **Figures**

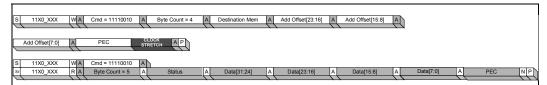

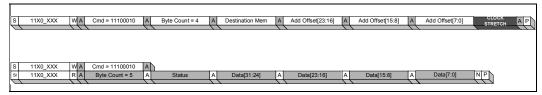

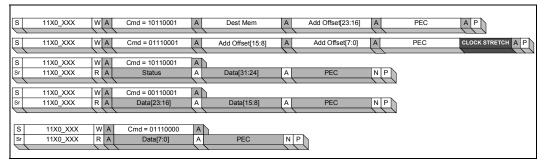

| 2-1  | DWord Configuration Read Protocol (SMBus Block Write/Block Read, PEC Enabled)  | 64  |

|------|--------------------------------------------------------------------------------|-----|

| 2-2  | DWord Memory Read Protocol (SMBus Block Write/Block Read, PEC Enabled)         |     |

| 2-3  | DWord Configuration Read Protocol (SMBus Word Write/Word Read, PEC Enabled)    | 64  |

| 2-4  | DWord Configuration Read Protocol (SMBus Block Write/Block Read, PEC Disabled) | 64  |

| 2-5  | DWord Memory Read Protocol (SMBus Block Write/Block Read, PEC Disabled)        | 64  |

| 2-6  | DWord Configuration Read Protocol (SMBus Word Write/Word Read, PEC Disabled)   | 65  |

| 2-7  | DWord Configuration Write Protocol (SMBus Block Write, PEC Enabled)            | 65  |

| 2-8  | DWord Memory Write Protocol (SMBus Word Write, PEC Enabled)                    | 65  |

| 2-9  | Word Configuration Write Protocol (SMBus Byte Write, PEC Enabled)              | 66  |

| 2-10 | DWord Memory Read Protocol (SMBus Word Write/(Word, Byte) Read, PEC            |     |

|      | Enabled)                                                                       | 66  |

| 2-11 | DWord Memory Read Protocol (SMBus Word Write/Byte Read, PEC                    |     |

|      | Enabled)                                                                       | 66  |

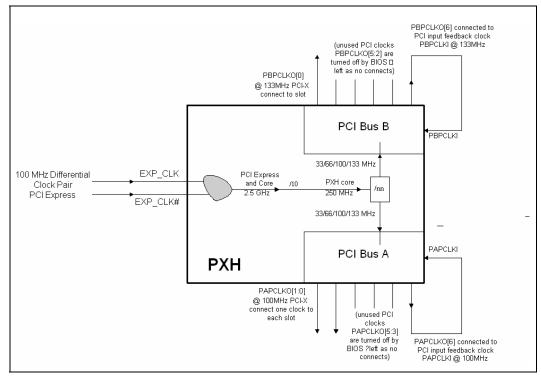

| 2-12 | Intel® 6700PXH 64-bit PCI Hub Clocking Diagram                                 | 68  |

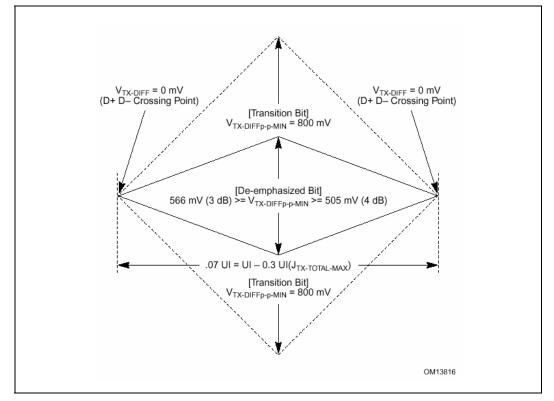

| 4-1  | Minimum Transmitter Timing and Voltage Output Compliance Specification         | 164 |

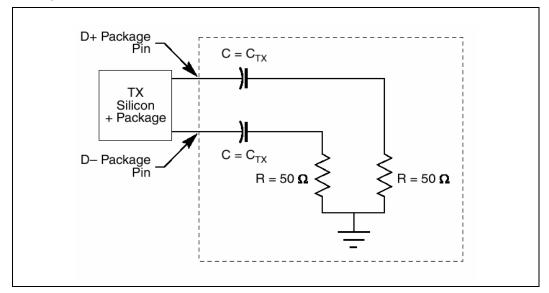

| 4-2  | Compliance Test/Measurement Load                                               | 165 |

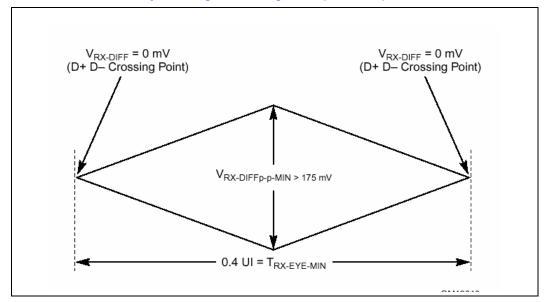

| 4-3  | Minimum Receiver Eye Timing and Voltage Compliance Specification               | 165 |

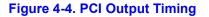

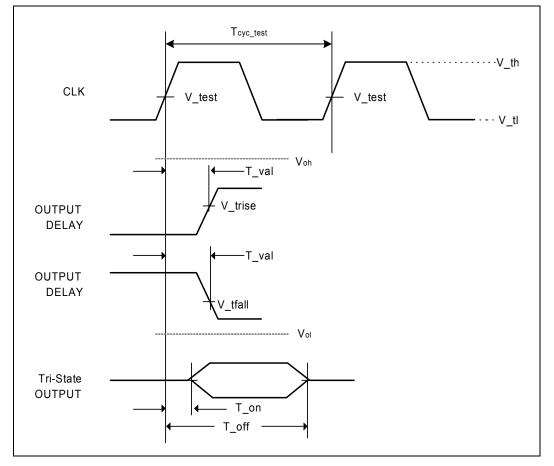

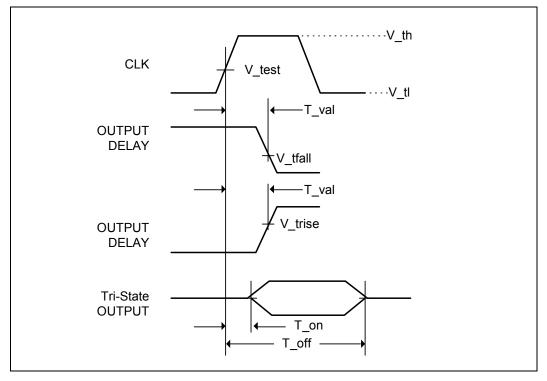

| 4-4  | PCI Output Timing                                                              | 173 |

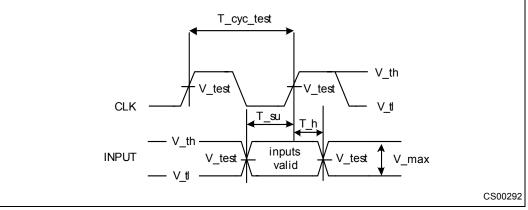

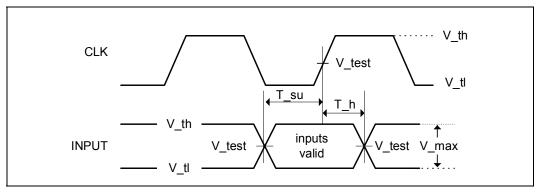

| 4-5  | PCI Input Timing                                                               | 173 |

| 4-6  | PCI-X Mode 1 Output Timing                                                     | 176 |

| 4-7  | PCI-X Mode 1 Input Timing                                                      | 176 |

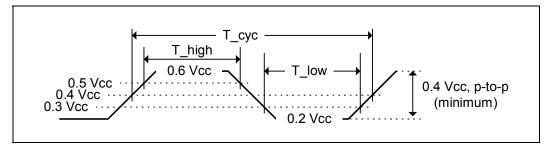

| 4-8  | PCI-X 3.3V Clock Waveform                                                      | 177 |

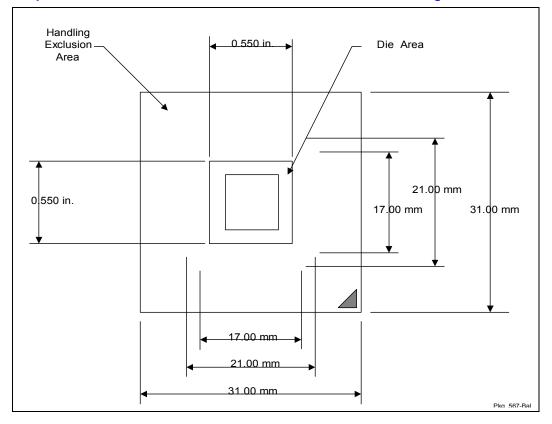

| 7-1  | Top View – Intel® 6700PXH 64-bit PCI Hub 567-Ball FCBGA<br>Package Dimensions  | 231 |

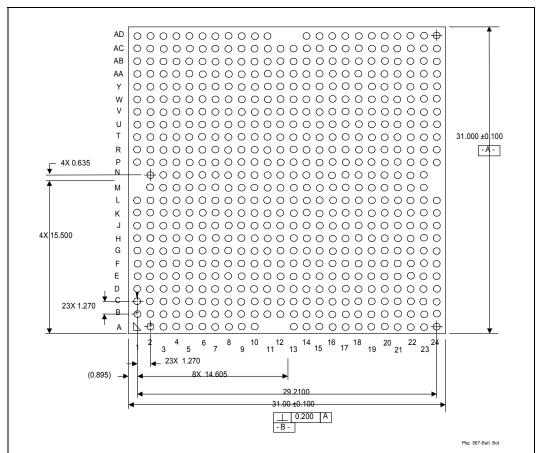

| 7-2  | Bottom View – Intel® 6700PXH 64-bit PCI Hub 567-Ball FCBGA                     |     |

|      | Package Dimensions                                                             | 232 |

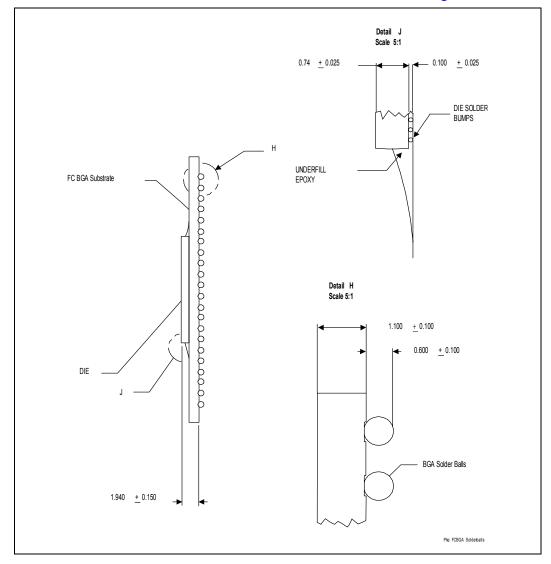

| 7-3  | Side View – Intel® 6700PXH 64-bit PCI Hub 567-Ball FCBGA                       |     |

| -    | Package Dimensions                                                             | 233 |

# int<sub>el</sub>.

### Tables

| 2-1          | PCI Express* Interface Signals                                             |  |

|--------------|----------------------------------------------------------------------------|--|

| 2-2          | PCI Bus Interface A and B Signals                                          |  |

| 2-3          | PCI Bus Interface 64-bit Extension Interface A and B Signals               |  |

| 2-4          | Interrupt Interface A and B Signals                                        |  |

| 2-5          | General Hot Plug Interface A and B Signals – All Hot Plug Modes            |  |

| 2-6          | Serial Mode Hot Plug Signals – Interface A and B – 3 to 6 Slots            |  |

| 2-7          | Parallel Mode Hot Plug Signals – Interface A and B – 1 to 2 Slots          |  |

| 2-8          | SMBus Interface Signals                                                    |  |

| 2-9          | Miscellaneous Signals                                                      |  |

| 2-10         | Voltage Pins                                                               |  |

| 2-11         | Normal Functional Pin Straps                                               |  |

| 2-12         | Intel® 6702PXH 64-bit PCI Hub Pin Strapping                                |  |

| 2-13         | Intel® 6700PXH 64-bit PCI Hub Signals, Interfaces and Power Planes         |  |

| 2-14         | Intel® 6700PXH 64-bit PCI Hub Platform Power Planes                        |  |

| 2-15         | Intel® 6700PXH 64-bit PCI Hub Signals and Default States                   |  |

| 2-16         | PCI/PCI-X Mode and Frequency Encoding                                      |  |

| 2-17         | PCI-X Initialization Pattern Driven by the Intel® 6700PXH 64-bit PCI Hub   |  |

| 2-18         | Intel® 6700PXH 64-bit PCI Hub PCI Transactions                             |  |

| 2-19         | PCI-X Transactions Supported                                               |  |

| 2-20         | Intel® 6700PXH 64-bit PCI Hub Implementation of Requester Attribute Fields |  |

| 2-21         | Intel® 6700PXH 64-bit PCI Hub Implementation Completion Attribute Fields   |  |

| 2-22         | Split Completion Abort Registers                                           |  |

| 2-23         | LOCK Transaction Handling                                                  |  |

| 2-24         | Hot Plug Mode Settings                                                     |  |

| 2-25         | Serial Input Stream                                                        |  |

| 2-26<br>2-27 | Serial Output Stream<br>Muxed Hot Plug Mode Signals Parallel Mode          |  |

| 2-27         | Inbound Transaction Ordering                                               |  |

| 2-20         | Outbound Transaction Ordering                                              |  |

| 2-25         | Intel® 6700PXH 64-bit PCI Hub INTx Routing                                 |  |

| 2-30         | System Bus Delivery Address Format                                         |  |

| 2-31         | System Bus Delivery Data Format                                            |  |

| 2-33         | SMBus Address Configuration                                                |  |

| 2-34         | SMBus Command Encoding                                                     |  |

| 2-35         | SMBus Status Byte Encoding                                                 |  |

| 2-36         | Intel® 6700PXH 64-bit PCI Hub Clocking                                     |  |

| 2-37         | Power-On Frequency of Intel® 6700PXH 64-bit PCI Hub                        |  |

| 3-1          | Configuration Register Summary                                             |  |

| 3-2          | Power Management Register Summary                                          |  |

| 3-3          | Hot Plug Controller Register Summary                                       |  |

| 3-4          | Indirect Memory Space Registers Summary                                    |  |

| 4-1          | Intel® 6700PXH 64-bit PCI Hub DC and AC Voltage Specifications             |  |

| 4-2          | Intel® 6700PXH 64-bit PCI Hub DC Current Specifications                    |  |

| 4-3          | Intel® 6700PXH 64-bit PCI Hub Thermal Current, Amps (nominal)              |  |

| 4-4          | DC Characteristics Input Signal Association                                |  |

| 4-5          | DC Input Characteristics                                                   |  |

| 4-6          | DC Characteristic Output Signal Association                                |  |

| 4-7          | DC Output Characteristic                                                   |  |

| 4-8          | Differential Transmitter (TX) DC Output Specifications                     |  |

|              |                                                                            |  |

| 4-9  | Differential Receiver (RX) DC Input Specifications                       | 162 |

|------|--------------------------------------------------------------------------|-----|

| 4-10 | DC Specifications for PCI and Mode 1 PCI-X 3.3V Signaling                | 166 |

| 4-11 | PCI Hot Plug Slot Power Requirements                                     | 167 |

| 4-12 | DC Specification for Input Clock Signals                                 | 167 |

| 4-13 | DC Specification for Output Clock Signals                                | 167 |

| 4-14 | Conventional PCI 3.3V AC Characteristics                                 | 168 |

| 4-15 | PCI-X 3.3V AC Characteristics                                            | 169 |

| 4-16 | Differential Transmitter (TX) Output Specifications                      | 170 |

| 4-17 | Differential Receiver (RX) Input Specifications                          | 171 |

| 4-18 | Conventional PCI Interface Timing                                        | 172 |

| 4-19 | PCI-X Mode 1 General Timing Parameters                                   | 174 |

| 4-20 | PCI and PCI-X Clock Timings                                              | 177 |

| 6-1  | Intel® 6700PXH 64-bit PCI Hub Signal List (Sorted by Signal Name)        |     |

| 6-2  | Intel® 6702PXH 64-bit PCI Hub Signal List (Sorted by Signal Name)        | 198 |

| 6-3  | Intel® 6700PXH/6702PXH 64-bit PCI Hub Signal List (Sorted by Pin Number) |     |

| 8-1  | TAP Controller Pins                                                      | 235 |

| 8-2  | TAP Instructions Supported By the Intel® 6700PXH 64-bit PCI Hub          | 235 |

|      |                                                                          |     |

# **Revision History**

| Revision | Doc #  | Description      | Date           |

|----------|--------|------------------|----------------|

| 001      | 303633 | Initial Release. | September 2004 |

# Intel® 6702PXH 64-bit PCI Hub Features

- PCI Express\* Interface

- Compatible with PCI Express Base Specification 1.0a

- Raw bit-rate on the data pins of 2.5 Gbit/s, resulting in a raw bandwidth per pin of 250 MB/s

- x8 and x4 modes of operation, support for x4 on 3:0 (with 3 being lane 3) and 4:7 (with 4 being lane 3)

- Support for x8, x4 lane reversal

- Support for x4 lane reversal only on the lower 4 lanes

- Maximum realized bandwidth (in x8 mode) on PCI Express interface is 2 GB/s in each direction simultaneously, for an aggregate of 4 GB/s

- Full-speed self-test and diagnostic (IBIST) functionality

- Automatic link initialization, configuration and re-training out of reset

- Runtime detection and recovery for loss of link synchronization

- PCI-X Interface

- PCI Spec rev 2.3 compliant

- PCI-X 1.0b spec compliant

- 64-bit 66MHz, 3.3V

- 6 external REQ/GNT Pairs for internal arbiter (only 3 pairs are available when operating SHPC in parallel mode)

- On-die termination of 8.33K ohms @ +/- 40%

- 64 bit addressing, inbound and outbound and support for DAC command

- **RAS** Features

- PCI Express interfaces protected with 32-bit CRC

- Full access to all registers via SMBus

- PCI bus protected with parity

- PCI standard Hot Plug

- PCI Standard Hot-Plug controller Specification Rev 1.0 compliant

- Support for 6 slots maximum

- Parallel mode operation for 1 and 2 slot systems and slot interface logic not needed.

- Serial mode operation for other systems with hot-plug slots from 3 to 6. Slot interface logic needed to serialize and de-serialize information from Intel® 6702PXH 64-bit PCI Hub

- 1-slot-no-glue parallel mode operation when the number of slots controlled is one and there are no other devices on the PCI bus. No on-board Q-Switches are needed for bus isolation in this mode

- I/OXAPIC

- One I/OxAPIC controller per PCI bus segment

- 24 interrupts per controller

- 16 physical PCI interrupt pins per PCI bus in the server mode

- PCI virtual wire interrupt support via writing to Pin Assertion Register in the I/OxAPIC

- SMBus Interface

- Electrically compliant with System Management Bus 2.0 Specification with PEC support

- Slave mode operation only

- Full read/write access to all configuration and memory spaces in Intel® 6702PXH 64-bit PCI Hub

- Power Management

- Support for PCI Express Active State Power Management (ASPM) L0s link state

- Support for PCI PM 1.1 compatible D0, D3hot and D3cold device power states

- Support for PME# event propagation on behalf of PCI devices

- §

# int<sub>e</sub>l。 1 *Introduction*

The Intel® 6702PXH 64-bit PCI Hub are peripheral chips that perform PCI bridging functions between the PCI Express interface and the PCI Bus. The Intel® 6702PXH 64-bit PCI Hub contains a single PCI bus interface that can be configured to operate in PCI (33 or 66 MHz) or PCI-X Mode 1 (66, 100, or 133 MHz).

The Intel® 6702PXH 64-bit PCI Hub further support the new *PCI Standard Hot-Plug Controller and Subsystem Specification*, Revision 1.0. Each PCI interface contains an I/OxAPIC with 24 interrupts and a standard hot plug controller.

### 1.1 Related Documents

- PCI Express Base Specification, Revision 1.0a, from www.pci-sig.com.

- *PCI-X Electrical and Mechanical Addendum to the PCI Local Bus Specification*, Revision 2.0a, and *PCI-X Protocol Addendum to the PCI Local Bus Specification*, Revision 2.0a, both from www.pci-sig.com.

- PCI Local Bus Specification, Revision 2.3, from www.pci-sig.com.

- *PCI Standard Hot-Plug Controller and Subsystem Specification*, Revision 1.0, from www.pci-sig.com.

- PCI to PCI Bridge Architecture Specification, Revision 1.1, from www.pci-sig.com.

- PCI Power Management Interface Specification, Revision 1.1, from www.pci-sig.com.

- SMBus Specification, Revision 2.0.

- IEEE Standard Test Access Port and Boundary Scan Architecture 1149.1a.

### 1.2 Intel® 6702PXH 64-bit PCI Hub Overview

#### 1.2.1 PCI Express Interface (Primary Bus)

The primary bus interface between the Intel® 6702PXH 64-bit PCI Hub and the core logic chipset component is the PCI Express interface. Maximum realized bandwidth on this interface is 2 GB/s in each direction simultaneously, for an aggregate of 4 GB/s. The PCI Express interface is compatible with the *PCI Express Base Specification*, Revision 1.0a. The Intel® 6702PXH 64-bit PCI Hub supports X1, X4, and X8 widths for PCI Express. X4 width is supported on 3:0 (with 3 being lane 3) and 4:7 (with 4 being lane 3), and X1 width is supported on lanes 7, 4, 3, and 0. The Intel® 6702PXH 64-bit PCI Hub also supports X8 lane reversal, plus X4 lane reversal on the lower 4 lanes only.

#### 1.2.2 PCI/PCI-X Bus Interfaces (Secondary Bus)

The Intel® 6702PXH 64-bit PCI Hub has a single PCI Bus interface (PCI Bus A). In this document these buses are referred to as the secondary buses. These interfaces can be independently configured as either a PCI Bus or PCI-X Bus. The Intel® 6702PXH 64-bit PCI Hub support conventional PCI and PCI-X Mode 1. PCI Bus extensions are also supported; these include 64-bit addressing outbound, with the capability to assert DAC, and full 64-bit addressing inbound. The inbound packet size is based on cache line size of the platform.

The PCI Bus interface is compliant with the *PCI Local Bus Specification*, Revision 2.3. The PCI-X interface on the Intel® 6702PXH 64-bit PCI Hub is compliant with the *PCI-X Addendum to the PCI Local Bus Specification*, Revision 1.0b as well as the Mode 1 section of the *PCI-X Electrical and Mechanical Addendum to the PCI Local Bus Specification*, Revision 2.0a and the *PCI-X Protocol Addendum to the PCI Local Bus Specification*, Revision 2.0a. For conventional PCI Mode, the Intel® 6702PXH 64-bit PCI Hub supports PCI bus frequencies of 33 MHz and 66 MHz. For the PCI-X Mode 1, the Intel® 6702PXH 64-bit PCI Hub supports PCI bus frequencies of 66 MHz, 100 MHz, and 133 MHz.

#### 1.2.3 PCI Standard Hot Plug Controller

The Intel® 6702PXH 64-bit PCI Hub hot plug controller is compliant with *PCI Standard-Hot Plug Controller and Subsystem Specification*, Revision 1.0 and allows PCI card removal, replacement, and addition without powering down the system. The Intel® 6702PXH 64-bit PCI Hub hot plug controller supports three to six PCI slots through an input/output serial interface when operating in Serial Mode, and one to two slots through an input/output parallel interface when operating in Parallel Mode. The Intel® 6702PXH 64-bit PCI Hub can also operate in "one-slot-no-glue" hot plug mode, which does not require and on-board logic for enabling and disabling the bus and clocks signals to the PCI/PCI-X hot plug slots. The input serial interface is polling and is in continuous operation. The output serial interface is "demand" and acts only when requested. These serial interfaces run at about 8.25 MHz regardless of the speed of the PCI bus. In parallel mode, the Intel® 6702PXH 64-bit PCI Hub performs the serial to parallel conversion internally, so the serial interface cannot be observed. However, internally the hot plug controller always operates in a serial mode.

#### 1.2.4 I/OxAPIC Controller

The Intel® 6702PXH 64-bit PCI Hub contains one I/OxAPIC controller, which reside on the primary bus. The intended use of this controller for the Intel® 6702PXH 64-bit PCI Hub is to have the interrupt from PCI bus A connected to the interrupt controller on device 0, function 1.

#### 1.2.5 SMBus Interface

The SMBus interface can be used for system and power management related tasks. The interface is compliant with *System Management Bus Specification*, Revision 2.0. The SMBus interface allows full read/write access to all configuration and memory spaces in the Intel® 6702PXH 64-bit PCI Hub.

#### 1.2.6 JTAG

The Intel® 6702PXH 64-bit PCI Hub has a JTAG (TAP) port compliant with the *IEEE Standard Test Access Port and Boundary Scan Architecture 1149.1 Specifications*. The TAP controller is accessed serially through five dedicated pins. This can be used for test and debug purposes. System board interconnects can be DC tested using the boundary scan logic in pads.

§

Introduction

# int<sub>el</sub>®

# intel<sup>®</sup> 2 Signal Description

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name the signal is asserted when at the high voltage level.

*Note:* Segment "A" signifies the interface of the PCI bus segment of the Intel® 6702PXH 64-bit PCI Hub. All Intel® 6702PXH 64-bit PCI Hub PCI bus signals will use the letter "A" in these signal names. For example, in the PCI Bus interface, PAAD[31:0] refer to the AD bus signals on PCI Bus A.

The following notations are used to describe the signal type:

- P Power pin

- I Input pin

- O Output pin

- I/O Bi-directional Input/Output pin

#### 2.1 PCI Express Interface

#### Table 2-1. PCI Express\* Interface Signals

| Signal                       | Туре | Description                                                                                                                                                                                                                                                                                                                     |

|------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXP_CLK<br>EXP_CLK#          | I    | <b>PCI Express* Reference Clocks:</b> 100 MHz differential clock pair. Connect to an external 100 MHz differential clock.                                                                                                                                                                                                       |

| EXP_COMP[1:0]                | I    | PCI Express Compensation Inputs: Analog signals.                                                                                                                                                                                                                                                                                |

| EXP_RXP[7:0]<br>EXP_RXN[7:0] | Ι    | PCI Express Serial Data Inputs: PCI Express differential data receive signals.<br>For 4X mode, only signals EXP_RXP[3:0] and EXP_RXN[3:0] are used.<br>For 8X mode, all of these signals, EXP_RXP[7:0] and EXP_RXN[7:0], are<br>used.<br>These signals are the PExRp[7:0] and PExRn[7:0] signals per the PCI SIG<br>convention. |

| EXP_TXP[7:0]<br>EXP_TXN[7:0] | 0    | PCI Express Serial Data Outputs: PCI Express differential data transmit signals.<br>For 4X mode, only signals EXP_TXP[3:0] and EXP_TXN[3:0] are used.<br>For 8X mode, all of these signals, EXP_TXP[7:0] and EXP_TXN[7:0], are used.<br>These signals are the PExTp[7:0] and PExTn[7:0] signals per the PCI SIG convention.     |

### 2.2 PCI/PCI-X Bus Interface

#### Table 2-2. PCI Bus Interface A Signals (Sheet 1 of 2)

| Signal       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA133EN      | I    | Only relevant when Intel® 6702PXH 64-bit PCI Hub samples PAPCIXCAP at a level indicating 133MHz PCI-X capability.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|              |      | <b>PCI-X 133 MHz Enable:</b> Sets the maximum frequency capability of a PCI-X mode 1 bus to either 100 MHz or 133 MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|              |      | This pin, when high, allows the PCI-X segment to run at a maximum 133 MHz when in PCI-X mode 1. When low, the PCI-X segment is limited to a maximum frequency of 100 MHz when in PCI-X mode 1.                                                                                                                                                                                                                                                                                                                                                                                          |

| PAAD[31:0]   | I/O  | <b>PCI Address/Data:</b> These signals are a multiplexed address and data bus. During the address phase or phases of a transaction, the initiator drives a physical address on PAAD[31:0]. During the data phases of a transaction, the initiator drives write data, or the target drives read data.                                                                                                                                                                                                                                                                                    |

| PACBE_[3:0]# | I/O  | <b>Bus Command and Byte Enables:</b> These signals are a multiplexed command field and byte enable field. During the address phase or phases of a transaction, the initiator drives the transaction type on PACBE_[3:0]#. For both read and write transactions, the initiator drives byte enables on PACBE_[3:0]# during the data phases.                                                                                                                                                                                                                                               |

| PADEVSEL#    | I/O  | <b>Device Select:</b> The Intel® 6702PXH 64-bit PCI Hub asserts PADEVSEL# to claim a PCI transaction. As a target, the Intel® 6702PXH 64-bit PCI Hub asserts PADEVSEL# when a PCI master peripheral attempts an access to an internal address or an address destined for the PCI Express* interface. As an initiator, PADEVSEL# indicates the response to a Intel® 6702PXH 64-bit PCI Hub-initiated transaction on the PCI bus. PADEVSEL# is tri-stated from the leading edge of PAPCIRST#. PADEVSEL# remains tri-stated by the Intel® 6702PXH 64-bit PCI Hub until driven as a target. |

| PAFRAME#     | I/O  | <b>Frame:</b> PAFRAME# is driven by the Initiator to indicate the beginning and duration of an access. While PAFRAME# is asserted, data transfers continue. When PAFRAME# is negated, the transaction is in the final data phase.                                                                                                                                                                                                                                                                                                                                                       |

| PAGNT_[5:0]# | 0    | <b>PCI Grants:</b> Bus grant output corresponding to request inputs 5 through 0 from the Intel® 6702PXH 64-bit PCI Hub arbiter. This signal indicates that an initiator can start a transaction on the PCI bus.                                                                                                                                                                                                                                                                                                                                                                         |

| PAIRDY#      | I/O  | <b>Initiator Ready:</b> PAIRDY# indicates the ability of the initiator to complete the current data phase of the transaction. A data phase is completed when both PAIRDY# and PATRDY# are sampled asserted.                                                                                                                                                                                                                                                                                                                                                                             |

| PAM66EN      | I/O  | Only relevant when Hot Plug Mode is disabled (HPA_SLOT[3] = 0) or when in one-slot-no-glue hot plug mode (HPA_SLOT[3:0] = 1111).                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              |      | <b>66 MHz Enable:</b> This input signal from the PCI Bus indicates the speed of the PCI Bus. If it is high, the bus speed is 66 MHz; if it is low, the bus speed is 33 MHz. This signal will be used to generate the appropriate clock (33 MHz or 66 MHz) on the PCI Bus.                                                                                                                                                                                                                                                                                                               |

|              |      | Hot Plug Mode Enabled: Not used. The PCI bus will power up as 33 MHz PCI and the Intel® 6702PXH 64-bit PCI Hub will drive this pin low. Also, if software ever writes 00 to the PFREQ Register, the Intel® 6702PXH 64-bit PCI Hub will drive this pin low.                                                                                                                                                                                                                                                                                                                              |

|              |      | Hot Plug Mode Disabled: Controls max frequency (33 MHz or 66 MHz) of the PCI segment when running in conventional PCI mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|              |      | 0 = 33 MHz PCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|              |      | 1 = 66 MHz PCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### Table 2-2. PCI Bus Interface A Signals (Sheet 2 of 2)

| Signal       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAPAR        | I/O  | <b>Parity:</b> Even parity calculated on 36 bits (PAAD[31:0] plus PACBE_[3:0]#). It is calculated on all 36 bits, regardless of the valid byte enables. It is driven identically to the PAAD[31:0] lines, except it is delayed by exactly one PCI clock.                                                                                                                                  |

| PAPCIRST#    | 0    | <ul> <li>PCI Reset: The Intel® 6702PXH 64-bit PCI Hub asserts PAPCIRST# to reset devices that reside on the secondary PCI bus. The Intel® 6702PXH 64-bit PCI Hub asserts PAPCIRST# due to one of the following events:</li> <li>RSTIN# is asserted.</li> <li>The PCI Reset (bit 6) in the Bridge Control Register is set.</li> <li>Connect to the RST# pin of the PCI slot(s).</li> </ul> |

| PAPCIXCAP    | I    | Only relevant when Hot Plug Mode is disabled (HPA_SLOT[3] = 0) or when in one-slot-no-glue hot plug mode (HPA_SLOT[3:0] = 1111).<br><b>PCI-X Capable:</b> This signal indicates whether all devices on the PCI bus are PCI-X devices, so that the Intel® 6702PXH 64-bit PCI Hub can switch into PCI-X mode.                                                                               |

| PAPCLKI      | I    | PCI Clock Input.                                                                                                                                                                                                                                                                                                                                                                          |

| PAPCLKO[6:0] | 0    | PCI Clock Output: These signals provide 33/66/100/133 MHz clock for a PCI/PCI-X device. PAPCLKO[0] goes to slot or device #1, PAPCLKO[1] goes to slot or device #2, etc. PAPCLKO[6] is connected to the PAPCLKI input. Unused PCI Clock outputs should be turned off by BIOS and left as no connects on the system board.                                                                 |

| PAPERR#      | I/O  | <b>Parity Error:</b> PAPERR# is driven by an external PCI device when it receives data that has a parity error. Driven by the Intel® 6702PXH 64-bit PCI Hub when, as an initiator it detects a parity error during a read transaction and as a target during write transactions.                                                                                                          |

| PAPLOCK#     | 0    | <b>PCI Lock:</b> This signal indicates an exclusive bus operation and may require multiple transactions to complete. The Intel® 6702PXH 64-bit PCI Hub asserts PAPLOCK# when it is doing exclusive transactions on the PCI bus. PAPLOCK# is ignored when PCI masters are granted the bus. The Intel® 6702PXH 64-bit PCI Hub does not propagate locked transactions upstream.              |

| PAPME#       | I    | <b>PCI Power Management Event:</b> PCI bus power management event signal. This is a shared open drain signal from all the PCI cards on the corresponding PCI bus segment. This is a level sensitive signal that will be converted to a PME event on the PCI Express bus.                                                                                                                  |

| PAREQ_[5:0]# | I    | PCI Request: Request input into the Intel® 6702PXH 64-bit PCI Hub arbiter.                                                                                                                                                                                                                                                                                                                |

| PASERR#      | I    | <b>System Error:</b> PASERR# can be pulsed active by any PCI device that detects a system error condition except the Intel® 6702PXH 64-bit PCI Hub. The Intel® 6702PXH 64-bit PCI Hub samples PASERR# as an input and conditionally forwards it to the PCI Express interface.                                                                                                             |

| PASTOP#      | I/O  | <b>Stop:</b> PASTOP# indicates that the target is requesting an initiator to stop the current transaction.                                                                                                                                                                                                                                                                                |

| PATRDY#      | I/O  | <b>Target Ready:</b> PATRDY# indicates the ability of the target to complete the current data phase of the transaction. A data phase is completed when both PATRDY# and PAIRDY# are sampled asserted. PATRDY# is tri-stated from the leading edge of PAPCIRST#. PATRDY# remains tri-stated by the Intel® 6702PXH 64-bit PCI Hub until driven as a target.                                 |

### 2.3 PCI Bus Interface 64-bit Extension

|          |      | _                                                                                                                                                         |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal   | Туре | Description                                                                                                                                               |

| PAACK64# | I/O  | PCI Interface Acknowledge 64-bit Transfer: This signal is asserted by the target only when PAREQ64# is asserted by the initiator. It indicates the target |

#### Table 2-3. PCI Bus Interface 64-bit Extension Interface A Signals

|              |     | target only when PAREQ64# is asserted by the initiator. It indicates the target's ability to transfer data using 64 bits. It has the same timing as PADEVSEL#.                                                                                                                                                                                             |

|--------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAAD[63:32]  | I/O | <b>PCI Address/Data:</b> These signals are a multiplexed address and data bus. This bus provides an additional 32 bits to the PCI bus. During the data phases of a transaction, the initiator drives the upper 32 bits of 64-bit write data, or the target drives the upper 32 bits of 64-bit read data, when PAREQ64# and PAACK64# are both asserted.     |

| PACBE_[7:4]# | I/O | <b>Bus Command and Byte Enables (Upper 4 bits):</b> These signals are a multiplexed command field and byte enable field. For both read and write transactions, the initiator will drive byte enables for the PAAD[63:32] data bits on PACBE_[7:4]# during the data phases when PAREQ64# and PAACK64# are both asserted.                                    |

| PAPAR64      | I/O | <b>PCI Interface Upper 32-bits Parity:</b> This signal carries the even parity of the 36 bits of PAAD[63:32] and PACBE_[7:4]# for both address and data phases.                                                                                                                                                                                            |

| PAREQ64#     | I/O | PCI interface Request 64-bit Transfer: This signal is asserted by the initiator to indicate that the initiator is requesting a 64-bit data transfer. It has the same timing as PAFRAME#. When the Intel® 6702PXH 64-bit PCI Hub is the initiator, this signal is an output. When the Intel® 6702PXH 64-bit PCI Hub is the target, this signal is an input. |

### 2.4 Interrupt Interface

This section lists the interrupt interface signals.

#### Table 2-4. Interrupt Interface A Signals

| Signal        | Туре | Description                                                                                                          |

|---------------|------|----------------------------------------------------------------------------------------------------------------------|

| PAIRQ_[15:0]# |      | <b>Interrupt Request Bus:</b> The PAIRQ# lines from PCI interrupts PIRQ[A:D] can be routed to these interrupt lines. |

### 2.5 Hot Plug Interface

#### Table 2-5. General Hot Plug Interface A Signals – All Hot Plug Modes

| Signal        | Туре | Description                                                                                                                                          |

|---------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPA_SLOT[3]   | I    | Enable/Disable PCI Hot Plug Mode:<br>1 = Hot Plug Mode Enabled                                                                                       |

|               |      | 0 = Hot Plug Mode Disabled                                                                                                                           |

| HPA_SLOT[2:0] | I    | Hot Plug Mode / # of PCI Slots: Used in conjunction with HPA_SLOT[3] signal to determine PCI Hot Plug Mode and number of PCI slots on a bus segment. |

|               |      | HPA_SLOT[3:0] = Hot Plug Mode Enable/Disable, # of PCI slots                                                                                         |

|               |      | 0000 = hot plug disabled, 1 slot (optional)                                                                                                          |

|               |      | 0001 = hot plug disabled, 2 slots (optional)                                                                                                         |

|               |      | 0010 = hot plug disabled, 3 slots (optional)                                                                                                         |

|               |      | 0011 = hot plug disabled, 4 slots (optional)                                                                                                         |

|               |      | 0100 = hot plug disabled, 5 slots (optional)                                                                                                         |

|               |      | 0101 = hot plug disabled, 6 slots (optional)                                                                                                         |

|               |      | 0110 = hot plug disabled, 7 slots (optional)                                                                                                         |

|               |      | 0111 = hot plug disabled, 8 slots (optional)                                                                                                         |

|               |      | 1000 = reserved                                                                                                                                      |

|               |      | 1001 = hot plug enabled, 1 slot (parallel mode)                                                                                                      |

|               |      | 1010 = hot plug enabled, 2 slots (parallel mode)                                                                                                     |

|               |      | 1011 = hot plug enabled, 3 slots (serial mode)                                                                                                       |

|               |      | 1100 = hot plug enabled, 4 slots (serial mode)                                                                                                       |

|               |      | 1101 = hot plug enabled, 5 slots (serial mode)                                                                                                       |

|               |      | 1110 = hot plug enabled, 6 slots (serial mode)                                                                                                       |

|               |      | 1111 = hot plug enabled, 1-slot-no-glue (parallel mode)                                                                                              |

#### Table 2-6. Serial Mode Hot Plug Signals – Interface A – 3 to 6 Slots (Sheet 1 of 2)

| Signal        | Туре | Description                                                                                                                                                                                                                                                                                                                                         |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPA_SLOT[3:0] | Ι    | Hot Plug Mode Enable / # of PCI Slots: Used to enable/disable hot plug<br>mode and to determine number of hot plug slots.<br>HPA_SLOT[3:0]:<br>1011 = hot plug enabled, 3 slots (serial mode)<br>1100 = hot plug enabled, 4 slots (serial mode)<br>1101 = hot plug enabled, 5 slots (serial mode)<br>1110 = hot plug enabled, 6 slots (serial mode) |

| HPA_PRST#     | 0    | <b>Primary Bus Reset Out (HPA_PRST#):</b> This is asserted whenever the primary side of the Intel® 6702PXH 64-bit PCI Hub goes through a reset, even if hot plug is disabled. Resets the slot interface logic in hot plug serial mode.                                                                                                              |

| HPA_SIC       | 0    | <b>Serial Input Clock:</b> This signal is normally high. It pulses low to shift external serial input shift register data one bit position. (The shift registers should be similar to standard "74x165" series).                                                                                                                                    |

| HPA_SID       | Ι    | Serial Input Data: Data shifted in from external logic on HPA_SIC.                                                                                                                                                                                                                                                                                  |

#### Table 2-6. Serial Mode Hot Plug Signals – Interface A – 3 to 6 Slots (Sheet 2 of 2)

| Signal   | Туре | Description                                                                                                                                                                                                    |

|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPA_SIL# | 0    | <b>Serial Input Load:</b> This signal is normally high. It pulses low to synchronously parallel load external serial input shift registers on the next rising edge of HPA_SIC.                                 |

| HPA_SOC  | 0    | Serial Output Clock: This signal is normally high. It pulses low to shift internal serial output shift register data one bit position. (The shift registers should be similar to standard "74x164" series.)    |

| HPA_SOD  | 0    | Serial Output Data: Data is shifted out to external logic on HPA_SOC.                                                                                                                                          |

| HPA_SOL  | 0    | Serial Output Non-Reset Latch Load: This signal is normally high. It pulses low to clock external latches (power-enable, clock-enable, slot bus-<br>enable, and LED latches). The high edge acts as the clock. |

| HPA_SOLR | 0    | Serial Output Reset Latch Load: This signal is normally high. It pulses high to clock external latches (Reset latches) reading the serial output shift registers. The high edge acts as the clock.             |

#### Table 2-7. Parallel Mode Hot Plug Signals – Interface A – 1 to 2 Slots (Sheet 1 of 4)

| Signal                     | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPA_SLOT[3:0]              | I    | Hot Plug Mode Enable / # of PCI Slots: Used to enable/disable hot plug<br>mode and to determine number of hot plug slots.<br>HPA_SLOT[3:0]:<br>1111 = hot plug enabled, one-slot-no-glue hot plug mode<br>1001 = hot plug enabled, 1 slot (parallel mode)<br>1010 = hot plug enabled, 2 slots (parallel mode)                                                                                                   |

| HAATNLED_1#                | 0    | Slot 1 Attention LED: Control for attention LED of the first hot plug slot, which is yellow or amber in color. Only used when in one-slot-no-glue, single-slot parallel, or dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1111, 1001, or 1010).                                                                                                                                                             |

| HPA_SOLR/<br>HAATNLED2#    | 0    | Slot 2 Attention LED: Control for attention LED of the second hot plug slot, which is yellow or amber in color. Only used when in dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1010).                                                                                                                                                                                                                      |

| PAGNT_[5]#/<br>HABUSEN_1#  | 0    | <b>Slot 1 Bus Enable:</b> Bus enable signals that connect the PCI bus signals of the first PCI slot to the system bus PCI bus via FET isolation switches. Only used when in single-slot or dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1001 or 1010).                                                                                                                                                     |

| PAGNT_[4]#/<br>HABUSEN_2#  | 0    | <b>Slot 2 Bus Enable:</b> Bus enable signals that connect the PCI bus signals of the second PCI slot to the system bus PCI bus via FET isolation switches. Only used when in dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1010).                                                                                                                                                                           |

| PAIRQ_[8]#/<br>HABUTTON_1# | I    | Slot 1 Attention Button: Optional. Attention button input signal connected to the first hot plug slot's attention button. When low, indicates that the operator has requested attention. If attention button is not implemented, then this input must be wired to a high logic level. Only used when in one-slot-no-glue, single-slot or dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1111, 1001 or 1010). |

#### Table 2-7. Parallel Mode Hot Plug Signals – Interface A – 1 to 2 Slots (Sheet 2 of 4)

| Signal                       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPA_SOL/<br>HABUTTON2#       | 0    | <b>Slot 2 Attention Button:</b> Optional. Attention button input signal connected to the second hot plug slot's attention button. When low, indicates that the operator has requested attention. If attention button is not implemented, then this input must be wired to a high logic level. Only used when in dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1010).                                                                                                                                                                                                                                                                                                                                                                                                              |

| HPA_SIL#/<br>HACLKEN_1#      | 0    | Slot 1 Clock Enable: Clock enable signals that connect the PCI clock signals of the first PCI slot to the system bus PCI bus via FET isolation switches.<br>Only used when in single-slot or dual-slot parallel hot plug mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| HPA_SOD/<br>HACLKEN_2        | 0    | (HPA_SLOT[3:0] = 1001 or 1010).<br><b>Slot 2 Clock Enable:</b> Clock enable signals that connect the PCI clock<br>signals of the second PCI slot to the system bus PCI bus via FET isolation<br>switches. Only used when in dual-slot parallel hot plug mode<br>(HPA_SLOT[3:0] = 1010).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PAIRQ_[11]#/<br>HAM66EN_1    | I    | <b>Slot 1 M66EN:</b> Determines if an add-in card is capable of running at 66 MHz in conventional PCI mode for the first hot plug slot.<br>Only used when in one-slot-no-glue, single-slot parallel, or dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1111, 1001, or 1010).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PAIRQ_[12]#/<br>HAM66EN_2    | I    | <b>Slot 2 M66EN:</b> Determines if an add-in card is capable of running at 66 MHz in conventional PCI mode for the second hot plug slot. Only used when in dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1010).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PAIRQ_[15]#/<br>HAMRL1#      | I    | Slot 1 Manual Retention Latch: Optional. Manually operated retention<br>latch sensor input. A logic low input that is connected directly to the MRL<br>sensor on the first hot plug slot. When asserted it indicates that the MRL<br>latch is closed. If a platform does not support MRL sensors, this must be<br>wired to a low logic level (MRL closed).<br>Only used when in one-slot-no-glue, single-slot parallel, or dual-slot parallel<br>hot plug mode (HPA SLOT[3:0] = 1111, 1001, or 1010).                                                                                                                                                                                                                                                                                 |

| HPA_SLOT[0]/<br>HAMRL_2#     | I    | Slot 2 Manual Retention Latch: Optional. Manually operated retention<br>latch sensor input. A logic low input that is connected directly to the MRL<br>sensor on the second hot plug slot. When asserted it indicates that the MRL<br>latch is closed. If a platform does not support MRL sensors, this must be<br>wired to a low logic level (MRL closed). Only used when in dual-slot parallel<br>hot plug mode (HPA_SLOT[3:0] = 1010).                                                                                                                                                                                                                                                                                                                                             |

| PAIRQ_[10]#/<br>HAPCIXCAP1_1 | I    | Slot 1 PCIXCAP1: Determines if the first hot plug slot is PCI-X capable,<br>and if so, whether it can operate at 133 MHz. PCIXCAP1 and PCIXCAP2<br>represent a decoded version of the three-state PCIXCAP pin present on<br>each slot. PCIXCAP2 represents whether the PCIXCAP pin was ground or<br>not ground (i.e., PCI-X capable), and PCIXCAP1 represents whether the<br>PCIXCAP pin was "low" (66 MHz only) or high (133 MHz capable). The<br>system initially powers up at 33 MHz PCI, and all hot plug slots are scanned<br>by firmware. If the system is capable, the bus is reset to run in the<br>appropriate PCI-X mode. These pins are used only in one-slot-no-glue,<br>single-slot parallel or dual-slot parallel hot plug mode<br>(HPA_SLOT[3:0] = 1111,1001 or 1010). |

#### Table 2-7. Parallel Mode Hot Plug Signals – Interface A – 1 to 2 Slots (Sheet 3 of 4)

| Signal                      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAIRQ_[9]#/<br>HAPCIXCAP2_1 | Γ    | Slot 1 PCIXCAP2: Determines if the first hot plug slot is PCI-X capable,<br>and if so, whether it can operate at 133 MHz. PCIXCAP1 and PCIXCAP2<br>represent a decoded version of the three-state PCIXCAP in present on<br>each slot. PCIXCAP2 represents whether the PCIXCAP pin was ground or<br>not ground (i.e., PCI-X capable), and PCIXCAP1 represents whether the<br>PCIXCAP pin was "low" (66 MHz only) or high (133 MHz capable). The<br>system initially powers up at 33 MHz PCI, and all hot plug slots are scanned<br>by firmware. If the system is capable, the bus is reset to run in the<br>appropriate PCI-X mode. These pins are used only in one-slot-no-glue,<br>single-slot parallel or dual-slot parallel hot plug mode<br>(HPA_SLOT[3:0] = 1111,1001 or 1010). |

| HPA_SID/<br>HAPCIXCAP1_2    | Ι    | <b>Slot 2 PCIXCAP1</b> : Determines if the first hot plug slot is PCI-X capable,<br>and if so, whether it can operate at 133 MHz. PCIXCAP1 and PCIXCAP2<br>represent a decoded version of the three-state PCIXCAP pin present on<br>each slot. PCIXCAP2 represents whether the PCIXCAP pin was ground or<br>not ground (i.e., PCI-X capable), and PCIXCAP1 represents whether the<br>PCIXCAP pin was "low" (66 MHz only) or high (133 MHz capable). The<br>system initially powers up at 33 MHz PCI, and all hot plug slots are scanned<br>by firmware. If the system is capable, the bus is reset to run in the<br>appropriate PCI-X mode. These pins are used only in dual-slot parallel hot<br>plug mode (HPA_SLOT[3:0] = 1010).                                                  |

| HPA_SOC/<br>HAPCIXCAP2_2    | 1    | <b>Slot 2 PCIXCAP2:</b> Determines if the second hot plug slot is PCI-X capable, and if so, whether it can operate at 133 MHz. PCIXCAP1 and PCIXCAP2 represent a decoded version of the three-state PCIXCAP pin present on each slot. PCIXCAP2 represents whether the PCIXCAP pin was ground or not ground (i.e., PCI-X capable), and PCIXCAP1 represents whether the PCIXCAP pin was "low" (66 MHz only) or high (133 MHz capable). The system initially powers up at 33 MHz PCI, and all hot plug slots are scanned by firmware. If the system is capable, the bus is reset to run in the appropriate PCI-X mode. These pins are used only in the dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1010).                                                                         |

| HPA_SLOT[1]/<br>HAPRSNT1_1# | I    | Slot 1 PRESENT1#: Input signal (optional). Used in conjunction with HAPRSNT2_1# to indicate to the Intel® 6702PXH 64-bit PCI Hub whether an add-on card is installed in the first hot plug slot and its power requirements. Only used when in one-slot-no-glue, single-slot or dual-slot parallel hot plug mode (HPA_SLOT[3:0] = 1111, 1001 or 1010).                                                                                                                                                                                                                                                                                                                                                                                                                                |