LMG3522R030 SNOSDF3 – NOVEMBER 2022

# LMG3522R030 650-V 30-mΩ GaN FET With Integrated Driver, Protection, and Temperature Reporting

# 1 Features

Texas

INSTRUMENTS

- 650-V GaN-on-Si FET with integrated gate driver

- Integrated high precision gate bias voltage

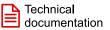

- 200-V/ns FET hold-off

- 2-MHz switching frequency

- 20-V/ns to 150-V/ns slew rate for optimization of switching performance and EMI mitigation

- Operates from 7.5-V to 18-V supply

- Robust protection

- Cycle-by-cycle overcurrent and latched shortcircuit protection with < 100-ns response</li>

- Withstands 720-V surge while hard-switching

- Self-protection from internal overtemperature and UVLO monitoring

- Advanced power management

- Digital temperature PWM output

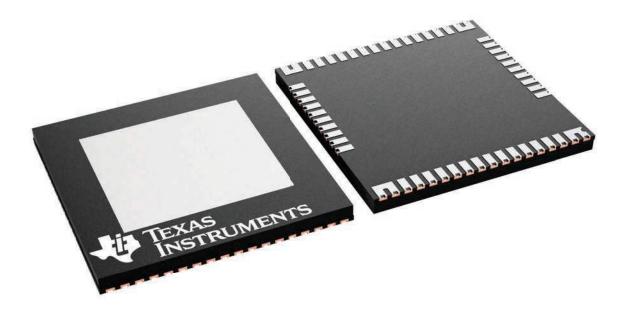

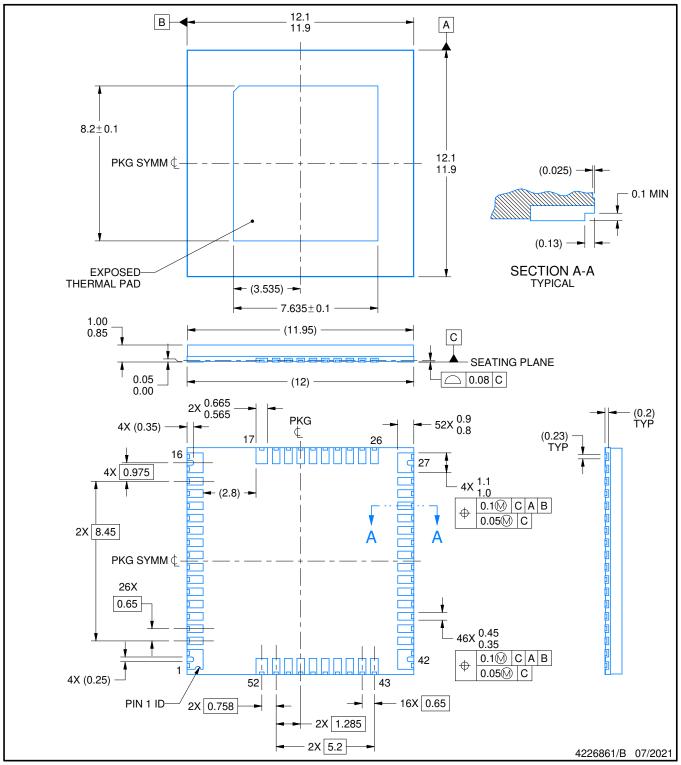

- Top-side cooled 12-mm × 12-mm VQFN package separates electrical and thermal paths for lowest power loop inductance

# 2 Applications

- Switch-mode power converters

- Merchant network and server PSU

- Merchant telecom rectifiers

- Solar inverters and industrial motor drives

- Uninterruptable power supplies

# **3 Description**

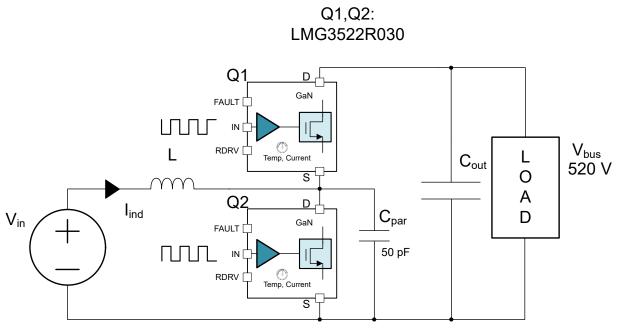

The LMG3522R030 GaN FET with integrated driver and protections is targeting switch-mode power converters and enables designers to achieve new levels of power density and efficiency.

The LMG3522R030 integrates a silicon driver that enables switching speed up to 150 V/ns. TI's integrated precision gate bias results in higher switching SOA compared to discrete silicon gate drivers. This integration, combined with TI's lowinductance package, delivers clean switching and minimal ringing in hard-switching power supply topologies. Adjustable gate drive strength allows control of the slew rate from 20 V/ns to 150 V/ns, which can be used to actively control EMI and optimize switching performance.

Advanced power management features include digital temperature reporting and fault detection. The temperature of the GaN FET is reported through a variable duty cycle PWM output, which simplifies managing device loading. Faults reported include overtemperature, overcurrent, and UVLO monitoring.

**Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)     |  |  |  |  |

|-------------|------------------------|---------------------|--|--|--|--|

| LMG3522R030 | VQFN (52)              | 12.00 mm × 12.00 mm |  |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

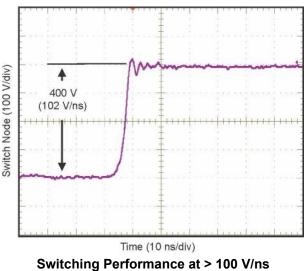

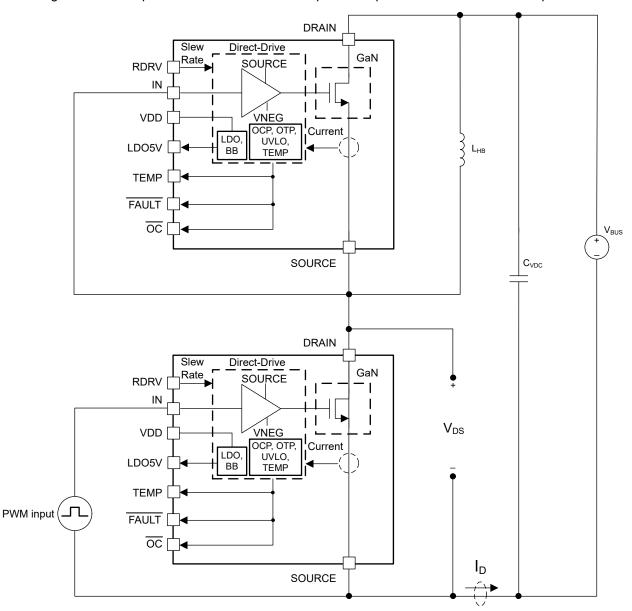

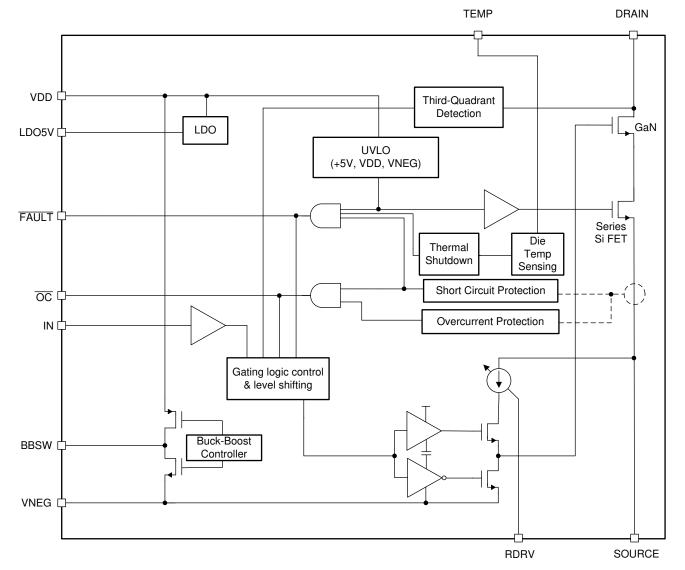

Simplified Block Diagram

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

# **Table of Contents**

| 1 Features                           | 1  |

|--------------------------------------|----|

| 2 Applications                       |    |

| 3 Description                        |    |

| 4 Revision History                   |    |

| 5 Pin Configuration and Functions    | 3  |

| 6 Specifications                     | 4  |

| 6.1 Absolute Maximum Ratings         |    |

| 6.2 ESD Ratings                      |    |

| 6.3 Recommended Operating Conditions | 5  |

| 6.4 Thermal Information              | 5  |

| 6.5 Electrical Characteristics       | 6  |

| 6.6 Switching Characteristics        | 8  |

| 6.7 Typical Characteristics          |    |

| 7 Parameter Measurement Information  | 11 |

| 7.1 Switching Parameters             | 11 |

| 8 Detailed Description               |    |

| 8.1 Overview                         | 13 |

| 8.2 Functional Block Diagram         |    |

| 8.3 Feature Description.             |    |

| 8.4 Start Up Sequence                                 | 23   |

|-------------------------------------------------------|------|

| 8.5 Safe Operation Area (SOA)                         |      |

| 8.6 Device Functional Modes.                          |      |

| 9 Application and Implementation                      |      |

| 9.1 Application Information                           |      |

| 9.2 Typical Application                               |      |

| 9.3 Do's and Don'ts                                   |      |

| 9.4 Power Supply Recommendations                      |      |

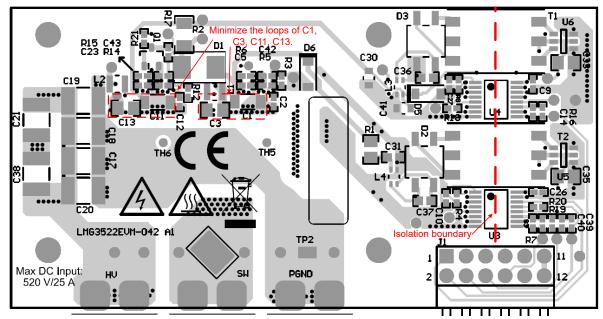

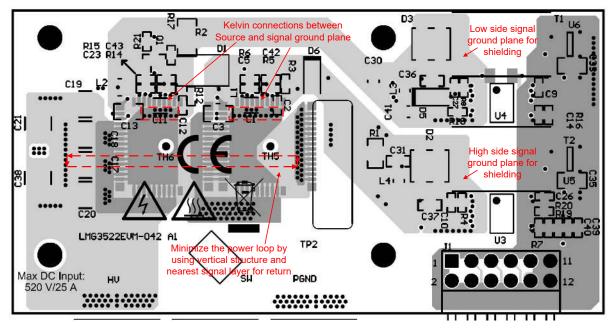

| 9.5 Layout                                            | . 32 |

| 10 Device and Documentation Support                   |      |

| 10.1 Documentation Support                            |      |

| 10.2 Receiving Notification of Documentation Updates. |      |

| 10.3 Support Resources                                |      |

| 10.4 Trademarks                                       |      |

| 10.5 Electrostatic Discharge Caution                  |      |

| 10.6 Export Control Notice                            |      |

| 10.7 Glossary                                         |      |

| 11 Mechanical, Packaging, and Orderable               |      |

| Information                                           | . 36 |

|                                                       |      |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| November 2022 | *        | Initial release. |

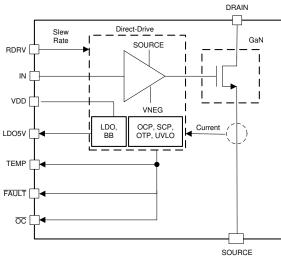

# **5** Pin Configuration and Functions

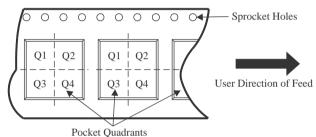

Figure 5-1. RQS Package 52-Pin VQFN (Top View)

#### Table 5-1. Pin Functions

| PIN            |                       | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                              |

|----------------|-----------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NO.                   |                     | DESCRIPTION                                                                                                                                                                                                                                              |

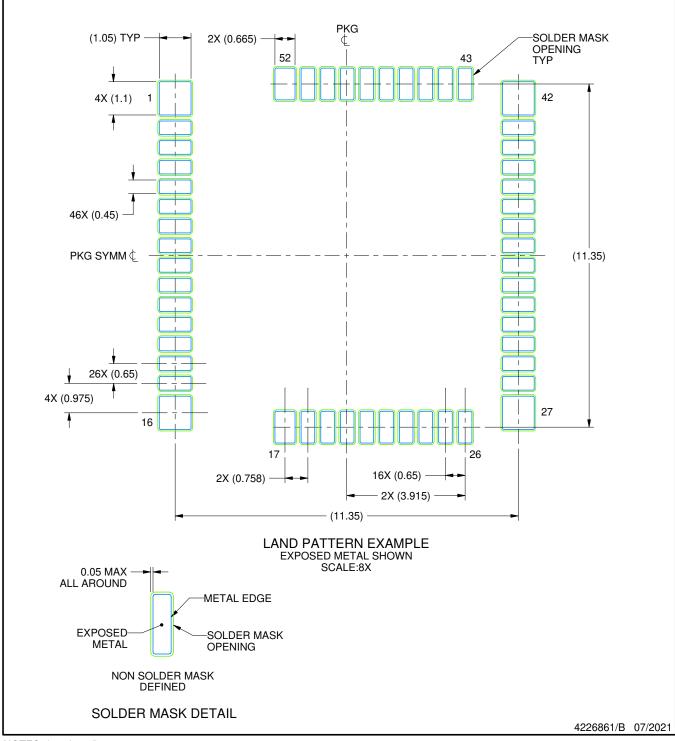

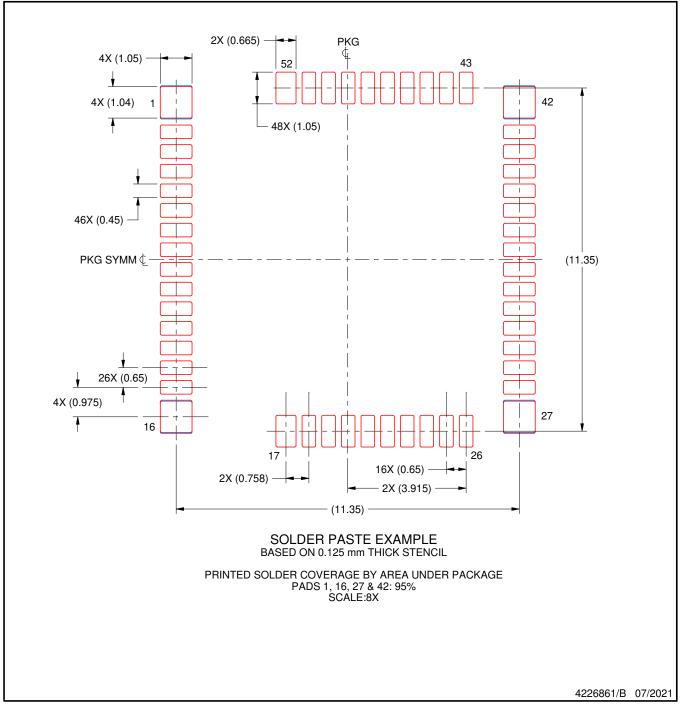

| NC1            | 1, 16                 | _                   | Used to anchor QFN package to PCB. Pins must be soldered to PCB landing pads. The PCB landing pads are non-solder mask defined pads and must not be physically connected to any other metal on the PCB. Internally connected to DRAIN.                   |

| DRAIN          | 2-15                  | Р                   | GaN FET drain. Internally connected to NC1.                                                                                                                                                                                                              |

| NC2            | 17, 27, 43, 47,<br>52 | _                   | Used to anchor QFN package to PCB. Pins must be soldered to PCB landing pads. The PCB landing pads are non-solder mask defined pads and must not be physically connected to any other metal on the PCB. Internally connected to SOURCE, and THERMAL PAD. |

| SOURCE         | 18-26, 28-39          | Р                   | GaN FET source. Internally connected to NC2, and THERMAL PAD.                                                                                                                                                                                            |

| VNEG           | 40, 41                | Р                   | Internal buck-boost converter negative output. Used as the negative supply to turn off the depletion mode GaN FET. Bypass to SOURCE with a $2.2$ - $\mu$ F capacitor.                                                                                    |

| BBSW           | 42                    | Р                   | Internal buck-boost converter switch pin. Connect an inductor from this point to SOURCE.                                                                                                                                                                 |

| VDD            | 44                    | Р                   | Device input supply.                                                                                                                                                                                                                                     |

| IN             | 45                    | I                   | CMOS-compatible non-inverting input used to turn the FET on and off.                                                                                                                                                                                     |

| FAULT          | 46                    | 0                   | Push-pull digital output that asserts low during a fault condition. Refer to Fault Detection for details.                                                                                                                                                |

| <u>OC</u>      | 48                    | 0                   | Push-pull digital output that asserts low during overcurrent and short-circuit fault conditions. Refer to <i>Fault Detection</i> for details.                                                                                                            |

| TEMP           | 49                    | 0                   | Push-pull digital output that gives information about the GaN FET temperature. Outputs a fixed 9-kHz pulsed waveform. The device temperature is encoded as the duty cycle of the waveform.                                                               |

| RDRV           | 50                    | I                   | Drive strength selection pin. Connect a resistor from this pin to SOURCE to set the turn-on drive strength to control slew rate. Tie the pin to SOURCE to enable 150 V/ns and tie the pin to LDO5V to enable 100 V/ns.                                   |

| LDO5V          | 51                    | Р                   | 5-V LDO output for external digital isolator. If using this externally, connect a 0.1-µF or greater capacitor to SOURCE.                                                                                                                                 |

| THERMAL<br>PAD | _                     | —                   | Thermal pad. Internally connected to SOURCE, and NC2.                                                                                                                                                                                                    |

(1) I = input, O = output, P = power

# 6 Specifications

#### 6.1 Absolute Maximum Ratings

Unless otherwise noted: voltages are in respect to SOURCE connected to reference ground<sup>(1)</sup>

|                        |                                                              |                                                 | MIN               | MAX                     | UNIT |

|------------------------|--------------------------------------------------------------|-------------------------------------------------|-------------------|-------------------------|------|

| V <sub>DS</sub>        | Drain-source voltage, FET off                                |                                                 |                   | 650                     | V    |

| V <sub>DS(surge)</sub> | Drain-source voltage, FET switching, surg                    | ge condition <sup>(2)</sup>                     |                   | 720                     | V    |

| V <sub>DS,tr</sub>     | Drain-source transient ringing peak voltage                  | ge, FET off, surge condition <sup>(2) (3)</sup> |                   | 800                     | V    |

|                        | V <sub>DE</sub>                                              | )                                               | -0.3              | 20                      | V    |

|                        | LDC                                                          | D5V                                             | -0.3              | 5.5                     | V    |

|                        | VNI                                                          | EG                                              | -16               | 0.5                     | V    |

|                        | Pin voltage BBS                                              | SW                                              | V <sub>VNEG</sub> | V <sub>VDD</sub> +0.5   | V    |

|                        | IN                                                           |                                                 | -0.3              | 20                      | V    |

|                        | FAU                                                          | JLT, OC, TEMP                                   | -0.3              | V <sub>LDO5V</sub> +0.3 | V    |

|                        | RDI                                                          | RV                                              | -0.3              | 5.5                     | V    |

| I <sub>D(RMS)</sub>    | Drain RMS current, FET on                                    |                                                 |                   | 55                      | А    |

| I <sub>D(pulse)</sub>  | Drain pulsed current, FET on, tp < 10 $\mu$ s <sup>(4)</sup> | 4)                                              | -125              | Internally Limited      | А    |

| I <sub>S(pulse)</sub>  | Source pulsed current, FET off, tp < 1 µs                    |                                                 |                   | 80                      | А    |

| TJ                     | Operating junction temperature <sup>(5)</sup>                |                                                 | -40               | 150                     | °C   |

| T <sub>STG</sub>       | Storage temperature                                          |                                                 | -55               | 150                     | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) See Section 8.3.3 for an explanation of the switching cycle drain-source voltage ratings.

(3) t1 < 200 ns in Figure 8-1.

- (4) The positive pulsed current must remain below the overcurrent threshold to avoid the FET being automatically shut off. The FET drain intrinsic positive pulsed current rating for  $t_p < 10 \ \mu$ s is 120 A.

- (5) Refer to the Electrical and Switching Characteristics Tables for junction temperature test conditions.

#### 6.2 ESD Ratings

|                    |               | PARAMETER                                                             | VALUE | UNIT |

|--------------------|---------------|-----------------------------------------------------------------------|-------|------|

|                    | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>     | ±2000 | V    |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per ANSI/ESDA/JEDEC JS-002 <sup>(2)</sup> | ±500  | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

Unless otherwise noted: voltages are in respect to SOURCE connected to reference ground.

|                         |                                         |                                                                            | MIN | NOM | MAX | UNIT |

|-------------------------|-----------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|------|

|                         | Supply voltage                          | VDD<br>(Maximum switching frequency derated for V <sub>VDD</sub> < 9<br>V) | 7.5 | 12  | 18  | V    |

|                         | Input voltage                           | IN                                                                         | 0   | 5   | 18  | V    |

| I <sub>D(RMS</sub><br>) | Drain RMS current                       |                                                                            |     |     | 38  | А    |

|                         | Positive source current                 | LDO5V                                                                      |     |     | 25  | mA   |

| R <sub>RDRV</sub>       | RDRV to SOURCE resistance from external | slew-rate control resistor                                                 | 0   |     | 500 | kΩ   |

| $C_{VNEG}$              | VNEG to SOURCE capacitance from externa | l bypass capacitor                                                         | 1   |     | 10  | uF   |

| L <sub>BBSW</sub>       | BBSW to SOURCE inductance from external | buck-boost inductor <sup>(1)</sup>                                         | 3   | 4.7 | 10  | uH   |

(1) > 1 A current rating is recommended.

#### 6.4 Thermal Information

|                       |                                           | LMG3522R030 |      |

|-----------------------|-------------------------------------------|-------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>             | RQS (VQFN)  | UNIT |

|                       |                                           | 52 PINS     |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance | 0.28        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### **6.5 Electrical Characteristics**

Unless otherwise noted: voltage, resistance, capacitance, and inductance are in respect to SOURCE connected with reference ground; –40 °C ≤  $T_J$  ≤ 125 °C; V<sub>DS</sub> = 520 V; 9 V ≤ V<sub>VDD</sub> ≤ 18 V; V<sub>IN</sub> = 0 V; RDRV connected to LDO5V; L<sub>BBSW</sub> = 4.7 µH

|                                | PARAMETER                                                                                                        | TEST CONDITIONS                                                        | MIN  | TYP  | MAX  | UNIT |

|--------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| GAN PO                         | WER TRANSISTOR                                                                                                   |                                                                        |      |      |      |      |

|                                | <b>_</b>                                                                                                         | V <sub>IN</sub> = 5 V, T <sub>J</sub> = 25°C                           |      | 26   | 35   | mΩ   |

| R <sub>DS(on)</sub>            | Drain-source on resistance                                                                                       | V <sub>IN</sub> = 5 V, T <sub>J</sub> = 125°C                          |      | 45   |      | mΩ   |

|                                | Third-quadrant mode source-drain                                                                                 | I <sub>S</sub> = 0.1 A                                                 |      | 3.6  |      | V    |

| V <sub>SD</sub>                | voltage                                                                                                          | I <sub>S</sub> = 20 A                                                  | 3    | 5    |      | V    |

|                                | Desire to all a second second                                                                                    | V <sub>DS</sub> = 650 V, T <sub>J</sub> = 25°C                         |      | 1    |      | uA   |

| DSS                            | Drain leakage current                                                                                            | V <sub>DS</sub> = 650 V, T <sub>J</sub> = 125°C                        |      | 10   |      | uA   |

| C <sub>OSS</sub>               | Output capacitance                                                                                               | V <sub>DS</sub> = 400 V                                                |      | 235  |      | pF   |

| C <sub>O(er)</sub>             | Energy related effective output<br>capacitance                                                                   |                                                                        |      | 320  |      | pF   |

| C <sub>O(tr)</sub>             | Time related effective output capacitance                                                                        | $V_{DS} = 0 V$ to 400 V                                                |      | 460  |      | pF   |

| Q <sub>OSS</sub>               | Output charge                                                                                                    |                                                                        |      | 190  |      | nC   |

| Q <sub>RR</sub>                | Reverse recovery charge                                                                                          |                                                                        |      | 0    |      | nC   |

| VDD - SU                       | PPLY CURRENTS                                                                                                    |                                                                        | ÷    |      |      |      |

|                                | V <sub>DD</sub> quiescent current                                                                                | V <sub>VDD</sub> = 12 V, V <sub>IN</sub> = 0 V or 5V                   |      | 700  | 1200 | uA   |

|                                | V <sub>DD</sub> operating current                                                                                | V <sub>VDD</sub> = 12 V, f <sub>IN</sub> = 140 kHz, soft-<br>switching |      | 15.5 | 20   | mA   |

| виск во                        | DOST CONVERTER                                                                                                   | -                                                                      |      |      |      |      |

|                                | VNEG output voltage                                                                                              | VNEG sinking 50 mA                                                     |      | -14  |      | V    |

| I <sub>BBSW,PK(I</sub><br>ow)  | Peak BBSW sourcing current at low peak<br>current mode setting<br>(Peak external buck-boost inductor<br>current) |                                                                        | 0.3  | 0.4  | 0.5  | A    |

| I <sub>BBSW,PK(</sub><br>high) | Peak BBSW sourcing current at low peak<br>current mode setting<br>(Peak external buck-boost inductor<br>current) |                                                                        | 0.8  | 1    | 1.2  | A    |

|                                | High peak current mode setting enable –<br>IN positive-going threshold frequency                                 |                                                                        | 280  | 420  | 515  | kHz  |

| LDO5V                          |                                                                                                                  |                                                                        |      |      |      |      |

|                                | Output voltage                                                                                                   | LDO5V sourcing 25 mA                                                   | 4.75 | 5    | 5.25 | V    |

|                                | Short-circuit current                                                                                            |                                                                        | 25   | 50   | 100  | mA   |

| IN                             |                                                                                                                  |                                                                        | ÷    |      |      |      |

| V <sub>IN,IT+</sub>            | Positive-going input threshold voltage                                                                           |                                                                        | 1.7  | 1.9  | 2.45 | V    |

| V <sub>IN,IT-</sub>            | Negative-going input threshold voltage                                                                           |                                                                        | 0.7  | 1.0  | 1.3  | V    |

|                                | Input threshold hysteresis                                                                                       |                                                                        | 0.7  | 0.9  | 1.3  | V    |

|                                | Input pulldown resistance                                                                                        | V <sub>IN</sub> = 2 V                                                  | 100  | 150  | 200  | kΩ   |

| FAULT, C                       | C, TEMP – OUPUT DRIVE                                                                                            |                                                                        |      |      |      |      |

|                                | Low-level output voltage                                                                                         | Output sinking 8 mA                                                    |      | 0.16 | 0.4  | V    |

|                                | High-level output voltage                                                                                        | Output sourcing 8 mA, Measured as $V_{LDO5V} - V_{O}$                  |      | 0.2  | 0.45 | V    |

| VDD, VNI                       | EG – UNDER VOLTAGE LOCKOUT                                                                                       |                                                                        |      |      |      |      |

| V <sub>VDD,T+</sub><br>(UVLO)  | VDD UVLO – positive-going threshold voltage                                                                      |                                                                        | 6.4  | 7    | 7.6  | V    |

|                                | VDD UVLO – negative-going threshold voltage                                                                      |                                                                        | 6    | 6.5  | 7.1  | V    |

#### 6.5 Electrical Characteristics (continued)

Unless otherwise noted: voltage, resistance, capacitance, and inductance are in respect to SOURCE connected with reference ground; –40 °C  $\leq T_J \leq 125$  °C;

$V_{DS} = 520$  V;  $9 \text{ V} \le V_{VDD} \le 18$  V;  $V_{IN} = 0$  V; RDRV connected to LDO5V;  $L_{BBSW} = 4.7 \text{ }\mu\text{H}$

|                        | PARAMETER                                                       | TEST CONDITIONS                                                                                                                                                                                                                 | MIN   | TYP    | MAX   | UNIT |

|------------------------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|------|

|                        | VDD UVLO – Input threshold voltage hysteresis                   |                                                                                                                                                                                                                                 |       | 510    |       | mV   |

|                        | VNEG UVLO – negative-going threshold voltage                    |                                                                                                                                                                                                                                 | -13.6 | -13.0  | -12.3 | V    |

|                        | VNEG UVLO – positive-going threshold voltage                    |                                                                                                                                                                                                                                 | -13.3 | -12.75 | -12.1 | V    |

| GATE DR                | IVER                                                            |                                                                                                                                                                                                                                 |       |        |       |      |

|                        |                                                                 | From $V_{DS}$ < 320 V to $V_{DS}$ < 80 V, RDRV<br>disconnected from LDO5V, $R_{RDRV}$ = 300<br>$k\Omega$ , $T_{J}$ = 25°C, $V_{BUS}$ = 400 V, $L_{HB}$ current<br>= 10 A, see Figure 7-1                                        |       | 20     |       | V/ns |

|                        | Turn-on slew rate                                               | From $V_{DS} < 320$ V to $V_{DS} < 80$ V, RDRV<br>tied to LDO5V, $T_J = 25^{\circ}$ C, $V_{BUS} = 400$ V,<br>$L_{HB}$ current = 10 A, see Figure 7-1                                                                            |       | 90     |       | V/ns |

|                        |                                                                 | From V <sub>DS</sub> < 320 V to V <sub>DS</sub> < 80 V, RDRV<br>disconnected from LDO5V, R <sub>RDRV</sub> = 0 $\Omega$ ,<br>T <sub>J</sub> = 25°C, V <sub>BUS</sub> = 400 V, L <sub>HB</sub> current = 10<br>A, see Figure 7-1 |       | 150    |       | V/ns |

|                        | Maximum GaN FET switching frequency.                            | $V_{NEG}$ rising to > –13.25 V, soft-switched, maximum switching frequency derated for $V_{VDD}$ < 9 V                                                                                                                          | 2     |        |       | MHz  |

| FAULTS                 | 1                                                               |                                                                                                                                                                                                                                 |       |        |       |      |

| T(OC)                  | DRAIN overcurrent fault – threshold<br>current                  |                                                                                                                                                                                                                                 | 60    | 70     | 80    | А    |

| T(SC)                  | DRAIN short-circuit fault – threshold current                   |                                                                                                                                                                                                                                 | 75    | 90     | 105   | А    |

| di/dt <sub>T(SC)</sub> | di/dt threshold between overcurrent and short-circuit faults    |                                                                                                                                                                                                                                 | 150   |        |       | A/µs |

|                        | GaN temperature fault – postive-going threshold temperature     |                                                                                                                                                                                                                                 |       | 175    |       | °C   |

|                        | GaN temperature fault – threshold temperature hysteresis        |                                                                                                                                                                                                                                 |       | 30     |       | °C   |

|                        | Driver temperature fault – positive-going threshold temperature |                                                                                                                                                                                                                                 |       | 185    |       | °C   |

|                        | Driver Temperature fault – threshold<br>temperature hysteresis  |                                                                                                                                                                                                                                 |       | 20     |       | °C   |

| ГЕМР                   |                                                                 |                                                                                                                                                                                                                                 |       |        |       |      |

|                        | Output Frequency                                                |                                                                                                                                                                                                                                 | 4.3   | 9      | 14    | kHz  |

|                        |                                                                 | GaN T <sub>J</sub> = 150°C                                                                                                                                                                                                      |       | 82     |       | %    |

|                        | Output PWM Duty Cycle                                           | GaN T <sub>J</sub> = 125°C                                                                                                                                                                                                      | 58.5  | 64.6   | 70    | %    |

|                        |                                                                 | GaN T <sub>J</sub> = 85°C                                                                                                                                                                                                       | 36.2  | 40     | 43.7  | %    |

|                        |                                                                 | GaN T <sub>J</sub> = 25°C                                                                                                                                                                                                       | 0.3   | 3      | 6     | %    |

| DEAL-DI                | ODE MODE CONTROL                                                |                                                                                                                                                                                                                                 |       |        |       |      |

| √ <sub>T(3rd)</sub>    | Drain-source third-quadrant detection – threshold voltage       |                                                                                                                                                                                                                                 | -0.15 | 0      | 0.15  | V    |

| L                      | Drain zero-current detection – threshold                        | $0^{\circ}C \le T_{J} \le 125^{\circ}C$                                                                                                                                                                                         | -0.2  | 0      | 0.2   | А    |

| T(ZC)                  | current                                                         | $-40^{\circ}C \le T_{J} \le 0^{\circ}C$                                                                                                                                                                                         | -0.35 | 0      | 0.35  | А    |

#### 6.6 Switching Characteristics

Unless otherwise noted: voltage, resistance, capacitance, and inductance are respect to SOURCE connected with reference ground; –40 °C  $\leq T_J \leq 125$  °C; 9 V  $\leq V_{VDD} \leq 18$  V; V<sub>IN</sub> = 0 V; RDRV connected to LDO5V; L<sub>BBSW</sub> = 4.7 µH

|                                | PARAMETER                                                                  | TEST CONDITIONS                                                                                                                                                                                                                                                | MIN | TYP | MAX | UNIT |

|--------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SWITCH                         | ING TIMES                                                                  |                                                                                                                                                                                                                                                                |     |     |     |      |

| t <sub>d(on)</sub><br>(Idrain) | Drain-current turn-on delay time                                           | $ \begin{array}{ c c c c } From V_{IN} > V_{IN,IT+} \mbox{ to } I_D > 1 \mbox{ A}, \mbox{ V}_{BUS} = \\ 400 \mbox{ V},  L_{HB} \mbox{ current} = 10 \mbox{ A}, \mbox{ see Figure 7-1} \\ and \mbox{ Figure 7-2} \\ \end{array} $                               |     | 28  | 42  | ns   |

| t <sub>d(on)</sub>             | Turn-on delay time                                                         | From V <sub>IN</sub> > V <sub>IN,IT+</sub> to V <sub>DS</sub> < 320 V, V <sub>BUS</sub> = 400 V, L <sub>HB</sub> current = 10 A, see Figure 7-1 and Figure 7-2                                                                                                 |     | 33  | 54  | ns   |

| t <sub>r(on)</sub>             | Turn-on rise time                                                          | From $V_{DS}$ < 320 V to $V_{DS}$ < 80 V, $V_{BUS}$ = 400 V, $L_{HB}$ current = 10 A, see Figure 7-1 and Figure 7-2                                                                                                                                            |     | 2.8 | 4.3 | ns   |

| t <sub>d(off)</sub>            | Turn-off delay time                                                        | From $V_{IN} < V_{IN,IT-}$ to $V_{DS} > 80$ V, $V_{BUS} =$<br>400 V, $L_{HB}$ current = 10 A, see Figure 7-1<br>and Figure 7-2                                                                                                                                 |     | 48  | 69  | ns   |

| t <sub>f(off)</sub>            | Turn-off fall time <sup>(1)</sup>                                          | From $V_{DS}$ > 80 V to $V_{DS}$ > 320 V, $V_{BUS}$ = 400 V, $L_{HB}$ current = 10 A, see Figure 7-1 and Figure 7-2                                                                                                                                            |     |     | 22  | ns   |

|                                | Minimum IN high pulse-width for FET turn-on                                | $V_{IN}$ rise/fall times < 1 ns, $V_{DS}$ falls to < 200 V, $V_{BUS}$ = 400 V, $L_{HB}$ current = 10 A, see Figure 7-1                                                                                                                                         |     |     | 24  | ns   |

| STARTU                         | P TIMES                                                                    | · · · ·                                                                                                                                                                                                                                                        |     |     |     |      |

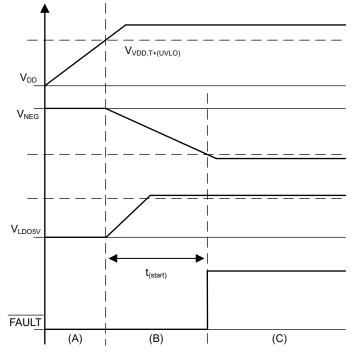

| t <sub>(start)</sub>           | Driver start-up time                                                       | $\label{eq:VDD} \begin{array}{l} \mbox{From $V_{VDD}$ > $V_{VDD,T+}$} \\ \mbox{$(UVLO)$ to FAULT high, $C_{LDO5V}$ = 100$} \\ \mbox{nF, $C_{VNEG}$ = $2.2 $ $\mu$F at $0$-V$ bias linearly} \\ \mbox{decreasing to $1.5 $ $\mu$F at $15$-V$ bias} \end{array}$ |     | 310 | 470 | us   |

| FAULT T                        | IMES                                                                       |                                                                                                                                                                                                                                                                |     |     |     |      |

| t <sub>off(OC)</sub>           | Overcurrent fault FET turn-off time, FET on before overcurrent             | $V_{IN}$ = 5 V, From $I_D$ > $I_{T(OC)}$ to $I_D$ < 50 A, $I_D$<br>di/dt = 100 A/µs                                                                                                                                                                            |     | 115 | 170 | ns   |

| t <sub>off(SC)</sub>           | Short-circuit current fault FET turn-off time, FET on before short circuit | $V_{IN}$ = 5 V, From $I_D$ > $I_{T(SC)}$ to $I_D$ < 50 A, $I_D$<br>di/dt = 700 A/µs                                                                                                                                                                            |     | 65  | 100 | ns   |

|                                | Overcurrent fault FET turn-off time, FET turning on into overcurrent       | From $I_D > I_{T(OC)}$ to $I_D < 50$ A                                                                                                                                                                                                                         |     | 200 | 250 | ns   |

|                                | Short-circuit fault FET turn-off time, FET turning on into short circuit   | From $I_D > I_{T(SC)}$ to $I_D < 50$ A                                                                                                                                                                                                                         |     | 80  | 180 | ns   |

|                                | IN reset time to clear FAULT latch                                         | From $V_{IN} < V_{IN,IT-}$ to FAULT high                                                                                                                                                                                                                       | 250 | 380 | 580 | us   |

| t <sub>(window)</sub><br>(OC)  | Overcurrent fault to short-circuit fault<br>window time                    |                                                                                                                                                                                                                                                                |     | 50  |     | ns   |

| IDEAL-D                        | IODE MODE CONTROL TIMES                                                    |                                                                                                                                                                                                                                                                |     |     |     |      |

|                                | Ideal-diode mode FET turn-on time                                          | $V_{DS} < V_{T(3rd)}$ to FET turn-on, $V_{DS}$ being discharged by half-bridge configuration inductor at 5 A                                                                                                                                                   |     | 50  | 65  | ns   |

|                                | Ideal-diode mode FET turn-off time                                         | I <sub>D</sub> > I <sub>T(ZC)</sub> to FET turn-off, I <sub>D</sub> di/dt<br>= 100 A/μs created with a half-bridge<br>configuration                                                                                                                            |     | 55  | 76  | ns   |

|                                | Overtemperature-shutdown ideal-diode mode IN falling blanking time         |                                                                                                                                                                                                                                                                | 150 | 230 | 360 | ns   |

(1) During turn-off, V<sub>DS</sub> rise time is the result of the resonance of C<sub>OSS</sub> and loop inductance as well as load current.

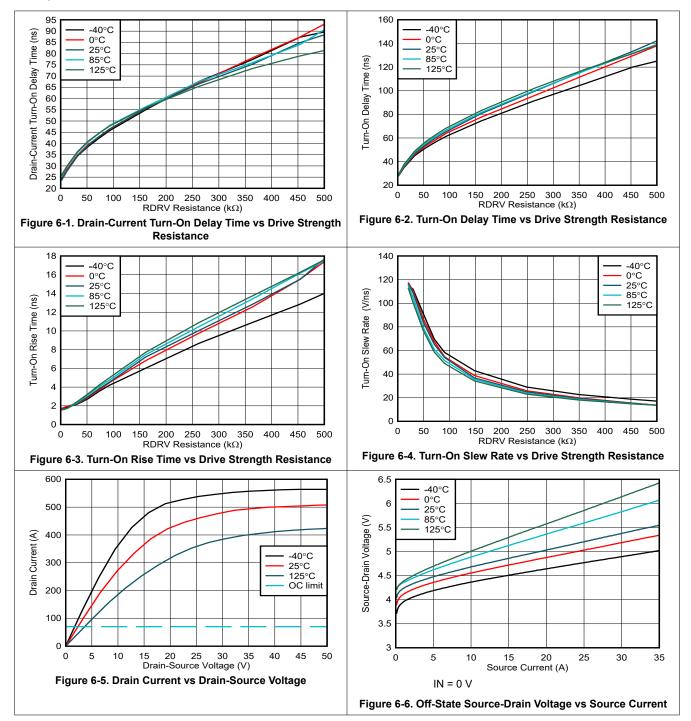

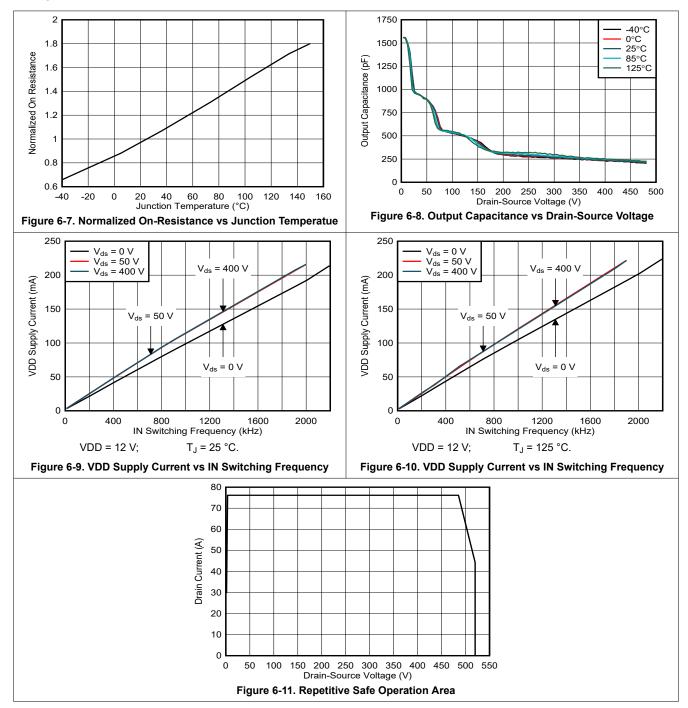

# 6.7 Typical Characteristics

#### 6.7 Typical Characteristics (continued)

# 7 Parameter Measurement Information

#### 7.1 Switching Parameters

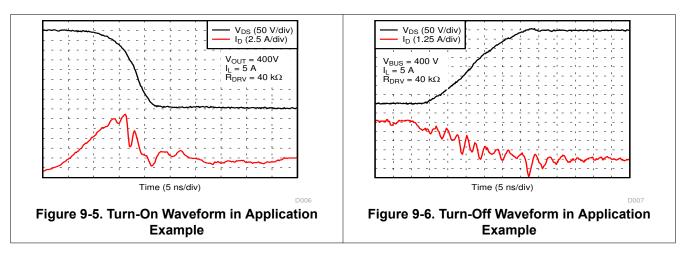

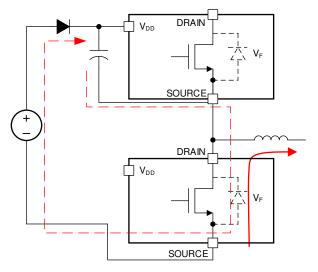

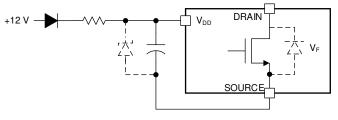

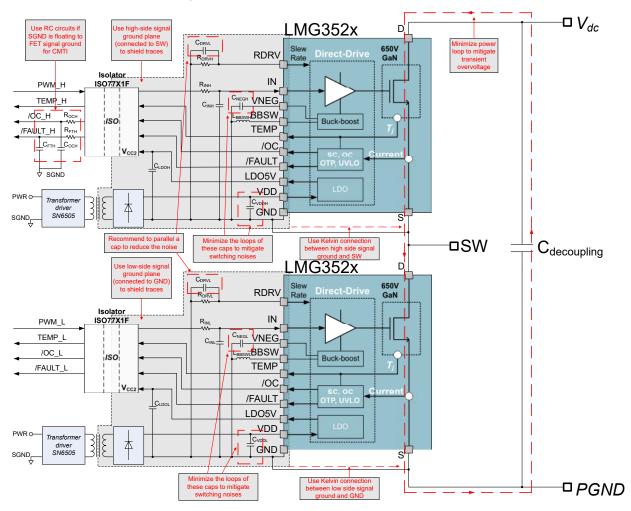

Figure 7-1 shows the circuit used to measure most switching parameters. The top device in this circuit is used to re-circulate the inductor current and functions in third-quadrant mode only. The bottom device is the active device that turns on to increase the inductor current to the desired test current. The bottom device is then turned off and on to create switching waveforms at a specific inductor current. Both the drain current (at the source) and the drain-source voltage is measured. Figure 7-2 shows the specific timing measurement. TI recommends to use the half-bridge as a double pulse tester. Excessive third-quadrant operation can overheat the top device.

Figure 7-1. Circuit Used to Determine Switching Parameters

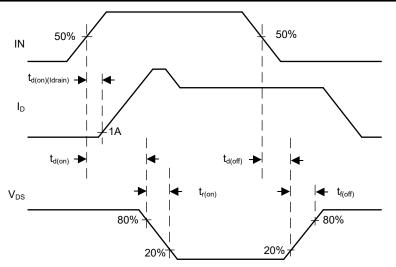

Figure 7-2. Measurement to Determine Propagation Delays and Slew Rates

#### 7.1.1 Turn-On Times

The turn-on transition has three timing components: drain-current turn-on delay time, turn-on delay time, and turn-on rise time. The drain-current turn-on delay time is from when IN goes high to when the GaN FET drain-current reaches 1 A. The turn-on delay time is from when IN goes high to when the drain-source voltage falls 20% below the bus voltage. Finally, the turn-on rise time is from when drain-source voltage falls 20% below the bus voltage to when the drain-source voltage falls 80% below the bus voltage. Note that the turn-on rise time is the same as the  $V_{DS}$  80% to 20% fall time. All three turn-on timing components are a function of the RDRV pin setting.

#### 7.1.2 Turn-Off Times

The turn-off transition has two timing components: turn-off delay time, and turn-off fall time. The turn-off delay time is from when IN goes low to when the drain-source voltage rises to 20% of the bus voltage. The turn-off fall time is from when the drain-source voltage rises to 20% of the bus voltage to when the drain-source voltage rises to 80% of the bus voltage. Note that the turn-off fall time is the same as the  $V_{DS}$  20% to 80% rise time. The turn-off timing components are independent of the RDRV pin setting, but heavily dependent on the L<sub>HB</sub> load current.

#### 7.1.3 Drain-Source Turn-On Slew Rate

The drain-source turn-on slew rate, measured in volts per nanosecond, is the inverse of the turn-on rise time or equivalently the inverse of the  $V_{DS}$  80% to 20% fall time. The RDRV pin is used to program the slew rate.

# 8 Detailed Description

#### 8.1 Overview

The LMG3522R030 is a high-performance power GaN device with integrated gate driver. The GaN device offers zero reverse recovery and ultra-low output capacitance, which enables high efficiency in bridge-based topologies. Direct Drive architecture is applied to control the GaN device directly by the integrated gate driver. This architecture provides superior switching performance compared to the traditional cascode approach and helps solve a number of challenges in GaN applications.

The integrated driver ensures the device stays off for high drain slew rates. The integrated driver also protects the GaN device from overcurrent, short-circuit, undervoltage, and overtemperature. Regarding fault signal reporting, LMG3522R030 provides different reporting method which is shown in Table 8-1. Refer to *Fault Detection* for more details. The integrated driver is also able to sense the die temperature and send out the temperature signal through a modulated PWM signal.

Unlike Si MOSFETs, GaN devices do not have a p-n junction from source to drain and thus have no reverse recovery charge. However, GaN devices still conduct from source to drain similar to a p-n junction body diode, but with higher voltage drop and higher conduction loss. Therefore, source-to-drain conduction time must be minimized while the LMG3522R030 GaN FET is turned off.

#### 8.2 Functional Block Diagram

#### 8.3 Feature Description

The LMG3522R030 includes advanced features to provide superior switching performance and converter efficiency.

#### 8.3.1 GaN FET Operation Definitions

For the purposes of this data sheet, the following terms are defined below. The SOURCE pin is assumed to be at 0 V for these definitions.

First-Quadrant Current = Positive current flowing internally from the DRAIN pin to the SOURCE pin.

**Third-Quadrant Current** = Positive current flowing internally from the SOURCE pin to the DRAIN pin.

First-Quadrant Voltage = Drain pin voltage – Source pin voltage = Drain pin voltage

Third-Quadrant Voltage = SOURCE pin voltage - DRAIN pin voltage = -DRAIN pin voltage

**FET On-State** = FET channel is at rated  $R_{DS(on)}$ . Both first-quadrant current and third-quadrant current can flow at rated  $R_{DS(on)}$ .

For LMG3522R030 in **On-State**, GaN FET internal gate voltage is held at the SOURCE pin voltage to achieve rated  $R_{DS(on)}$ . The GaN FET channel is at rated  $R_{DS(on)}$  with  $V_{GS}$  = 0 V because the LMG3522R030 GaN FET is a depletion mode FET.

**FET Off-State** = FET channel is fully off for positive first-quadrant voltage. No first-quadrant current can flow. While first-quadrant current cannot flow in the FET Off-State, third-quadrant current still flows if the DRAIN voltage is taken sufficiently negative (positive third-quadrant voltage). For devices with an intrinsic p-n junction body diode, current flow begins when the DRAIN voltage drops enough to forward bias the p-n junction.

GaN FETS do not have an intrinsic p-n junction body diode. Instead, current flows because the GaN FET channel turns back on. In this case, the DRAIN pin becomes the electrical source and the SOURCE pin becomes the electrical drain. To enhance the channel in third-quadrant, the DRAIN (electrical source) voltage must be taken sufficiently low to establish a  $V_{GS}$  voltage greater than the GaN FET threshold voltage. The GaN FET channel is operating in saturation and only turns on enough to support the third-quadrant current as its saturated current.

For LMG3522R030 in **Off-State**, GaN FET internal gate voltage is held at the VNEG pin voltage to block all first-quadrant current. The VNEG voltage is lower than the GaN FET negative threshold voltage to cut off the channel.

To enhance the channel in off-state third quadrant, the LMG3522R030 DRAIN (electrical source) voltage must be taken sufficiently close to VNEG to establish a  $V_{GS}$  voltage greater than the GaN FET threshold voltage. Again, because the LMG3522R030 GaN FET is a depletion mode FET with a negative threshold voltage, this means the GaN FET turns on with DRAIN (electrical source) voltage between 0 V and VNEG. The typical off-state third-quadrant voltage is 5 V for third-quadrant current at 20 A. Thus, the off-state third-quadrant losses for the LMG3522R030 are significantly higher than a comparable power device with an intrinsic p-n junction body diode.

#### 8.3.2 Direct-Drive GaN Architecture

The LMG3522R030 uses a series Si FET to ensure the power IC stays off when VDD bias power is not applied. When the VDD bias power is off, the series Si FET is interconnected with the GaN device in a cascode mode, which is shown in the *Functional Block Diagram*. The gate of the GaN device is held within a volt of the series Si FET's source. When a high voltage is applied on the drain and the silicon FET blocks the drain voltage, the V<sub>GS</sub> of the GaN device decreases until the GaN device passes the threshold voltage. Then, the GaN device is turned off and blocks the remaining major part of drain voltage. There is an internal clamp to make sure that the V<sub>DS</sub> of the Si FET does not exceed its maximum rating. This feature avoids the avalanche of the series Si FET when there is no bias power.

When LMG3522R030 is powered up with VDD bias power, the internal buck-boost converter generates a negative voltage ( $V_{VNEG}$ ) that is sufficient to directly turn off the GaN device. In this case, the series Si FET is held on and the GaN device is gated directly with the negative voltage.

Comparing with traditional cascode drive GaN architecture, where the GaN gate is grounded and the Si MOSFET gate is being driven to control the GaN device, direct-drive configuration has multiple advantages. First, as the Si MOSFET does need to switch in every switching cycle, GaN gate-to-source charge ( $Q_{GS}$ ) is lower and there's no Si MOSFET reverse-recovery related losses. Second, the voltage distribution between the GaN and Si MOSFET in off-mode in a cascode configuration can cause the MOSFET to avalanche due to high GaN drain-to-source capacitance ( $C_{DS}$ ). Finally, the switching slew rate in direct-drive configuration can be controlled while cascode drive cannot. More information about the direct-drive GaN architecture can be found in Direct-drive configuration for GaN devices.

#### 8.3.3 Drain-Source Voltage Capability

Due to the silicon FET's long reign as the dominant power-switch technology, many designers are unaware that the headline drain-source voltage cannot be used as an equivalent point to compare devices across technologies. The headline drain-source voltage of a silicon FET is set by the avalanche breakdown voltage. The headline drain-source voltage of a GaN FET is set by the long term reliability with respect to data sheet specifications.

Exceeding the headline drain-source voltage of a silicon FET can lead to immediate and permanent damage. Meanwhile, the breakdown voltage of a GaN FET is much higher than the headline drain-source voltage. For example, the breakdown voltage of the LMG3522R030 is more than 800 V.

A silicon FET is usually the weakest link in a power application during an input voltage surge. Surge protection circuits must be carefully designed to ensure the silicon FET avalanche capability is not exceeded because it is not feasible to clamp the surge below the silicon FET breakdown voltage. Meanwhile, it is easy to clamp the surge voltage below a GaN FET breakdown voltage. In fact, a GaN FET can continue switching during the surge event which means output power is safe from interruption.

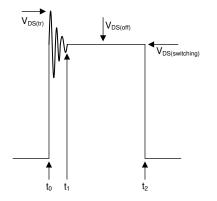

The LMG3522R030 drain-source capability is explained with the assistance of Figure 8-1. The figure shows the drain-source voltage versus time for a GaN FET for a single switch cycle in a switching application. No claim is made about the switching frequency or duty cycle.

Figure 8-1. Drain-Source Voltage Switching Cycle

The waveform starts before  $t_0$  with the FET in the on state. At  $t_0$  the GaN FET turns off and parasitic elements cause the drain-source voltage to ring at a high frequency. The peak ring voltage is designated  $V_{DS(tr)}$ . The high frequency ringing has damped out by  $t_1$ . Between  $t_1$  and  $t_2$  the FET drain-source voltage is set by the characteristic response of the switching application. The characteristic is shown as a flat line, but other responses are possible. The voltage between  $t_1$  and  $t_2$  is designated  $V_{DS(off)}$ . At  $t_2$  the GaN FET is turned on at a non-zero drain-source voltage. The drain-source voltage at  $t_2$  is designated  $V_{DS(switching)}$ . Unique  $V_{DS(tr)}$ ,  $V_{DS(off)}$  and  $V_{DS(switching)}$  parameters are shown because each can contribute to stress over the lifetime of the GaN FET.

The LMG3522R030 drain-source surge voltage capability is seen with the absolute maximum ratings  $V_{DS(tr)(surge)}$  and  $V_{DS(surge)}$  in the *Specifications* where  $V_{DS(tr)(surge)}$  maps to  $V_{DS(tr)}$  in Figure 8-1 and  $V_{DS(surge)}$  maps to both  $V_{DS(off)}$  and  $V_{DS(switching)}$  in Figure 8-1. More information about the surge capability of TI GaN FETs is found in *A New Approach to Validate GaN FET Reliability to Power-line Surges Under Use-conditions.*

Copyright © 2022 Texas Instruments Incorporated

#### 8.3.4 Internal Buck-Boost DC-DC Converter

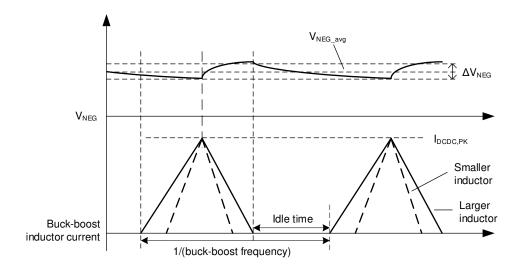

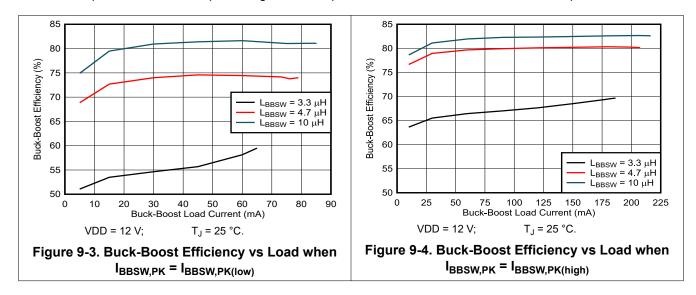

An internal inverting buck-boost converter generates a regulated negative rail for the turn-off supply of the GaN device. The buck-boost converter is controlled by a peak current mode, hysteretic controller. In normal operation, the converter remains in discontinuous-conduction mode, but can enter continuous-conduction mode during start-up. The converter is controlled internally and requires only a single surface-mount inductor and output bypass capacitor. Typically, the converter is designed to use a 4.7 µH inductor and a 2.2 µF output capacitor.

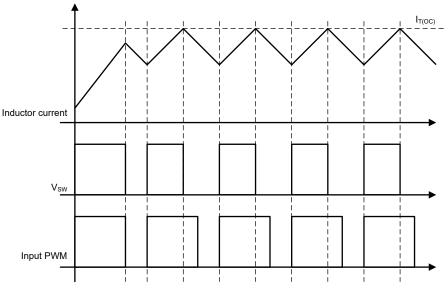

The buck-boost converter uses a peak current hysteretic control. As shown in Figure 8-2, the inductor current increases at the beginning of a switching cycle until the inductor reaches the peak current limit. Then the inductor current goes down to zero. The idle time between each current pulse is determined automatically by the buck-boost controller, and can be reduced to zero. Therefore, the maximum output current happens when the idle time is zero, and is decided by the peak current but to a first order is independent of the inductor value. However, the peak output current the buck-boost can deliver to the -14V rail is proportional to the VDD input voltage. Therefore, the maximum switching frequency of the GaN that the buck-boost can support varies with VDD voltage and is only specified for operation up to 2 MHz for VDD voltages above 9V.

Figure 8-2. Buck-Boost Converter Inductor Current

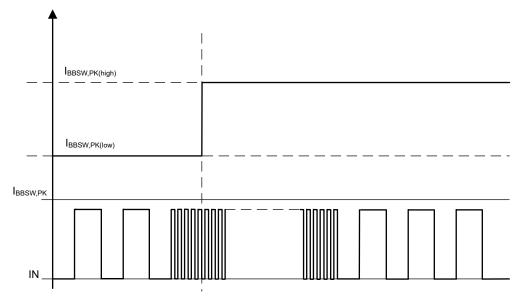

The LMG3522R030 supports the GaN operation up to 2 MHz. As power consumption is very different in a wide switching frequency range enabled by the GaN device, two peak current limits are used to control the buck-boost converter. The two ranges are separated by IN positive-going threshold frequency. As shown in Figure 8-3, when switching frequency is in the lower range, the peak current is initially set to the lower value I<sub>BBSW,M(low)</sub> (typically 0.4 A) . When switching frequency is in the higher range, the peak current is raised to the higher value I<sub>BBSW,M(high)</sub> (typically 1 A) and requires a larger inductor. There is a filter on this frequency detection logic, therefore the LMG3522R030 requires five consecutive cycles at the higher frequency before it is set to the higher buck-boost peak current limit. The current limit does not go down again until power off after the higher limit is set. Even if the switching frequency returns to the lower range, the current limit does not decrease to the lower limit.

Figure 8-3. Buck-Boost Converter Peak Current

As the peak current of the buck-boost is subject to two different peak current limits which are 0.4 A and 1 A for low and high frequency operation (see *Internal Buck-Boost DC-DC Converter*), so the inductor must have a saturation current well above the rated peak current limit. After the higher limit is established by switching at a higher frequency, the current limit does not go back to the lower level even when GaN device is then switched at a lower frequency. Therefore, selecting an inductor according to the higher 1-A limit is recommended.

#### 8.3.5 VDD Bias Supply

Wide VDD voltage ranges from 7.5 V to 18 V are supported by internal regulators which supply the bias supplies needed for the internal circuits to function. TI recommends to use a 12-V unregulated power supply to supply VDD.

#### 8.3.6 Auxiliary LDO

There is a 5-V voltage regulator inside the part used to supply external loads, such as digital isolators for the high-side drive signal. The digital outputs of the part use this rail as their supply. No capacitor is required for stability, but transient response is poor if no external capacitor is provided. If the application uses this rail to supply external circuits, TI recommends to have a capacitor of at least 0.1  $\mu$ F for improved transient response. A larger capacitor can be used for further transient response improvement. The decoupling capacitor used here must be a low-ESR ceramic type. Capacitances above 0.47  $\mu$ F will slow down the start-up time of the LMG3522R030 due to the ramp-up time of the 5-V rail.

#### 8.3.7 Fault Detection

The GaN power IC integrates overcurrent protection (OCP), short-circuit protection (SCP), overtemperature protection (OTP) and undervoltage lockout (UVLO).

### 8.3.7.1 Overcurrent Protection and Short-Circuit Protection

There are two types of current faults which can be detected by the driver: overcurrent fault and short-circuit fault.

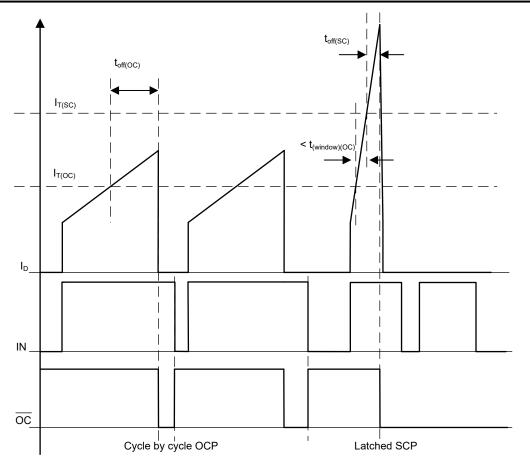

The overcurrent protection (OCP) circuit monitors drain current and compares that current signal with an internally set limit  $I_{T(OC)}$ . Upon detection of the overcurrent, the LMG3522R030 conducts cycle-by-cycle overcurrent protection as shown in Figure 8-4. In this mode, the GaN device is shut off and the OC pin is pulled low when the drain current crosses the  $I_{T(OC)}$  plus a delay  $t_{off(OC)}$ , but the overcurrent signal clears after the IN pin signal goes low. In the next cycle, the GaN device can turn on as normal. The cycle-by-cycle function can be used in cases where steady-state operation current is below the OCP level but transient response can still reach current limit, while the circuit operation cannot be paused. The cycle-by-cycle function also prevents the GaN device from overheating by overcurrent induced conduction losses.

The short-circuit protection (SCP) monitors the drain current and triggers if the *di/dt* of the current exceeds a threshold *di/dt*  $_{T(SC)}$  as the current crosses between the OC and SC thresholds. It performs this *di/dt* detection by delaying the OC detection signal by an amount  $t_{OC,window}$  and using a higher current SC detection threshold. If the delayed OC occurs before the non-delayed SC, the *di/dt* is below the threshold and an OC is triggered. If the SC is detected first, the *di/dt* is fast enough and the SC is detected as shown in Figure 8-5. This extremely high *di/dt* current would typically be caused by a short of the output of the half-bridge and can be damaging for the GaN to continue to operate in that condition. Therefore, if a short-circuit fault is detected, the GaN device is turned off with an intentionally slowed driver so that a lower overshoot voltage and ringing can be achieved during the turn-off event. This fast response circuit helps protect the GaN device even under a hard short-circuit condition. In this protection, the GaN device is shut off and held off until the fault is reset by either holding the IN pin low for a period of time defined in the *Specifications* or removing power from VDD.

During OCP or SCP in a half bridge, after the current reaches the upper limit and the device is turned off by protection, the PWM input of the device could still be high and the PWM input of the complementary device could still be low. In this case, the load current can flow through the third quadrant of the complementary device with no synchronous rectification. The high negative  $V_{DS}$  of the GaN device (–3 V to –5 V) from drain to source could lead to high third-quadrant loss, similar to dead-time loss but for a longer time.

For safety considerations, OCP allows cycle-by-cycle operation while SCP latches the device until reset. By reading the  $\overline{FAULT}$  and  $\overline{OC}$  pins, the exact current fault type can be determined. Refer to *Fault Reporting* for detailed information.

Figure 8-4. Cycle-by-Cycle OCP Operation

Figure 8-5. Overcurrent Detection vs Short-Circuit Detection

### 8.3.7.2 Overtemperature Shutdown

The LMG3522R030 implements two overtemperature-shutdown (OTSD) functions, the GaN OTSD and the Driver OTSD. Two OTSD functions are needed to maximize device protection by sensing different locations in the device and protecting against different thermal-fault scenarios.

The GaN OTSD senses the GaN FET temperature. The GaN FET can overheat from both first-quadrant current and third-quadrant current. As explained in *GaN FET Operation Definitions*, a FET can prevent first-quadrant current by going into the off-state but is unable to prevent third-quadrant current. FET third-quadrant losses are a function of the FET technology, current magnitude, and if the FET is operating in the on-state or off-state. As explained in *GaN FET Operation Definitions*, the LMG3522R030 has much higher GaN FET third-quadrant losses in the off-state.

When the GaN FET is too hot, the best protection is to turn off the GaN FET when first-quadrant current tries to flow and turn on the GaN FET when third-quadrant current is flowing. This type of FET control is known as ideal-diode mode (IDM). When the GaN OTSD trip point is exceeded, the GaN OTSD puts the GaN FET into overtemperature-shutdown ideal-diode mode (OTSD-IDM) operation to achieve this optimum protection. OTSD-IDM is explained in *Section 8.3.10*.

The Driver OTSD senses the integrated driver temperature and trips at a higher temperature compared to the GaN OTSD. This second OTSD function exists to protect the LMG3522R030 from driver thermal-fault events while allowing sufficient temperature difference for OTSD-IDM to operate. These driver thermal events include shorts on the LDO5V, BBSW, and VNEG device pins. When the Driver OTSD trip point is exceeded, the Driver OTSD shuts off the LDO5V regulator, the VNEG buck-boost converter, and the GaN FET. Note that OTSD-IDM does not function in Driver OTSD. This is why the Driver OTSD must trip higher than the GaN OTSD function. Otherwise, GaN FET third-quadrant overheating cannot be addressed.

Copyright © 2022 Texas Instruments Incorporated

Besides the temperature difference in the GaN OTSD and Driver OTSD trip points, further temperature separation is obtained due to the thermal gradient difference between the GaN OTSD and Driver OTSD sense points. The GaN OTSD sensor is typically at least 20°C hotter than the driver OTSD sensor when the device is in GaN OTSD due to GaN FET power dissipation.

The FAULT pin is asserted for either or both the GaN OTSD state and the Driver OTSD state. FAULT de-asserts and the device automatically returns to normal operation after both the GaN OTSD and Driver OTSD fall below their negative-going trip points. During cool down, when the device exits the Driver OTSD state but is still in the GaN OTSD state, the device automatically resumes OTSD-IDM operation.

#### 8.3.7.3 UVLO Protection

The LMG3522R030 supports a wide range of VDD voltages. However, when the device is below UVLO threshold, the GaN device stops switching and is held off. The  $\overline{FAULT}$  pin is pulled low as an indication of UVLO. The LDO and buck-boost are turned on by the rising-edge of the VIN UVLO and shuts off around 5 V to 6 V.

#### 8.3.7.4 Fault Reporting

The  $\overline{FAULT}$  and  $\overline{OC}$  outputs form a fault reporting scheme together. The  $\overline{FAULT}$  and  $\overline{OC}$  outputs are both push-pull outputs indicating the readiness and fault status of the driver. These two pins are logic high in normal operation, and change logic according to Table 8-1.

|       | NORMAL | UVLO, OT, and RDRV-OPEN | OVERCURRENT | SHORT-CIRCUIT |

|-------|--------|-------------------------|-------------|---------------|

| FAULT | 1      | 0                       | 1           | 0             |

|       | 1      | 1                       | 0           | 0             |

#### Table 8-1. Fault Types and Reporting

$\overline{FAULT}$  is held low when starting up until the series Si FET is turned on. During operation, if the power supplies go below the UVLO thresholds or the device temperature go above the OT thresholds, power device is disabled and  $\overline{FAULT}$  is held low until a fault condition is no longer detected. If RDRV is open,  $\overline{FAULT}$  is also held low. In a short-circuit or overtemperature fault condition,  $\overline{FAULT}$  is held low until the fault latches are reset or fault is cleared. The  $\overline{OC}$  pin is held low if there is a short-circuit or overcurrent fault. The signals help notify the controller the exact type of faults by reading the truth table. If a combined reporting of the faults on a single pin is desired, one can short the  $\overline{OC}$  pin to ground during power up. All faults assert the  $\overline{FAULT}$  pin then and the  $\overline{OC}$  pin is not used. Please note: internal protection happens regardless of the connection of the pin outputs, which means that the protection features continue to operate even if fault reporting is ignored.

#### 8.3.8 Drive Strength Adjustment

The LMG3522R030 allows users to adjust the drive strength of the device and obtain a desired slew rate, which provides flexibility when optimizing switching losses and noise coupling.

To adjust drive strength, a resistor can be placed between the RDRV pin and SOURCE pin. The resistance determines the slew rate of the device, from 20 V/ns to 150 V/ns, during turn-on. On the other hand, there are two dv/dt values that can be selected without the resistor: shorting the RDRV pin to ground sets the slew rate to 150 V/ns, and shorting the RDRV pin to LDO5V sets the slew rate to 100 V/ns. The device detects the short to LDO5V one time at power up. Once the short to LDO5V condition is detected, the device no longer monitors the RDRV pin. Otherwise, the RDRV pin is continuously monitored and the dv/dt setting can be changed by modulating the resistance during device operation. The modulation must be fairly slow since there is significant internal filtering to reject switching noise.

Please note: parasitic power loop inductance can influence the voltage slew rate reading from the  $V_{DS}$  switching waveform. The inductance induces a drop on  $V_{DS}$  in the current rising phase before voltage falling phase, if this drop is more than 20% of the  $V_{DC}$ , the voltage slew rate reading can be influenced. Refer to Section 9.5.1.2 for the power loop design guideline and how to estimate the parasitic power loop inductance.

#### 8.3.9 Temperature-Sensing Output

The integrated driver senses the GaN die temperature and outputs the information through a modulated PWM signal on the TEMP pin. The typical PWM frequency is 9 kHz with the same refresh rate. The minimum PWM duty cycle is around 1%, which can be observed at temperature below 25°C. The target temperature range is from 25°C to 150°C, and the corresponding PWM duty cycle is typically from 3% to 82%. Following equation can be used to calculate the typical junction temperature T<sub>J,typ</sub> in °C from the duty cycle D<sub>TEMP</sub>:

T<sub>J,tvp</sub> (°C) = 162.3 \* D<sub>TEMP</sub> + 20.1

The tolerances of typical measurement are listed in Table 8-2.

| Table 8-2. Typical Junction Temperature Measurement based on TEMP Signal and Tolera |

|-------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------|

| Typical T <sub>J</sub> Measurement based on TEMP Signal (°C) | 25  | 85  | 125  |

|--------------------------------------------------------------|-----|-----|------|

| Tolerance (°C)                                               | ± 5 | ± 6 | ± 10 |

At temperatures above 150°C, the duty cycle continues to increase linearly until overtemperature fault happens. When overtemperature happens, the TEMP pin is pulled high to indicate this fault until the temperature is reduced to the normal range. There is a hysteresis to clear overtemperature fault.

#### 8.3.10 Ideal-Diode Mode Operation

Off-state FETs act like diodes by blocking current in one direction (first quadrant) and allowing current in the other direction (third quadrant) with a corresponding *diode like* voltage drop. FETs, though, can also conduct third-quadrant current in the on-state at a significantly lower voltage drop. Ideal-diode mode (IDM) is when an FET is controlled to block first-quadrant current by going to the off-state and conduct third-quadrant current by going to the on-state, thus achieving an *ideal* lower voltage drop.

FET off-state third-quadrant current flow is commonly seen in power converters, both in normal and fault situations. As explained in *GaN FET Operation Definitions*, GaN FETs do not have an intrinsic p-n junction body diode to conduct off-state third-quadrant current. Instead, the off-state third-quadrant voltage drop for the LMG3522R030 is several times higher than a p-n junction voltage drop, which can impact efficiency in normal operation and device ruggedness in fault conditions.

To improve device ruggedness in a GaN FET overtemperature fault situation, LMG3522R030 devices implement a GaN FET overtemperature-shutdown ideal-diode mode (OTSD-IDM) function as referenced in *Overtemperature Shutdown*. The OTSD-IDM function is described in more detail below.

#### 8.3.10.1 Overtemperature-Shutdown Ideal-Diode Mode

Overtemperature-shutdown ideal-diode mode (OTSD-IDM) is implemented in LMG3522R030. As explained in *Overtemperature Shutdown*, ideal-diode mode provides the best GaN FET protection when the GaN FET is overheating.

OTSD-IDM accounts for all, some, or none of the power system operating when OTSD-IDM is protecting the GaN FET. The power system may not have the capability to shut itself down, in response to the LMG3522R030 asserting the FAULT pin in a GaN OTSD event, and just continue to try to operate. Parts of the power system can stop operating due to any reason such as a controller software bug or a solder joint breaking or a device shutting off to protect itself. At the moment of power system shutdown, the power system stops providing gate drive signals but the inductive elements continue to force current flow while they discharge.

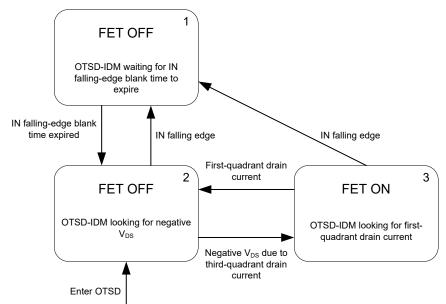

The OTSD-IDM state machine is shown in Figure 8-6. Each state is assigned a state number in the upper right side of the state box. The OTSD-IDM state machine has a similar structure to the OP-IDM state machine. Similar states use the same state number.

#### Figure 8-6. Overtemperature-Shutdown Ideal-Diode Mode (OTSD-IDM) State Machine

- 1. The LMG3522R030 GaN FET always goes to state #1 if a falling edge is detected on the IN pin. OTSD-IDM turns off the GaN FET in OTSD-IDM state #1. OTSD-IDM is waiting for the IN falling edge blank time to expire. This time gives the opposite-side FET time to switch to create a positive drain voltage. After the blank time expires, the device moves to OTSD-IDM state #2.

- 2. For OTSD-IDM state #2, OTSD-IDM keeps the GaN FET off if it is coming from OTSD-IDM state #1 and turns the GaN FET off if it is coming from OTSD-IDM state #3. OTSD-IDM is monitoring the GaN FET drain voltage in OP-IDM state #2. It is looking for a negative drain voltage which means third-quadrant current is flowing. This is also the starting state when the device enters OTSD. After a negative GaN FET drain voltage is detected, the device moves to OTSD-IDM state #3

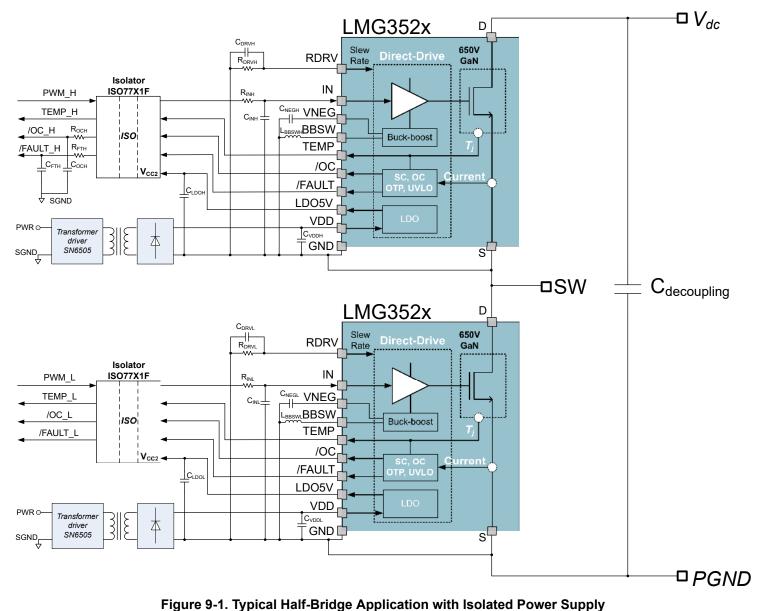

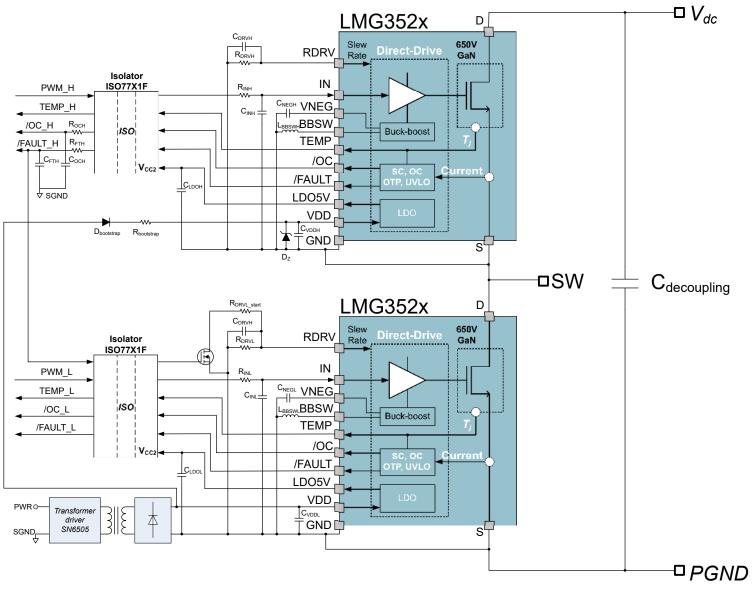

- 3. OP-IDM turns on the GaN FET in OTSD-IDM state #3. OP-IDM monitors the drain current in this state. If first-quadrant drain current is detected, the device moves to OP-IDM state #2.