# **inter<sub>sil</sub>**

## DATASHEET

## ISL6406

## Single Synchronous Buck Pulse-Width Modulation (PWM) Controller

FN9073 Rev 9.00 Oct 21, 2015

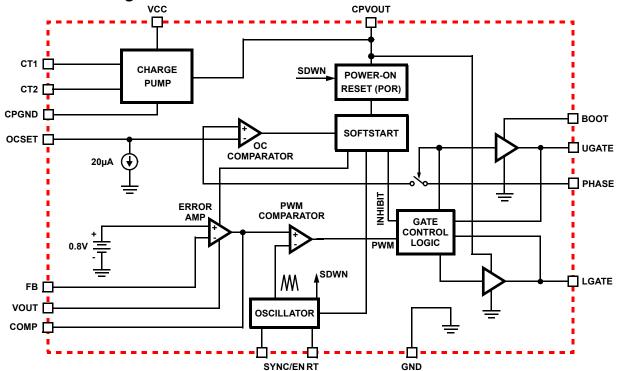

The ISL6406 is an adjustable frequency, synchronous buck switching regulator optimized for generating lower voltages for the distributed DC/DC architectures. The ISL6406 offers an adjustable output voltage.

Designed to drive N-Channel MOSFETs in synchronous buck topology, the ISL6406 integrates the control, output adjustment and protection functions into a single package.

The ISL6406 provides simple, single feedback loop, voltage-mode control with fast transient response. The output voltage can be precisely regulated to as low as 0.8V. The error amplifier features a 15MHz gain-bandwidth product and  $6V/\mu s$  slew rate which enables high converter bandwidth for fast transient performance.

Protection from overcurrent conditions is provided by monitoring the  $r_{DS(ON)}$  of the upper MOSFET to inhibit PWM operation appropriately. This approach simplifies the implementation and improves efficiency by eliminating the need for a current sense resistor.

The wide programmable switching frequency range of 100kHz to 700kHz allows the use of small surface mount inductors and capacitors. The device also provides external frequency synchronization making it an ideal choice for DC/DC converter applications.

### Features

- Operates from 3.3V/5V Input

- 0.8V to V<sub>IN</sub> Output Range

- 0.8V Internal Reference

- ±1.5% Reference Accuracy

- Simple Single-Loop Control Design

Voltage-Mode PWM Control

- Fast Transient Response

- High-Bandwidth Error Amplifier

- · Lossless, Programmable Overcurrent Protection

- Uses Upper MOSFET's r<sub>DS(ON)</sub>

- Programmable Switching Frequency 100kHz to 700kHz

- External Frequency Synchronization

- Internal Soft-Start

- QFN Package Option

- QFN Compliant to JEDEC PUB95 MO-220 QFN Quad Flat No Leads - Product Outline

- QFN Near Chip-Scale Package Footprint; Improves PCB Efficiency, Thinner in Profile

- Pb-Free (RoHS compliant)

#### Applications

- 3V/5V DC/DC Converter Modules

- Distributed DC/DC 3.3V, 2.5V and 1.8V Power Architectures for DSP, Logic, and Memory

- Power Supplies for Microprocessors

- PCs

- Embedded Controllers

- · Memory Supplies

- Personal Computer Peripherals

### Ordering Information

| PART NUMBER<br>(Note)                                                     | PART MARKING | TEMP. RANGE (°C) | PACKAGE<br>(RoHS Compliant) | PKG. DWG. # |

|---------------------------------------------------------------------------|--------------|------------------|-----------------------------|-------------|

| ISL6406IBZ* (No longer available,<br>recommended replacement: ISL6406IVZ) | 6406IBZ      | -40 to +85       | 16 Ld SOIC                  | M16.15      |

| ISL6406IRZ* (No longer available or supported)                            | ISL6406 IRZ  | -40 to +85       | 16 Ld 5x5 QFN               | L16.5x5B    |

| ISL6406IVZ*                                                               | 6406 IVZ     | -40 to +85       | 16 Ld TSSOP                 | M16.173     |

\*Add "-T" suffix to part number for tape and reel packaging. Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

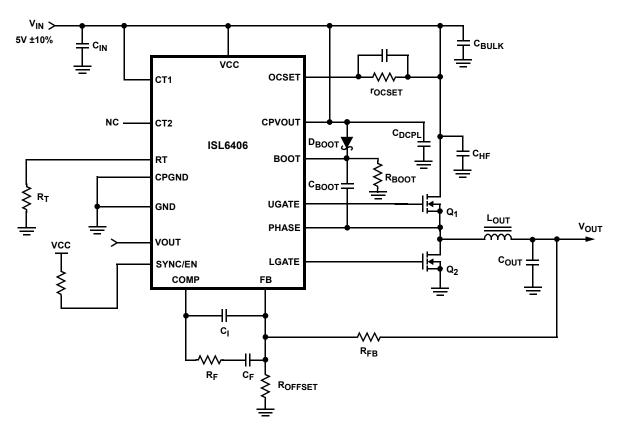

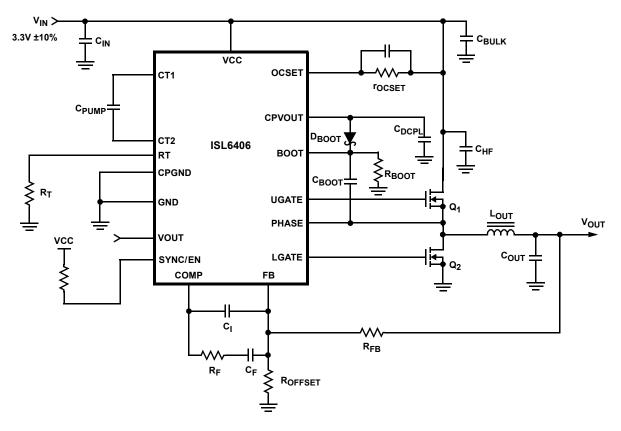

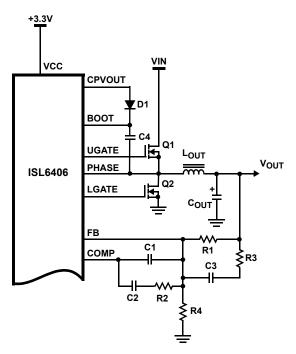

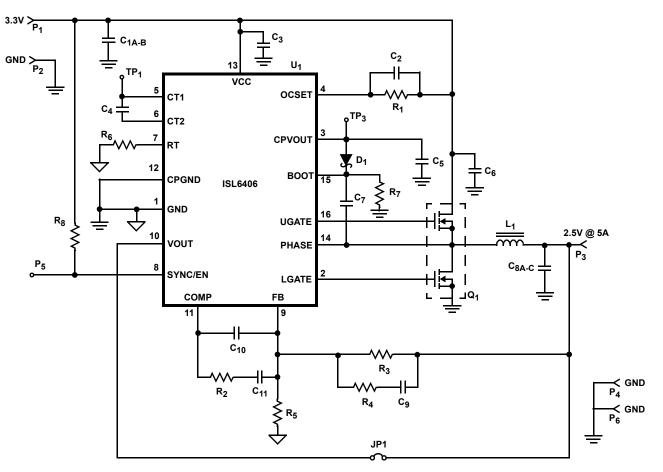

Typical Application Schematic for 3.3V Input

#### **Absolute Maximum Ratings**

| Thermal Resistance (Typical) $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W) |                                                                                                                                                                                                                                                                                       |  |  |  |

|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 16 Ld SOIC (Note 2) 70 N/A                                             |                                                                                                                                                                                                                                                                                       |  |  |  |

| 16 Ld TSSOP (Note 2) 90 N/A                                            |                                                                                                                                                                                                                                                                                       |  |  |  |

| 16 Ld QFN (Notes 3, 4)                                                 |                                                                                                                                                                                                                                                                                       |  |  |  |

| Maximum Junction Temperature (Plastic Package)55°C to +150°C           |                                                                                                                                                                                                                                                                                       |  |  |  |

| Maximum Storage Temperature Range65°C to +150°C                        |                                                                                                                                                                                                                                                                                       |  |  |  |

| Pb-Free Reflow Profile                                                 |                                                                                                                                                                                                                                                                                       |  |  |  |

|                                                                        | Thermal Resistance (Typical) $\theta_{JA}$ (°C/W) $\theta_{JC}$ (°C/W)16 Ld SOIC (Note 2)70N/A16 Ld TSSOP (Note 2)90N/A16 Ld QFN (Notes 3, 4)354.5Maximum Junction Temperature (Plastic Package)-55°C to +150°CMaximum Storage Temperature Range-65°C to +150°CPb-Free Reflow Profile |  |  |  |

Thermal Information

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- 1. Please refer to the Typical Application Schematics (page 3) for 3.3V/5V input configuration.

- 2.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 3.  $\theta_{\text{LA}}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 4. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications** Recommended operating conditions unless otherwise noted. Refer to "Functional Block Diagram" on page 2 and Typical Application Schematic beginning on page 2.  $V_{CC}$  = +3.3V. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

| PARAMETER                         | TEST CONDITIONS                        | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------|----------------------------------------|------|------|------|-------|

| V <sub>CC</sub> SUPPLY            |                                        | 1    |      | I    |       |

| Shutdown Supply Current           | SYNC/EN = GND                          | -    | 20   | 50   | μA    |

| Operating Supply Current (Note 5) | RT = 64.9kΩ                            | 7    | 9.8  | 11.5 | mA    |

| REFERENCE VOLTAGE                 |                                        |      | 1    |      |       |

| Nominal Reference Voltage         |                                        | -    | 0.8  | -    | V     |

| Reference Voltage Tolerance       |                                        | -1.5 | -    | 1.5  | %     |

|                                   | $T_A = 0^{\circ}C$ to +70°C            | -1.8 | -    | 1.8  | %     |

|                                   | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ | -2.1 | -    | 2.1  | %     |

| ERROR AMPLIFIER                   |                                        |      | 1    |      |       |

| Open Loop Voltage Gain (Note 6)   |                                        | -    | 82   | -    | dB    |

| Gain-Bandwidth Product (Note 6)   |                                        | 14   | -    | -    | MHz   |

| Slew Rate (Note 5)                | COMP = 10pF                            | 4.65 | 6.0  | 9.2  | V/µs  |

| CHARGE PUMP                       |                                        |      | 1    |      |       |

| Nominal Charge Pump Output        | V <sub>CC</sub> = 3.3V, No Load        | 4.8  | 5.1  | 5.5  | V     |

| Charge Pump Output Regulation     |                                        | -5.0 | -    | 5.0  | %     |

| POWER-ON RESET                    |                                        |      | 1    |      |       |

| Rising CPVOUT POR Threshold       | $T_A = 0^{\circ}C$ to +70°C            | 4.20 | 4.35 | 4.5  | V     |

|                                   | $T_A = -40^{\circ}C$ to $+85^{\circ}C$ | 4.1  | 4.35 | 4.6  | V     |

| CPVOUT POR Threshold Hysteresis   |                                        | 0.3  | 0.5  | 0.9  | V     |

| OSCILLATOR                        |                                        |      | 1    |      |       |

| Gate Output Frequency Range       | RT = 200kΩ                             | 80   | 100  | 120  | kHz   |

|                                   | RT = 64.9kΩ                            | 250  | 300  | 340  | kHz   |

|                                   | RT = 26.1kΩ                            | 650  | 715  | 770  | kHz   |

| Sawtooth Amplitude                | Peak-to-Peak ∆V <sub>OSC</sub>         | 1.1  | 1.4  | 1.7  | V     |

| Sync. Frequency Range (Note 6)    | 1.1x the natural switching frequency.  | 110  | -    | 770  | kHz   |

| Minimum Sync Pulse Width (Note 6) |                                        | -    | 40   | 100  | ns    |

#### **Electrical Specifications**

Recommended operating conditions unless otherwise noted. Refer to "Functional Block Diagram" on page 2 and Typical Application Schematic beginning on page 2.  $V_{CC}$  = +3.3V. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued)

| PARAMETER                   | PARAMETER TEST CONDITIONS                                                       |     | TYP  | MAX | UNITS      |  |

|-----------------------------|---------------------------------------------------------------------------------|-----|------|-----|------------|--|

| PWM Maximum Duty Cycle      |                                                                                 | -   | 96   | -   | %          |  |

| GATE DRIVER OUTPUT (Note 6) | · · · ·                                                                         |     |      |     |            |  |

| Upper Gate Source Current   | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 5V, V <sub>UGATE</sub> = 4V            | -   | -1   | -   | А          |  |

| Upper Gate Sink Current     |                                                                                 | -   | 1    | -   | А          |  |

| Lower Gate Source Current   | V <sub>VCC</sub> = 3.3V, V <sub>LGATE</sub> = 4V                                | -   | -1   | -   | А          |  |

| Lower Gate Sink Current     |                                                                                 | -   | 2    | -   | А          |  |

| SOFT-START                  |                                                                                 |     | 4    | 1   | 1          |  |

| Soft-Start Slew Rate        | $f = 300 \text{kHz}, T_A = 0^{\circ} \text{C} \text{ to } +70^{\circ} \text{C}$ | 6.2 | 6.7  | 7.3 | ms         |  |

|                             | f = 300kHz, T <sub>A</sub> = -40°C to +85°C                                     | 6.2 | 6.7  | 7.6 | ms         |  |

|                             | Internal Digital Circuit Clock Count<br>(Soft-start time varies with frequency) | -   | 2048 | -   | Clk Cycles |  |

| OVERCURRENT                 | · · · · · ·                                                                     |     | 1    | 1   | ł          |  |

| OCSET Current Source        | $T_A = 0^{\circ}C$ to +70°C                                                     | 18  | 20   | 22  | μΑ         |  |

|                             | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                                   | 16  | 20   | 23  | μA         |  |

NOTES:

5. This is the  $V_{CC}$  current consumed when the device is active but not switching.

6. Limits established by characterization and are not production tested.

## **Typical Performance Curve**

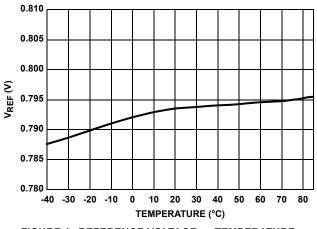

FIGURE 1. REFERENCE VOLTAGE vs TEMPERATURE

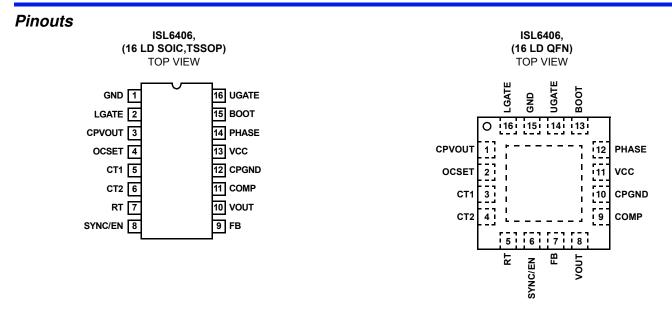

### **Pin Descriptions**

**CPVOUT** - This pin represents the output of the charge pump. The voltage at this pin is the bias voltage for the IC. Connect a decoupling capacitor from this pin to ground. The value of the decoupling capacitor should be at least 10x the value of the charge pump capacitor. This pin may be tied to the bootstrap circuit as the source for creating the BOOT voltage.

CT1 and CT2 - These pins are the connections for the external charge pump capacitor. A minimum of a  $0.1\mu F$  ceramic capacitor is recommended for proper operation of the IC.

**OCSET** - Connect a resistor ( $r_{OCSET}$ ) from this pin to the drain of the upper MOSFET ( $V_{IN}$ ).  $r_{OCSET}$ , an internal 20µA current source ( $I_{OCSET}$ ), and the upper MOSFET ON-resistance ( $r_{DS(ON)}$ ) set the converter overcurrent (OC) trip point according to Equation 1:

$I_{PEAK} = \frac{(I_{OCSET})(R_{OCSET})}{r_{DS(ON)}}$ (EQ. 1)

An overcurrent trip cycles the soft-start function.

**VOUT** - This pin provides the external switcher output voltage to the IC as feedback for the 1.8V fixed output voltage option. Leave this pin open on the ISL6406 for the adjustable output voltage option.

**VCC** - This pin provides bias supply for the ISL6406. Connect a well-coupled 3.3V supply to this pin.

**PHASE** - Connect this pin to the upper MOSFET's source. This pin is used to monitor the voltage drop across the upper MOSFET for overcurrent protection.

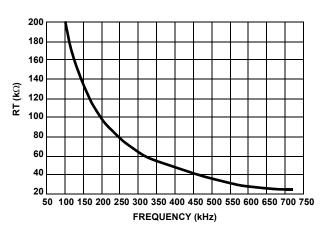

**RT** - Connect an external resistor from this pin to ground for frequency selection. Refer to Figure 3 (RT vs Frequency).

**BOOT** - This pin provides ground referenced bias voltage to the upper MOSFET driver. A bootstrap circuit is used to create a voltage suitable to drive a logic-level N-Channel MOSFET. A large (~1M $\Omega$ ) resistor should be connected from this pin to GND. The purpose of this resistor is to discharge the BOOT pin during a shutdown condition, SYNC/EN = LOW so that the gate drivers are quickly powered off by this bleed resistor.

**UGATE** - Connect this pin to the upper MOSFET's gate. This pin provides the PWM-controlled gate drive for the upper MOSFET. This pin is also monitored by the adaptive shoot-through protection circuitry to determine when the upper MOSFET has turned off.

**GND** - This pin represents the signal and power ground for the IC. Tie this pin to the ground island/plane through the lowest impedance connection available.

**LGATE -** Connect this pin to the lower MOSFET's gate. This pin provides the PWM-controlled gate drive for the lower MOSFET. This pin is also monitored by the adaptive shoot-through protection circuitry to determine when the lower MOSFET has turned off.

**COMP and FB -** COMP and FB are the available external pins of the error amplifier. The FB pin is the inverting input of the internal error amplifier and the COMP pin is the error amplifier output. These pins are used to compensate the control feedback loop of the converter.

**CPGND** - This pin represents the signal and power ground for the charge pump. Tie this pin to the ground island/plane through the lowest impedance connection available.

**SYNC/EN** - This is a dual-function pin. To synchronize with an external clock, apply a clock with a frequency 1.1x to 2.0xhigher than the part's natural frequency to this pin. The device may be disabled by tying this pin to ground. In this shutdown mode, all functions are disabled and the device will draw <50µA supply current.

## Functional Description

#### Initialization

The ISL6406 automatically initializes upon receipt of power. Special sequencing of the input supplies is not necessary. The Power-On Reset (POR) function continually monitors the the output voltage of the charge pump. During POR, the charge pump operates on a free running oscillator. Once the POR level is reached, the charge pump oscillator is synched to the PWM oscillator. The POR function also initiates the soft-start operation after the charge pump output voltage exceeds its POR threshold.

#### Soft-Start

The POR function initiates the digital soft-start sequence. The PWM error amplifier reference is clamped to a level proportional to the soft-start voltage. As the soft-start voltage slews up, the PWM comparator generates PHASE pulses of increasing width that charge the output capacitor(s). This method provides a rapid and controlled output voltage rise. The soft start sequence typically takes about 6.5ms.

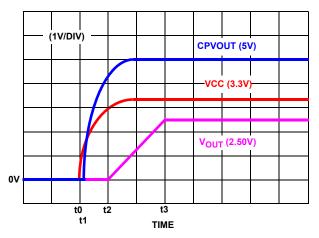

FIGURE 2. SOFT-START INTERVAL

Figure 2 shows the soft-start sequence for a typical application. At t0, the +3.3V VCC voltage starts to ramp. At time t1, the Charge Pump begins operation and the +5V CPVOUT IC bias voltage starts to ramp up. Once the voltage on CPVOUT crosses the POR threshold at time t2, the output begins the soft-start sequence. The triangle waveform from the PWM oscillator is compared to the rising error amplifier output voltage. As the error amplifier voltage increases, the pulse-width on the UGATE pin increases to reach the steady-state duty cycle at time t3.

#### **Frequency Selection**

The ISL6406 offers adjustable frequency from 100kHz to 700kHz by changing external resistor connected at pin RT. Figure 3 shows the typical RT vs Frequency variation curve.

#### Shoot-Through Protection

A shoot-through condition occurs when both the upper MOSFET and lower MOSFET are turned on simultaneously, effectively shorting the input voltage to ground. To protect the regulator from a shoot-through condition, the ISL6406 incorporates specialized circuitry which insures that the MOSFETs are not ON simultaneously.

The adaptive shoot-through protection utilized by the ISL6406 looks at the lower gate drive pin, LGATE, and the upper gate drive pin, UGATE, to determine whether a MOSFET is ON or OFF. If the voltage from UGATE or from LGATE to GND is less than 0.8V, then the respective MOSFET is defined as being OFF and the other MOSFET is turned ON. This method of shoot-through protection allows the regulator to sink or source current.

Since the voltage of the lower MOSFET gate and the upper MOSFET gate are being measured to determine the state of the MOSFET, the designer is encouraged to consider the repercussions of introducing external components between the gate drivers and their respective MOSFET gates before actually implementing such measures. Doing so may interfere with the shoot-through protection.

#### **Output Voltage Selection**

The output voltage can be programmed to any level between  $V_{IN}$  and the internal reference, 0.8V. An external resistor divider is used to scale the output voltage relative to the reference voltage and feed it back to the inverting input of the error amplifier, see Figure 4. However, since the value of  $R_1$  affects the values of the rest of the compensation components, it is advisable to keep its value less than 5k.  $R_4$  can be calculated based on Equation 2:

$$R_4 = \frac{(R_1)(0.8V)}{V_{OUT1} - (0.8V)}$$

(EQ. 2)

If the output voltage desired is 0.8V, simply route the output back to the FB pin through  $R_1$ , but do not populate  $R_4$ .

FIGURE 4. OUTPUT VOLTAGE SELECTION

#### Frequency Synchronization and Enable

The external frequency synchronization and enable functions are combined in SYNC/EN pin. This pin is TTL compatible for VCC = 3.3V or 5V. The device is disabled if the input to this pin is TTL LOW for more than 40µs (typ); it is enabled if the input is TTL HIGH without delay. When disabling the IC, the charge pump is turned off and the BOOT pin is left charged at ~5V. In some cases, this charge will inadvertently leak through the upper gate driver and can possibly turn on the upper FET. To avoid this, it is recommended that a 1M $\Omega$  'bleed' resistor be connected from the BOOT pin to GND. This resistor is shown in the Typical Application Schematics on page 3 as R<sub>BOOT</sub>.

The SYNC/EN pin is monitored by the internal timer. The timer allows SYNC pulses (TTL LOW level) to pass through, as long as the pulses are shorter than  $22\mu$ s. The minimum SYNC pulse width is 40ns (typ).

The oscillator can SYNC to an external frequency of between 1.1x and 2.0x the free-running frequency. Loop acquisition time is about 200 clock cycles. The timing resistor (RT) is always required, regardless of whether SYNC pulses are being used or not.

For instance, if RT is selected such that the switching frequency is 100kHz then the ISL6406 can be synchronized to a switching frequency from 110kHz to 200kHz.

#### **Overcurrent Protection**

The overcurrent function protects the converter from a shorted output by using the upper MOSFET ON-resistance,  $r_{DS(ON)}$ , to monitor the current. This method enhances the

converter's efficiency and reduces cost by eliminating a current sensing resistor. The over current function cycles the soft-start function in a hiccup mode to provide fault protection. A resistor ( $r_{OCSET}$ ) programs the over current trip level (see Typical Application diagrams beginning on page 3). An internal 20µA (typical) current sink develops a voltage across  $r_{OCSET}$  that is referenced to  $V_{IN}$ . When the voltage across the upper MOSFET (also referenced to  $V_{IN}$ ) exceeds the voltage across  $r_{OCSET}$ , the overcurrent function initiates a soft-start sequence.

FIGURE 5. OVERCURRENT PROTECTION RESPONSE

Figure 5 illustrates the protection feature responding to an overcurrent event. At time t0, an overcurrent condition is sensed across the upper MOSFET. As a result, the regulator is quickly shutdown and the internal soft-start function begins producing soft-start ramps. The delay interval seen by the output is equivalent to three soft-start cycles. The fourth internal soft-start cycle initiates a normal soft-start ramp of the output, at time t1. The output is brought back into regulation by time t2, as long as the overcurrent event has cleared. Had the cause of the overcurrent still been present after the delay interval, the overcurrent condition would be sensed and the regulator would be shut down again for another delay interval of three soft-start cycles. The resulting hiccup mode style of protection would continue to repeat indefinitely.

The overcurrent function will trip at a peak inductor current  $(I_{peak})$  determined by Equation 3:

$$I_{PEAK} = \frac{(I_{OCSET})(R_{OCSET})}{r_{DS(ON)}}$$

(EQ. 3)

where  $I_{OCSET}$  is the internal OCSET current source (20µA typical). The OC trip point varies mainly due to the MOSFET  $r_{DS(ON)}$  variations. To avoid overcurrent tripping in the

normal operating load range, find the  $\ensuremath{r_{\text{OCSET}}}$  resistor from Equation 3 with:

- 1. The maximum  $r_{\text{DS}(\text{ON})}$  at the highest junction temperature.

- 2. The minimum I<sub>OCSET</sub> from the specification table.

- 3. Determine I<sub>PEAK</sub> for, I<sub>PEAK</sub> > I<sub>OUT(MAX)</sub> + ( $\Delta$ I/2) where  $\Delta$ I is the output inductor ripple current.

For an equation for the ripple current see the section under Component Selection Guidelines titled "Output Inductor Selection" on page 11. A small ceramic capacitor should be placed in parallel with  $r_{OCSET}$  to smooth the voltage across  $r_{OCSET}$  in the presence of switching noise on the input voltage.

When the controller enters hiccup mode the differential voltage across the error amplifier forces the COMP pin to rail HIGH to approximately 5V. When the controller begins a new soft-start sequence out of hiccup mode the COMP pin will need to discharge down to approximately 1.2V near the beginning of the PWM ramp in order to start up correctly. To ensure the controller can discharge the COMP pin fast enough the R and C from COMP to FB must not have too high a time constant. For time constant recommendations refer to the section "Feedback Compensation" on page 10.

#### **Current Sinking**

The ISL6406 incorporates a MOSFET shoot-through protection method which allows a converter to sink current as well as source current. Care should be exercised when designing a converter with the ISL6406 when it is known that the converter may sink current. When the converter is sinking current, it is behaving as a boost converter that is regulating its input voltage. This means that the converter is boosting current into the input rail of the regulator. If there is nowhere for this current to go, such as to other distributed loads on the rail or through a voltage limiting protection device, the capacitance on this rail will absorb the current. This situation will allow the voltage level of the input rail to increase. If the voltage level of the rail is boosted to a level that exceeds the maximum voltage rating of any components attached to the input rail, then those components may experience an irreversible failure or experience stress that may shorten their lifespan. Ensuring that there is a path for the current to flow other than the capacitance on the rail will prevent this failure mode.

## **Application Guidelines**

#### Layout Considerations

Layout is very important in high frequency switching converter design. With power devices switching, the resulting current transitions from one device to another cause voltage spikes across the interconnecting impedances and parasitic circuit elements. These voltage spikes can degrade efficiency, radiate noise into the circuit, and lead to device overvoltage stress.

Careful component layout and printed circuit board design minimizes the voltage spikes in the converters. As an example, consider the turn-off transition of the PWM MOSFET. Prior to turn-off, the MOSFET is carrying the full load current. During turn-off, current stops flowing in the MOSFET and is picked up by the lower MOSFET. Any parasitic inductance in the switched current path generates a large voltage spike during the switching interval. Careful component selection, tight layout of the critical components, and short wide traces minimizes the magnitude of voltage spikes.

There are two sets of critical components in a DC/DC converter using the ISL6406. The switching components are the most critical because they switch large amounts of energy, and therefore tend to generate large amounts of noise. Next, are the small signal components which connect to sensitive nodes or supply critical bypass current and signal coupling.

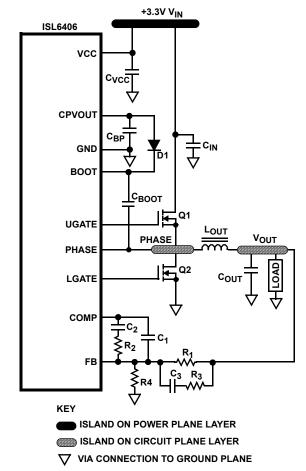

A multi-layer printed circuit board is recommended. Figure 6 shows the connections of the critical components in the converter. Note that capacitors  $C_{IN}$  and  $C_{OUT}$  could each represent numerous physical capacitors.

FIGURE 6. PRINTED CIRCUIT BOARD POWER PLANES AND ISLANDS

Dedicate one solid layer, usually a middle layer of the PC board, for a ground plane and make all critical component ground connections with vias to this layer. Dedicate another solid layer as a power plane and break this plane into smaller islands of common voltage levels. Keep the metal runs from the PHASE terminals to the output inductor short. The power plane should support the input power and output power nodes. Use copper-filled polygons on the top and bottom circuit layers for the phase nodes. Use the remaining printed circuit layers for small signal wiring. The wiring traces from the GATE pins to the MOSFET gates should be kept short and wide enough to easily handle the 1A of drive current. The switching components should be placed close to the ISL6406 first. Minimize the length of the connections between the input capacitors,  $C_{IN}$ , and the power switches by placing them nearby. Position both the ceramic and bulk input capacitors as close to the upper MOSFET drain and islands as possible. Position the output inductor and output capacitors between the upper and lower MOSFETs and the load.

The critical small signal components include any bypass capacitors, feedback components, and compensation components. Position the bypass capacitor,  $C_{BP}$ , close to the VCC pin with a via directly to the ground plane. Place the PWM converter compensation components close to the FB and COMP pins. The feedback resistors for both regulators should also be located as close as possible to the relevant FB pin with vias tied straight to the ground plane as required.

#### Feedback Compensation

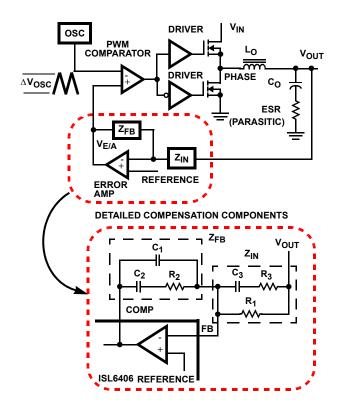

Figure 7 highlights the voltage-mode control loop for a synchronous-rectified buck converter. The output voltage (V<sub>OUT</sub>) is regulated to the Reference voltage level. The error amplifier (Error Amp) output (V<sub>E/A</sub>) is compared with the oscillator (OSC) triangular wave to provide a pulse-width modulated (PWM) wave with a peak amplitude of V<sub>IN</sub> at the PHASE node. The PWM wave is smoothed by the output filter (L and C<sub>O</sub>). The modulator transfer function is the small-signal transfer function of V<sub>OUT</sub>/V<sub>E/A</sub>. This function is dominated by a DC Gain and the output filter (L<sub>O</sub> and C<sub>O</sub>), with a double pole break frequency at F<sub>LC</sub> and a zero at F<sub>ESR</sub>. The DC Gain of the modulator is simply the input voltage (V<sub>IN</sub>) divided by the peak-to-peak oscillator voltage, V<sub>OSC</sub>.

FIGURE 7. VOLTAGE-MODE BUCK CONVERTER COMPENSATION DESIGN

#### Modulator Break Frequency Equations

$$E_{\rm LC} = \frac{1}{2\pi \sqrt{L_{\rm O}C_{\rm O}}} \tag{EQ. 4}$$

$$f_{ESR} = \frac{1}{2\pi(ESR)(C_0)}$$

(EQ. 5)

The compensation network consists of the error amplifier (internal to the ISL6406) and the impedance networks  $Z_{IN}$  and  $Z_{FB}$ . The goal of the compensation network is to provide a closed-loop transfer function with the highest 0dB crossing frequency (f 0dB) and adequate phase margin. Phase margin is the difference between the closed loop phase at f 0dB and 180°.

Equations 4 and 5 relate the compensation network's poles, zeros and gain to the components ( $R_1$ ,  $R_2$ ,  $R_3$ ,  $C_1$ ,  $C_2$  and  $C_3$ ) in Figure 7. Use these guidelines for locating the poles and zeros of the compensation network:

- 1. Pick gain  $(R_2/R_1)$  for desired converter bandwidth.

- 2. Place first zero below filter's double pole (~75%  $F_{LC}).$

- 3. Place second zero at filter's double pole.

- 4. Place first pole at the ESR zero.

- 5. Place second pole at half the switching frequency.

- 6. Check gain against error amplifier's open-loop gain.

- 7. Estimate phase margin-repeat if necessary.

During overcurrent hiccup mode the COMP pin will rail HIGH to about 5V. When the soft-start sequence is initiated out-of-hiccup mode, the COMP pin will have to discharge from 5V to about 1.2V, the beginning of the PWM ramp in order to start up properly. Use of a small COMP to FB Rs and Cs as possible is recommended. The recommended value for  $C_2$  in Figure 7 is 4700pF or less.

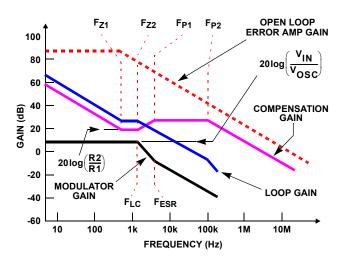

### Compensation Break Frequency Equations

Figure 8 shows an asymptotic plot of the DC/DC converter's gain vs frequency. The actual Modulator Gain has a high gain peak due to the high Q factor of the output filter and is not shown in Figure 8. Using the above guidelines should give a Compensation Gain similar to the curve plotted. The open loop error amplifier gain bounds the compensation gain. Check the compensation gain at FP2 with the capabilities of the error amplifier. The Closed Loop Gain is constructed on the graph of Figure 8 by adding the Modulator Gain (in dB) to the Compensation Gain (in dB). This is equivalent to multiplying the modulator transfer function to the compensation transfer function and plotting the gain. The compensation gain uses external impedance networks Z<sub>FB</sub> and Z<sub>IN</sub> to provide a stable, high bandwidth (BW) overall loop. A stable control loop has a gain crossing with -20dB/decade slope and a phase margin greater than 45°. Include worst-case component variations when determining phase margin.

FIGURE 8. ASYMPTOTIC BODE PLOT OF CONVERTER GAIN

## **Component Selection Guidelines**

#### Charge Pump Capacitor Selection

A capacitor across pins CT1 and CT2 is required to create the proper bias voltage for the ISL6406 when operating the IC from 3.3V. Selecting the proper capacitance value is important so that the bias current draw and the current required by the MOSFET gates do not overburden the capacitor. A conservative approach is presented in Equation 6.

$$C_{PUMP} = \frac{I_{BIAS} + I_{GATE}}{V_{CC}(f_S)} (1.5)$$

(EQ. 6)

#### **Output Capacitor Selection**

An output capacitor is required to filter the output and supply the load transient current. The filtering requirements are a function of the switching frequency and the ripple current. The load transient requirements are a function of the slew rate (di/dt) and the magnitude of the transient load current. These requirements are generally met with a mix of capacitors and careful layout.

Modern digital ICs can produce high transient load slew rates. High-frequency capacitors initially supply the transient and slow the current load rate seen by the bulk capacitors. The bulk filter capacitor values are generally determined by the ESR (Effective Series Resistance) and voltage rating requirements rather than actual capacitance requirements.

High-frequency decoupling capacitors should be placed as close to the power pins of the load as physically possible. Be careful not to add inductance in the circuit board wiring that could cancel the usefulness of these low inductance components. Consult with the manufacturer of the load on specific decoupling requirements. Use only specialized low-ESR capacitors intended for switching-regulator applications for the bulk capacitors. The bulk capacitor's ESR will determine the output ripple voltage and the initial voltage drop after a high slew-rate transient. An aluminum electrolytic capacitor's ESR value is related to the case size with lower ESR available in larger case sizes. However, the Equivalent Series Inductance (ESL) of these capacitors increases with case size and can reduce the usefulness of the capacitor to high slew-rate transient loading. Unfortunately, ESL is not a specified parameter. Work with your capacitor supplier and measure the capacitor's impedance with frequency to select a suitable component. In most cases, multiple electrolytic capacitors of small case size perform better than a single large case capacitor.

#### **Output Inductor Selection**

The output inductor is selected to meet the output voltage ripple requirements and minimize the converter's response time to the load transient. The inductor value determines the converter's ripple current and the ripple voltage is a function of the ripple current. The ripple voltage and current are approximated by Equations 7 and 8:

$$\Delta I = \frac{V_{IN} - V_{OUT}}{f_{S} \times L} \times \frac{V_{OUT}}{V_{IN}}$$

(EQ. 7)

$$\Delta V_{OUT} = \Delta I \times ESR$$

(EQ. 8)

Increasing the value of inductance reduces the ripple current and voltage. However, the large inductance values reduce the converter's response time to a load transient.

One of the parameters limiting the converter's response to a load transient is the time required to change the inductor current. Given a sufficiently fast control loop design, the ISL6406 will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level. During this interval, the difference between the inductor current and the transient current level must be supplied by the output capacitor. Minimizing the response time can minimize the output capacitance required.

The response time to a transient is different for the application of load and the removal of load. Equations 9 and 10 give the approximate response time interval for application and removal of a transient load:

$$t_{\text{RISE}} = \frac{L \times I_{\text{TRAN}}}{V_{\text{IN}} - V_{\text{OUT}}}$$

(EQ. 9)

$$t_{FALL} = \frac{L \times I_{TRAN}}{V_{OUT}}$$

(EQ. 10)

where:  $I_{TRAN}$  is the transient load current step,  $t_{RISE}$  is the response time to the application of load, and  $t_{FALL}$  is the response time to the removal of load. The worst case response time can be either at the application or removal of load. Be sure to check both of these equations at the minimum and maximum output levels for the worst case response time.

#### Input Capacitor Selection

Use a mix of input bypass capacitors to control the voltage overshoot across the MOSFETs. Use small ceramic capacitors for high frequency decoupling and bulk capacitors to supply the current needed each time  $Q_1$  turns on. Place the small ceramic capacitors physically close to the MOSFETs and between the drain of  $Q_1$  and the source of  $Q_2$ .

The important parameters for the bulk input capacitor are the voltage rating and the RMS current rating. For reliable operation, select the bulk capacitor with voltage and current ratings above the maximum input voltage and largest RMS current required by the circuit. The capacitor voltage rating should be at least 1.25x greater than the maximum input voltage and a voltage rating of 1.5x is a conservative guideline. The RMS current rating requirement for the input capacitor of a buck regulator is approximately 1/2 the DC load current.

The maximum RMS current required by the regulator may be closely approximated through Equation 11:

$$I_{RMS_{MAX}} = \sqrt{\frac{V_{OUT}}{V_{IN}} \times \left(I_{OUT_{MAX}}^{2} + \frac{1}{12} \times \left(\frac{V_{IN} - V_{OUT}}{L \times f_{s}} \times \frac{V_{OUT}}{V_{IN}}\right)^{2}\right)}$$

(EQ. 11)

For a through-hole design, several electrolytic capacitors may be needed. For surface mount designs, solid tantalum capacitors can be used, but caution must be exercised with regard to the capacitor surge current rating. These capacitors must be capable of handling the surge-current at power-up. Some capacitor series available from reputable manufacturers are surge current tested.

#### **MOSFET Selection/Considerations**

The ISL6406 requires two N-Channel power MOSFETs. These should be selected based upon  $r_{DS(ON)}$ , gate supply requirements, and thermal management requirements.

In high-current applications, the MOSFET power dissipation, package selection and heatsink are the dominant design factors. The power dissipation includes two loss components; conduction loss and switching loss. The conduction losses are the largest component of power dissipation for both the upper and the lower MOSFETs. These losses are distributed between the two MOSFETs according to duty factor.

The switching losses seen when sourcing current will be different from the switching losses seen when sinking current. When sourcing current, the upper MOSFET realizes most of the switching losses. The lower switch realizes most of the switching losses when the converter is sinking current (see Equations 13 and 14). These equations assume linear voltage-current transitions and do not adequately model power loss due the reverse-recovery of the upper and lower MOSFET's body diode.

The gate-charge losses are dissipated by the ISL6406 and don't heat the MOSFETs. However, large gate-charge increases the switching interval,  $t_{SW}$  which increases the MOSFET switching losses. Ensure that both MOSFETs are within their maximum junction temperature at high ambient temperature by calculating the temperature rise according to package thermal-resistance specifications. A separate heatsink may be necessary depending upon MOSFET power, package type, ambient temperature and air flow.

Losses while sourcing current:

$$P_{UPPER} = Io^{2} \times r_{DS(ON)} \times D + \frac{1}{2} \cdot Io \times V_{IN} \times t_{SW} \times f_{s}$$

$$P_{LOWER} = Io^{2} \times r_{DS(ON)} \times (1 - D)$$

Losses while sinking current:

$P_{UPPER} = lo^2 x r_{DS(ON)} x D$

$$P_{LOWER} = 10^2 \times r_{DS(ON)} \times (1 - D) + \frac{1}{2} \cdot 10 \times V_{IN} \times t_{SW} \times f_s$$

Where: D is the duty cycle =  $V_{OUT} / V_{IN}$ ,

$t_{SW}$  is the combined switch ON and OFF time, and

$f_s$  is the switching frequency.

intersil

(EQ. 12)

Given the reduced available gate bias voltage (5V), logic-level or sub-logic-level transistors should be used for both N-MOSFETs. Caution should be exercised with devices exhibiting very low  $V_{GS(ON)}$  characteristics. The shoot-through protection present aboard the ISL6406 may be circumvented by these MOSFETs if they have large parasitic impedances and/or capacitances that would inhibit the gate of the MOSFET from being discharged below its threshold level before the complementary MOSFET is turned on.

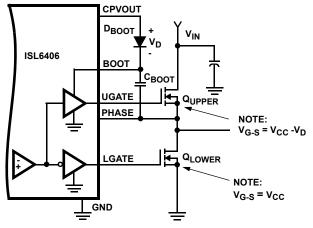

#### Bootstrap Component Selection

External bootstrap components, a diode and capacitor, are required to provide sufficient gate enhancement to the upper MOSFET. The internal MOSFET gate driver is supplied by the external bootstrap circuitry as shown in Figure 9. The boot capacitor,  $C_{BOOT}$ , develops a floating supply voltage referenced to the PHASE pin. This supply is refreshed each cycle, when  $D_{BOOT}$  conducts, to a voltage of CPVOUT less the boot diode drop,  $V_D$ , plus the voltage rise across  $Q_{LOWER}$ .

FIGURE 9. UPPER GATE DRIVE BOOTSTRAP

Just after the PWM switching cycle begins and the charge transfer from the bootstrap capacitor to the gate capacitance is complete, the voltage on the bootstrap capacitor is at its lowest point during the switching cycle. The charge lost on the bootstrap capacitor will be equal to the charge transferred to the equivalent gate-source capacitance of the upper MOSFET as shown in Equation 13:

$$Q_{GATE} = C_{BOOT} \times (V_{BOOT1} - V_{BOOT2})$$

(EQ. 13)

where  $Q_{GATE}$  is the maximum total gate charge of the upper MOSFET,  $C_{BOOT}$  is the bootstrap capacitance,  $V_{BOOT1}$  is the bootstrap voltage immediately before turn-on, and  $V_{BOOT2}$  is the bootstrap voltage immediately after turn-on.

The bootstrap capacitor begins its refresh cycle when the gate drive begins to turn-off the upper MOSFET. A refresh cycle ends when the upper MOSFET is turned on again, which varies depending on the switching frequency and duty cycle.

The minimum bootstrap capacitance can be calculated by rearranging Equation 13 and solving for  $C_{BOOT}$  using Equation 14:

$$C_{BOOT} = \frac{Q_{GATE}}{V_{BOOT1} - V_{BOOT2}}$$

(EQ. 14)

Typical gate charge values for MOSFETs considered in these types of applications range from 20nC to 100nC. Since the voltage drop across  $Q_{LOWER}$  is negligible,  $V_{BOOT1}$  is simply  $V_{CPVOUT}$  -  $V_D$ . A Schottky diode is recommended to minimize the voltage drop across the bootstrap capacitor during the on-time of the upper MOSFET. Initial calculations with  $V_{BOOT2}$  no less than 4V will quickly help narrow the bootstrap capacitor range.

For example, consider an upper MOSFET is chosen with a maximum gate charge,  $Q_g$ , of 100nC. Limiting the voltage drop across the bootstrap capacitor to 1V results in a value of no less than  $0.1\mu$ F. The tolerance of the ceramic capacitor should also be considered when selecting the final bootstrap capacitance value.

A fast recovery diode is recommended when selecting a bootstrap diode to reduce the impact of reverse recovery charge loss. Otherwise, the recovery charge,  $Q_{RR}$ , would have to be added to the gate charge of the MOSFET and taken into consideration when calculating the minimum bootstrap capacitance.

## ISL6406 DC/DC Converter Application Circuit

The circuit below shows the device as it is configured on the ISL6406 evaluation board. Detailed information on the

circuit, including a complete Bill-of-Materials and circuit board description, can be found in Application Note AN1031.

NOTE: Remove  $R_3$ ,  $R_4$ ,  $C_9$ , and  $R_5$  from the board.

#### **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to the web to make sure that you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                           |

|--------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Oct 21, 2015 | FN9073.9 | Updated the Ordering Information table on page 1.<br>Added Revision History and About Intersil sections.<br>Updated Package Outline Drawing M16.173 to the latest revision. Changes are as follows:<br>-Convert to new POD format by moving dimensions from table onto drawing and adding land pattern. No<br>dimension changes. |

#### About Intersil

Intersil Corporation is a leading provider of innovative power management and precision analog solutions. The company's products address some of the largest markets within the industrial and infrastructure, mobile computing and high-end consumer markets.

For the most updated datasheet, application notes, related documentation and related parts, please see the respective product information page found at <u>www.intersil.com</u>.

You may report errors or suggestions for improving this datasheet by visiting www.intersil.com/ask.

Reliability reports are also available from our website at www.intersil.com/support.

© Copyright Intersil Americas LLC 2002-2015. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

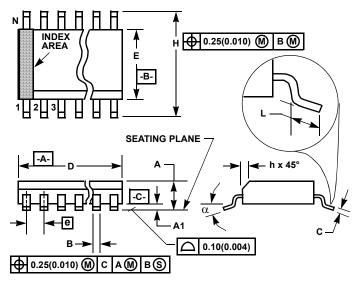

## Small Outline Plastic Packages (SOIC)

#### NOTES:

- 1. Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication Number 95.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusion and gate burrs shall not exceed 0.15mm (0.006 inch) per side.

- 4. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- 5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- 6. "L" is the length of terminal for soldering to a substrate.

- 7. "N" is the number of terminal positions.

- 8. Terminal numbers are shown for reference only.

- 9. The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

- 10. Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

#### M16.15 (JEDEC MS-012-AC ISSUE C) 16 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

|        | INC    | INCHES    |      | MILLIMETERS |       |

|--------|--------|-----------|------|-------------|-------|

| SYMBOL | MIN    | MAX       | MIN  | MAX         | NOTES |

| A      | 0.0532 | 0.0688    | 1.35 | 1.75        | -     |

| A1     | 0.0040 | 0.0098    | 0.10 | 0.25        | -     |

| В      | 0.013  | 0.020     | 0.33 | 0.51        | 9     |

| С      | 0.0075 | 0.0098    | 0.19 | 0.25        | -     |

| D      | 0.3859 | 0.3937    | 9.80 | 10.00       | 3     |

| E      | 0.1497 | 0.1574    | 3.80 | 4.00        | 4     |

| е      | 0.050  | 0.050 BSC |      | 1.27 BSC    |       |

| Н      | 0.2284 | 0.2440    | 5.80 | 6.20        | -     |

| h      | 0.0099 | 0.0196    | 0.25 | 0.50        | 5     |

| L      | 0.016  | 0.050     | 0.40 | 1.27        | 6     |

| Ν      | 1      | 16        |      | 16          |       |

| α      | 0°     | 8°        | 0°   | 8°          | -     |

Rev. 1 6/05

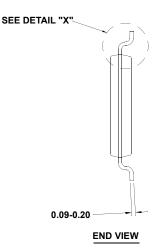

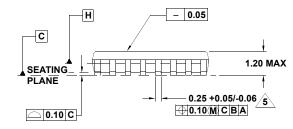

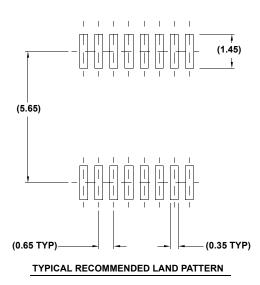

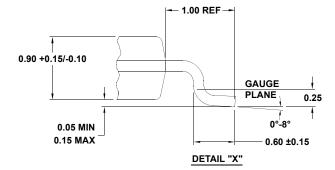

## Package Outline Drawing

#### M16.173

16 LEAD THIN SHRINK SMALL OUTLINE PACKAGE (TSSOP) Rev 2, 5/10

NOTES:

- 1. Dimension does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 per side.

- 2. Dimension does not include interlead flash or protrusion. Interlead flash or protrusion shall not exceed 0.25 per side.

- 3. Dimensions are measured at datum plane H.

- 4. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 5. Dimension does not include dambar protrusion. Allowable protrusion shall be 0.08mm total in excess of dimension at maximum material condition. Minimum space between protrusion and adjacent lead is 0.07mm.

- 6. Dimension in ( ) are for reference only.

- 7. Conforms to JEDEC MO-153.

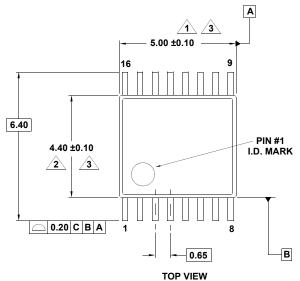

## Package Outline Drawing

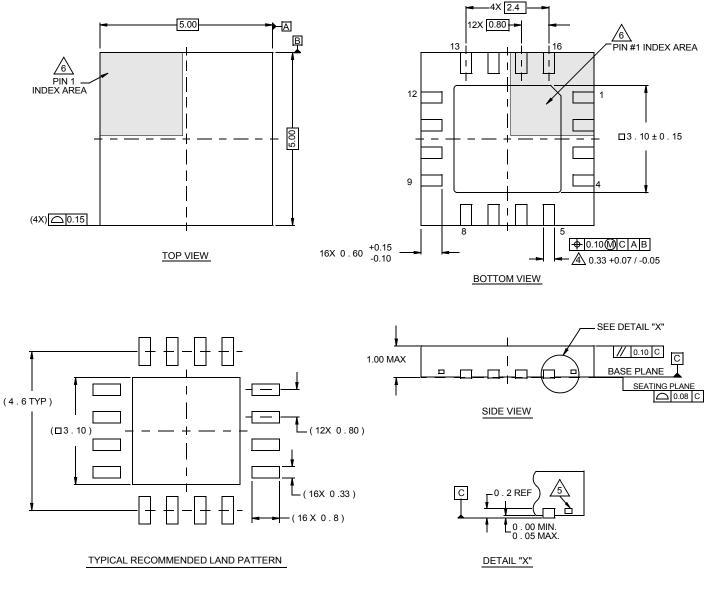

#### L16.5x5B

16 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 2, 02/08

NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSE Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.