# DSLVDS1047-1048EVM User's Guide

The DSLVDS1047-1048EVM is an evaluation module designed for performance and functional evaluation of the Texas Instruments DSLVDS1047 3-V LVDS Quad CMOS Differential Line Driver and DSLVDS1048 3-V LVDS CMOS Differential Line Receiver. With this kit, users can quickly evaluate the output waveform characteristics and signal integrity supported by the DSLVDS1047 and DSLVDS1048. Header pins allow access to the DSLVDS1047 and DSLVDS1048 inputs and outputs and also facilitate connection to lab equipment or user systems for performance evaluation.

Figure 1. DSLVDS1047-1048EVM

#### Contents

|   | Features             |     |

|---|----------------------|-----|

| 2 | Applications         | . 3 |

| 3 | Ordering Information | . 3 |

| 4 | Setup                | . 4 |

| 5 | Bill of Materials    | . 8 |

| 6 | Schematic            | . 9 |

|   | EVM Layout           |     |

#### List of Figures

| 1  | DSLVDS1047-1048EVM                                     | 1  |

|----|--------------------------------------------------------|----|

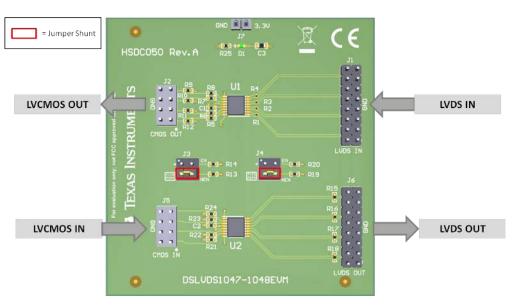

| 2  | DSLVDS1047-1048EVM Input and Output Diagram            | 4  |

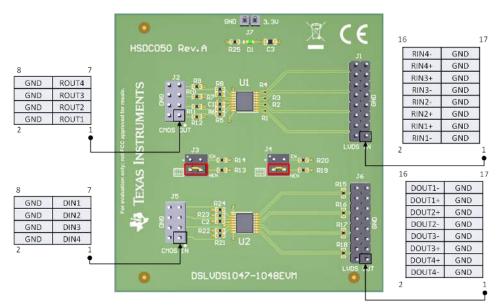

| 3  | DSLVDS1047-1048EVM Input and Output Header Connections | 4  |

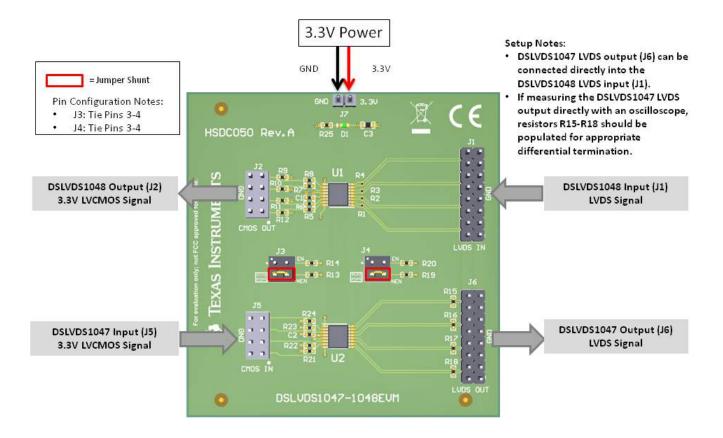

| 4  | DSLVDS1047-1048EVM Setup Configuration                 | 5  |

| 5  | DSLVDS1047 3.3 V LVCMOS Input                          | 7  |

| 6  | DSLVDS1047 Differential LVDS Output                    | 7  |

| 7  | DSLVDS1047 Single-Ended LVDS Output                    | 7  |

| 8  | DSLVDS1048 LVCMOS Output                               | 7  |

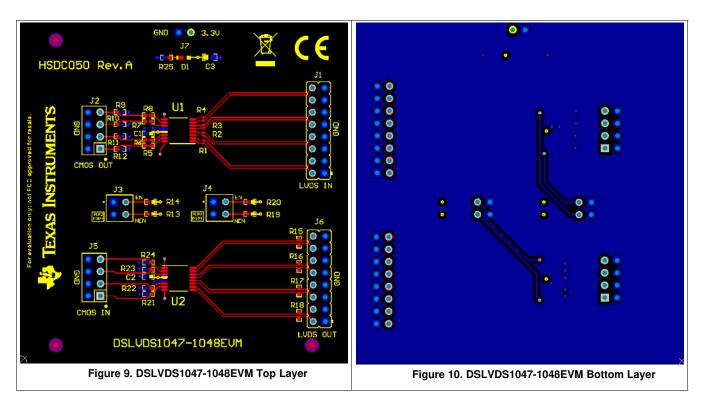

| 9  | DSLVDS1047-1048EVM Top Layer                           | 10 |

| 10 | DSLVDS1047-1048EVM Bottom Layer                        | 10 |

|    |                                                        |    |

### List of Tables

| 1 | Description of Jumper Settings | 4 |

|---|--------------------------------|---|

|---|--------------------------------|---|

## **Trademarks**

All trademarks are the property of their respective owners.

Texas Instruments

#### www.ti.com

#### 1 Features

### DSLVDS1047:

- Converts Single-Ended LVCMOS to Differential LVDS

- >400 Mbps (200 MHz) Switching Rates

- Single Supply Operation:  $VDD = 3.3 V \pm 5\%$

- Low Power (13 mW at 3.3 V Static)

- Interoperable With Existing 5-V LVDS Receivers

- Flow-Through Pinout Simplifies PCB Layout

## DSLVDS1048:

- Converts Differential LVDS to Single-Ended LVCMOS

- >400 Mbps (200 MHz) Switching Rates

- Single Supply Operation: VDD = 3.3 V ± 5%

- Accepts Small ±35 mV Differential Signaling

- Supports Input Failsafe Open, Short, and Terminated

- Low Power Design (40 mW at 3.3 V Static)

- · Flow-Through Pinout Simplifies PCB Layout

# 2 Applications

- Multifunction Printers

- Board-to-Board Communication

- Test and Measurement

- Printers

- Data Center Interconnect

- Lab Instrumentation

- Ultrasound Scanners

# 3 Ordering Information

| EVM ID             | Device ID              | Device Package |  |

|--------------------|------------------------|----------------|--|

| DSLVDS1047-1048EVM | DSLVDS1047, DSLVDS1048 | SOIC           |  |

#### Setup

## 4 Setup

The DSLVDS1047 is a LVDS Quad CMOS Differential Line Driver, and the DSLVDS1048 is a LVDS Quad CMOS Differential Line Receiver. When operating the DSLVDS1047-1048EVM, jumper setting definitions can be referenced in Table 1, while signal input and output connection descriptions can be found in Figure 2 and Figure 3. When using the DSLVDS1047 and DSLVDS1048 together, the typical configuration is to connect the DSLVDS1047 outputs (J6) such that they drive the inputs of the DSLVDS1048 (J1).

| Component | Name    | Comments                                                            |

|-----------|---------|---------------------------------------------------------------------|

| J7        | VDD/GND | 3.3 V VDD power supply                                              |

| J3        | ENABLE1 | Leave Pins 1 and 2 open, and tie Pins 3 and 4 to enable DSLVDS1048. |

| J4        | ENABLE2 | Leave Pins 1 and 2 open, and tie Pins 3 and 4 to enable DSLVDS1047. |

| Table 1. | . Description | of Jumper | Settings |

|----------|---------------|-----------|----------|

|----------|---------------|-----------|----------|

Figure 2. DSLVDS1047-1048EVM Input and Output Diagram

Figure 3. DSLVDS1047-1048EVM Input and Output Header Connections

## 4.1 Hardware Description and Setup

For hardware setup and connections, reference the diagrams in Figure 3 and Figure 4.

1. Connect a 3.3 V DC power supply (30 mA max) to the header J7 on EVM.

2. Install a shunt jumper on J3 Pins 3-4 to tie DSLVDS1048 NEN to GND and install a shunt jumper on J4 Pins 3-4 to tie DSLVDS1047 NEN to GND for appropriate operation, as shown in Figure 4.

3. Apply a high-speed 3.3 V LVCMOS signal to the DSLVDS1047 inputs on header J5.

4. The DSLVDS1047 LVDS output signals can be measured deferentially on an oscilloscope by applying a Tektronix P6247 probe or equivalent differential probe at header J6 to measure the differential signal across the 100  $\Omega$  termination resistors R15-R18. The expected output waveform is a ±350 mV LVDS signal.

5. Apply a high-speed  $\pm 350 \text{ mV}$  (700 mV<sub>pp</sub> differential) LVDS signal to the DSLVDS1048 inputs on header J1. If desired, the LVDS inputs can be provided by connecting the LVDS outputs on header J4 to the desired LVDS input pins on header J1. If this is done, remove resistors R15-R18 to avoid double-termination.

6. The DSLVDS1048 LVCMOS output signals can be measured on an oscilloscope by applying a Tektronix P6247 probe or equivalent differential probe at header J2.

## Figure 4. DSLVDS1047-1048EVM Setup Configuration

Setup

In order to measure LVDS signals properly, a 100  $\Omega$  termination resistor must be present across each differential pair at the point of measurement. However, if multiple 100  $\Omega$  termination resistors are placed across a differential pair between the transmitter and receiver, the signal becomes double terminated. Double termination should be avoided, since this reduces the output amplitude and noise margin.

By factory default, the DSLVDS1047-1048EVM comes with stuffed termination resistors R1-R4 on the DSLVDS1048 inputs and stuffed termination resistors R15-R18 on the DSLVDS1047 outputs.

Remove R15-R18...

- if the DSLVDS1047 output interfaces with a DSLVDS1048 input by connecting J6 to J1.

- if the DSLVDS1047 output interfaces with an external load that has an appropriate 100  $\Omega$  differential termination.

Populate R15-R18 with 100  $\Omega$  termination resistors (or leave R15-R18 populated)...

- if the DSLVDS1047 output is measured by a high-impedance differential probe.

- if the DSLVDS1047 output interfaces with an external load that does **not** have an appropriate 100  $\Omega$  differential termination.

#### Setup

# 4.2 DSLVDS1047-1048EVM Performance Plots

The following plots show typical waveforms measured on the DSLVDS1047-1048EVM inputs and outputs using the hardware setup in Figure 4. For these measurements, the following parameters were used:

- Operating Frequency: 200 MHz (400 Mbps)

- DSLVDS1047 Input: 3.3 V LVCMOS sine wave to DIN1

- DSLVDS1047 Output: Measured with 100  $\Omega$  termination resistor R15 populated across DOUT1±

- DSLVDS1048 Input: LVDS signal to RIN1± from DSLVDS1047 output DOUT1±. 100  $\Omega$  termination resistor R15 removed

- 14295 Acqs 21 Jan 16 14:11:35 6481 Acqs 21 Jan 16 14:07:18 Run Sample Tek Run Sample Buttons Buttons Curs1 Pos Curs1 Pos 306.0mV 3.3V Curs2 Pos Curs2 Pos 0.07 -294.0mV V1: 306.0mV V2: -294.0mV ΔV: -600.0mV V1 V2 8V npl(01) 576.0mV 568.90316m : 424.0m M: 601.4r pl(C1) 3.247 7429 9 M: 3.61 n: 14.28k 40.0m 48.12m 424.0m M: 601.4r 19.52m n: 6.479k 12+ eq(C1) 200.7MHz 200.06338M : 186.9M M: 512.5M : 957.2k n: 14.28k eq(C1) 200.2MHz 199.96458M : 198.4M M: 201.3N : 384.7k n: 6.479k Ch1 1.09 M 2.0ns 5.0GS/s A Ch1 / 1.76V IT 8.0ps/pt Ch1 100mV 0 IT 8.0ps/pt M 2.0ns 5.0GS/s A Ch1 / 24.0mV Figure 6. DSLVDS1047 Differential LVDS Output Figure 5. DSLVDS1047 3.3 V LVCMOS Input Tek Run Sample 8820 Acqs 21 Jan 16 14:08:43 Tek Run Sample 6472 Acqs 21 Jan 16 14:04:46 (Buttons) Buttons Curs1 Pos Curs1 Pos 1.417 3.3V Curs2 Pos Curs2 Pos 1.06V 0.07 1.41V 1.06V -350.0mV V1 V2 8Y 3.3V 0.0V -3.3V ¥1 ¥2 8¥ npl(C1) 220.40644 260.0mV npl(01) 3.1391202 140.0m M: 300.0r 28.49m n: 7.671k : 2.99 M: 3.4 : 59.31m n: 6.459 E. eq(C1) 199.7MHz 200.01325M : 198.8M M: 201.3N : 284.9k n: 6.459k q(C1)! 19 200.07653M 196.5MH; 191.3M M: 210.37 2.479M n: 7.671k M 4.0ns 5.0GS/s A Ch1 / 1.8V Ch1 500mV 16.0ps/p IT 8.0ps/p Ch M 2.0ns 5.0GS/s A Ch1 / 1.25Y Figure 7. DSLVDS1047 Single-Ended LVDS Output Figure 8. DSLVDS1048 LVCMOS Output

Copyright © 2018, Texas Instruments Incorporated

DSLVDS1048 Output: Measured at ROUT1

# 5 Bill of Materials

| Part Number      | Description                                                             | Designator                                                   | Quantity |

|------------------|-------------------------------------------------------------------------|--------------------------------------------------------------|----------|

| LMK105BJ104KV-F  | CAP, CERM, 0.1 uF, 10 V,+/-<br>10%, X5R, 0402                           | C1, C2                                                       | 2        |

| CL10A106MQ8NNNC  | CAP, CERM, 10 uF, 6.3 V, +/-<br>20%, X5R, 0603                          | C3                                                           | 1        |

| SML-LX0603GW-TR  | LED, Green, SMD                                                         | D1                                                           | 1        |

| PEC08DAAN        | Header, 2.54 mm, 8x2, Tin,<br>Vertical, TH                              | J1, J6                                                       | 2        |

| PEC04DAAN        | Header, 100 mil, 4x2, Tin, TH                                           | J2, J5                                                       | 2        |

| PEC02DAAN        | Header, 100 mil, 2x2, Tin, TH                                           | J3, J4                                                       | 2        |

| TSW-102-07-T-S   | Header, 2.54 mm, 2x1, Tin, TH                                           | J7                                                           | 1        |

| RC0201JR-07100RL | RES, 100, 5%, 0.05 W, 0201                                              | R1, R2, R3, R4                                               | 4        |

| ERJ-2GE0R00X     | RES, 0, 5%, 0.1 W, AEC-Q200<br>Grade 0, 0402                            | R5, R6, R7, R8                                               | 4        |

| CRCW040210K0FKED | RES, 10.0 k, 1%, 0.063 W,<br>AEC-Q200 Grade 0, 0402                     | R9, R10, R11, R12, R13, R14,<br>R19, R20, R21, R22, R23, R24 | 12       |

| ERJ-2RKF1000X    | RES, 100, 1%, 0.1 W, 0402                                               | R15, R16, R17, R18                                           | 4        |

| CRCW0402301RFKED | RES, 301, 1%, 0.063 W, AEC-<br>Q200 Grade 0, 0402                       | R25                                                          | 1        |

| SNT-100-BK-G     | Shunt, 100mil, Gold plated,<br>Black                                    | SH-J3, SH-J4                                                 | 2        |

| DSLVDS1048PWR    | 3-V LVDS Quad CMOS<br>Differential Line Receiver,<br>PW0016A (TSSOP-16) | U1                                                           | 1        |

| DSLVDS1047PWR    | 3-V LVDS Quad CMOS<br>Differential Line Driver,<br>PW0016A (TSSOP-16)   | U2                                                           | 1        |

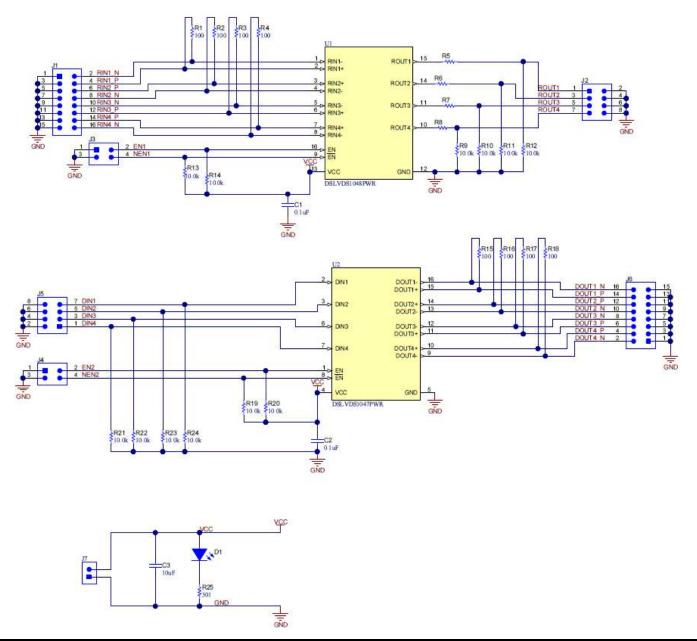

# 6 Schematic

EVM Layout

www.ti.com

## 7 EVM Layout

Figure 9 and Figure 10 show the DSLVDS1047-1048EVM layout. The DSLVDS1047 and DSLVDS1048 inputs and outputs can be accessed via header pins.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2018, Texas Instruments Incorporated