# Inverting Switching Regulators - Step-Up/Down 3.0 A

# MC34166, MC33166

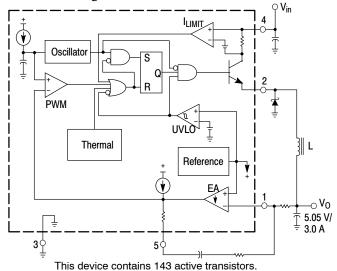

The MC34166, MC33166 series are high performance fixed frequency power switching regulators that contain the primary functions required for dc-to-dc converters. This series was specifically designed to be incorporated in step-down and voltage-inverting configurations with a minimum number of external components and can also be used cost effectively in step-up applications.

These devices consist of an internal temperature compensated reference, fixed frequency oscillator with on-chip timing components, latching pulse width modulator for single pulse metering, high gain error amplifier, and a high current output switch.

Protective features consist of cycle-by-cycle current limiting, undervoltage lockout, and thermal shutdown. Also included is a low power standby mode that reduces power supply current to 36 μA.

#### **Features**

- Output Switch Current in Excess of 3.0 A

- Fixed Frequency Oscillator (72 kHz) with On-Chip Timing

- Provides 5.05 V Output without External Resistor Divider

- Precision 2% Reference

- 0% to 95% Output Duty Cycle

- Cycle-by-Cycle Current Limiting

- Undervoltage Lockout with Hysteresis

- Internal Thermal Shutdown

- Operation from 7.5 V to 40 V

- Standby Mode Reduces Power Supply Current to 36 μA

- Economical 5-Lead TO-220 Package with Two Optional Leadforms

- Also Available in Surface Mount D<sup>2</sup>PAK Package

- Moisture Sensitivity Level (MSL) Equals 1

- Pb-Free Packages are Available

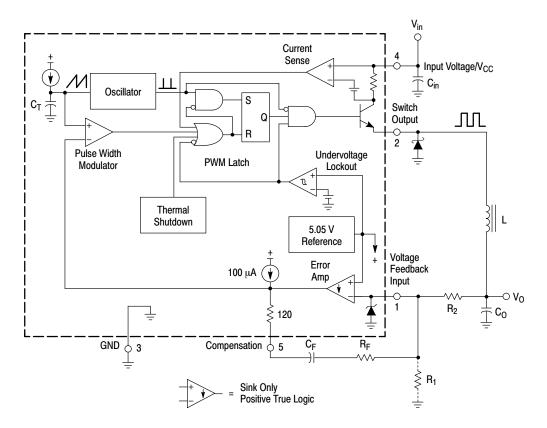

Figure 1. Simplified Block Diagram (Step Down Application)

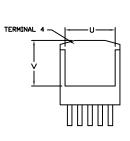

#### MARKING DIAGRAMS

TO-220 TV SUFFIX CASE 314B

Heatsink surface connected to Pin 3

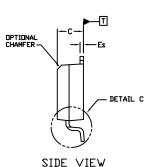

D<sup>2</sup>PAK D2T SUFFIX CASE 936A

Heatsink surface (shown as terminal 6 in case outline drawing) is connected to Pin 3

x = 3 or 4

A = Assembly Location

WL = Wafer Lot Y = Year

WW = Work Week

G = Pb-Free Package

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

#### **MAXIMUM RATINGS**

| Rating                                                    | Symbol                 | Value                     | Unit |

|-----------------------------------------------------------|------------------------|---------------------------|------|

| Power Supply Input Voltage                                | V <sub>CC</sub>        | 40                        | V    |

| Switch Output Voltage Range                               | V <sub>O(switch)</sub> | -1.5 to + V <sub>in</sub> | V    |

| Voltage Feedback and Compensation Input Voltage Range     | $V_{FB}$ , $V_{Comp}$  | -1.0 to + 7.0             | V    |

| Power Dissipation                                         |                        |                           |      |

| Case 314A, 314B and 314D (T <sub>A</sub> = +25°C)         | $P_{D}$                | Internally Limited        | W    |

| Thermal Resistance, Junction-to-Ambient                   | $\theta_{\sf JA}$      | 65                        | °C/W |

| Thermal Resistance, Junction-to-Case                      | $\theta_{\sf JC}$      | 5.0                       | °C/W |

| Case 936A (D <sup>2</sup> PAK) ( $T_A = +25^{\circ}C$ )   | $P_{D}$                | Internally Limited        | W    |

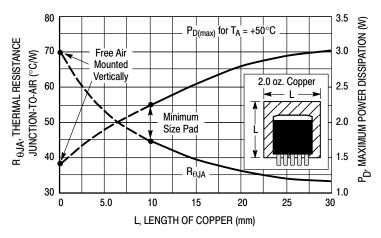

| Thermal Resistance, Junction-to-Ambient                   | $\theta_{\sf JA}$      | 70                        | °C/W |

| Thermal Resistance, Junction-to-Case                      | $\theta_{\sf JC}$      | 5.0                       | °C/W |

| Operating Junction Temperature                            | $T_J$                  | +150                      | °C   |

| Operating Ambient Temperature (Note 2) MC34166<br>MC33166 | T <sub>A</sub>         | 0 to + 70<br>- 40 to + 85 | °C   |

| Storage Temperature Range                                 | T <sub>stg</sub>       | – 65 to +150              | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

Machine Model Method 200 V. 2.  $T_{low} = 0^{\circ}C$  for MC34166 = - 40°C for MC33166

$T_{high} = +70^{\circ}C \text{ for MC34166}$ = +85°C for MC33166

#### **ORDERING INFORMATION**

| Device        | Operating<br>Temperature Range | Package                                         | Shipping <sup>†</sup> |

|---------------|--------------------------------|-------------------------------------------------|-----------------------|

| MC33166D2TG   |                                | D <sup>2</sup> PAK – Surface Mount<br>(Pb-Free) | 50 Units/Rail         |

| MC33166D2TR4G | T <sub>A</sub> = -40° to +85°C | D <sup>2</sup> PAK – Surface Mount<br>(Pb–Free) | 800 / Tape & Reel     |

| MC33166TVG    |                                | TO-220 - Vertical Mount<br>(Pb-Free)            | 50 Units/Rail         |

| MC34166D2TR4G | T <sub>A</sub> = 0° to +70°C   | D <sup>2</sup> PAK – Surface Mount<br>(Pb–Free) | 800 / Tape & Reel     |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

should not be assumed, damage may occur and reliability may be affected.

1. This device series contains ESD protection and exceeds the following tests:

Human Body Model 2000 V per MIL–STD–883, Method 3015.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 12 \text{ V}$ , for typical values  $T_A = +25^{\circ}\text{C}$ , for min/max values  $T_A$  is the operating ambient temperature range that applies [Notes 3, 4], unless otherwise noted.)

| Characteristic                                                                                                                                                                                  |                                                       | Symbol                                     | Min          | Тур                    | Max                    | Unit     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------|--------------|------------------------|------------------------|----------|

| OSCILLATOR                                                                                                                                                                                      |                                                       | •                                          |              | •                      |                        |          |

| Frequency (V <sub>CC</sub> = 7.5 V to 40 V)                                                                                                                                                     | $T_A = +25^{\circ}C$<br>$T_A = T_{low}$ to $T_{high}$ | fosc                                       | 65<br>62     | 72<br>-                | 79<br>81               | kHz      |

| ERROR AMPLIFIER                                                                                                                                                                                 |                                                       |                                            |              |                        |                        |          |

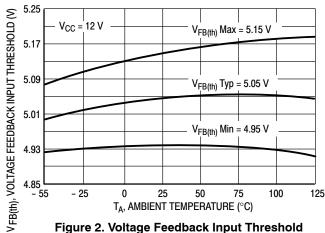

| Voltage Feedback Input Threshold                                                                                                                                                                | $T_A = +25^{\circ}C$<br>$T_A = T_{low}$ to $T_{high}$ | V <sub>FB(th)</sub>                        | 4.95<br>4.85 | 5.05<br>-              | 5.15<br>5.2            | V        |

| Line Regulation ( $V_{CC} = 7.5 \text{ V to } 40 \text{ V}, T_A = +$                                                                                                                            | 25°C)                                                 | Reg <sub>line</sub>                        | -            | 0.03                   | 0.078                  | %/V      |

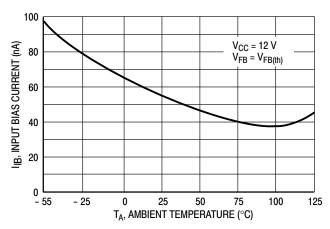

| Input Bias Current (V <sub>FB</sub> = V <sub>FB(th)</sub> + 0.15 V)                                                                                                                             |                                                       | I <sub>IB</sub>                            | _            | 0.15                   | 1.0                    | μΑ       |

| Power Supply Rejection Ratio (V <sub>CC</sub> = 10 V to                                                                                                                                         | o 20 V, f = 120 Hz)                                   | PSRR                                       | 60           | 80                     | -                      | dB       |

| Output Voltage Swing<br>High State ( $I_{Source}$ = 75 $\mu$ A, $V_{FB}$ = 4.5 V)<br>Low State ( $I_{Sink}$ = 0.4 mA, $V_{FB}$ = 5.5 V)                                                         |                                                       | V <sub>OH</sub><br>V <sub>OL</sub>         | 4.2<br>-     | 4.9<br>1.6             | -<br>1.9               | ٧        |

| PWM COMPARATOR                                                                                                                                                                                  |                                                       |                                            |              |                        |                        |          |

| Duty Cycle  Maximum (V <sub>FB</sub> = 0 V)  Minimum (V <sub>Comp</sub> = 1.9 V)                                                                                                                |                                                       | DC <sub>(max)</sub><br>DC <sub>(min)</sub> | 92<br>0      | 95<br>0                | 100<br>0               | %        |

| SWITCH OUTPUT                                                                                                                                                                                   |                                                       |                                            |              |                        |                        |          |

| Output Voltage Source Saturation ( $V_{CC} = 7$ .                                                                                                                                               | 5 V, I <sub>Source</sub> = 3.0 A)                     | V <sub>sat</sub>                           | -            | (V <sub>CC</sub> -1.5) | (V <sub>CC</sub> -1.8) | V        |

| Off-State Leakage ( $V_{CC} = 40 \text{ V}$ , Pin 2 = GN                                                                                                                                        | D)                                                    | I <sub>sw(off)</sub>                       | _            | 0                      | 100                    | μΑ       |

| Current Limit Threshold                                                                                                                                                                         |                                                       | I <sub>pk(switch)</sub>                    | 3.3          | 4.3                    | 6.0                    | Α        |

| Switching Times ( $V_{CC}$ = 40 V, $I_{pk}$ = 3.0 A, L = Output Voltage Rise Time Output Voltage Fall Time                                                                                      | t <sub>r</sub><br>t <sub>f</sub>                      | -<br>-                                     | 100<br>50    | 200<br>100             | ns                     |          |

| UNDERVOLTAGE LOCKOUT                                                                                                                                                                            |                                                       |                                            |              |                        |                        |          |

| Startup Threshold ( $V_{CC}$ Increasing, $T_A = +2$                                                                                                                                             | V <sub>th(UVLO)</sub>                                 | 5.5                                        | 5.9          | 6.3                    | V                      |          |

| Hysteresis (V <sub>CC</sub> Decreasing, T <sub>A</sub> = +25°C)                                                                                                                                 |                                                       | V <sub>H(UVLO)</sub>                       | 0.6          | 0.9                    | 1.2                    | V        |

| TOTAL DEVICE                                                                                                                                                                                    |                                                       |                                            |              |                        |                        |          |

| Power Supply Current ( $T_A = +25^{\circ}C$ )<br>Standby ( $V_{CC} = 12 \text{ V}$ , $V_{Comp} < 0.15 \text{ V}$ )<br>Operating ( $V_{CC} = 40 \text{ V}$ , Pin 1 = GND for maximum duty cycle) |                                                       | I <sub>CC</sub>                            |              | 36<br>31               | 100<br>55              | μA<br>mA |

Figure 2. Voltage Feedback Input Threshold versus Temperature

Figure 3. Voltage Feedback Input Bias Current versus Temperature

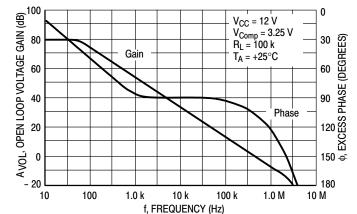

Figure 4. Error Amp Open Loop Gain and Phase versus Frequency

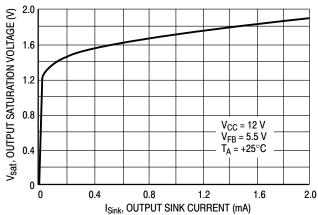

Figure 5. Error Amp Output Saturation versus Sink Current

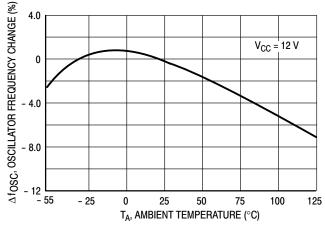

Figure 6. Oscillator Frequency Change versus Temperature

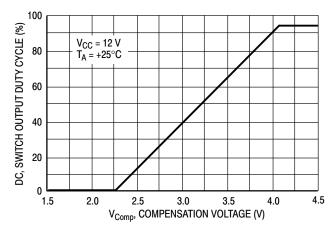

Figure 7. Switch Output Duty Cycle versus Compensation Voltage

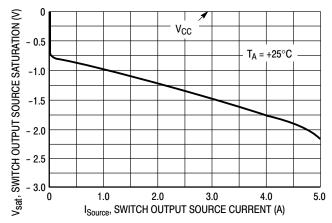

Figure 8. Switch Output Source Saturation versus Source Current

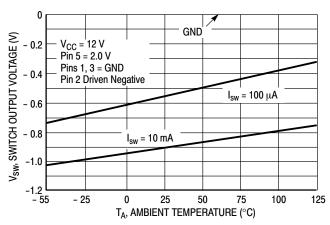

Figure 9. Negative Switch Output Voltage versus Temperature

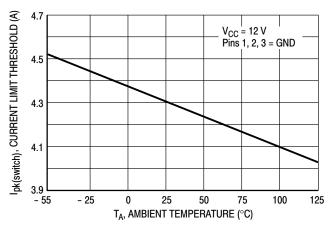

Figure 10. Switch Output Current Limit

Threshold versus Temperature

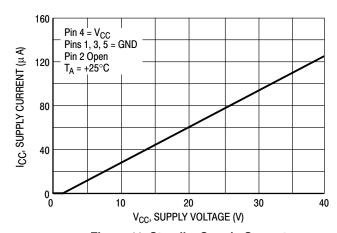

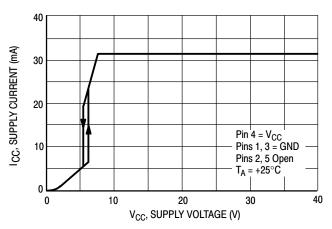

Figure 11. Standby Supply Current versus Supply Voltage

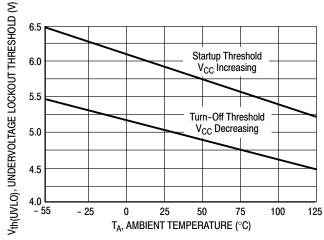

Figure 12. Undervoltage Lockout Threshold versus Temperature

Figure 13. Operating Supply Current versus Supply Voltage

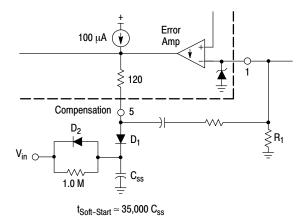

Figure 14. MC34166 Representative Block Diagram

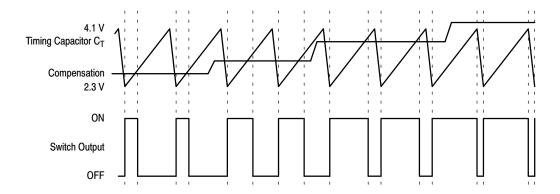

Figure 15. Timing Diagram

#### INTRODUCTION

The MC34166, MC33166 series are monolithic power switching regulators that are optimized for dc-to-dc converter applications. These devices operate as fixed frequency, voltage mode regulators containing all the active functions required to directly implement step-down and voltage-inverting converters with a minimum number of external components. They can also be used cost effectively in step-up converter applications. Potential markets include automotive, computer, industrial, and cost sensitive consumer products. A description of each section of the device is given below with the representative block diagram shown in Figure 14.

#### Oscillator

The oscillator frequency is internally programmed to 72 kHz by capacitor  $C_T$  and a trimmed current source. The charge to discharge ratio is controlled to yield a 95% maximum duty cycle at the Switch Output. During the discharge of  $C_T$ , the oscillator generates an internal blanking pulse that holds the inverting input of the AND gate high, disabling the output switch transistor. The nominal oscillator peak and valley thresholds are 4.1 V and 2.3 V respectively.

#### **Pulse Width Modulator**

The Pulse Width Modulator consists of a comparator with the oscillator ramp voltage applied to the noninverting input, while the error amplifier output is applied into the inverting input. Output switch conduction is initiated when  $C_T$  is discharged to the oscillator valley voltage. As  $C_T$  charges to a voltage that exceeds the error amplifier output, the latch resets, terminating output transistor conduction for the duration of the oscillator ramp—up period. This PWM/Latch combination prevents multiple output pulses during a given oscillator clock cycle. Figures 7 and 15 illustrate the switch output duty cycle versus the compensation voltage.

#### **Current Sense**

The MC34166 series utilizes cycle-by-cycle current limiting as a means of protecting the output switch transistor from overstress. Each on-cycle is treated as a separate situation. Current limiting is implemented by monitoring the output switch transistor current buildup during conduction, and upon sensing an overcurrent condition, immediately turning off the switch for the duration of the oscillator ramp-up period.

The collector current is converted to a voltage by an internal trimmed resistor and compared against a reference by the Current Sense comparator. When the current limit threshold is reached, the comparator resets the PWM latch. The current limit threshold is typically set at 4.3 A. Figure 10 illustrates switch output current limit threshold versus temperature.

#### **Error Amplifier and Reference**

A high gain Error Amplifier is provided with access to the inverting input and output. This amplifier features a typical dc voltage gain of 80 dB, and a unity gain bandwidth of 600 kHz with 70 degrees of phase margin (Figure 4). The noninverting

input is biased to the internal 5.05 V reference and is not pinned out. The reference has an accuracy of  $\pm$  2.0% at room temperature. To provide 5.0 V at the load, the reference is programmed 50 mV above 5.0 V to compensate for a 1.0% voltage drop in the cable and connector from the converter output. If the converter design requires an output voltage greater than 5.05 V, resistor  $R_1$  must be added to form a divider network at the feedback input as shown in Figures 14 and 19. The equation for determining the output voltage with the divider network is:

$$V_{out} = 5.05 \left( \frac{R_2}{R_1} + 1 \right)$$

External loop compensation is required for converter stability. A simple low-pass filter is formed by connecting a resistor (R<sub>2</sub>) from the regulated output to the inverting input, and a series resistor-capacitor (R<sub>F</sub>, C<sub>F</sub>) between Pins 1 and 5. The compensation network component values shown in each of the applications circuits were selected to provide stability over the tested operating conditions. The step-down converter (Figure 19) is the easiest to compensate for stability. The step-up (Figure 21) and voltage-inverting (Figure 23) configurations operate as continuous conduction flyback converters, and are more difficult to compensate. The simplest way to optimize the compensation network is to observe the response of the output voltage to a step load change, while adjusting R<sub>F</sub> and C<sub>F</sub> for critical damping. The final circuit should be verified for stability under four boundary conditions. These conditions are minimum and maximum input voltages, with minimum and maximum loads.

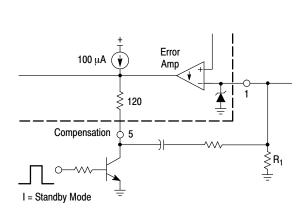

By clamping the voltage on the error amplifier output (Pin 5) to less than 150 mV, the internal circuitry will be placed into a low power standby mode, reducing the power supply current to  $36 \,\mu\text{A}$  with a 12 V supply voltage. Figure 11 illustrates the standby supply current versus supply voltage.

The Error Amplifier output has a 100  $\mu A$  current source pullup that can be used to implement soft–start. Figure 18 shows the current source charging capacitor  $C_{SS}$  through a series diode. The diode disconnects  $C_{SS}$  from the feedback loop when the 1.0 M resistor charges it above the operating range of Pin 5.

#### **Switch Output**

The output transistor is designed to switch a maximum of 40 V, with a minimum peak collector current of 3.3 A. When configured for step-down or voltage-inverting applications, as in Figures 19 and 23, the inductor will forward bias the output rectifier when the switch turns off. Rectifiers with a high forward voltage drop or long turn-on delay time should not be used. If the emitter is allowed to go sufficiently negative, collector current will flow, causing additional device heating and reduced conversion efficiency. Figure 9 shows that by clamping the emitter to 0.5 V, the collector current will be in the range of  $100 \text{ }\mu\text{A}$  over temperature. A 1N5822 or

equivalent Schottky barrier rectifier is recommended to fulfill these requirements.

#### **Undervoltage Lockout**

An Undervoltage Lockout comparator has been incorporated to guarantee that the integrated circuit is fully functional before the output stage is enabled. The internal 5.05 V reference is monitored by the comparator which enables the output stage when  $V_{\rm CC}$  exceeds 5.9 V. To prevent erratic output switching as the threshold is crossed, 0.9 V of hysteresis is provided.

#### **Thermal Protection**

Internal Thermal Shutdown circuitry is provided to protect the integrated circuit in the event that the maximum junction temperature is exceeded. When activated, typically at 170°C, the latch is forced into a 'reset' state, disabling the output switch. This feature is provided to prevent catastrophic failures from accidental device overheating. It is not intended to be used as a substitute for proper heatsinking. The MC34166 is contained in a 5–lead TO–220 type package. The tab of the package is common with the center pin (Pin 3) and is normally connected to ground.

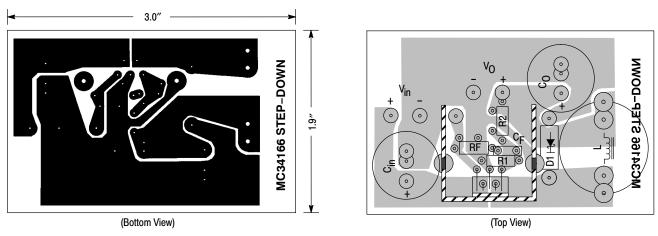

#### **DESIGN CONSIDERATIONS**

Do not attempt to construct a converter on wire-wrap or plug-in prototype boards. Special care should be taken to separate ground paths from signal currents and ground paths from load currents. All high current loops should be kept as short as possible using heavy copper runs to minimize ringing and radiated EMI. For best operation, a tight

component layout is recommended. Capacitors  $C_{IN}$ ,  $C_{O}$ , and all feedback components should be placed as close to the IC as physically possible. It is also imperative that the Schottky diode connected to the Switch Output be located as close to the IC as possible.

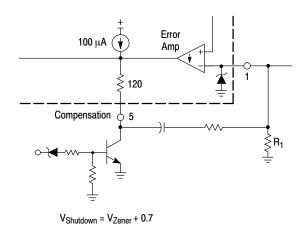

Figure 16. Low Power Standby Circuit

Figure 17. Over Voltage Shutdown Circuit

Figure 18. Soft-Start Circuit

| Test                  | Conditions                                               | Results             |

|-----------------------|----------------------------------------------------------|---------------------|

| Line Regulation       | V <sub>in</sub> = 8.0 V to 36 V, I <sub>O</sub> = 3.0 A  | 5.0 mV = ± 0.05%    |

| Load Regulation       | V <sub>in</sub> = 12 V, I <sub>O</sub> = 0.25 A to 3.0 A | 2.0 mV = ± 0.02%    |

| Output Ripple         | V <sub>in</sub> = 12 V, I <sub>O</sub> = 3.0 A           | 10 mV <sub>pp</sub> |

| Short Circuit Current | $V_{in}$ = 12 V, $R_L$ = 0.1 $\Omega$                    | 4.3 A               |

| Efficiency            | V <sub>in</sub> = 12 V, I <sub>O</sub> = 3.0 A           | 82.8%               |

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns of #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

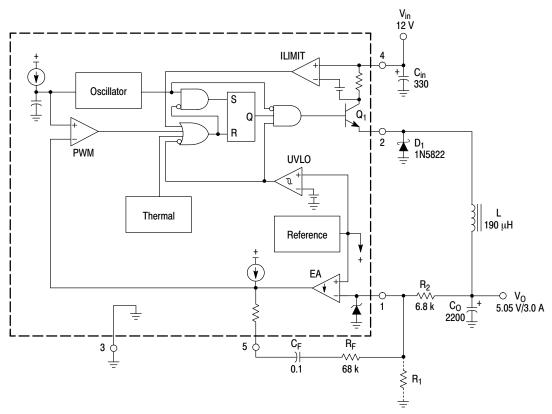

The Step-Down Converter application is shown in Figure 19. The output switch transistor  $Q_1$  interrupts the input voltage, generating a squarewave at the  $LC_0$  filter input. The filter averages the squarewaves, producing a dc output voltage that can be set to any level between  $V_{in}$  and  $V_{ref}$  by controlling the percent conduction time of  $Q_1$  to that of the total oscillator cycle time. If the converter design requires an output voltage greater than 5.05 V, resistor  $R_1$  must be added to form a divider network at the feedback input.

#### Figure 19. Step-Down Converter

Figure 20. Step-Down Converter Printed Circuit Board and Component Layout

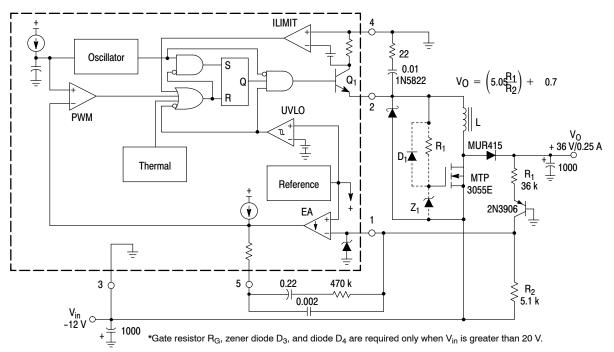

| Test                  | Conditions                                                       | Results                        |

|-----------------------|------------------------------------------------------------------|--------------------------------|

| Line Regulation       | $V_{in} = 8.0 \text{ V to } 24 \text{ V}, I_{O} = 0.6 \text{ A}$ | 23 mV = ± 0.41%                |

| Load Regulation       | $V_{in} = 12 \text{ V}, I_{O} = 0.1 \text{ A to } 0.6 \text{ A}$ | $3.0 \text{ mV} = \pm 0.005\%$ |

| Output Ripple         | V <sub>in</sub> = 12 V, I <sub>O</sub> = 0.6 A                   | 100 mV <sub>pp</sub>           |

| Short Circuit Current | $V_{in}$ = 12 V, $R_L$ = 0.1 $\Omega$                            | 4.0 A                          |

| Efficiency            | V <sub>in</sub> = 12 V, I <sub>O</sub> = 0.6 A                   | 82.8%                          |

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns of #16 AWG on Magnetics Inc. 58350–A2 core.

Heatsink = AAVID Engineering Inc. MC34166: 5903B, or 5930B MTP3055EL: 5925B

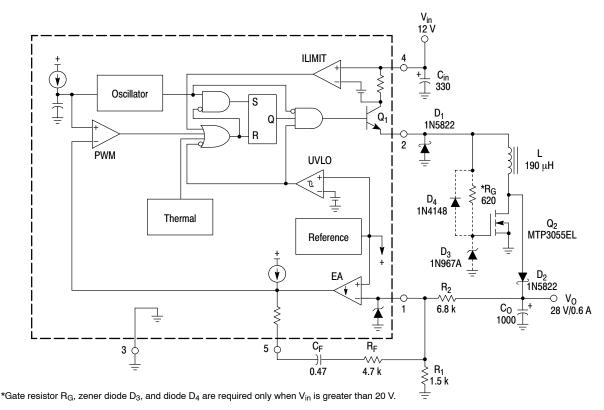

Figure 21 shows that the MC34166 can be configured as a step-up/down converter with the addition of an external power MOSFET. Energy is stored in the inductor during the on-time of transistors  $Q_1$  and  $Q_2$ . During the off-time, the energy is transferred, with respect to ground, to the output filter capacitor and load. This circuit configuration has two significant advantages over the basic step-up converter circuit. The first advantage is that output short-circuit protection is provided by the MC34166, since  $Q_1$  is directly in series with  $V_{in}$  and the load. Second, the output voltage can be programmed to be less than  $V_{in}$ . Notice that during the off-time, the inductor forward biases diodes  $D_1$  and  $D_2$ , transferring its energy with respect to ground rather than with respect to  $V_{in}$ . When operating with  $V_{in}$  greater than 20 V, a gate protection network is required for the MOSFET. The network consists of components  $R_G$ ,  $D_3$ , and  $D_4$ .

Figure 21. Step-Up/Down Converter

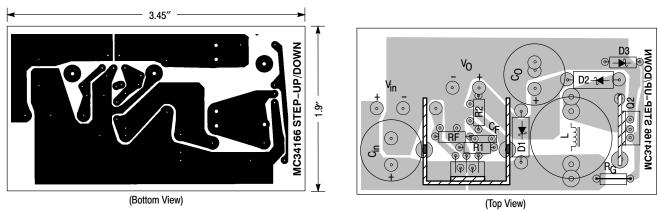

Figure 22. Step-Up/Down Converter Printed Circuit Board and Component Layout

| Test                  | Conditions                                              | Results             |

|-----------------------|---------------------------------------------------------|---------------------|

| Line Regulation       | V <sub>in</sub> = 8.0 V to 24 V, I <sub>O</sub> = 1.0 A | 3.0 mV = ± 0.01%    |

| Load Regulation       | V <sub>in</sub> = 12 V, I <sub>O</sub> = 0.1 A to 1.0 A | 4.0 mV = ± 0.017%   |

| Output Ripple         | V <sub>in</sub> = 12 V, I <sub>O</sub> = 1.0 A          | 80 mV <sub>pp</sub> |

| Short Circuit Current | $V_{in}$ = 12 V, $R_L$ = 0.1 $\Omega$                   | 3.74 A              |

| Efficiency            | V <sub>in</sub> = 12 V, I <sub>O</sub> = 1.0 A          | 81.2%               |

L = Coilcraft M1496–A or General Magnetics Technology GMT–0223, 42 turns of #16 AWG on Magnetics Inc. 58350–A2 core. Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

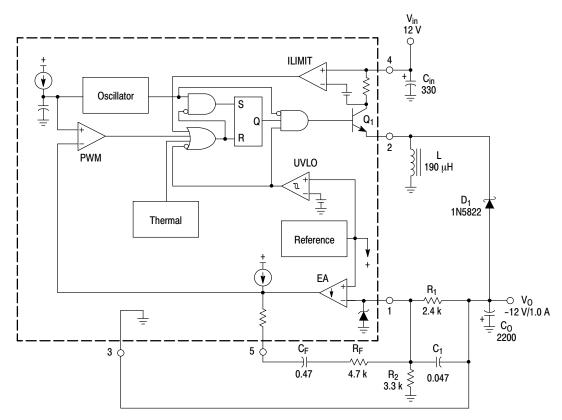

Two potential problems arise when designing the standard voltage–inverting converter with the MC34166. First, the Switch Output emitter is limited to -1.5 V with respect to the ground pin and second, the Error Amplifier's noninverting input is internally committed to the reference and is not pinned out. Both of these problems are resolved by connecting the IC ground pin to the converter's negative output as shown in Figure 23. This keeps the emitter of  $Q_1$  positive with respect to the ground pin and has the effect of reversing the Error Amplifier inputs. Note that the voltage drop across  $R_1$  is equal to 5.05 V when the output is in regulation.

#### Figure 23. Voltage-Inverting Converter

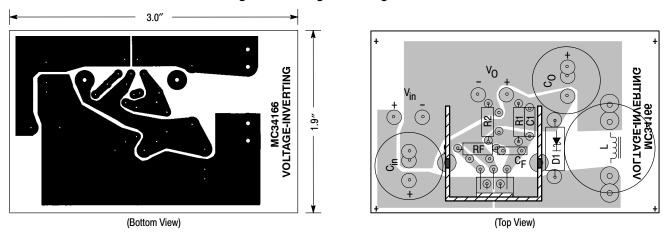

Figure 24. Voltage-Inverting Converter Printed Circuit Board and Component Layout

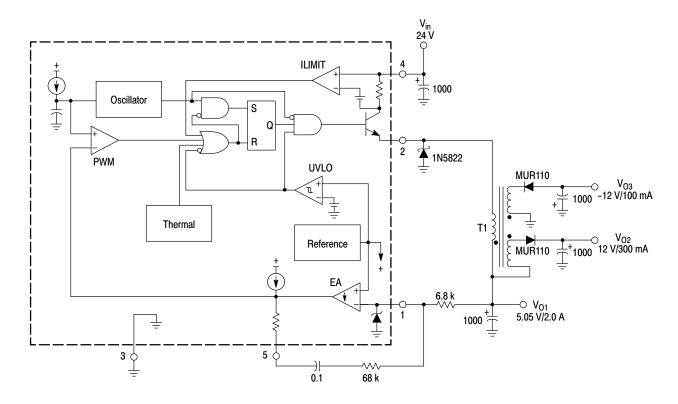

| Tests                 |                        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                | Results                                                           |

|-----------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Line Regulation       | 5.0 V<br>12 V<br>–12 V | $V_{in}$ = 15 V to 30 V, $I_{O1}$ = 2.0 A, $I_{O2}$ = 300 mA, $I_{O3}$ = 100 mA                                                                                                                                                                                                                                                                                                                           | 4.0 mV = ± 0.04%<br>450 mV = ±1.9%<br>350 mV = ±1.5%              |

| Load Regulation       | 5.0 V<br>12 V<br>–12 V | $\begin{aligned} &V_{in} = 24 \text{ V, } I_{O1} = 500 \text{ mA to } 2.0 \text{ A, } I_{O2} = 300 \text{ mA, } I_{O3} = 100 \text{ mA} \\ &V_{in} = 24 \text{ V, } I_{O1} = 2.0 \text{ A, } I_{O2} = 100 \text{ mA to } 300 \text{ mA, } I_{O3} = 100 \text{ mA} \\ &V_{in} = 24 \text{ V, } I_{O1} = 2.0 \text{ A, } I_{O2} = 300 \text{ mA, } I_{O3} = 30 \text{ mA to } 100 \text{ mA} \end{aligned}$ | 2.0 mV = ± 0.02%<br>420 mV = ±1.7%<br>310 mV = ±1.3%              |

| Output Ripple         | 5.0 V<br>12 V<br>–12 V | $V_{in}$ = 24 V, $I_{O1}$ = 2.0 A, $I_{O2}$ = 300 mA, $I_{O3}$ = 100 mA                                                                                                                                                                                                                                                                                                                                   | 50 mV <sub>pp</sub><br>25 mV <sub>pp</sub><br>10 mV <sub>pp</sub> |

| Short Circuit Current | 5.0 V<br>12 V<br>–12 V | $V_{in}$ = 24 V, $R_L$ = 0.1 $\Omega$                                                                                                                                                                                                                                                                                                                                                                     | 4.3 A<br>1.83 A<br>1.47 A                                         |

| Efficiency            | TOTAL                  | V <sub>in</sub> = 24 V, I <sub>O1</sub> = 2.0 A, I <sub>O2</sub> = 300 mA, I <sub>O3</sub> = 100 mA                                                                                                                                                                                                                                                                                                       | 83.3%                                                             |

T1 = Primary: Coilcraft M1496-A or General Magnetics Technology GMT-0223, 42 turns of #16 AWG on Magnetics Inc. 58350-A2 core. Secondary: V<sub>O2</sub> - 65 turns of #26 AWG

$V_{O3} = 96$  turns of #28 AWG

Heatsink = AAVID Engineering Inc. 5903B, or 5930B.

Multiple auxiliary outputs can easily be derived by winding secondaries on the main output inductor to form a transformer. The secondaries must be connected so that the energy is delivered to the auxiliary outputs when the Switch Output turns off. During the OFF time, the voltage across the primary winding is regulated by the feedback loop, yielding a constant Volts/Turn ratio. The number of turns for any given secondary voltage can be calculated by the following equation:

$$# TURNS(SEC) = \frac{VO(SEC) + VF(SEC)}{\left(\frac{VO(PRI) + VF(PRI)}{#TURNS(PRI)}\right)}$$

Note that the 12 V winding is stacked on top of the 5.0 V output. This reduces the number of secondary turns and improves lead regulation. For best auxiliary regulation, the auxiliary outputs should be less than 33% of the total output power.

Figure 25. Triple Output Converter

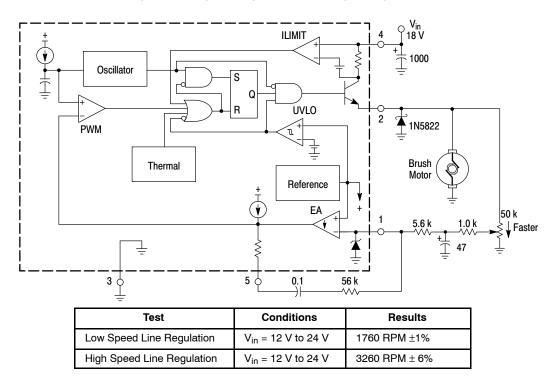

| Test            | Conditions                                                         | Results             |

|-----------------|--------------------------------------------------------------------|---------------------|

| Line Regulation | $V_{in} = -10 \text{ V to} - 20 \text{ V}, I_{O} = 0.25 \text{ A}$ | 250 mV = ± 0.35%    |

| Load Regulation | $V_{in} = -12 \text{ V}, I_O = 0.025 \text{ A to } 0.25 \text{ A}$ | 790 mV = ±1.19%     |

| Output Ripple   | $V_{in} = -12 \text{ V}, I_O = 0.25 \text{ A}$                     | 80 mV <sub>pp</sub> |

| Efficiency      | $V_{in} = -12 \text{ V}, I_O = 0.25 \text{ A}$                     | 79.2%               |

$L = \mbox{Coilcraft M1496-A}$  or ELMACO CHK1050, 42 turns of #16 AWG on Magnetics Inc.  $58350-\mbox{A2}$  core.

Heatsink = AAVID Engineering Inc. 5903B or 5930B

Figure 26. Negative Input/Positive Output Regulator

Figure 27. Variable Motor Speed Control with EMF Feedback Sensing

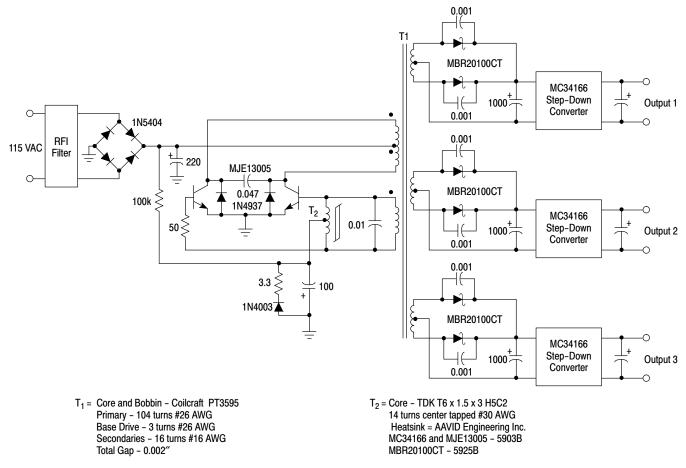

The MC34166 can be used cost effectively in off–line applications even though it is limited to a maximum input voltage of 40 V. Figure 28 shows a simple and efficient method for converting the AC line voltage down to 24 V. This preconverter has a total power rating of 125 W with a conversion efficiency of 90%. Transformer  $T_1$  provides output isolation from the AC line and isolation between each of the secondaries. The circuit self–oscillates at 50 kHz and is controlled by the saturation characteristics of  $T_2$ . Multiple MC34166 post regulators can be used to provide accurate independently regulated outputs for a distributed power system.

Figure 29. D<sup>2</sup>PAK Thermal Resistance and Maximum Power Dissipation versus P.C.B. Copper Length

**Table 1. Design Equations**

| Calculation                 | Step-Down                                                                     | Step-Up/Down                                                                                                      | Voltage-Inverting                                                                             |

|-----------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| ton<br>toff<br>(Notes 1, 2) | $\frac{V_{out} + V_{F}}{V_{in} - V_{sat} - V_{out}}$                          | V <sub>out</sub> + V <sub>F1</sub> + V <sub>F2</sub><br>V <sub>in</sub> - V <sub>satQ1</sub> - V <sub>satQ2</sub> | V <sub>out</sub>   + V <sub>F</sub><br> V <sub>in</sub> - V <sub>sat</sub>                    |

| t <sub>on</sub>             | $\frac{\frac{t_{on}}{t_{off}}}{f_{osc}\left(\frac{t_{on}}{t_{off}}+1\right)}$ | $\frac{\frac{ton}{toff}}{fosc\!\!\left(\!\frac{ton}{toff} + 1\right)}$                                            | $\frac{\frac{ton}{toff}}{fosc\left(\frac{ton}{toff} + 1\right)}$                              |

| Duty Cycle<br>(Note 3)      | t <sub>on</sub> f <sub>osc</sub>                                              | t <sub>on</sub> f <sub>osc</sub>                                                                                  | t <sub>on</sub> f <sub>osc</sub>                                                              |

| I <sub>L avg</sub>          | l <sub>out</sub>                                                              | $I_{out} \left( \frac{t_{on}}{t_{off}} + 1 \right)$                                                               | $I_{out}\left(\frac{t_{on}}{t_{off}} + 1\right)$                                              |

| I <sub>pk(switch)</sub>     | $I_{L \text{ avg}} + \frac{\Delta I_{L}}{2}$                                  | $I_{L \text{ avg }} + \frac{\Delta I_{L}}{2}$                                                                     | $I_{L \text{ avg}} + \frac{\Delta I_{L}}{2}$                                                  |

| L                           | $\left(\frac{V_{in} - V_{sat} - V_{out}}{\Delta I_L}\right) t_{on}$           | $\left(\frac{V_{in}-V_{satQ1}-V_{satQ2}}{\Delta I_L}\right)$ ton                                                  | $\left(\frac{V_{in} - V_{sat}}{\Delta I_L}\right) t_{on}$                                     |

| V <sub>ripple(pp)</sub>     | $\Delta I_L \sqrt{\left(\frac{1}{8f_{OSC}C_O}\right)^2 + (ESR)^2}$            | $\left(\frac{t_{on}}{t_{off}} + 1\right)\sqrt{\left(\frac{1}{t_{osc}C_o}\right)^2 + (ESR)^2}$                     | $\left(\frac{t_{on}}{t_{off}} + 1\right)\sqrt{\left(\frac{1}{t_{osc}C_o}\right)^2 + (ESR)^2}$ |

| V <sub>out</sub>            | $V_{ref}\left(\frac{R_2}{R_1} + 1\right)$                                     | $V_{ref}\left(\frac{R_2}{R_1} + 1\right)$                                                                         | $V_{ref}\left(\frac{R_2}{R_1} + 1\right)$                                                     |

- V<sub>sat</sub> Switch Output source saturation voltage, refer to Figure 8.

V<sub>F</sub> Output rectifier forward voltage drop. Typical value for 1N5822 Schottky barrier rectifier is 0.5 V.

- 3. Duty cycle is calculated at the minimum operating input voltage and must not exceed the guaranteed minimum DC<sub>(max)</sub> specification of 0.92.

The following converter characteristics must be chosen:

- Vout Desired output voltage.

- I<sub>out</sub> Desired output current.

- ΔI<sub>L</sub> Desired peak-to-peak inductor ripple current. For maximum output current especially when the duty cycle is greater than 0.5, it is suggested that  $\Delta I_L$  be chosen to be less than 10% of the average inductor current  $I_{Lavg}$ . This will help prevent  $I_{pk(switch)}$  from reaching the guaranteed minimum current limit threshold of 3.3 A. If the design goal is to use a minimum inductance value, let  $\Delta I_L = 2$  ( $I_{Lavg}$ ). This will proportionally reduce the converter's output current capability.

- V<sub>ripple(pp)</sub> Desired peak-to-peak output ripple voltage. For best performance, the ripple voltage should be kept to less than 2% of V<sub>out</sub>. Capacitor CO should be a low equivalent series resistance (ESR) electrolytic designed for switching regulator applications.

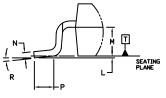

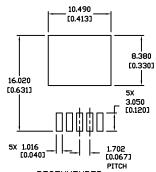

SCALE 1:1

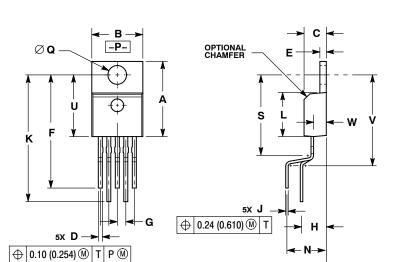

#### **TO-220 5 LEAD OFFSET CASE 314B-05 ISSUE L**

DATE 01/07/1994

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION D DOES NOT INCLUDE INTERCONNECT BAR (DAMBAR) PROTRUSION. DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 0.043 (1.092) MAXIMUM.

|     | INCHES    |       | MILLIN    | IETERS |

|-----|-----------|-------|-----------|--------|

| DIM | MIN       | MAX   | MIN       | MAX    |

| Α   | 0.572     | 0.613 | 14.529    | 15.570 |

| В   | 0.390     | 0.415 | 9.906     | 10.541 |

| С   | 0.170     | 0.180 | 4.318     | 4.572  |

| D   | 0.025     | 0.038 | 0.635     | 0.965  |

| E   | 0.048     | 0.055 | 1.219     | 1.397  |

| F   | 0.850     | 0.935 | 21.590    | 23.749 |

| G   | 0.067 BSC |       | 1.702 BSC |        |

| Н   | 0.166     | BSC   | 4.216 BSC |        |

| J   | 0.015     | 0.025 | 0.381     | 0.635  |

| K   | 0.900     | 1.100 | 22.860    | 27.940 |

| L   | 0.320     | 0.365 | 8.128     | 9.271  |

| N   | 0.320     | BSC   | 8.128     | BSC    |

| Q   | 0.140     | 0.153 | 3.556     | 3.886  |

| S   |           | 0.620 |           | 15.748 |

| U   | 0.468     | 0.505 | 11.888    | 12.827 |

| ٧   |           | 0.735 |           | 18.669 |

| w   | 0.090     | 0 110 | 2 286     | 2 794  |

STYLE 1 THRU 4: CANCELLED

STYLE 5: PIN 1. GATE

-T- SEATING PLANE

- 2. MIRROR 3. DRAIN

- 4. KELVIN 5. SOURCE

| DOCUMENT NUMBER: | 98ASB42218B          | Electronic versions are uncontrolled except when accessed directly from the Document Report Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | TO-220 5 LEAD OFFSET |                                                                                                                                                                             | PAGE 1 OF 1 |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

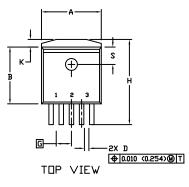

## **MECHANICAL CASE OUTLINE**

#### D<sup>2</sup>PAK 5-LEAD CASE 936A-02 **ISSUE E**

**DATE 28 JUL 2021**

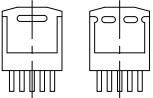

DUAL GUAGE

BOTTOM VIEW

SINGLE GUAGE

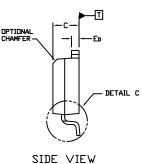

DETAIL C TIP LEADFORM ROTATED 90° CW

BOTTOM VIEW OPTIONAL CONSTRUCTIONS

#### RECOMMENDED MOUNTING FOOTPRINT \*

For additional information on our Pb-Free strategy and soldering details, please download the IN Seniconductor Soldering and Mounting Techniques Reference Manual, SILDERRM/D.

#### NOTES

- 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

- 2. CONTROLLING DIMENSION: INCHES

- TAB CONTOUR OPTIONAL WITHIN DIMENSIONS

- DIMENSIONS U AND V ESTABLISH A MINIMUM MOUNTING SURFACE FOR TERMINAL 4.

- DIMENSIONS A AND B DO NOT INCLUDE MOLD FLASH OR GATE PROTRUSIONS. MOLD FLASH AND GATE PROTRUSIONS NOT TO EXCEED 0.025 (0.635) MAXIMUM.

|          | INCHES    |       | MILLIN    | ETERS  |

|----------|-----------|-------|-----------|--------|

| DIM      | MIN.      | MAX.  | MIN.      | MAX.   |

| Α        | 0.396     | 0.403 | 9.804     | 10.236 |

| В        | 0.356     | 0.368 | 9.042     | 9.347  |

| C        | 0.170     | 0.180 | 4.318     | 4.572  |

| D        | 0.026     | 0.036 | 0.660     | 0.914  |

| ED       | 0.045     | 0.055 | 1.143     | 1.397  |

| Es       | 0.018     | 0.026 | 0.457     | 0.660  |

| G        | 0.067     | BSC   | 1.702 BSC |        |

| H        | 0.539     | 0.579 | 13.691    | 14.707 |

| K        | 0.050     | REF   | 1.270     | REF    |

| ٦        | 0.000     | 0.010 | 0.000     | 0.254  |

| М        | 0.088     | 0.102 | 2.235     | 2.591  |

| N        | 0.018     | 0.026 | 0.457     | 0.660  |

| Р        | 0.058     | 0.078 | 1.473     | 1.981  |

| R        | 0*        | 8•    | 0*        | 8*     |

| S        | 0.116 REF |       | 2.946     | REF    |

| U        | 0.200 MIN |       | 5.080     | MIN    |

| <b>V</b> | 0.250 MIN |       | 6.350     | MIN    |

### **GENERIC MARKING DIAGRAM\***

= Device Code XXXXXX = Assembly Location Α WL = Wafer Lot

= Year WW = Work Week G = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "=", may or may not be present. Some products may not follow the Generic Marking.

|                                                                                                                                                                                                             | DESCRIPTION:     | PTION: D2PAK 5-LEAD |  | PAGE 1 OF 1 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------|--|-------------|

| CUMENT NUMBER: 98ASH01006A Electronic versions are uncontrolled except when accessed directly from the Document Repository. Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. | DOCUMENT NUMBER: | JMBER: 98ASH01006A  |  |             |

ON Semiconductor and un are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales