# RENESAS

# Description

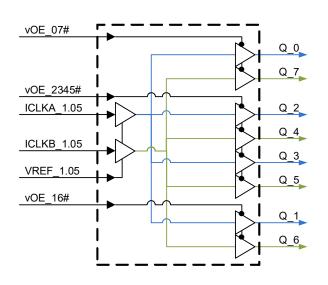

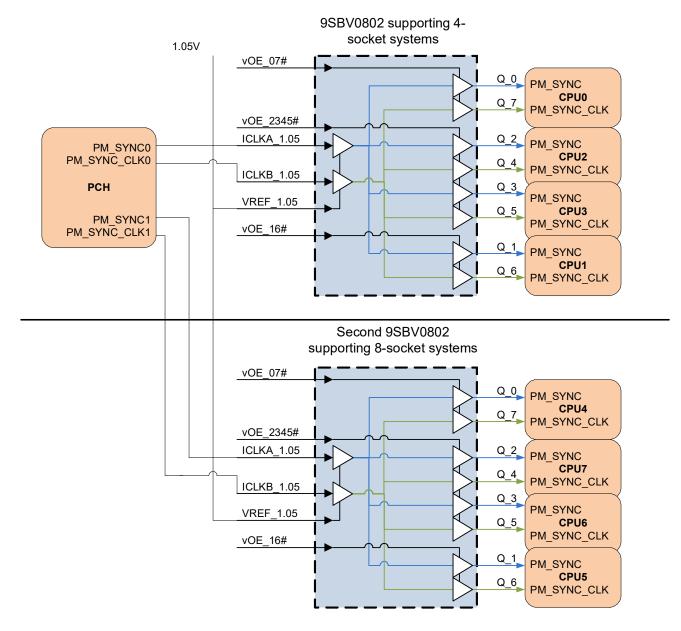

The 9SBV0802 provides two banks of four 1.05V LVCMOS outputs. Each bank has its own input. There are three OE pins. Two OE pins control two outputs each and one OE pin controls four outputs. One 9SBV0802 allows one PCH to easily support four CPUs with point to point routing of the PM signals. Two 9SBV0802 devices allow one PCH to easily support up to eight CPUs with point-to-point routing of the PM signals.

# **Typical Application**

Fanout buffer for PM-SYNC and PM\_SYNC CLK in Intel Servers

# **Output Features**

• Eight 1-48MHz 1.05V LVCMOS outputs

# **Key Specifications**

- Additive cycle-to-cycle jitter < 8ps

- Output-to-output skew within a bank < 50ps

- Output-to-output skew between banks < 100ps</li>

### **Block Diagram**

### Features

- 1.8V power supply, 15mW typical power consumption; eliminate thermal concerns

- OE pins; support 1, 2, 3 or 4 socket systems

- 1.05V LVCMOS inputs with VREF pin; input thresholds matched to chipset power supply

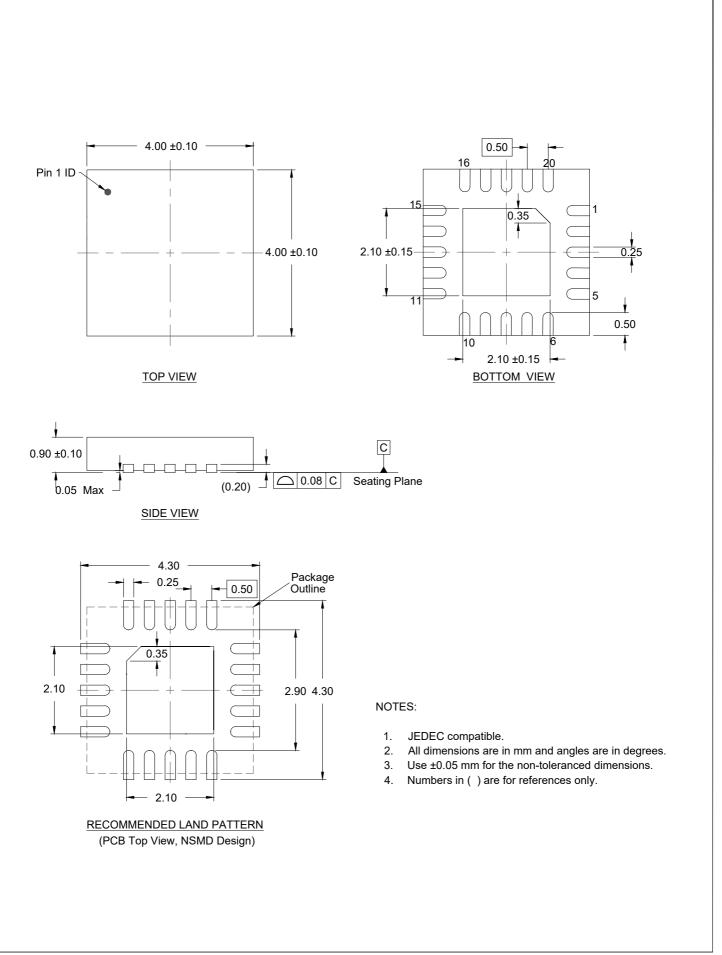

- Space saving 4 × 4 mm 20-VFQFPN; minimal board space

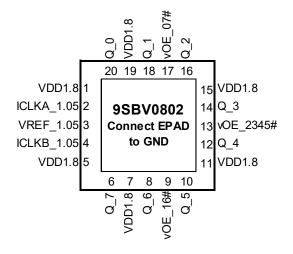

# **Pin Configuration**

### 4 × 4 mm 20-VFQFPN, 0.5mm pitch

^ prefix indicates internal 120kOhm pull-up resistor v prefix indicates internal 120kOhm pull-down resistor

### **Output Control Table**

| ICLKA_1.05<br>ICLKB_1.05 | OE_07 | OE_16 | OE_2345 | Q_7 | Q_6 | Q_5 | Q_4 | Q_3 | Q_2 | Q_1 | Q_0 |

|--------------------------|-------|-------|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Х                        | Х     | Х     | Х       | Х   | Х   | Х   | Х   | Х   | Х   | Х   | Х   |

| Running                  | 1     | 1     | 1       | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Running                  | 1     | 1     | 0       | 0   | 0   | Run | Run | Run | Run | 0   | 0   |

| Running                  | 1     | 0     | 1       | 0   | Run | 0   | 0   | 0   | 0   | Run | 0   |

| Running                  | 1     | 0     | 0       | 0   | Run | Run | Run | Run | Run | Run | 0   |

| Running                  | 0     | 1     | 1       | Run | 0   | 0   | 0   | 0   | 0   | 0   | Run |

| Running                  | 0     | 1     | 0       | Run | 0   | Run | Run | Run | Run | 0   | Run |

| Running                  | 0     | 0     | 1       | Run | Run | 0   | 0   | 0   | 0   | Run | Run |

| Running                  | 0     | 0     | 0       | Run |

### **Power Connections**

| Description     | Pin Number |     |  |  |

|-----------------|------------|-----|--|--|

| Description     | VDD        | GND |  |  |

| Input Circuits  | 1,5        | 21  |  |  |

| 1.05V reference | 3          | 21  |  |  |

| Quitauta        | 7,11,      | 21  |  |  |

| Outputs         | 15,19      | 21  |  |  |

# **Pin Descriptions**

| Pin# | Pin Name   | Туре | Pin Description                                                         |  |  |  |

|------|------------|------|-------------------------------------------------------------------------|--|--|--|

| 1    | VDD1.8     | PWR  | Power supply, nominally 1.8V.                                           |  |  |  |

| 2    | ICLKA 1.05 | IN   | 1.05V LVCMOS single-ended input clock. Voltage reference is set         |  |  |  |

|      |            |      | by the VREF_1.05 pin.                                                   |  |  |  |

| 3    |            |      | Voltage reference for 1.05V single-ended inputs. Connect the VDDIO      |  |  |  |

| Ľ    |            |      | 1.05V power rail from chipset to this pin.                              |  |  |  |

| 4    |            |      | 1.05V LVCMOS single-ended input clock. Voltage reference is set         |  |  |  |

|      | —          |      | by the VREF_1.05 pin.                                                   |  |  |  |

| 5    | VDD1.8     | PWR  | Power supply, nominally 1.8V.                                           |  |  |  |

| 6    | Q_7        | OUT  | LVCMOS single-ended output                                              |  |  |  |

| 7    | VDD1.8     | PWR  | Power supply, nominally 1.8V.                                           |  |  |  |

| 8    | Q_6        | OUT  | LVCMOS single-ended output                                              |  |  |  |

|      |            |      | Active low input for enabling outputs 1 and 6. This pin has an internal |  |  |  |

| 9    | vOE_16#    | IN   | pull down.                                                              |  |  |  |

|      |            |      | 0 = enable outputs, 1 = disable outputs                                 |  |  |  |

| 10   | Q_5        | OUT  | LVCMOS single-ended output                                              |  |  |  |

| 11   | VDD1.8     | PWR  | Power supply, nominally 1.8V.                                           |  |  |  |

| 12   | Q_4        | OUT  | LVCMOS single-ended output                                              |  |  |  |

|      |            |      | Active low input for enabling outputs 2 through 5. This pin has an      |  |  |  |

| 13   | vOE_2345#  | IN   | internal pull down.                                                     |  |  |  |

|      |            |      | 0 = enable outputs, 1 = disable outputs                                 |  |  |  |

| 14   | Q_3        | OUT  | LVCMOS single-ended output                                              |  |  |  |

| 15   | VDD1.8     | PWR  | Power supply, nominally 1.8V.                                           |  |  |  |

| 16   | Q_2        | OUT  | LVCMOS single-ended output                                              |  |  |  |

|      |            |      | Active low input for enabling outputs 0 and 7. This pin has an internal |  |  |  |

| 17   | vOE_07#    | IN   | pull down.                                                              |  |  |  |

|      |            |      | 0 = enable outputs, 1 = disable outputs                                 |  |  |  |

| 18   | Q_1        | OUT  | LVCMOS single-ended output                                              |  |  |  |

| 19   | VDD1.8     | PWR  | Power supply, nominally 1.8V.                                           |  |  |  |

| 20   | Q_0        | OUT  | LVCMOS single-ended output                                              |  |  |  |

| 21   | EPAD       | GND  | Connect to Ground.                                                      |  |  |  |

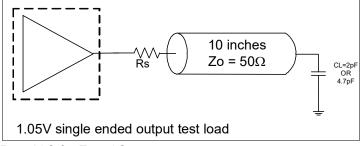

## **Test Loads**

Rs =  $33\Omega$  for Zo= $50\Omega$

## **Applications Diagram**

### **Electrical Characteristics–Absolute Maximum Ratings**

| PARAMETER                 | SYMBOL          | CONDITIONS                | MIN  | TYP | MAX                  | UNITS | NOTES |

|---------------------------|-----------------|---------------------------|------|-----|----------------------|-------|-------|

| Supply Voltage            | VDDx            |                           | -0.5 |     | 2.5                  | V     | 1,2   |

| Input Voltage             | V <sub>IN</sub> |                           | -0.5 |     | V <sub>DD</sub> +0.5 | V     | 1,3   |

| Input High Voltage, SMBus | VIHSMB          | SMBus clock and data pins |      |     | 3.6                  | V     | 1     |

| Storage Temperature       | Ts              |                           | -65  |     | 150                  | °C    | 1     |

| Junction Temperature      | Tj              |                           |      |     | 125                  | С°    | 1     |

| Input ESD protection      | ESD prot        | Human Body Model          | 2000 |     |                      | V     | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Operation under these conditions is neither implied nor guaranteed.

<sup>3</sup> Not to exceed 2.5V.

# Electrical Characteristics–Input/Supply/Common Parameters–Normal Operating Conditions

TA = T<sub>AMB</sub>, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                                 | SYMBOL                | CONDITIONS                                                                                                                                                    | MIN           | TYP  | MAX                   | UNITS  | NOTES |

|-------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------|-----------------------|--------|-------|

| Supply Voltage                            | VDD1.8                | Supply voltage for core and analog                                                                                                                            | 1.7           | 1.8  | 1.9                   | V      |       |

| Reference Supply Voltage                  | VDDREF_1.05           | Reference for 1.05V inputs                                                                                                                                    | 0.8           | 1.05 | 1.1                   | V      |       |

| Ambient Operating<br>Temperature          | T <sub>AMB</sub>      | Industrial range                                                                                                                                              | -40           | 25   | 85                    | °C     |       |

| Input High Voltage                        | V <sub>IH</sub>       | Control Inputs                                                                                                                                                | $0.75 V_{DD}$ | 1.6  | V <sub>DD</sub> + 0.3 | V      |       |

| Input Low Voltage                         | VIL                   | Control Inputs                                                                                                                                                | -0.3          | 0.2  | 0.25 V <sub>DD</sub>  | V      |       |

|                                           | l <sub>in</sub>       | Single-ended inputs, $V_{IN}$ = GND, $V_{IN}$ = VDD                                                                                                           | -5            | 0.0  | 5                     | uA     |       |

| Input Current                             | l <sub>INP</sub>      | Single-ended inputs<br>V <sub>IN</sub> = 0 V; Inputs with internal pull-up<br>resistors<br>V <sub>IN</sub> = VDD; Inputs with internal pull-down<br>resistors | -200          | 0.0  | 200                   | uA     |       |

| Input Frequency                           | F <sub>in</sub>       |                                                                                                                                                               | 1             | 24   | 48                    | MHz    |       |

| Pin Inductance                            | L <sub>pin</sub>      |                                                                                                                                                               |               |      | 7                     | nH     | 1     |

|                                           | C <sub>IN</sub>       | Logic Inputs, except DIF_IN                                                                                                                                   | 1.5           |      | 5                     | pF     | 1     |

| Capacitance                               | C <sub>INDIF_IN</sub> | DIF_IN differential clock inputs                                                                                                                              | 1.5           |      | 2.7                   | pF     | 1     |

|                                           | C <sub>OUT</sub>      | Output pin capacitance                                                                                                                                        |               |      | 6                     | pF     | 1     |

| Clk Stabilization                         | T <sub>STAB</sub>     | From V <sub>DD</sub> Power-Up and after input clock<br>stabilization or de-assertion of PD# to 1st<br>clock                                                   |               |      | 1                     | ms     | 1,2   |

| Input SS Modulation<br>Frequency non-PCle | f <sub>modin</sub>    | Allowable Frequency for non-PCle<br>Applications<br>(Triangular Modulation)                                                                                   | 0             |      | 66                    | kHz    | 1     |

| OE Latency                                | t <sub>LATOE#</sub>   | Output start after OE assertion<br>Output stop after OE deassertion                                                                                           | 1             |      | 3                     | clocks | 1     |

| Tfall                                     | t <sub>F</sub>        | Fall time of single-ended control inputs                                                                                                                      |               |      | 5                     | ns     | 2     |

| Trise                                     | t <sub>R</sub>        | Rise time of single-ended control inputs                                                                                                                      |               |      | 5                     | ns     | 2     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>Control input must be monotonic from 20% to 80% of input swing.

## **Electrical Characteristics–Clock Input Parameters**

TA = T<sub>AMB</sub>, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER             | SYMBOL          | CONDITIONS                                            | MIN  | TYP | MAX                  | UNITS | NOTES |

|-----------------------|-----------------|-------------------------------------------------------|------|-----|----------------------|-------|-------|

| Input High Voltage    | V <sub>IH</sub> | ICLKx_1.05                                            | 800  | 1.0 | VREF_1.05<br>+ 200mV | mV    | 1     |

| Input Low Voltage     | V <sub>IL</sub> | ICLKx_1.05                                            | -200 | 0   | 200                  | mV    | 1     |

| Input Slew Rate       | dv/dt           | Single-ended measurement, between 40% and 60% of VREF | 0.5  | -   | 5                    | V/ns  | 1     |

| Input Leakage Current | l <sub>IN</sub> | $V_{IN} = V_{DD}$ , $V_{IN} = GND$                    | -5   | 0   | 5                    | uA    |       |

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

# Electrical Characteristics–Q\_x 1.05V Single-ended Outputs

TA =  $T_{AMB}$ , Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER       | SYMBOL            | CONDITIONS                                                                                               | MIN | TYP  | MAX  | UNITS | NOTES |

|-----------------|-------------------|----------------------------------------------------------------------------------------------------------|-----|------|------|-------|-------|

| Slew Rate dV/dt | dV/dt             | Scope averaging on, CL = 2pF                                                                             | 0.8 | 1.5  | 2.5  | V/ns  | 1, 2  |

| Siew Rate       | uv/ut             | Scope averaging on, CL = 4.7pF                                                                           | 0.5 | 1    | 1.5  | V/ns  | 1, 2  |

| Voltage High    | V <sub>HIGH</sub> | Statistical measurement on single-ended signal using<br>oscilloscope math function. (Scope averaging on) |     | 1000 | 1100 | mV    |       |

| Voltage Low     | V <sub>LOW</sub>  |                                                                                                          |     | 0    | 150  |       |       |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Measured from 20% to 80% of swing.

## **Electrical Characteristics–Current Consumption**

TA = T<sub>AMB</sub>, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER                | SYMBOL                   | CONDITIONS                                 | MIN | TYP  | MAX | UNITS | NOTES |

|--------------------------|--------------------------|--------------------------------------------|-----|------|-----|-------|-------|

| Operating Supply Current | I <sub>DDVref 1.05</sub> | VREF_1.05V pin                             |     | 0.07 | 0.5 | mA    |       |

|                          | I <sub>DD1.8</sub>       | VDD, All outputs active at 24MHz, CL = 2pF |     | 8.2  | 12  | mA    |       |

| Powerdown Current        | I <sub>DDAPD</sub>       | VREF_1.05V pin                             |     | 0.07 | 0.5 | mA    | 1     |

| r owerdown Current       | I <sub>DDPD</sub>        | VDD, All outputs disabled.                 |     | 3.3  | 5   | mA    | 1     |

<sup>1</sup> Input clock stopped.

## Electrical Characteristics–Output Duty Cycle, Jitter, and Skew Characteristics

TA = T<sub>AMB</sub>, Supply Voltages per normal operation conditions, See Test Loads for Loading Conditions

| PARAMETER              | SYMBOL                | CONDITIONS                                   | MIN  | TYP   | MAX  | UNITS | NOTES |

|------------------------|-----------------------|----------------------------------------------|------|-------|------|-------|-------|

| Duty Cycle Distortion  | t <sub>DCD</sub>      | At 24MHz                                     | -2   | -0.8% | 0    | %     | 1, 2  |

| Skew, Input to Output  | t <sub>I2O</sub>      | V <sub>T</sub> = 50%                         | 2000 | 2474  | 3000 | ps    | 1     |

| Skew, Output to Output | t <sub>o2oA</sub>     | Within banks Q[3:0] or Q[7:4], $V_T = 50\%$  |      | 10    | 50   | ps    | 1     |

| Skew, Matching         | t <sub>o2oB</sub>     | Between banks Q[3:0] and Q[7:4], $V_T$ = 50% |      | 47    | 100  | ps    | 1     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | Additive Jitter, $V_T = 50\%$                |      | 3.5   | 8    | ps    | 1     |

<sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> Duty cycle distortion is the difference in duty cycle between the output and the input clock.

### **Marking Diagram**

● LOT 802AIL YYWW

- Line 1: "LOT" denotes the lot number.

- Line 2: truncated part number.

- Line 3: "YYWW" is the last two digits of the year and week that the part was assembled.

# **Thermal Characteristics**

| PARAMETER          | SYMBOL           | CONDITIONS                      | PKG   | TYP<br>VALUE | UNITS | NOTES |

|--------------------|------------------|---------------------------------|-------|--------------|-------|-------|

|                    | θ <sub>JC</sub>  | Junction to Case                |       | 42           | °C/W  | 1     |

|                    | $\theta_{Jb}$    | Junction to Base                |       | 2.4          | °C/W  | 1     |

| Thermal Resistance | θ <sub>JA0</sub> | Junction to Air, still air      |       | 39           | °C/W  | 1     |

| mermai Resistance  | $\theta_{JA1}$   | Junction to Air, 1 m/s air flow | NLG20 | 33           | °C/W  | 1     |

|                    | $\theta_{JA3}$   | Junction to Air, 3 m/s air flow |       | 28           | °C/W  | 1     |

|                    | $\theta_{JA5}$   | Junction to Air, 5 m/s air flow |       | 27           | °C/W  | 1     |

<sup>1</sup>ePad soldered to board

# Package Outline Drawings

The package outline drawings are appended at the end of this document and are accessible from the link below. The package information is the most current data available.

www.renesas.com/us/en/document/psc/package-outline-drawing-package-code-nlg20p1-20-vfqfpn-40-x-40-x-09-mm-body -05-mm-pitch

### **Ordering Information**

| Part / Order Number | Shipping Packaging | Package       | Temperature   |

|---------------------|--------------------|---------------|---------------|

| 9SBV0802AKILF       | Tubes              | 20-pin VFQFPN | -40° to +85°C |

| 9SBV0802AKILFT      | Tape and Reel      | 20-pin VFQFPN | -40° to +85°C |

"LF" to the suffix denotes Pb-Free configuration, RoHS compliant.

"A" is the device revision designator (will not correlate with the datasheet revision).

# **Revision History**

| Revision Date      | Description                                                                               |

|--------------------|-------------------------------------------------------------------------------------------|

| January 31, 2023   | Updated POD link.                                                                         |

|                    | 1. Removed input duty cycle specification, it is not needed.                              |

| April 21, 2020     | 2. Removed mention of bypass mode from footnote 2 of Output Duty Cycle, Jitter and Skew   |

|                    | Characteristics table.                                                                    |

| October 3, 2019    | 1. Updated measurement conditions of input clock slew rate to specify 40% to 60% of VREF. |

| October 5, 2019    | 2. Removed erroneous references to footnote 2 and duplicate footnote 1.                   |

| December 15, 2016  | Updated POD drawings with latest showing 2.1 mm SQ. EPAD (PSC-4170-01).                   |

|                    | 1. Update front page text.                                                                |

|                    | 2. Add Applications Diagram.                                                              |

| December 15, 2015  | 3. Update Electrical tables with characterization data.                                   |

| December 15, 2015  | 4. Added "Output Duty Cycle, Jitter, and Skew Characteristics" Table                      |

|                    | 5. Correct pin description for pin 9.                                                     |

|                    | 6. Move to final.                                                                         |

|                    | 1. Corrected polarity of OE inputs to be active low instead of active high.               |

|                    | 2. Added 2pF test loads in addition to 4.7pF.                                             |

| September 22, 2015 | 3. Updated electrical tables with preliminary data.                                       |

|                    | 4. Updated block diagram with proper OE polarity.                                         |

|                    | 5. Moved from Advance to Preliminary.                                                     |

### Package Outline Drawing

Package Code:NLG20P1 20-VFQFPN 4.0 x 4.0 x 0.9 mm Body, 0.5mm Pitch PSC-4170-01, Revision: 02, Date Created: Oct 4, 2022

### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>