# K8 Clock Chip for Serverworks GC-HT 2-Way Servers

Recommended Application: Serverworks GC-HT systems using AMD K8 processors

#### **Output Features:**

- 4 Pairs of AMD K8 clocks

- 1 Pair of SRC/PCI Express\* clock

- 2 14.318 MHz REF clocks

- 2 USB\_48MHz clocks

- 4 HyperTransport 66 MHz clocks

- 4 PCI 33 MHz clocks

#### Features:

- Spread Spectrum for EMI reduction

- Outputs may be disabled via SMBus

- M/N programming via SMBus

|         | • | <b>J</b> |          |

|---------|---|----------|----------|

| X1      | 1 | 48       | VDDREF   |

| X2      | 2 | 47       | FS0/REF0 |

| VDD48   | 3 | 46       | FS1/REF1 |

| 48MHz_0 | 4 | 45       | FS2      |

| 48MHz_1 | 5 | 44       | GND      |

| GND     | 6 | 43       | CPUCLK8T |

|         |   |          |          |

**Pin Configuration**

| 48MHz_1 | 5      |                   | 44  | GND       |

|---------|--------|-------------------|-----|-----------|

| GND     | 6      |                   | 43  | CPUCLK8T0 |

| SCLK    | 7      |                   | 42  | CPUCLK8C0 |

| SDATA   | 8      |                   | 41  | VDDCPU    |

| VDDHTT  | 9      | Ξ                 | 40  | GNDCPU    |

| HTTCLK0 | 10     | CS932S801         | 39  | CPUCLK8T1 |

| HTTCLK1 | 11     | 2S                | 38  | CPUCLK8C1 |

| HTTCLK2 | 12     | 63                | 37  | VDDCPU    |

| HTTCLK3 | 13     | SC                | 36  | GNDCPU    |

| GNDHTT  | 14     | $\mathbf{\Sigma}$ |     | CPUCLK8T2 |

| VDDPCI  | 15     |                   | 34  | CPUCLK8C2 |

| PCICLK0 | 16     |                   | 33  | VDDCPU    |

| PCICLK1 | 17     |                   | 32  | GNDCPU    |

| PCICLK2 | 18     |                   | 31  | CPUCLK8T3 |

| PCICLK3 | 19     |                   | 30  | CPUCLK8C3 |

| GNDPCI  | 20     |                   | 29  | SPREAD_EN |

| PD#     | 21     |                   | 28  | GNDSRC    |

| VDDA    | 22     |                   | 27  | VDDSRC    |

| GNDA    | 23     |                   | 26  | SRCCLKT0  |

| IREF    | 24     |                   | 25  | SRCCLKC0  |

|         | 48-SSC | P, TS             | SOP | -         |

### **Power Groups**

| Pin N    | Number   | Description                 |

|----------|----------|-----------------------------|

| VDD      | GND      | Description                 |

| 3        | 6        | 48MHz                       |

| 9 14     |          | 66MHz HTT Clocks            |

| 15       | 20       | 33 MHz PCI Clocks           |

| 22       | 23       | IREF, Analog Core           |

| 27       | 28       | SRC PLL, SRCCLK             |

| 33,37,41 | 32,36,40 | K8 CPU Clocks, CPU PLL      |

| 48       | 44       | REF Clocks, Xtal Oscillator |

### **Functionality**

| FS2 | FS2 FS1 |     | CPU    | HTT   | PCI   |

|-----|---------|-----|--------|-------|-------|

| F32 | гэт     | FS0 | MHz    | MHz   | MHz   |

| 0   | 0       | 0   | Hi-Z   | Hi-Z  | Hi-Z  |

| 0   | 0       | 1   | Х      | X/3   | X/6   |

| 0   | 1       | 0   | 180.00 | 60.00 | 30.00 |

| 0   | 1       | 1   | 220.00 | 73.12 | 36.56 |

| 1   | 0       | 0   | 100.00 | 66.66 | 33.33 |

| 1   | 0       | 1   | 133.33 | 66.66 | 33.33 |

| 1   | 1       | 0   | 166.67 | 66.66 | 33.33 |

| 1   | 1       | 1   | 200.00 | 66.66 | 33.33 |

### **Pin Descriptions**

| 2<br>3<br>4 | X1<br>X2  | IN  | Crystal input, Nominally 14.318MHz.                                                      |

|-------------|-----------|-----|------------------------------------------------------------------------------------------|

| 2<br>3<br>4 |           |     |                                                                                          |

| 3<br>4      |           | OUT | Crystal output, Nominally 14.318MHz                                                      |

| 4           | VDD48     | PWR | Power pin for the 48MHz output.3.3V                                                      |

|             | 48MHz_0   | OUT | 48MHz clock output.                                                                      |

| 5           | 48MHz_1   | OUT | 48MHz clock output.                                                                      |

| 6           | GND       | PWR | Ground pin.                                                                              |

| 7           | SCLK      | I/O | Clock pin of SMBus circuitry, 5V tolerant.                                               |

| 8           | SDATA     | I/O | Data pin for SMBus circuitry, 5V tolerant.                                               |

| 9           | VDDHTT    | PWR | Supply for HTT clocks, nominal 3.3V.                                                     |

| 10          | HTTCLK0   | OUT | 3.3V Hyper Transport output                                                              |

| 11          | HTTCLK1   | OUT | 3.3V Hyper Transport output                                                              |

|             | HTTCLK2   | OUT | 3.3V Hyper Transport output                                                              |

| 13          | HTTCLK3   | OUT | 3.3V Hyper Transport output                                                              |

| 14          | GNDHTT    | PWR | Ground pin for the HTT outputs                                                           |

| 15          | VDDPCI    | PWR | Power supply for PCI clocks, nominal 3.3V                                                |

| 16          | PCICLK0   | OUT | PCI clock output.                                                                        |

| 17          | PCICLK1   | OUT | PCI clock output.                                                                        |

| 18          | PCICLK2   | OUT | PCI clock output.                                                                        |

| 19          | PCICLK3   | OUT | PCI clock output.                                                                        |

| 20          | GNDPCI    | PWR | Ground pin for the PCI outputs                                                           |

| 21          | PD#       | IN  | Asynchronous active low input pin used to power down the device. The internal            |

| 21          | 1.0#      |     | clocks are disabled and the VCO and the crystal are stopped.                             |

| 22          | VDDA      | PWR | 3.3V power for the PLL core.                                                             |

| 23          | GNDA      | OUT | Ground pin for the PLL core.                                                             |

|             |           |     | This pin establishes the reference current for the differential current-mode output      |

| 24          | IREF      | OUT | pairs. This pin requires a fixed precision resistor tied to ground in order to establish |

|             |           |     | the appropriate current. 475 ohms is the standard value.                                 |

|             | SRCCLKC0  | OUT | Complement clock of differential SRC clock pair.                                         |

|             | SRCCLKT0  | OUT | True clock of differential SRC clock pair.                                               |

| 27          | VDDSRC    | PWR | Supply for SRC clocks, 3.3V nominal                                                      |

| 28          | GNDSRC    | PWR | Ground pin for the SRC outputs                                                           |

|             | SPREAD_EN | IN  | Asynchronous, active high input to enable spread spectrum functionality.                 |

| 30          | CPUCLK8C3 | OUT | Complementary clock of differential 3.3V push-pull K8 pair.                              |

| 31          | CPUCLK8T3 | OUT | True clock of differential 3.3V push-pull K8 pair.                                       |

| 32          | GNDCPU    | PWR | Ground pin for the CPU outputs                                                           |

| 33          | VDDCPU    | PWR | Supply for CPU clocks, 3.3V nominal                                                      |

| 34          | CPUCLK8C2 | OUT | Complementary clock of differential 3.3V push-pull K8 pair.                              |

| 35          | CPUCLK8T2 | OUT | True clock of differential 3.3V push-pull K8 pair.                                       |

|             | GNDCPU    | PWR | Ground pin for the CPU outputs                                                           |

| 37          | VDDCPU    | PWR | Supply for CPU clocks, 3.3V nominal                                                      |

| 38          | CPUCLK8C1 | OUT | Complementary clock of differential 3.3V push-pull K8 pair.                              |

| 39          | CPUCLK8T1 | OUT | True clock of differential 3.3V push-pull K8 pair.                                       |

| 40          | GNDCPU    | PWR | Ground pin for the CPU outputs                                                           |

| 41          |           | PWR | Supply for CPU clocks, 3.3V nominal                                                      |

| 42          |           | OUT | Complementary clock of differential 3.3V push-pull K8 pair.                              |

| 43          | CPUCLK8T0 | OUT | True clock of differential 3.3V push-pull K8 pair.                                       |

| 44          | GND       | PWR | Ground pin.                                                                              |

|             | FS2       |     | Frequency select pin.                                                                    |

|             | FS1/REF1  | I/O | Frequency select latch input pin / 14.318 MHz reference clock.                           |

| 47          | FS0/REF0  |     | Frequency select latch input pin / 14.318 MHz reference clock.                           |

| 48          | VDDREF    | PWR | Ref, XTAL power supply, nominal 3.3V                                                     |

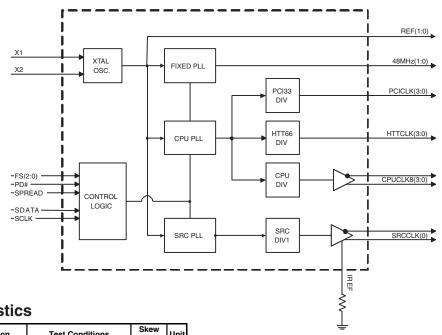

### **General Description**

The **ICS932S801** is a main clock synthesizer chip that, when paired with ICS9DB108, provides all clocks required by Serverworks GC-HT-based servers.

An SMBus interface allows full control of the device.

### **Block Diagram**

### **Skew Characteristics**

|                  | Parameter                         | Description      | Test Conditions                                                       | Skew<br>Window | Unit |

|------------------|-----------------------------------|------------------|-----------------------------------------------------------------------|----------------|------|

| T<br>i<br>m<br>e | Tsk_CPU_CPU                       | CPU to CPU Skew  | Measured at crossing points<br>of CPUCLKT rising edges                | 250            | ps   |

| I<br>n<br>d      | Tsk_CPU_PCI                       | CPU to PCI skew  | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>PCI clock  | 2000           | ps   |

| e<br>p<br>e<br>n | Tsk_PCI33-HT66 PCI33 to HT66 skew |                  | Measured between rising<br>edges at 1.5V                              | 500            | ps   |

| e<br>n<br>t      | Tsk_CPU_HT66 CPU to HT66 skew     |                  | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>HT66 clock | 2000           | ps   |

| т<br>i           | Tsk_CPU_CPU                       | CPU to CPU Skew  | Measured at crossing points<br>of CPUCLKT rising edges                | 200            | ps   |

| m<br>e<br>V      | Tsk_CPU_PCI                       | CPU to PCI skew  | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>PCI clock  | 200            | ps   |

| a<br>r<br>i<br>a | Lek PC133-H166 PC133 to H166 ekow |                  | Measured between rising edges at 1.5V                                 | 200            | ps   |

| n                | Tsk_CPU_HT66                      | CPU to HT66 skew | Meastured at crossing point<br>for CPUCLKT and 1.5V for<br>HT66 clock | 200            | ps   |

0959C-03/13/06

© 2019 Renesas Electronics Corporation

### Table1: SRC Frequency Selection Table

| SRCFS1<br>B5b3 | SRCFS0<br>B5b2 | SRCCLK<br>(MHz) |

|----------------|----------------|-----------------|

| 0              | 0              | 100.00          |

| 0              | 1              | 101.00          |

| 1              | 0              | 102.00          |

| 1              | 1              | 104.00          |

### Table 2: CPU Divider Ratios

|         |     |         |     | ]       | Divider (3:2 | 2)      |     |         |     |

|---------|-----|---------|-----|---------|--------------|---------|-----|---------|-----|

|         | Bit | 00      |     | 01      |              | 10      |     | 11      | MSB |

| (1:0)   | 00  | 0000    | 2   | 0100    | 4            | 1000    | 8   | 1100    | 16  |

|         | 01  | 0001    | 3   | 0101    | 6            | 1001    | 12  | 1101    | 24  |

| ide     | 10  | 0010    | 5   | 0110    | 10           | 1010    | 20  | 1110    | 40  |

| Divider | 11  | 0011    | 15  | 0111    | 30           | 1011    | 60  | 1111    | 120 |

|         | LSB | Address | Div | Address | Div          | Address | Div | Address | Div |

### **Table 3: HTT Divider Ratios**

|         |     |         |     | ]       | Divider (3:2 | 2)      |     |         |     |

|---------|-----|---------|-----|---------|--------------|---------|-----|---------|-----|

| (       | Bit | 00      |     | 01      |              | 10      |     | 11      | MSB |

| (1:0)   | 00  | 0000    | 4   | 0100    | 8            | 1000    | 16  | 1100    | 32  |

|         | 01  | 0001    | 3   | 0101    | 6            | 1001    | 12  | 1101    | 24  |

| ide     | 10  | 0010    | 5   | 0110    | 10           | 1010    | 20  | 1110    | 40  |

| Divider | 11  | 0011    | 15  | 0111    | 30           | 1011    | 60  | 1111    | 120 |

|         | LSB | Address | Div | Address | Div          | Address | Div | Address | Div |

#### **Table 4: SRC Divider Ratios**

|         |     |         |     | ]       | Divider (3:2 | 2)      |     |         |     |

|---------|-----|---------|-----|---------|--------------|---------|-----|---------|-----|

| (       | Bit | 00      |     | 01      |              | 10      |     | 11      | MSB |

| (1:0)   | 00  | 0000    | 2   | 0100    | 4            | 1000    | 8   | 1100    | 16  |

|         | 01  | 0001    | 3   | 0101    | 6            | 1001    | 12  | 1101    | 24  |

| ide     | 10  | 0010    | 5   | 0110    | 10           | 1010    | 20  | 1110    | 40  |

| Divider | 11  | 0011    | 7   | 0111    | 14           | 1011    | 28  | 1111    | 56  |

|         | LSB | Address | Div | Address | Div          | Address | Div | Address | Div |

### **Absolute Maximum Ratings**

| Supply Voltage                | 3.8V                                              |

|-------------------------------|---------------------------------------------------|

| Logic Inputs                  | GND -0.5 V to V <sub>DD</sub> +3.8 V              |

| Ambient Operating Temperature | 0°C to +70°C                                      |

| Storage Temperature           | -65°C to +150°C                                   |

| ESD Protection                | Input ESD protection usung human body model > 1KV |

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### Electrical Characteristics - Input/Supply/Common Output Parameters

$T_A$  = 0 - 70°C; Supply Voltage  $V_{\text{DD}}$  = 3.3 V +/-5%

| PARAMETER                                       | SYMBOL               | CONDITIONS                                                           | MIN                   | TYP      | MAX                   | UNITS | NOTES |

|-------------------------------------------------|----------------------|----------------------------------------------------------------------|-----------------------|----------|-----------------------|-------|-------|

| Input High Voltage                              | V <sub>IH</sub>      | 3.3 V +/-5%                                                          | 2                     |          | V <sub>DD</sub> + 0.3 | V     | 1     |

| Input Low Voltage                               | VIL                  | 3.3 V +/-5%                                                          | V <sub>SS</sub> - 0.3 |          | 0.8                   | V     | 1     |

| Input High Current                              | I <sub>IH</sub>      | $V_{IN} = V_{DD}$                                                    | -5                    |          | 5                     | uA    | 1     |

| Input Low Current                               | I <sub>IL1</sub>     | V <sub>IN</sub> = 0 V; Inputs with no pull-up resistors              | -5                    |          |                       | uA    | 1     |

|                                                 | $I_{IL2}$            | $V_{IN} = 0$ V; Inputs with pull-up resistors                        | -200                  |          |                       | uA    | 1     |

| Operating Current                               | I <sub>DD3.30P</sub> | all outputs driven                                                   |                       |          | 325                   | mA    |       |

| Powerdown Current                               | I <sub>DD3.3PD</sub> |                                                                      |                       |          | 100                   | mA    |       |

| Input Frequency <sup>3</sup>                    | Fi                   | $V_{DD} = 3.3 V$                                                     |                       | 14.31818 |                       | MHz   | 3     |

| Pin Inductance <sup>1</sup>                     | L <sub>pin</sub>     |                                                                      |                       |          | 7                     | nH    | 1     |

|                                                 | C <sub>IN</sub>      | Logic Inputs                                                         |                       |          | 5                     | pF    | 1     |

| Input Capacitance <sup>1</sup>                  | C <sub>OUT</sub>     | Output pin capacitance                                               |                       |          | 6                     | pF    | 1     |

|                                                 | CINX                 | X1 & X2 pins                                                         |                       |          | 5                     | рF    | 1     |

| Clk Stabilization <sup>1,2</sup>                | T <sub>STAB</sub>    | From V <sub>DD</sub> Power-Up or de-assertion of<br>PD# to 1st clock |                       |          | 3                     | ms    | 1,2   |

| Modulation Frequency                            |                      | Triangular Modulation                                                | 30                    |          | 33                    | kHz   | 1     |

| SMBus Voltage                                   | V <sub>DD</sub>      |                                                                      | 2.7                   |          | 5.5                   | V     | 1     |

| Low-level Output Voltage                        | V <sub>OL</sub>      | @ I <sub>PULLUP</sub>                                                |                       |          | 0.4                   | V     | 1     |

| Current sinking at $V_{OL} = 0.4 V$             | I <sub>PULLUP</sub>  |                                                                      | 4                     |          |                       | mA    | 1     |

| SCLK/SDATA<br>Clock/Data Rise Time <sup>3</sup> | T <sub>RI2C</sub>    | (Max VIL - 0.15) to (Min VIH + 0.15)                                 |                       |          | 1000                  | ns    | 1     |

| SCLK/SDATA<br>Clock/Data Fall Time <sup>3</sup> | T <sub>FI2C</sub>    | (Min VIH + 0.15) to (Max VIL - 0.15)                                 |                       |          | 300                   | ns    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup>See timing diagrams for timing requirements.

<sup>3</sup> Input frequency should be measured at the REFOUT pin and tuned to ideal 14.31818MHz to meet

ppm frequency accuracy on PLL outputs.

<sup>© 2019</sup> Renesas Electronics Corporation

### **Electrical Characteristics - K8 Push Pull Differential Pair**

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V} \pm -5\%$ ;  $C_L = AMD64 \text{ Processor Test Load}$

| PARAMETER                                   | SYMBOL                | CONDITIONS                                                                                                                                                                         | MIN   | TYP  | MAX  | UNITS | NOTES |

|---------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|-------|

| Rising Edge Rate                            | $\delta V / \delta t$ | Measured at the AMD64 processor's test load. 0 V +/- 400 mV (differential                                                                                                          | 2     |      | 10   | V/ns  | 1     |

| Falling Edge Rate                           | $\delta V / \delta t$ | measurement)                                                                                                                                                                       | 2     |      | 10   | V/ns  | 1     |

| Differential Voltage                        | $V_{DIFF}$            |                                                                                                                                                                                    | 0.4   | 1.25 | 2.3  | V     | 1     |

| Change in V <sub>DIFF_DC</sub><br>Magnitude | $\Delta V_{DIFF}$     | Measured at the AMD64 processor's                                                                                                                                                  | -150  |      | 150  | mV    | 1     |

| Common Mode Voltage                         | $V_{CM}$              | test load. (single-ended measurement)                                                                                                                                              | 1.05  | 1.25 | 1.45 | V     | 1     |

| Change in Common<br>Mode Voltage            | $\Delta V_{CM}$       |                                                                                                                                                                                    | -200  |      | 200  | mV    | 1     |

| Jitter, Cycle to cycle                      | t <sub>jcyc-cyc</sub> | Measurement from differential<br>wavefrom. Maximum difference of cycle<br>time between 2 adjacent cycles.                                                                          | 0     | 100  | 200  | ps    | 1     |

| Jitter, Accumulated                         | t <sub>ja</sub>       | Measured using the JIT2 software<br>package with a Tek 7404 scope.<br>TIE (Time Interval Error) measurement<br>technique:<br>Sample resolution = 50 ps,<br>Sample Duration = 10 µs | -1000 |      | 1000 |       | 1,2,3 |

| Duty Cycle                                  | $d_{t3}$              | Measurement from differential<br>wavefrom                                                                                                                                          | 45    |      | 53   | %     | 1     |

| Output Impedance                            | R <sub>ON</sub>       | Average value during switching<br>transition. Used for determining series<br>termination value.                                                                                    | 15    | 35   | 55   | Ω     | 1     |

| Group Skew                                  | t <sub>src-skew</sub> | Measurement from differential<br>wavefrom                                                                                                                                          |       |      | 250  | ps    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All accumulated jitter specifications are guaranteed assuming that REF is at 14.31818MHz

<sup>3</sup> Spread Spectrum is off

### Electrical Characteristics - SRC 0.7V Current Mode Differential Pair

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 V + -5\%$ ;  $C_L = 2pF$ ,  $R_S = 33.2\Omega$ ,  $R_P = 49.9\Omega$ ,  $I_{REF} = 475\Omega$

| PARAMETER                          | SYMBOL                    | CONDITIONS                                               | MIN    | TYP     | MAX     | UNITS | NOTES |

|------------------------------------|---------------------------|----------------------------------------------------------|--------|---------|---------|-------|-------|

| Current Source Output<br>Impedance | Zo                        | $V_{O} = V_{x}$                                          | 3000   |         |         | Ω     | 1     |

| Voltage High                       | VHigh                     | Statistical measurement on                               | 660    |         | 850     |       | 1,3   |

| Voltage Low                        | VLow                      | single ended signal using<br>oscilloscope math function. | -150   |         | 150     | mV    | 1,3   |

| Max Voltage                        | Vovs                      | Measurement on single ended                              |        |         | 1150    | mV    | 1     |

| Min Voltage                        | Vuds                      | signal using absolute value.                             | -300   |         |         | IIIV  | 1     |

| Crossing Voltage (abs)             | Vcross(abs)               |                                                          | 250    | 350     | 550     | mV    | 1     |

| Crossing Voltage (var)             | d-Vcross                  | Variation of crossing over all<br>edges                  |        | 12      | 140     | mV    | 1     |

| Long Accuracy                      | ppm                       | see Tperiod min-max values                               | -300   |         | 300     | ppm   | 1,2   |

| Average period                     | Tperiod                   | 100.00 MHz nominal                                       | 9.9970 | 10.0000 | 10.0030 | ns    | 2     |

|                                    |                           | 100.00 MHz spread                                        | 9.9970 |         | 10.0530 | ns    | 2     |

| Absolute min period                | Tabsmin                   | @100.00MHz nominal/spread                                | 9.8720 |         |         | ns    | 1,2   |

| Rise Time                          | t <sub>r</sub>            | $V_{OL} = 0.175V, V_{OH} = 0.525V$                       | 175    |         | 700     | ps    | 1     |

| Fall Time                          | t <sub>f</sub>            | $V_{OH} = 0.525 V V_{OL} = 0.175 V$                      | 175    |         | 700     | ps    | 1     |

| <b>Rise Time Variation</b>         | d-t <sub>r</sub>          |                                                          |        | 30      | 125     | ps    | 1     |

| Fall Time Variation                | d-t <sub>f</sub>          |                                                          |        | 30      | 125     | ps    | 1     |

| Duty Cycle                         | d <sub>t3</sub>           | Measurement from differential<br>wavefrom                | 45     |         | 55      | %     | 1     |

| Group Skew                         | t <sub>src-skew</sub>     | Measurement from differential<br>wavefrom                |        |         | N/A     | ps    |       |

| littor Phase                       | t                         | PCI Express Gen 1 phase jitter<br>CPU=200MHz, Spread off |        | 38      | 86      | ps    | 1, 4  |

| Jitter, Phase                      | t <sub>jphase-pcie1</sub> | PCI Express Gen 1 phase jitter<br>CPU=200MHz, Spread on  |        | 52      | 86      | ps    | 1, 4  |

| Jitter, Cycle to cycle             | t <sub>jcyc-cyc</sub>     | Measurement from differential<br>wavefrom                |        |         | 100     | ps    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed assuming that REF is at 14.31818MHz

${}^{3}I_{REF} = V_{DD}/(3xR_{R})$ . For  $R_{R} = 475\Omega$  (1%),  $I_{REF} = 2.32mA$ .  $I_{OH} = 6 \times I_{REF}$  and  $V_{OH} = 0.7V @ Z_{O} = 50\Omega$ .

<sup>4</sup>Per PCI SIG method for PCI Express Gen 1. Visit http://www.pcisig.com for details.

**Output High Current**

**Output Low Current**

Edge Rate

Edge Rate

Duty Cycle

Skew

Jitter, Cycle to cycle

#### SYMBOL TYP PARAMETER CONDITIONS MIN Long Accuracy see Tperiod min-max values -300 ppm 29.9910 30.0090 33.33MHz output nominal PCI33 Clock period Tperiod 29.9910 33.33MHz output spread 30.1598 14.9955 15.0045 66.67MHz output nominal HTT66 Clock period Tperiod 14.9955 15.0799 66.67MHz output spread Output High Voltage V<sub>OH</sub> $I_{OH} = -1 \text{ mA}$ 2.4 Output Low Voltage $I_{OL} = 1 \text{ mA}$ VoL

UNITS

ppm

ns

ns

ns

ns

٧

٧

mA

mΑ

mA

mΑ

V/ns

V/ns

%

ps

ps

Notes

1,2

2

2

2

2

1

1

1

1

1

1

1

1

1

1

1

MAX

300

0.55

-33

38

4

4

55

200

250

-33

30

1

1

45

#### Electrical Characteristics - PCICLK 33 MHz, HTTCLK 66 MHz Clocks

$T_A = 0 - 70^{\circ}C$ ; VDD=3.3V +/-5%;  $C_L = 20 \text{ pF}$  (unless otherwise specified)

Guaranteed by design and characterization, not 100% tested in production.

I<sub>OH</sub>

I<sub>OL</sub>

$\delta V/\delta t$

δV/δt

d<sub>t1</sub>

t<sub>sk1</sub>

t<sub>jcyc-cyc</sub>

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

V <sub>OH</sub> @MIN = 1.0 V

V<sub>OH</sub>@ MAX = 3.135 V

V<sub>OL</sub> @ MIN = 1.95 V

V<sub>OL</sub> @ MAX = 0.4 V

Rising edge rate

Falling edge rate

$V_{T} = 1.5 V$

$V_{T} = 1.5 V$

$V_{T} = 1.5 V$

### **Electrical Characteristics - 48MHz**

| $T_{A} = 0 - 70^{\circ}C$ : $V_{DD} =$ | 3.3 V +/-5%; C1 = | = 20 pF (unless | otherwise specified) |

|----------------------------------------|-------------------|-----------------|----------------------|

|----------------------------------------|-------------------|-----------------|----------------------|

| PARAMETER              | SYMBOL                | CONDITIONS                      | MIN     | TYP | MAX     | UNITS | Notes |

|------------------------|-----------------------|---------------------------------|---------|-----|---------|-------|-------|

| Long Accuracy          | ppm                   | see Tperiod min-max values      | -100    |     | 100     | ppm   | 1,2   |

| Clock period           | T <sub>period</sub>   | 48.00MHz output nominal         | 20.8257 |     | 20.8340 | ns    | 2     |

| Output High Voltage    | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA         | 2.4     |     |         | V     | 1     |

| Output Low Voltage     | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA          |         |     | 0.55    | V     | 1     |

| Output High Current    | 1                     | V <sub>OH</sub> @ MIN = 1.0 V   | -33     |     |         | mA    | 1     |

| Output High Current    | I <sub>ОН</sub>       | V <sub>OH</sub> @ MAX = 3.135 V |         |     | -33     | mA    | 1     |

| Outrout Law Ourrant    | I <sub>OL</sub>       | V <sub>OL</sub> @MIN = 1.95 V   | 30      |     |         | mA    | 1     |

| Output Low Current     |                       | V <sub>OL</sub> @ MAX = 0.4 V   |         |     | 38      | mA    | 1     |

| Edge Rate              | $\delta V / \delta t$ | Rising edge rate                | 1       |     | 4       | V/ns  | 1     |

| Edge Rate              | $\delta V / \delta t$ | Falling edge rate               | 1       |     | 4       | V/ns  | 1     |

| Duty Cycle             | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V          | 45      |     | 55      | %     | 1     |

| Skew                   | t <sub>sk1</sub>      | V <sub>T</sub> = 1.5 V          |         |     | 50      | ps    | 1     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V          |         |     | 200     | ps    | 1     |

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

<sup>2</sup> All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

<sup>© 2019</sup> Renesas Electronics Corporation

### **Electrical Characteristics - REF-14.318MHz**

| A, DD                  | · · · , - L           |                                                                 | /       |     |         |       |       |

|------------------------|-----------------------|-----------------------------------------------------------------|---------|-----|---------|-------|-------|

| PARAMETER              | SYMBOL                | CONDITIONS                                                      | MIN     | TYP | MAX     | UNITS | Notes |

| Long Accuracy          | ppm                   | see Tperiod min-max values                                      | -300    |     | 300     | ppm   | 1     |

| Clock period           | T <sub>period</sub>   | 14.318MHz output nominal                                        | 69.8270 |     | 69.8550 | ns    | 2     |

| Output High Voltage    | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                                         | 2.4     |     |         | V     | 1     |

| Output Low Voltage     | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                                          |         |     | 0.4     | V     | 1     |

| Output High Current    | I <sub>OH</sub>       | V <sub>OH</sub> @MIN = 1.0 V,<br>V <sub>OH</sub> @MAX = 3.135 V | -29     |     | -23     | mA    | 1     |

| Output Low Current     | I <sub>OL</sub>       | V <sub>OL</sub> @MIN = 1.95 V,<br>V <sub>OL</sub> @MAX = 0.4 V  | 29      |     | 27      | mA    | 1     |

| Edge Rate              | $\delta V / \delta t$ | Rising edge rate                                                | 1       |     | 2       | V/ns  | 1     |

| Edge Rate              | $\delta V / \delta t$ | Falling edge rate                                               | 1       |     | 2       | V/ns  | 1     |

| Duty Cycle             | d <sub>t1</sub>       | V <sub>T</sub> = 1.5 V                                          | 45      |     | 55      | %     | 1     |

| Skew                   | t <sub>sk1</sub>      | V <sub>T</sub> = 1.5 V                                          |         |     | 50      | ps    | 1     |

| Jitter, Cycle to cycle | t <sub>jcyc-cyc</sub> | V <sub>T</sub> = 1.5 V                                          |         |     | 1000    | ps    | 1     |

$T_A = 0 - 70^{\circ}C$ ;  $V_{DD} = 3.3 \text{ V} \pm -5\%$ ;  $C_L = 27 \text{ pF}$  (unless otherwise specified)

<sup>1</sup>Guaranteed by design and characterization, not 100% tested in production.

$^2$  All Long Term Accuracy and Clock Period specifications are guaranteed with the assumption that REF is at 14.31818MHz

### General SMBus serial interface information

### How to Write:

- Controller (host) sends a start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will *acknowledge*

- Controller (host) sends the data byte count = X

- ICS clock will acknowledge

- Controller (host) starts sending *Byte N through Byte N + X -1* (see Note 2)

- ICS clock will *acknowledge* each byte *one at a time*

- Controller (host) sends a Stop bit

### How to Read:

- Controller (host) will send start bit.

- Controller (host) sends the write address D2 (H)

- ICS clock will acknowledge

- Controller (host) sends the begining byte location = N

- ICS clock will acknowledge

- Controller (host) will send a separate start bit.

- Controller (host) sends the read address D3 (H)

- ICS clock will acknowledge

- ICS clock will send the data byte count = X

- ICS clock sends **Byte N + X -1**

- ICS clock sends Byte 0 through byte X (if X<sub>(H)</sub> was written to byte 8).

- Controller (host) will need to acknowledge each byte

- Controllor (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

| In    | dex Block W                 | /rit     | e Operation          |

|-------|-----------------------------|----------|----------------------|

| Cor   | ntroller (Host)             |          | ICS (Slave/Receiver) |

| Т     | starT bit                   |          |                      |

| Slav  | e Address D2 <sub>(H)</sub> |          |                      |

| WR    | WRite                       |          |                      |

|       |                             |          | ACK                  |

| Beg   | inning Byte = N             |          |                      |

|       |                             |          | ACK                  |

| Data  | Byte Count = X              |          |                      |

|       |                             |          | ACK                  |

| Begir | nning Byte N                |          |                      |

|       |                             |          | ACK                  |

|       | 0                           | te       |                      |

|       | 0                           | X Byte   | 0                    |

|       | 0                           | $\times$ | 0                    |

|       |                             |          | 0                    |

| Byte  | e N + X - 1                 |          |                      |

|       |                             |          | ACK                  |

| Р     | stoP bit                    |          |                      |

| In   | dex Block Rea               | ad (                | Operation          |  |  |

|------|-----------------------------|---------------------|--------------------|--|--|

| Cor  | ntroller (Host)             | IC                  | S (Slave/Receiver) |  |  |

| Т    | starT bit                   |                     |                    |  |  |

| Slav | e Address D2 <sub>(H)</sub> |                     |                    |  |  |

| WR   | WRite                       |                     |                    |  |  |

|      |                             |                     | ACK                |  |  |

| Begi | nning Byte = N              |                     |                    |  |  |

|      | -                           |                     | ACK                |  |  |

| RT   | Repeat starT                |                     |                    |  |  |

| Slav | e Address D3 <sub>(H)</sub> |                     |                    |  |  |

| RD   | ReaD                        |                     |                    |  |  |

|      |                             |                     | ACK                |  |  |

|      |                             |                     |                    |  |  |

|      |                             | Data Byte Count = X |                    |  |  |

|      | ACK                         |                     |                    |  |  |

|      |                             |                     | Beginning Byte N   |  |  |

|      | ACK                         |                     |                    |  |  |

|      |                             | Ъ,                  | 0                  |  |  |

|      | 0                           | X Byte              | 0                  |  |  |

|      | 0                           | ×                   | 0                  |  |  |

|      | 0                           |                     |                    |  |  |

|      |                             |                     | Byte N + X - 1     |  |  |

| N    | Not acknowledge             |                     |                    |  |  |

| Р    | stoP bit                    |                     |                    |  |  |

| Byt   | ie 0 | Pin # | Name      | Control Function                                        | Туре | 0                 | 1        | PWD     |

|-------|------|-------|-----------|---------------------------------------------------------|------|-------------------|----------|---------|

| Bit 7 |      | -     | FS Source | Latched Input or SMBus<br>Frequency Select              | RW   | Latched<br>Inputs | SMBus    | 0       |

| Bit 6 |      | -     | CPU SS_EN | Spread Enable for CPU<br>and SRC PLLs. Setting          | RW   | OFF               | ON       | 0       |

| Bit 5 |      | -     | SRC SS_EN | SPREAD_EN to '1',<br>forces Spread ON for<br>both PLLs. | RW   | OFF               | ON       | 0       |

| Bit 4 |      | -     | Reserved  | Reserved                                                | RW   | Reserved          | Reserved | 0       |

| Bit 3 |      | -     | FS3       | Freq Select Bit 3                                       | RW   |                   |          | 0       |

| Bit 2 |      | -     | FS2       | Freq Select Bit 2                                       | RW   | See Functiona     | Latched  |         |

| Bit 1 |      | -     | FS1       | Freq Select Bit 1                                       | RW   | Page 1            |          | Latched |

| Bit 0 |      | -     | FS0       | Freq Select Bit 0                                       | RW   |                   |          | Latched |

### SMBus Table: Frequency Select and Spread Control Register

### SMBus Table: Output Control Register

| Byt   | te 1 | Pin # | Name    | Control Function | Туре | 0             | 1      | PWD |

|-------|------|-------|---------|------------------|------|---------------|--------|-----|

| Bit 7 |      |       | PCICLK3 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 6 |      |       | PCICLK2 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 5 |      |       | PCICLK1 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 4 |      |       | PCICLK0 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 3 |      |       | HTTCLK3 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 2 |      |       | HTTCLK2 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 1 |      |       | HTTCLK1 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 0 |      |       | HTTCLK0 | Output Enable    | RW   | Disable (Low) | Enable | 1   |

#### SMBus Table: Output Control Register

| Byt   | ie 2 | Pin # | Name       | Control Function | Туре | 0             | 1      | PWD |

|-------|------|-------|------------|------------------|------|---------------|--------|-----|

| Bit 7 |      |       | 48MHz_1    | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 6 |      |       | 48MHz_0    | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 5 |      |       | REF1       | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 4 |      |       | REF0       | Output Enable    | RW   | Disable (Low) | Enable | 1   |

| Bit 3 |      |       | CPUCLK8(3) | Output Enable    | RW   | Disable       | Enable | 1   |

| Bit 2 |      |       | CPUCLK8(2) | When Disabled    | RW   | Disable       | Enable | 1   |

| Bit 1 |      |       | CPUCLK8(1) | CPUCLKT = 0      | RW   | Disable       | Enable | 1   |

| Bit 0 |      |       | CPUCLK8(0) | CPUCLKC = 1      | RW   | Disable       | Enable | 1   |

#### SMBus Table: SRCCLK(0) Output Control Register

| Byt   | te 3 | Pin # | Name       | Control Function                | Туре | 0              | 1        | PWD |

|-------|------|-------|------------|---------------------------------|------|----------------|----------|-----|

| Bit 7 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 6 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 5 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 4 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 3 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 2 |      | -     | Reserved   | Reserved                        | RW   | Reserved       | Reserved | 0   |

| Bit 1 |      | -     | SRCCLK0 PD | SRCCLK Power Down<br>Drive Mode | RW   | Driven         | Hi-Z     | 0   |

| Bit 0 |      |       | SRCCLK0    | Output Enable                   | RW   | Disable (Hi-Z) | Enable   | 1   |

#### SMBus Table: 48MHz Drive Strength Control Register

| By    | te 4 | Pin # | Name       | Control Function       | Туре | 0        | 1        | PWD |

|-------|------|-------|------------|------------------------|------|----------|----------|-----|

| Bit 7 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 6 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 5 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 4 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 3 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 2 |      | -     | Reserved   | Reserved               | RW   | Reserved | Reserved | 0   |

| Bit 1 |      | 5     | 48MHz_1 DS | Drive Strength Control | RW   | 1X       | 2X       | 0   |

| Bit 0 |      | 4     | 48MHz_0 DS | Drive Strength Control | RW   | 1X       | 2X       | 0   |

### SMBus Table: SRC Frequency Select Register

| By    | te 5 | Pin # | Name     | Control Function | Туре | 0          | 1          | PWD |

|-------|------|-------|----------|------------------|------|------------|------------|-----|

| Bit 7 |      | -     | Reserved | Reserved         | RW   | Reserved   | Reserved   | 0   |

| Bit 6 |      |       | Reserved | Reserved         | RW   | Reserved   | Reserved   | 0   |

| Bit 5 |      | -     | Reserved | Reserved         | RW   | Reserved   | Reserved   | 0   |

| Bit 4 |      | -     | Reserved | Reserved         | RW   | Reserved   | Reserved   | 0   |

| Bit 3 |      | -     | SRCFS1   | SRC FS bit 1     | RW   | See Ta     | ble 1:     | 0   |

| Bit 2 |      | -     | SRCFS0   | SRC FS bit 0     | RW   | SRC Freque | ncy Select | 0   |

| Bit 1 |      | -     | Reserved | Reserved         | RW   | Reserved   | Reserved   | 0   |

| Bit 0 |      | -     | Reserved | Reserved         | RW   | Reserved   | Reserved   | 0   |

### SMBus Table: Device ID Register

| By    | te 6 | Pin # | Name    | Control Function | Туре | 0 | 1 | PWD |

|-------|------|-------|---------|------------------|------|---|---|-----|

| Bit 7 |      | -     | DevID 7 | Device ID MSB    | R    | - | - | 1   |

| Bit 6 |      | -     | DevID 6 | Device ID 6      | R    | - | - | 0   |

| Bit 5 |      | -     | DevID 5 | Device ID 5      | R    | - | - | 0   |

| Bit 4 |      | -     | DevID 4 | Device ID4       | R    | - | - | 0   |

| Bit 3 |      | -     | DevID 3 | Device ID3       | R    | - | - | 0   |

| Bit 2 |      | -     | DevID 2 | Device ID2       | R    | - | - | 0   |

| Bit 1 |      | -     | DevID 1 | Device ID1       | R    | - | - | 0   |

| Bit 0 |      | -     | DevID 0 | Device ID LSB    | R    | - | - | 1   |

### SMBus Table: Vendor ID Register

| By    | te 7 | Pin # | Name | Control Function | Туре | 0 | 1 | PWD |

|-------|------|-------|------|------------------|------|---|---|-----|

| Bit 7 |      | -     | RID3 |                  | R    | - | - | Х   |

| Bit 6 |      | -     | RID2 | Revision ID      | R    | - | - | Х   |

| Bit 5 |      | -     | RID1 | Revision ID      | R    | - | - | Х   |

| Bit 4 |      | -     | RID0 |                  | R    | - | - | Х   |

| Bit 3 |      | -     | VID3 |                  | R    | - | - | 0   |

| Bit 2 |      | -     | VID2 | VENDOR ID        | R    | - | - | 0   |

| Bit 1 |      | -     | VID1 | (0001 = ICS)     | R    | - | - | 0   |

| Bit 0 |      | -     | VID0 |                  | R    | - | - | 1   |

### SMBus Table: Byte Count Register

| Byt   | te 8 | Pin # | Name | Control Function       | Туре | 0               | 1              | PWD |

|-------|------|-------|------|------------------------|------|-----------------|----------------|-----|

| Bit 7 |      | -     | BC7  |                        | RW   |                 |                | 0   |

| Bit 6 |      | -     | BC6  |                        | RW   |                 |                | 0   |

| Bit 5 |      | -     | BC5  |                        | RW   | Writing to this | register will  | 0   |

| Bit 4 |      | -     | BC4  | Byte Count Programming | RW   | configure how   | many bytes     | 0   |

| Bit 3 |      | -     | BC3  | b(7:0)                 | RW   | will be read ba | ck, default is | 1   |

| Bit 2 |      | -     | BC2  |                        | RW   | 9 byt           | es.            | 0   |

| Bit 1 |      | -     | BC1  |                        | RW   | -               |                | 0   |

| Bit 0 |      | -     | BC0  |                        | RW   |                 |                | 1   |

### SMBus Table: Reserved Register

| By    | te 9 | Pin # | Name     | Control Function | Туре | 0        | 1        | PWD |

|-------|------|-------|----------|------------------|------|----------|----------|-----|

| Bit 7 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 6 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 5 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 4 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 3 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 2 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 1 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

| Bit 0 |      | -     | Reserved | Reserved         | RW   | Reserved | Reserved | 0   |

### SMBus Table: M/N Programming Enable

| Byt   | e 10 | Pin # | Name     | Control Function                          | Туре | 0       | 1      | PWD |

|-------|------|-------|----------|-------------------------------------------|------|---------|--------|-----|

| Bit 7 |      | -     | M/N_EN   | CPU and SRC PLL M/N<br>Programming Enable | RW   | Disable | Enable | 0   |

| Bit 6 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Bit 5 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Bit 4 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Bit 3 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Bit 2 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Bit 1 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Bit 0 |      | -     | Reserved | Reserved                                  | RW   | -       | -      | 0   |

| Byte  | e 11 | Pin # | Name   | Control Function      | Туре | 0                         | 1             | PWD |

|-------|------|-------|--------|-----------------------|------|---------------------------|---------------|-----|

| Bit 7 |      | -     | N Div8 | N Divider Prog bit 8  | RW   | The decimal representatio |               | Х   |

| Bit 6 |      | -     | N Div9 | N Divider Prog bit 9  | RW   | of M and N Di             | vier in Byte  | Х   |

| Bit 5 |      | -     | M Div5 |                       | RW   | 11 and 12 wil             | l configure   | Х   |

| Bit 4 |      | -     | M Div4 |                       | RW   | RW the CPU VCO frequency. |               | Х   |

| Bit 3 |      | -     | M Div3 |                       | RW   | Default at powe           | er up = latch | Х   |

| Bit 2 |      | -     | M Div2 | M Divider Programming | RW   | in or Byte 0 I            | Rom table.    | Х   |

| Bit 1 |      | -     | M Div1 | bit (5:0)             | RW   | V VCO Frequency = 14.3    |               | Х   |

| Bit 0 |      | -     | M Div0 |                       | RW   | x [NDiv(9<br>[MDiv(5:     | , <b>-</b>    | Х   |

### SMBus Table: CPU Frequency Control Register

#### SMBus Table: CPU Frequency Control Register

| Byte  | e 12 | Pin # | Name   | Control Function      | Туре | 0                           | 1            | PWD |

|-------|------|-------|--------|-----------------------|------|-----------------------------|--------------|-----|

| Bit 7 |      | -     | N Div7 |                       | RW   | The decimal re              | presentation | Х   |

| Bit 6 |      | -     | N Div6 |                       | RW   | of M and N Divier in Byte   |              | Х   |

| Bit 5 |      | -     | N Div5 |                       | RW   | 11 and 12 will configure    |              | Х   |

| Bit 4 |      | -     | N Div4 | N Divider Programming | RW   | the CPU VCO frequency.      |              | Х   |

| Bit 3 |      | -     | N Div3 | Byte12 bit(7:0) and   | RW   | Default at power up = latch |              | Х   |

| Bit 2 |      | -     | N Div2 | Byte11 bit(7:6)       | RW   | in or Byte 0 I              | Rom table.   | Х   |

| Bit 1 |      | -     | N Div1 |                       | RW   | VCO Frequency = 14.318      |              | Х   |

| Bit 0 |      | -     | N Div0 |                       | RW   | x [NDiv(9<br>[MDiv(5        | , <u>-</u>   | Х   |

### SMBus Table: CPU Spread Spectrum Control Register

| Byte  | e 13 | Pin # | Name | Control Function     | Туре | 0               | 1             | PWD |

|-------|------|-------|------|----------------------|------|-----------------|---------------|-----|

| Bit 7 |      | -     | SSP7 |                      | RW   |                 |               | Х   |

| Bit 6 |      | -     | SSP6 |                      | RW   |                 |               | Х   |

| Bit 5 |      | -     | SSP5 |                      | RW   | These Spread    | d Spectrum    | Х   |

| Bit 4 |      | -     | SSP4 | Spread Spectrum      | RW   | bits in Byte 13 | 3 and 14 will | Х   |

| Bit 3 |      | -     | SSP3 | Programming bit(7:0) | RW   | program th      | e spread      | Х   |

| Bit 2 |      | -     | SSP2 |                      | RW   | pecentage       | of CPU        | Х   |

| Bit 1 |      | -     | SSP1 |                      | RW   |                 |               | Х   |

| Bit 0 |      | -     | SSP0 |                      | RW   |                 |               | Х   |

### SMBus Table: CPU Spread Spectrum Control Register

| Byte  | e 14 | Pin # | Name     | Control Function                         | Туре | 0                                                                           | 1 | PWD   |  |   |

|-------|------|-------|----------|------------------------------------------|------|-----------------------------------------------------------------------------|---|-------|--|---|

| Bit 7 |      | -     | Reserved | Reserved                                 | R    | -                                                                           | - | 0     |  |   |

| Bit 6 |      | -     | SSP14    |                                          | RW   | These Spread Spectrum                                                       |   | · · · |  | Х |

| Bit 5 |      | -     | SSP13    |                                          | RW   |                                                                             |   | Х     |  |   |

| Bit 4 |      | -     | SSP12    | Carood Capatrum                          | RW   | <ul> <li>bits in Byte 13 and 14 will</li> <li>program the spread</li> </ul> | Х |       |  |   |

| Bit 3 |      | -     | SSP11    | Spread Spectrum<br>Programming bit(14:8) | RW   |                                                                             |   | Х     |  |   |

| Bit 2 | -    |       | SSP10    | Flogramming bit(14.0)                    | RW   |                                                                             | • | Х     |  |   |

| Bit 1 |      |       | SSP9     | 1 [                                      |      | pecentage of CPU                                                            |   | Х     |  |   |

| Bit 0 |      | -     | SSP8     |                                          | RW   |                                                                             |   | Х     |  |   |

| Byte  | e 15 | Pin # | Name   | Control Function      | Туре | 0                                                     | 1            | PWD |

|-------|------|-------|--------|-----------------------|------|-------------------------------------------------------|--------------|-----|

| Bit 7 |      | -     | N Div8 | N Divider Prog bit 8  | RW   | The decimal re                                        | presentation | Х   |

| Bit 6 |      | -     | N Div9 | N Divider Prog bit 9  | RW   | of M and N Divier in Byte                             |              | Х   |

| Bit 5 |      | -     | M Div5 |                       | RW   | 15 and 16 wi                                          | ll configure | Х   |

| Bit 4 |      | -     | M Div4 |                       | RW   | the SRC VCO frequency.<br>Default at power up = latch |              | Х   |

| Bit 3 |      | -     | M Div3 |                       | RW   |                                                       |              | Х   |

| Bit 2 |      | -     | M Div2 | M Divider Programming | RW   | in or Byte 0 I                                        | Rom table.   | Х   |

| Bit 1 |      | -     | M Div1 | bits                  | RW   | VCO Frequen                                           | cy = 14.318  | Х   |

| Bit 0 |      | -     | M Div0 |                       | RW   | x [NDiv(9:0)+8] /<br>[MDiv(5:0)+2]                    |              | Х   |

### SMBus Table: SRC Frequency Control Register

#### SMBus Table: SRC Frequency Control Register

| Byte  | e 16 | Pin # | Name   | Control Function      | Туре | 0                          | 1             | PWD |

|-------|------|-------|--------|-----------------------|------|----------------------------|---------------|-----|

| Bit 7 |      | -     | N Div7 |                       | RW   | The decimal representation |               | Х   |

| Bit 6 | -    |       | N Div6 |                       | RW   | of M and N Di              | vier in Byte  | Х   |

| Bit 5 |      | -     | N Div5 |                       | RW   | 15 and 16 will configure   |               | Х   |

| Bit 4 |      | -     | N Div4 |                       | RW   | the SRC VCO frequency.     |               | Х   |

| Bit 3 |      | -     | N Div3 | N Divider Programming | RW   | Default at pow             | er up = latch | Х   |

| Bit 2 |      | -     | N Div2 | b(7:0)                | RW   | in or Byte 0 I             | Rom table.    | Х   |

| Bit 1 |      | -     | N Div1 |                       | RW   | VCO Frequency = 14.318     |               | Х   |

| Bit 0 |      | -     | N Div0 |                       | RW   | x [NDiv(9<br>[MDiv(5       | , <b>-</b>    | х   |

### SMBus Table: SRC Spread Spectrum Control Register

| Byte  | e 17 | Pin # | Name | Control Function   | Туре | 0               | 1             | PWD |

|-------|------|-------|------|--------------------|------|-----------------|---------------|-----|

| Bit 7 |      | -     | SSP7 |                    | RW   |                 |               | Х   |

| Bit 6 |      | -     | SSP6 |                    | RW   |                 |               | Х   |

| Bit 5 |      | -     | SSP5 |                    | RW   | These Spread    | d Spectrum    | Х   |

| Bit 4 |      | -     | SSP4 | Spread Spectrum    | RW   | bits in Byte 17 | 7 and 18 will | Х   |

| Bit 3 |      | -     | SSP3 | Programming b(7:0) | RW   | program th      | e spread      | Х   |

| Bit 2 |      | -     | SSP2 |                    | RW   | pecentage       | of SRC        | Х   |

| Bit 1 |      | -     | SSP1 |                    | RW   |                 |               | Х   |

| Bit 0 |      | -     | SSP0 | I                  | RW   |                 |               | Х   |

### SMBus Table: SRC Spread Spectrum Control Register

| Byte  | e 18 | Pin # | Name     | Control Function                       | Туре | 0                                                    | 1 | PWD |

|-------|------|-------|----------|----------------------------------------|------|------------------------------------------------------|---|-----|

| Bit 7 |      | -     | Reserved | Reserved                               | R    | -                                                    | - | 0   |

| Bit 6 |      | -     | SSP14    |                                        | RW   | These Spread Spectrum<br>bits in Byte 17 and 18 will |   | Х   |

| Bit 5 |      | -     | SSP13    |                                        | RW   |                                                      |   | Х   |

| Bit 4 |      | -     | SSP12    | Enroad Enastrum                        | RW   |                                                      |   | Х   |

| Bit 3 |      | -     | SSP11    | Spread Spectrum<br>Programming b(14:8) | RW   |                                                      |   | Х   |

| Bit 2 |      | -     | SSP10    | Flogramming b(14.0)                    | RW   | program the spread                                   | Х |     |

| Bit 1 |      | -     | SSP9     |                                        | RW   | <ul> <li>pecentage of SRC</li> </ul>                 |   | Х   |

| Bit 0 |      | -     | SSP8     |                                        | RW   |                                                      | Х |     |

#### SMBus Table: Programmable Output Divider Register

| Byte  | e 19 | Pin # | Name    | Control Function          | Туре | 0            | 1         | PWD |

|-------|------|-------|---------|---------------------------|------|--------------|-----------|-----|

| Bit 7 |      | -     | CPUDiv3 |                           | RW   |              |           | Х   |

| Bit 6 | 6 -  |       | CPUDiv2 | CPU Divider Ratio         | RW   | See Table 2: |           | Х   |

| Bit 5 |      | -     | CPUDiv1 | Programming Bits          | RW   | CPU Divide   | er Ratios | Х   |

| Bit 4 |      | -     | CPUDiv0 |                           | RW   |              |           | Х   |

| Bit 3 |      | -     | HTTDiv3 | HTT Divider Ratio         | RW   |              |           | Х   |

| Bit 2 |      | -     | HTTDiv2 | Programming Bits (PCI     | RW   | See Ta       | ble 3:    | Х   |

| Bit 1 |      | -     | HTTDiv1 | divider is always 2x the  | RW   | HTT Divide   | er Ratios | Х   |

| Bit 0 |      | -     | HTTDiv0 | HTT divider or 1/2 freq.) | RW   |              |           | Х   |

### SMBus Table: Programmable Output Divider Register

| Byt   | e 20 | Pin # | Name     | Control Function   | Туре | 0            | 1         | PWD |

|-------|------|-------|----------|--------------------|------|--------------|-----------|-----|

| Bit 7 |      | -     | Reserved | Reserved           | R    | -            | -         | Х   |

| Bit 6 |      | -     | Reserved | Reserved           | R    | -            | -         | Х   |

| Bit 5 |      | -     | Reserved | Reserved           | R    | -            | -         | Х   |

| Bit 4 |      | -     | Reserved | Reserved           | R    | -            | -         | Х   |

| Bit 3 |      | -     | SRC_Div3 |                    | RW   |              |           | Х   |

| Bit 2 |      | -     | SRC_Div2 | SRC_ Divider Ratio | RW   | See Table 4: |           | Х   |

| Bit 1 |      | -     | SRC_Div1 | Programming Bits   | RW   | SRC Divide   | er Ratios | Х   |

| Bit 0 |      | -     | SRC_Div0 |                    | RW   |              |           | Х   |

### SMBusTable: Test Byte Register

| Byte 21 Test |                 | Test | Test Function |    | Test Result | PWD |

|--------------|-----------------|------|---------------|----|-------------|-----|

| Bit 7        |                 | `    | ICS ONLY TEST | RW | Reserved    | 0   |

| Bit 6        | 6 ICS ONLY TEST |      | ICS ONLY TEST | RW | Reserved    | 0   |

| Bit 5        | Bit 5           |      | ICS ONLY TEST |    | Reserved    | 0   |

| Bit 4        |                 |      | ICS ONLY TEST | RW | Reserved    | 0   |

| Bit 3        |                 |      | ICS ONLY TEST | RW | Reserved    | 0   |

| Bit 2        |                 |      | ICS ONLY TEST | RW | Reserved    | 0   |

| Bit 1        |                 |      | ICS ONLY TEST | RW | Reserved    | 0   |

| Bit 0        | t 0             |      | ICS ONLY TEST | RW | Reserved    | 0   |

### Shared Pin Operation -Input/Output Pins

The I/O pins designated by (input/output) on the **ICS932S801** serve as dual signal functions to the device. During initial power-up, they act as input pins. The logic level (voltage) that is present on these pins at this time is read and stored into a 5-bit internal data latch. At the end of Power-On reset, (see AC characteristics for timing values), the device changes the mode of operations for these pins to an output function. In this mode the pins produce the specified buffered clocks to external loads.

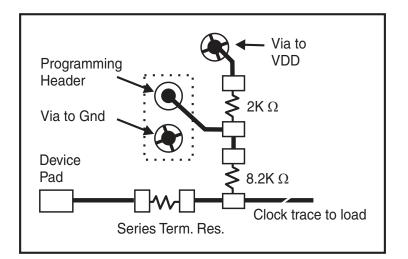

To program (load) the internal configuration register for these pins, a resistor is connected to either the VDD (logic 1) power supply or the GND (logic 0) voltage potential. A 10 Kilohm (10K) resistor is used to provide both the solid CMOS programming voltage needed during the power-up programming period and to provide an insignificant load on the output clock during the subsequent operating period. Figure 1 shows a means of implementing this function when a switch or 2 pin header is used. With no jumper is installed the pin will be pulled high. With the jumper in place the pin will be pulled low. If programmability is not necessary, than only a single resistor is necessary. The programming resistors should be located close to the series termination resistor to minimize the current loop area. It is more important to locate the series termination resistor close to the driver than the programming resistor.

Fig. 1

0959C-03/13/06

© 2019 Renesas Electronics Corporation

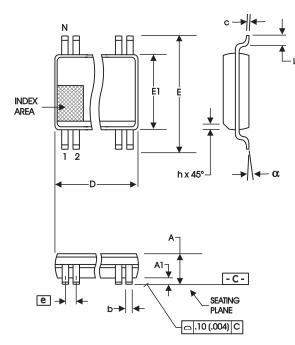

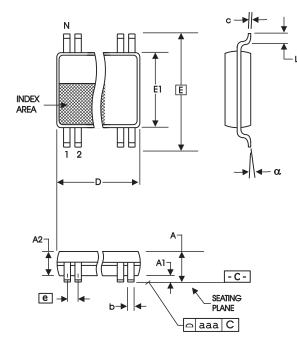

|        | 300 mil SSOP |           |                |           |  |  |  |  |

|--------|--------------|-----------|----------------|-----------|--|--|--|--|

|        | In Milli     | meters    | In Inches      |           |  |  |  |  |

| SYMBOL | COMMON D     | IMENSIONS | COMMON D       | IMENSIONS |  |  |  |  |

|        | MIN          | MAX       | MIN            | MAX       |  |  |  |  |

| Α      | 2.41         | 2.80      | .095           | .110      |  |  |  |  |

| A1     | 0.20         | 0.40      | .008           | .016      |  |  |  |  |

| b      | 0.20         | 0.34      | .008           | .0135     |  |  |  |  |

| С      | 0.13         | 0.25      | .005           | .010      |  |  |  |  |

| D      | SEE VAF      | RIATIONS  | SEE VARIATIONS |           |  |  |  |  |

| E      | 10.03        | 10.68     | .395           | .420      |  |  |  |  |

| E1     | 7.40         | 7.60      | .291           | .299      |  |  |  |  |

| е      | 0.635        | BASIC     | 0.025 BASIC    |           |  |  |  |  |

| h      | 0.38         | 0.64      | .015           | .025      |  |  |  |  |

| L      | 0.50         | 1.02      | .020           | .040      |  |  |  |  |

| N      | SEE VAF      | RIATIONS  | SEE VAF        | RIATIONS  |  |  |  |  |

| а      | 0°           | 8°        | 0°             | 8°        |  |  |  |  |

#### VARIATIONS

| N  | D n   | nm.   | D (inch) |      |  |

|----|-------|-------|----------|------|--|

| IN | MIN   | MAX   | MIN      | MAX  |  |

| 48 | 15.75 | 16.00 | .620     | .630 |  |

Reference Doc.: JEDEC Publication 95, MO-118

10-0034

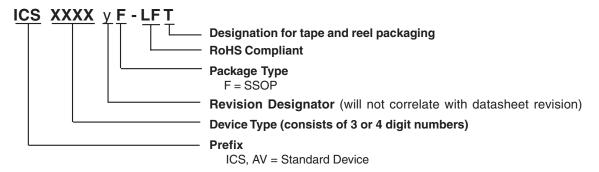

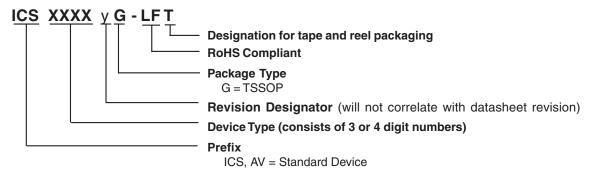

### **Ordering Information**

### ICS932S801<u>y</u>FLFT

Example:

| -      | (240 m         | il) (20  | mil)           |           |  |

|--------|----------------|----------|----------------|-----------|--|

|        | In Millir      | neters   | In Inches      |           |  |

| SYMBOL | COMMON DI      | MENSIONS | COMMON D       | IMENSIONS |  |

|        | MIN            | MAX      | MIN            | MAX       |  |

| А      |                | 1.20     |                | .047      |  |

| A1     | 0.05           | 0.15     | .002           | .006      |  |

| A2     | 0.80           | 1.05     | .032           | .041      |  |

| b      | 0.17           | 0.27     | .007           | .011      |  |

| С      | 0.09           | 0.20     | .0035          | .008      |  |

| D      | SEE VAR        | IATIONS  | SEE VARIATIONS |           |  |

| E      | 8.10 B         | ASIC     | 0.319 BASIC    |           |  |

| E1     | 6.00           | 6.20     | .236           | .244      |  |

| е      | 0.50 B         | ASIC     | 0.020 BASIC    |           |  |

| L      | 0.45           | 0.75     | .018           | .030      |  |

| N      | SEE VARIATIONS |          | SEE VARIATIONS |           |  |

| а      | 0°             | 8°       | 0°             | 8°        |  |

| aaa    |                | 0.10     |                | .004      |  |

#### VARIATIONS

| Ν  | Drr   | ım.   | D (inch) |      |  |

|----|-------|-------|----------|------|--|

|    | MIN   | MAX   | MIN      | MAX  |  |

| 48 | 12.40 | 12.60 | .488     | .496 |  |

Reference Doc.: JEDEC Publication 95, MO-153

10-0039

### **Ordering Information**

### ICS932S801<u>y</u>GLFT

Example:

### **Revision History**

| Rev. | Issue Date | Description                                                                         | Page # |

|------|------------|-------------------------------------------------------------------------------------|--------|

|      |            | 1. Updated Electrical Characteristics Tables:                                       |        |

|      |            | i) Changed SRC jitter from 125ps to 100ps;                                          |        |

|      |            | ii) Changed PCI/HTT Skew from 500ps to 200ps;                                       |        |

|      |            | iii) Added USB Skew, 50ps.                                                          |        |

|      |            | iv) Change REF Skew from 500ps to 50ps.                                             | 14-16  |

| В    | 5/18/2005  | 2. Updated LF Ordering Information from "Lead Free" to "RoHS Compliant".            | 18-19  |

|      |            | 1. Correct pin description of PD# (Pin 21). It does not contain a pull up resistor. |        |

| С    | 3/13/2006  | 2. Added PCIe Gen 1 phase noise numbers to SRC output characterisitics              | 2, 7   |

#### IMPORTANT NOTICE AND DISCLAIMER

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers skilled in the art designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only for development of an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising out of your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use o any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.0 Mar 2020)

#### **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners. **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit: <u>www.renesas.com/contact/</u>