# AOZ6763DI

3A 1.25MHz Synchronous EZBuck™ Regulator

#### **General Description**

The AOZ6763DI is a high efficiency, easy to use, 3A synchronous buck regulator at high switching frequency for small form factor solution. The AOZ6763DI works from 4.5V to 18V input voltage range, and provides up to 3A of continuous output current with an output voltage adjustable down to 0.6V.

The AOZ6763DI comes in a DFN 3mm x 3mm package and is rated over a -40°C to +85°C operating ambient temperature range.

#### **Features**

- 4.5V to 18V operating input voltage range

- Synchronous Buck: 145mΩ internal high-side switch and 80mΩ Internal low-side switch

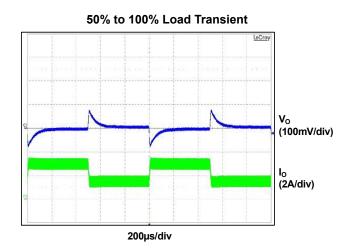

- Up to 95% efficiency

- 30ns controllable minimum on-time enabling this part can work at Vo=0.9V with 12V power rail

- Pulse Energy Mode for light load efficiency (Vin=12V, Vo=5V, 86%@10mA)

- Output voltage adjustable to 0.6V

- 3A continuous output current

- Fixed frequency 1.25MHz PWM operation

- External compensation for flexible LC design

- Internal Soft Start

- Cycle-by-cycle current limit

- Pre-bias start-up

- Short-circuit protection

- Thermal shutdown

#### **Applications**

- High performance wireless AP/router

- High reliable DC/DC converters

- High performance LCD TV

- High performance cable modems

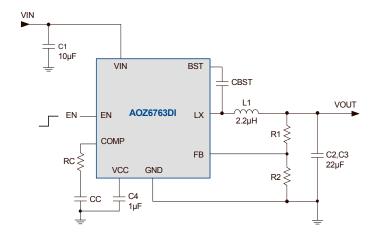

### Typical Application

Figure 1. 3A Synchronous Buck Regulator, Fs = 1.25 MHz

### **Ordering Information**

| Part Number | Ambient Temperature Range | Package             | Environmental |  |  |

|-------------|---------------------------|---------------------|---------------|--|--|

| AOZ6763DI   | -40°C to +85°C            | 8-Pin 3mm x 3mm DFN | RoHS          |  |  |

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant. Please visit Please visit www.aosmd.com/media/AOSGreenPolicy.pdf for additional information.

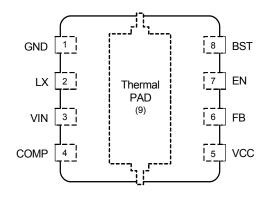

### **Pin Configuration**

8-Pin 3mm x 3mm DFN

Top Transparent View

### **Pin Description**

| Pin Number | Pin Name    | Pin Function                                                                                                                                                                   |

|------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | GND         | System ground.                                                                                                                                                                 |

| 2          | LX          | Switching output.                                                                                                                                                              |

| 3          | VIN         | Supply voltage input. When VIN rises above the UVLO threshold and EN is logic high, the device starts up.                                                                      |

| 4          | COMP        | External Loop Compensation Pin. Connect a RC network between COMP and GND to compensate the control loop.                                                                      |

| 5          | VCC         | The output of LDO. 1µF decoupling capacitor needs added.                                                                                                                       |

| 6          | FB          | Feedback input. The FB pin is used to set the output voltage via a resistor voltage divider between the output and GND.                                                        |

| 7 EN       |             | Enable input. Pull up EN to logic high will enable the device. Pull EN to logic low will disable the device. EN pin must be connected to VIN if no Enable control is required. |

| 8          | BST         | Bootstrap input. Connect a capacitor to LX. Typical value is 0.1µF.                                                                                                            |

| 9          | Thermal PAD | This thermal pad must be connected to GND for normal operation.                                                                                                                |

Rev. 1.0 October 2019 **www.aosmd.com** Page 2 of 15

### **Absolute Maximum Ratings**(1)

Exceeding the Absolute Maximum Ratings may damage the device.

| Parameter                                                | Rating                         |

|----------------------------------------------------------|--------------------------------|

| Supply Voltage (V <sub>IN</sub> ), EN (V <sub>EN</sub> ) | 20V                            |

| LX to GND                                                | -0.3V to V <sub>IN</sub> +0.3V |

| LX to GND (20ns)                                         | -5V to 22V                     |

| VCC, FB to GND                                           | -0.3V to 6V                    |

| VBST TO LX                                               | 6V                             |

| Junction Temperature (T <sub>J</sub> )                   | +150°C                         |

| Storage Temperature (T <sub>S</sub> )                    | -65°C to +150°C                |

| ESD Rating <sup>(2)</sup>                                | 2kV                            |

#### Notes:

- 1. Exceeding the Absolute Maximum ratings may damage the device.

- 2. Devices are inherently ESD sensitive, handling precautions are required. Human body model rating: 1.5k $\Omega$  in series with 100pF.

### Maximum Operating Ratings<sup>(3)</sup>

The device is not guaranteed to operate beyond the Maximum Operating ratings.

| Parameter                                                               | Rating                       |

|-------------------------------------------------------------------------|------------------------------|

| Supply Voltage (V <sub>IN</sub> )                                       | 4.5V to 18V                  |

| Output Voltage Range                                                    | 0.6V to 0.65*V <sub>IN</sub> |

| Ambient Temperature (T <sub>A</sub> )                                   | -40°C to +85°C               |

| Package Thermal Resistance<br>DFN 3x3 (θ <sub>JA</sub> ) <sup>(4)</sup> | 50°C/W                       |

#### Notes:

- The device is not guaranteed to operate beyond the Maximum Operating ratings.

- 4. The value of  $\theta_{JA}$  is measured with the device mounted on a 1-in<sup>2</sup> FR-4 four layer board with 2oz copper and Vias, in a still air environment with  $T_A$  = 25°C. The value in any given application depends on the user's specification board design.

#### **Electrical Characteristics**

$T_A = 25$ °C,  $V_{IN} = V_{EN} = 12$ V,  $V_{OUT} = 3.3$ V, unless otherwise specified. Specifications in bold indicate an ambient temperature range of -40°C to +85°C. These specifications are guaranteed by design.

| Symbol                                           | Parameter                             | Conditions                                              | Min.  | Тур.       | Max   | Units  |

|--------------------------------------------------|---------------------------------------|---------------------------------------------------------|-------|------------|-------|--------|

| V <sub>IN</sub>                                  | Supply Voltage                        |                                                         | 4.5   |            | 18    | V      |

| V <sub>UVLO</sub>                                | Input Under-Voltage Lockout Threshold | V <sub>IN</sub> rising<br>V <sub>IN</sub> falling       | 3.2   | 4.1<br>3.7 | 4.49  | V<br>V |

| I <sub>IN</sub>                                  | Supply Current (Quiescent)            | I <sub>OUT</sub> = 0V, VFB = 1.2V, V <sub>EN</sub> > 2V |       | 260        |       | μΑ     |

| I <sub>OFF</sub>                                 | Shutdown Supply Current               | V <sub>EN</sub> = 0V                                    |       | 0.1        | 1     | μΑ     |

| V <sub>FB</sub>                                  | Feedback Voltage                      | T <sub>A</sub> = 25°C                                   | 0.591 | 0.6        | 0.609 | V      |

| R <sub>O</sub>                                   | Load Regulation                       | PWM mode 500mA < ILoad < 3A                             |       | 0.5        |       | %      |

| S <sub>V</sub>                                   | Line Regulation                       | 4.5V < V <sub>IN</sub> < 18V                            |       | 1          |       | %      |

| I <sub>FB</sub>                                  | Feedback Voltage Input Current        |                                                         |       |            | 200   | nA     |

| $V_{EN}$                                         | EN Input Threshold                    | Off threshold<br>On threshold                           | 2     |            | 0.6   | V<br>V |

| V <sub>HYS</sub>                                 | EN Input Hysteresis                   |                                                         |       | 300        |       | mV     |

| I <sub>EN</sub>                                  | EN Input Current                      | V <sub>EN</sub> = 5V                                    |       | 2.5        | 4     | μΑ     |

| t <sub>SS</sub>                                  | SS Time                               |                                                         |       | 2.6        |       | ms     |

| Modulator                                        |                                       |                                                         |       |            |       |        |

| f <sub>O</sub>                                   | Frequency                             |                                                         | 1100  | 1250       | 1400  | kHz    |

| D <sub>MAX</sub>                                 | Maximum Duty Cycle                    |                                                         | 65    | 70         |       | %      |

| T <sub>MIN</sub> Controllable Minimum Duty Cycle |                                       |                                                         |       | 30         |       | ns     |

| Protection                                       |                                       |                                                         |       |            |       |        |

| I <sub>LIM</sub>                                 | Current Limit                         |                                                         | 3.5   | 4.5        |       | Α      |

| T <sub>OTP</sub>                                 | Over Temperature Shutdown Limit       | $T_J$ rising $T_J$ falling                              |       | 150<br>100 |       | °C     |

| Output Sta                                       | ge                                    |                                                         | •     | •          | •     |        |

| R <sub>HS</sub>                                  | High-Side Switch On-Resistance        | BST - LX = 5V                                           |       | 145        |       | mΩ     |

| R <sub>LS</sub>                                  | Low-Side Switch On-Resistance         |                                                         |       | 80         |       | mΩ     |

Rev. 1.0 October 2019 www.aosmd.com Page 3 of 15

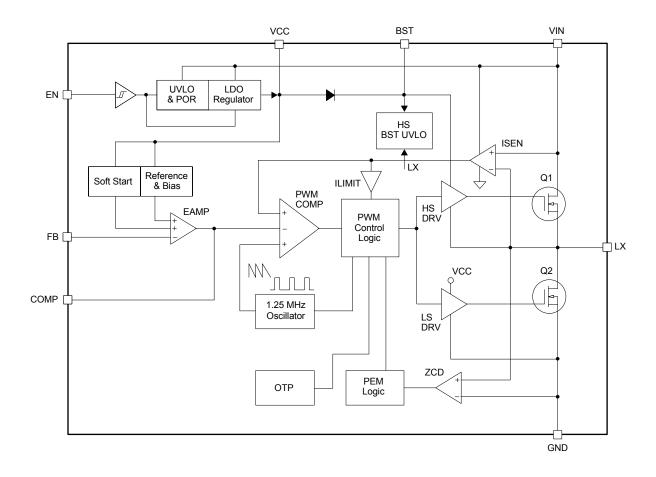

### **Functional Block Diagram**

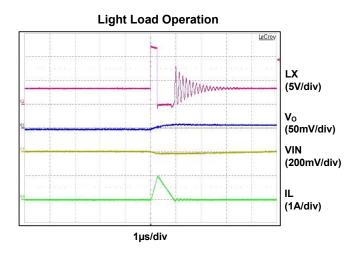

### **Typical Characteristics**

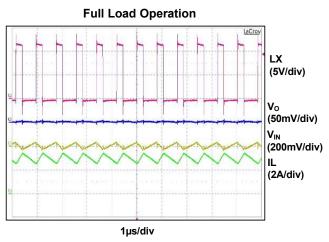

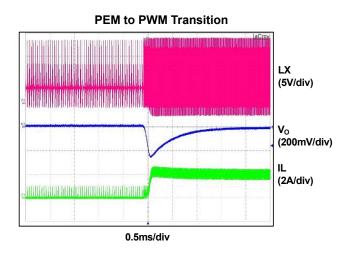

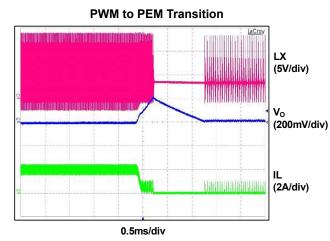

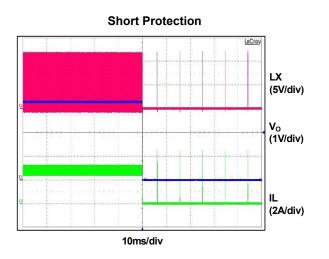

$T_A$  = 25°C,  $V_{IN}$  =  $V_{EN}$  = 12V,  $V_{OUT}$  = 3.3V, unless otherwise specified.

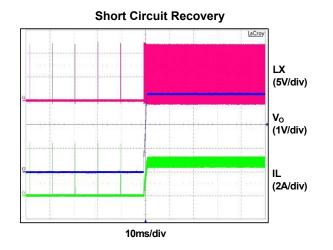

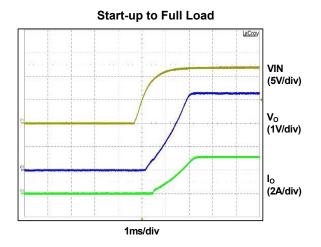

### **Typical Characteristics** (continued)

$T_A$  = 25°C,  $V_{IN}$  =  $V_{EN}$  = 12V,  $V_{OUT}$  = 3.3V, unless otherwise specified.

### **Efficiency**

Rev. 1.0 October 2019 **www.aosmd.com** Page 6 of 15

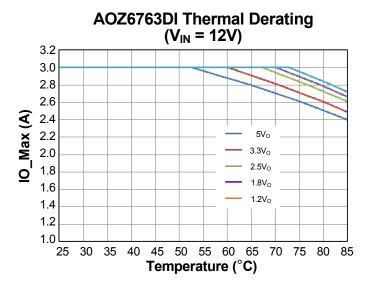

### **Thermal Derating**

Rev. 1.0 October 2019 **www.aosmd.com** Page 7 of 15

#### **Detailed Description**

The AOZ6763DI is a current-mode step down regulator with integrated high-side NMOS switch and low-side NMOS switch. It operates from a 4.5V to 18V input voltage range and supplies up to 3A of load current. Features include, enable control, Power-On Reset, input under voltage lockout, output over voltage protection, internal soft-start and thermal shut down.

The AOZ6763DI is available in DFN3x3 package.

#### **Enable and Soft Start**

The AOZ6763DI has internal soft start feature to limit inrush current and ensure the output voltage ramps up smoothly to regulation voltage. A soft start process begins when the input voltage rises to 4.1V and voltage on EN pin is HIGH. The soft start time is programmed by internal soft start capacitor and is set to 3.5ms (Typ).

The EN pin of the AOZ6763DI is active high. Connect the EN pin to VIN if enable function is not used. Pull it to ground will disable the AOZ6763DI. Do not leave it open. The voltage on EN pin must be above 2V to enable the AOZ6763DI. When voltage on EN pin falls below 0.6V, the AOZ6763DI is disabled.

#### **Light Load and PWM Operation**

Under low output current settings, the AOZ6763DI will operate with pulse energy mode to obtain high efficiency. In pulse energy mode, the PWM will not turn off until the on time get a fixed time which is defined by Vin, Vo and switching frequency.

#### **Steady-State Operation**

Under heavy load steady-state conditions, the converter operates in fixed frequency and Continuous-Conduction Mode (CCM).

he AOZ6763DI integrates an internal N-MOSFET as the high-side switch. Inductor current is sensed by amplifying the voltage drop across the drain to source of the high side power MOSFET. Output voltage is divided down by the external voltage divider at the FB pin. The difference of the FB pin voltage and reference is amplified by the internal transconductance error amplifier. The error voltage is compared against the current signal, which is sum of inductor current signal and input and output modulated voltage ramp compensation signal, at PWM comparator input. If the current signal is less than the error voltage, the internal high-side switch is on. The inductor current flows from the input through the inductor to the output. When the current signal exceeds the error voltage, the high-side switch is off. The inductor current is freewheeling through the internal low-side N-MOSFET

switch to output. The internal adaptive FET driver guarantees no turn on overlap of both high-side and low-side switch.

Comparing with regulators using freewheeling Schottky diodes, the AOZ6763DI uses freewheeling NMOSFET to realize synchronous rectification. It greatly improves the converter efficiency and reduces power loss in the low-side switch.

The AOZ6763DI uses a N-Channel MOSFET as the high-side switch. Since the NMOSFET requires a gate voltage higher than the input voltage, a boost capacitor is needed between LX pin and BST pin to drive the gate. The boost capacitor is charged while LX is low

#### **Output Voltage Programming**

Output voltage can be set by feeding back the output to the FB pin by using a resistor divider network. In the application circuit shown in Figure 1. Usually, a design is started by picking a fixed  $R_2$  value and calculating the required R1 with equation below.

$$V_O = 0.6 \times \left(1 + \frac{R_1}{R_2}\right)$$

Combination of R1 and R2 should be large enough to avoid drawing excessive current from the output, which will cause power loss.

Some standard value of  $R_1$ ,  $R_2$  and most used output voltage values are listed in Table 1.

| VO (V) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) |  |  |  |  |

|--------|-----------------|-----------------|--|--|--|--|

| 1.0    | 10              | 15              |  |  |  |  |

| 1.2    | 10              | 10              |  |  |  |  |

| 1.5    | 15              | 10              |  |  |  |  |

| 1.8    | 20              | 10              |  |  |  |  |

| 2.5    | 31.6            | 10              |  |  |  |  |

| 3.3    | 68.1            | 15              |  |  |  |  |

| 5.0    | 110             | 15              |  |  |  |  |

Table 1.

Rev. 1.0 October 2019 www.aosmd.com Page 8 of 15

#### **Protection Features**

The AOZ6763DI has multiple protection features to prevent system circuit damage under abnormal conditions.

#### **Over Current Protection (OCP)**

The sensed low side MOSFET valley current signal is also used for over current protection. Since the AOZ6763DI employs valley current mode control, during over current conditions, it will skip a pulse if the valley current over the OC point setting until the output drop to some level after current limit. The AOZ6763DI will shut down and auto restart with hiccup mode. To prevent the current running away in the extreme case, the minimum inductor value needed is 2.2µH for the application.

#### Power-On Reset (POR)

A power-on reset circuit monitors the VIN voltage. When the VIN voltage exceeds 4.1V, the converter starts operation. When VIN voltage falls below 3.7V, the converter will be shut down.

#### **Thermal Protection**

An internal temperature sensor monitors the junction temperature. It shuts down the internal control circuit and high side NMOS if the junction temperature exceeds 150°C. The regulator will restart automatically under the control of soft-start circuit when the junction temperature decreases to 100°C.

#### Application Information

The basic AOZ6763DI application circuit is show in Figure 1. Component selection is explained below.

#### **Input Capacitor**

The input capacitor must be connected to the  $V_{\text{IN}}$  pin and GND pin of AOZ6763DI to maintain steady input voltage and filter out the pulsing input current. The voltage rating of input capacitor must be greater than maximum input voltage plus ripple voltage.

The input ripple voltage can be approximated by equation below:

$$\Delta V_{IN} = \frac{I_{O}}{f \times C_{IN}} \times \left(1 - \frac{V_{O}}{V_{IN}}\right) \times \frac{V_{O}}{V_{IN}}$$

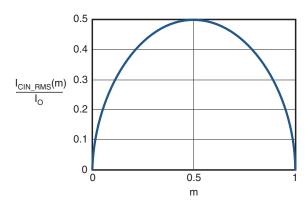

Since the input current is discontinuous in a buck converter, the current stress on the input capacitor is another concern when selecting the capacitor. For a buck circuit, the RMS value of input capacitor current can be calculated by:

$$I_{CIN\_RMS} = I_O \times \sqrt{\frac{V_O}{V_{IN}} (1 - \frac{V_O}{V_{IN}})}$$

if let *m* equal the conversion ratio:

$$\frac{V_O}{V_{IN}} = m$$

The relation between the input capacitor RMS current and voltage conversion ratio is calculated and shown in Figure 2 below. It can be seen that when  $V_O$  is half of  $V_{IN}$ ,  $C_{IN}$  it is under the worst current stress. The worst current stress on  $C_{IN}$  is 0.5 x  $I_O$ .

Figure 2. I<sub>CIN</sub> vs. Voltage Conversion Ratio

For reliable operation and best performance, the input capacitors must have current rating higher than I<sub>CIN-RMS</sub> at worst operating conditions. Ceramic capacitors are preferred for input capacitors because of their low ESR and high current rating. Depending on the application circuits, other low ESR tantalum capacitor may also be used. When selecting ceramic capacitors, X5R or X7R type dielectric ceramic capacitors should be used for their better temperature and voltage characteristics. Note that the ripple current rating from capacitor manufactures are based on certain amount of life time. Further derating may be necessary in practical design.

#### Inductor

The inductor is used to supply constant current to output when it is driven by a switching voltage. For given input and output voltage, inductance and switching frequency together decide the inductor ripple current, which is:

$$\Delta I_L = \frac{V_O}{f \times L} \times \left(1 - \frac{V_O}{V_{IN}}\right)$$

The peak inductor current is:

$$I_{Lpeak} = I_O + \frac{\Delta I_L}{2}$$

High inductance gives low inductor ripple current but requires larger size inductor to avoid saturation. Low ripple current reduces inductor core losses. It also reduces RMS current through inductor and switches, which results in less conduction loss. Usually, peak to peak ripple current on inductor is designed to be 20% to 40% of output current.

When selecting the inductor, make sure it is able to handle the peak current without saturation even at the highest operating temperature.

The inductor takes the highest current in a buck circuit. The conduction loss on inductor need to be checked for thermal and efficiency requirements.

Surface mount inductors in different shape and styles are available from Coilcraft, Elytone and Murata. Shielded inductors are small and radiate less EMI noise. But they cost more than unshielded inductors. The choice depends on EMI requirement, price and size.

#### **Output Capacitor**

The output capacitor is selected based on the DC output voltage rating, output ripple voltage specification and ripple current rating.

The selected output capacitor must have a higher rated voltage specification than the maximum desired output voltage including ripple. De-rating needs to be considered for long term reliability.

Output ripple voltage specification is another important factor for selecting the output capacitor. In a buck converter circuit, output ripple voltage is determined by inductor value, switching frequency, output capacitor value and ESR. It can be calculated by the equation below:

$$\Delta V_{O} = \Delta I_{L} \times \left( ESR_{CO} + \frac{1}{8 \times f \times C_{O}} \right)$$

where.

${\sf C}_{\sf O}$  is output capacitor value and  ${\sf ESR}_{\sf CO}$  is the Equivalent Series Resistor of output capacitor.

When a low ESR ceramic capacitor is used as output capacitor, When low ESR ceramic capacitor is used as output capacitor, the impedance of the capacitor at the switching frequency dominates. Output ripple is mainly

caused by capacitor value and inductor ripple current. The output ripple voltage calculation can be simplified to:

$$\Delta V_{O} = \Delta I_{L} \times \frac{1}{8 \times f \times C_{O}}$$

If the impedance of ESR at switching frequency dominates, the output ripple voltage is mainly decided by capacitor ESR and inductor ripple current. The output ripple voltage calculation can be further simplified to:

$$\Delta V_{O} = \Delta I_{L} \times ESR_{CO}$$

For lower output ripple voltage across the entire operating temperature range, X5R or X7R dielectric type of ceramic, or other low ESR tantalum are recommended to be used as output capacitors.

In a buck converter, output capacitor current is continuous. The RMS current of output capacitor is decided by the peak to peak inductor ripple current. It can be calculated by:

$$I_{CO\_RMS} = \frac{\Delta I_L}{\sqrt{12}}$$

Usually, the ripple current rating of the output capacitor is a smaller issue because of the low current stress. When the buck inductor is selected to be very small and inductor ripple current is high, output capacitor could be overstressed.

#### **Loop Compensation**

The AOZ6763DI employs peak current mode control for easy use and fast transient response. Peak current mode control eliminates the double pole effect of the output L&C filter. It greatly simplifies the compensation loop design.

With peak current mode control, the buck power stage can be simplified to be a one-pole and one-zero system in frequency domain. The pole is dominant pole can be calculated by:

$$f_{p1} = \frac{1}{2\pi \times C_O \times R_L}$$

The zero is a ESR zero due to output capacitor and its ESR. It is can be calculated by:

$$f_{Z1} = \frac{1}{2\pi \times C_O \times ESR_{CO}}$$

Where CO is the output filter capacitor;

R<sub>I</sub> is load resistor value;

ESR<sub>CO</sub> is the equivalent series resistance of output capacitor;

The compensation design is actually to shape the converter control loop transfer function to get desired gain and phase. Several different types of compensation network can be used for the AOZ6763DI. For most cases, a series capacitor and resistor network connected to the COMP pin sets the pole-zero and is adequate for a stable high-bandwidth control loop.

In the AOZ6763DI, FB pin and COMP pin are the inverting input and the output of internal error amplifier. A series R and C compensation network connected to COMP provides one pole and one zero. The pole is:

$$f_{p2} = \frac{G_{EA}}{2\pi \times Cc \times G_{VEA}}$$

Where  $G_{EA}$  is the error amplifier transconductance,  $G_{VEA}$  is the error amplifier voltage gain,  $C_c$  is compensation capacitor in figure 1.

The zero given by the external compensation network, capacitor Cc and resistor Rc, is located at:

$$f_{Z2} = \frac{1}{2\pi \times C_c \times R_c}$$

To design the compensation circuit, a target crossover frequency  $f_{\mathbb{C}}$  for close loop must be selected. The system crossover frequency is where control loop has unity gain. The crossover is the also called the converter bandwidth. Generally a higher bandwidth means faster response to load transient. However, the bandwidth should not be too high because of system stability concern. When designing the compensation loop, converter stability under all line and load condition must be considered.

Usually, it is recommended to set the bandwidth to be equal or less than 1/10 of switching frequency.

The strategy for choosing  $R_{\text{c}}$  and Cc is to set the cross over frequency with Rc and set the compensator zero

with  $C_{c}$ . Using selected crossover frequency,  $f_{C}$ , to calculate  $R_{3}$ :

$$R_c = f_C \times \frac{V_O}{V_{FR}} \times \frac{2\pi \times C_o}{G_{EA} \times G_{CS}}$$

where  $f_C$  is desired crossover frequency. For best performance, fc is set to be about 1/10 of switching frequency;

$V_{FB}$  is 0.6V;

G<sub>EA</sub> is the error amplifier transconductance,

G<sub>CS</sub> is the current sense circuit

transconductance, which is 5 A/V;

The compensation capacitor  $C_c$  and resistor  $R_c$  together make a zero. This zero is put somewhere close to the dominate pole  $f_{p1}$  but lower than 1/5 of selected crossover frequency.  $C_2$  can is selected by:

Equation above can also be simplified to:

$$C_c = \frac{C_O \times R_L}{Rc}$$

An easy-to-use application software which helps to design and simulate the compensation loop can be found at <a href="https://www.aosmd.com">www.aosmd.com</a>.

## Thermal Management and Layout Consideration

In the AOZ6763DI buck regulator circuit, high pulsing current flows through two circuit loops. The first loop starts from the input capacitors, to the VIN pin, to the LX pad, to the filter inductor, to the output capacitor and load, and then return to the input capacitor through ground. Current flows in the first loop when the high side switch is on. The second loop starts from inductor, to the output capacitors and load, to the low side NMOSFET. Current flows in the second loop when the low side NMOSFET is on.

In PCB layout, minimizing the two loops area reduces the noise of this circuit and improves efficiency. A ground plane is strongly recommended to connect input capacitor, output capacitor, and GND pin of the AOZ6763DI

In the AOZ6763DI buck regulator circuit, the major power dissipating components are the AOZ6763DI and the output inductor. The total power dissipation of converter circuit can be measured by input power minus output power.

$$P_{total\ loss} = V_{IN} \times I_{IN} - V_O \times I_O$$

The power dissipation of inductor can be approximately calculated by output current and DCR of inductor.

$$P_{inductor\_loss} = I_0^2 \times R_{inductor} \times 1.1$$

The actual junction temperature can be calculated with power dissipation in the AOZ6763DI and thermal impedance from junction to ambient.

$$T_{junction} = (P_{total\_loss} - P_{inductor\_loss}) \times \Theta_{JA}$$

The maximum junction temperature of AOZ6763DI is 150°C, which limits the maximum load current capability.

The thermal performance of the AOZ6763DI is strongly affected by the PCB layout. Extra care should be taken by users during design process to ensure that the IC will operate under the recommended environmental conditions.

The AOZ6763DI is an exposed pad DFN3x3 package. Several layout tips are listed below for the best electric and thermal performance.

- 1. The exposed thermal pad has to connect to ground by PCB externally. Connect a large copper plane to exposed thermal pad to help thermal dissipation.

- Do not use thermal relief connection to the VIN and the GND pin. Pour a maximized copper area to the GND pin and the VIN pin to help thermal dissipation.

- 3. Input capacitor should be connected to the VIN pin and the GND pin as close as possible.

- 4. Make the current trace from LX pins to L to Co to the GND as short as possible.

- Pour copper plane on all unused board area and connect it to stable DC nodes, like VIN, GND or VOUT.

- 6. Keep sensitive signal trace far away from the LX pad.

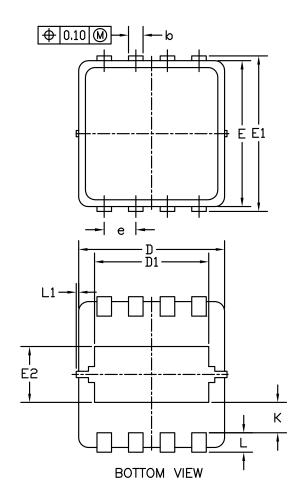

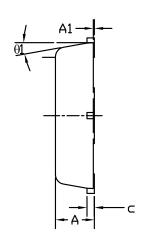

### Package Dimensions, DFN3x3B-8L, EP1\_P

| SYMBOLS | DIMENS | IONS IN MILLI | METERS | DIMENSIONS IN INCHES |       |       |  |  |

|---------|--------|---------------|--------|----------------------|-------|-------|--|--|

| STMBULS | MIN    | NOM           | MAX    | MIN                  | NOM   | MAX   |  |  |

| A       | 0.70   | 0.80          | 0.90   | 0.028                | 0.031 | 0.035 |  |  |

| A1      | 0.00   |               | 0.05   | 0.000                |       | 0.002 |  |  |

| b       | 0. 24  | 0.30          | 0.35   | 0.009                | 0.012 | 0.014 |  |  |

| c       | 0. 10  | 0. 15         | 0. 25  | 0.004                | 0.006 | 0.010 |  |  |

| D       | 2. 90  | 3.00          | 3. 10  | 0.114                |       | 0.122 |  |  |

| D1      | 2. 15  | 2. 35         | 2. 55  | 0.085                |       | 0.100 |  |  |

| Е       | 2. 90  | 3.00          | 3. 10  | 0.114                | 0.118 | 0.122 |  |  |

| E1      | 3. 05  | 05 3. 20 3. 3 |        | 0.120                | 0.126 | 0.132 |  |  |

| E2      | 1. 10  | 1. 15         | 1.20   | 0.043                | 0.045 | 0.047 |  |  |

| e       | 0.60   | 0.65          | 0.70   | 0.024                | 0.026 | 0.028 |  |  |

| K       | 0. 575 | 0.625         | 0.675  | 0.023                | 0.025 | 0.027 |  |  |

| L       | 0.30   | 0.40          | 0.50   | 0.012                | 0.016 | 0.020 |  |  |

| L1      | 0      |               | 0.10   | 0                    |       | 0.004 |  |  |

| θ1      | 0      | 10            | 12     | 0                    | 10    | 12    |  |  |

### NOTE

- 1. PAKCAGE BODY SIZES EXCLUDE MOLD FLASH AND GATE BURRS. MOLD FLASH AT THE NON-LEAD SIDES SHOULD BE LESS THAN 6 MILS EACH.

- 2. CONTROLLING DIMENSION IS MILLIMETER. CONVERTED INCH DIMENSIONS ARE NOT NECESSARILY EXACT.

Rev. 1.0 October 2019 **www.aosmd.com** Page 13 of 15

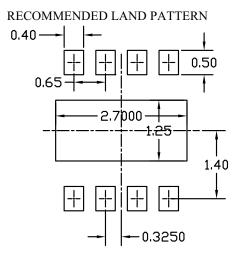

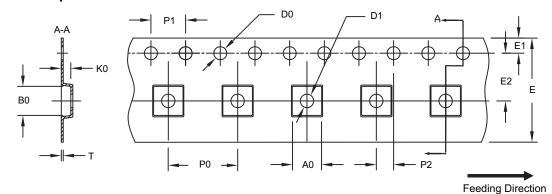

### Tape and Reel Dimensions, DFN3x3B-8L, EP1\_P

#### **Carrier Tape**

UNIT: mm

| Package    | A0    | В0    | K0    | D0       | D1       | E     | E1    | E2    | P0    | P1    | P2    | Т     |

|------------|-------|-------|-------|----------|----------|-------|-------|-------|-------|-------|-------|-------|

| DFN 3x3 EP | 3.40  | 3.35  | 1.10  | 1.50     | 1.50     | 12.00 | 1.75  | 5.50  | 8.00  | 4.00  | 2.00  | 0.30  |

|            | ±0.10 | ±0.10 | ±0.10 | +0.10/-0 | +0.10/-0 | ±0.30 | ±0.10 | ±0.05 | ±0.10 | ±0.10 | ±0.05 | ±0.05 |

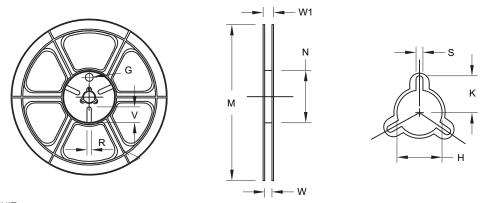

#### Reel

UNIT: mm

| Tape Size | Reel Size | M      | N     | W     | W1   | Н         | K    | S    | G | R | ٧ |  |

|-----------|-----------|--------|-------|-------|------|-----------|------|------|---|---|---|--|

| 12mm      | ø330      | ø330.0 | ø97.0 | 13.0  | 17.4 | ø13.0     | 10.6 | 2.0  | _ | _ | _ |  |

|           |           | ±0.50  | ±1.0  | ±0.30 | ±1.0 | +0.5/-0.2 |      | ±0.5 |   |   |   |  |

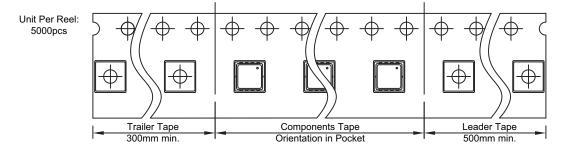

#### Leader/Trailer and Orientation

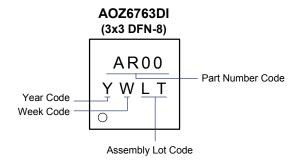

#### Part Marking

#### LEGAL DISCLAIMER

Applications or uses as critical components in life support devices or systems are not authorized. AOS does not assume any liability arising out of such applications or uses of its products. AOS reserves the right to make changes to product specifications without notice. It is the responsibility of the customer to evaluate suitability of the product for their intended application. Customer shall comply with applicable legal requirements, including all applicable export control rules, regulations and limitations.

AOS' products are provided subject to AOS' terms and conditions of sale which are set forth at: http://www.aosmd.com/terms and conditions of sale

#### LIFE SUPPORT POLICY

ALPHA AND OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

#### As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

Rev. 1.0 October 2019 www.aosmd.com Page 15 of 15