# **LED Backlight Driver**

The NCS29001 is an integrated LED driver used in LCD display backlighting applications. A configurable bill of materials allows the designer to create a highly efficient solution for a variety of LCD screen sizes. The NCS29001 uses a boost type converter to deliver constant current in a string of LEDs. High accuracy PWM dimming is supported for a frequency up to 500 Hz. The integrated soft start function provides excellent control during the power up sequence to avoid current overshoot. The device protects against output overvoltage, open / short LED, and thermal overload. The NCS29001 is offered in the cost effective SOIC–14 package.

#### **Features**

- 8.5 V to 18 V Input Voltage Range

- ±1% Vref Voltage Accuracy to set LED Current

- PWM Controlled Dimming

- Soft Start Limits In-Rush Current

- Open Feedback Protection

- Open LED Protection

- Short LED Protection

- LED String Cathode Short to ground Protection

- Max Duty Cycle Above 90%

- SOIC-14 Package

- This is a Pb-Free Device

### **Typical Application**

- TFT-LCD TV Panels

- LCD Monitor Panels

### ON Semiconductor®

http://onsemi.com

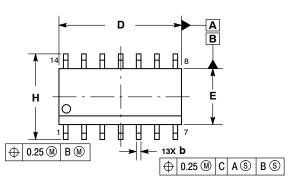

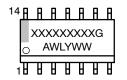

SOIC-14 NB CASE 751A

**MARKING**

**DIAGRAM**

NCS29001= Specific Device Code

A = Assembly Location

WL = Wafer Lot

Y = Year

WW = Work Week

G = Pb-Free Package

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 15 of this data sheet.

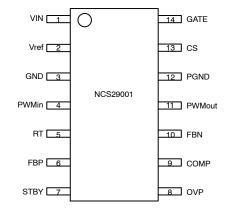

Figure 1. Block Diagram

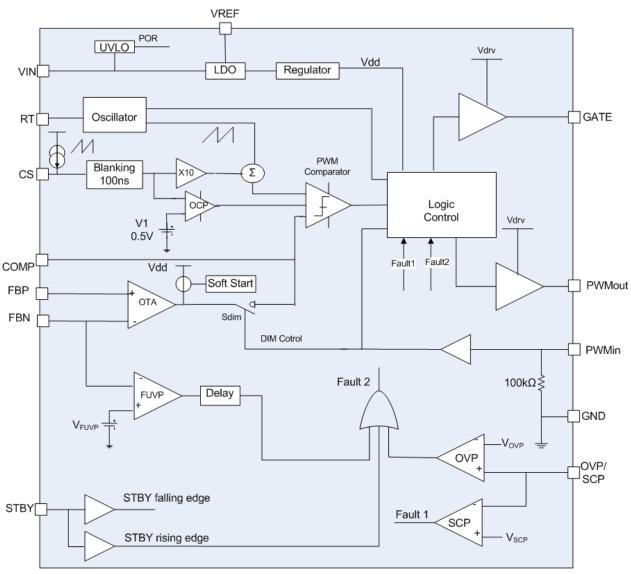

## **PINOUT ASSIGNMENT**

Figure 2. NSC29001 Pinout

### **PIN DESCRIPTION**

| Pin# | Symbol | Type   | Description                                                                                                                                                                                                                                                                                       |

|------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VIN    | Input  | VIN supply input. Small 1.0 μF low ESR bypass capacitor required from VIN to GND.                                                                                                                                                                                                                 |

| 2    | VREF   | Output | $5~V/10$ mA reference voltage. Small 1.0 $\mu F$ low ESR bypass capacitor required from VREF to GND.                                                                                                                                                                                              |

| 3    | GND    | Ground | Analog ground.                                                                                                                                                                                                                                                                                    |

| 4    | PWMin  | Output | PWM dimming control input.                                                                                                                                                                                                                                                                        |

| 5    | RT     | Output | The resistor connected between RT and GND sets the switching frequency                                                                                                                                                                                                                            |

| 6    | FBP    | Input  | The reference voltage for the feedback (FBN). Reference level can be adjusted from 0.5 V up to 3.0 V using an external voltage divider.                                                                                                                                                           |

| 7    | STBY   | Input  | The converter enters in standby mode when STBY is floating or pulled high. When STBY goes from low to high the circuit will discharge the capacitors on the COMP pin and keep PWMout high to discharge the output capacitor. STBY must remain high for 50 ms before the part enters standby mode. |

| 8    | OVP    | Output | This pin provides the overvoltage protection for the converter. When the voltage at this pin exceeds 1.2 V, the boost converter stops immediately and the device enters standby mode.                                                                                                             |

| 9    | COMP   | Power  | Loop compensation pin                                                                                                                                                                                                                                                                             |

| 10   | FBN    | Input  | Feedback pin and LED cathode connection. External resistor from FBN to GND sets the LED current.                                                                                                                                                                                                  |

| 11   | PWMout | Output | PWM dimming output driver.                                                                                                                                                                                                                                                                        |

| 12   | PGND   | Ground | Power ground.                                                                                                                                                                                                                                                                                     |

| 13   | CS     | Power  | This pin is used to sense the drain current of the external power MOSFET. It includes a built-in blanking time.                                                                                                                                                                                   |

| 14   | GATE   | Output | This pin is the output GATE driver for an external N-channel power MOSFET                                                                                                                                                                                                                         |

#### **ATTRIBUTES**

| Characteristics                                                              | Values               |

|------------------------------------------------------------------------------|----------------------|

| ESD protection (all pins) Human Body Model (HBM) (Note 1) Machine Model (MM) | 2 kV<br>150 V        |

| Moisture sensitivity (Note 2)                                                | Level 1              |

| Flammability Rating Oxygen Index: 28 to 34                                   | UL 94 V-0 @ 0.125 in |

| Meets or exceeds JEDEC Spec EIA/JESD78 IC Latch-up Test                      |                      |

- 1. Human Body Model (HBM), R = 1500  $\Omega$ , C = 100 pF. 2. For additional information, see Application Note AND8003/D.

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating          | V <sub>MIN</sub> | V <sub>MAX</sub> | Unit |

|-----------------|------------------|------------------|------|

| V <sub>IN</sub> | -0.3             | 30               | V    |

| PWMin           | -0.3             | 5.5              | V    |

| STBY            | -0.3             | 5.5              | V    |

| FBP             | -0.3             | 5.5              | V    |

| FBN             | -0.3             | 5.5              | V    |

| OVP             | -0.3             | 5.5              | V    |

| CS              | -0.3             | 5.5              | V    |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## OPERATING CONDITIONS $(T_A = +25^{\circ}C)$

| Rating                                 | Min | Тур | Max | Unit |

|----------------------------------------|-----|-----|-----|------|

| V <sub>IN</sub>                        | 8.5 | 12  | 18  | V    |

| VIL_PWMin: PWMin input low voltage     |     |     | 1   | V    |

| VIH_PWMin: PWMin input high voltage    | 2   |     |     | V    |

| FBP                                    | 0.5 |     | 3.0 | V    |

| VIL_STBY: STBY input low voltage       |     |     | 1   | V    |

| VIH_STBY: STBY input high voltage      | 2   |     |     | V    |

| RT clock frequency resistor (Note 3)   | 20  |     | 140 | kΩ   |

| Fdim dimming frequency (5 V amplitude) | 100 |     | 300 | Hz   |

| Ddim dimming duty-cycle                | 3   |     | 95  | %    |

NOTE: With respect to the GND pin.

3. Choose RT to keep clock frequency between 100 kHz and 500 kHz.

### **THERMAL RATINGS**

| Parameter                                      | Symbol           | Rating      | Unit |

|------------------------------------------------|------------------|-------------|------|

| Junction to ambient thermal impedance (Note 4) | $R_{\theta JA}$  | 150         | °C/W |

| Maximum Junction Temperature (Note 5)          | TJ               | +150        | °C   |

| Operating Ambient Temperature                  | T <sub>A</sub>   | -40 to +85  | °C   |

| Storage temperature                            | T <sub>stg</sub> | -65 to +150 | °C   |

- 4. Power dissipation must be considered to ensure maximum junction temperature ( $\theta JA$ ) is not exceeded.

- 5. Thermal Pad attached to PCB, 0 lfm airflow, and 76 mm x 76 mm copper area.

# **ELECTRICAL SPECIFICATIONS** $V_{IN}$ = 12 V, $T_{AMB}$ = -40°C to 85°C; typical values are at 25°C

| Symbol                 | Parameter                            | Condition                                                                                                       | Min  | Тур  | Max  | Unit  |

|------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| VIN (VIN Pin)          |                                      |                                                                                                                 |      |      |      |       |

| I <sub>VIN</sub>       | Operating Supply Current             | V <sub>IN</sub> = 12 V; PWMin = 5 V; no load,<br>STBY = 5 V                                                     |      |      | 5    | mA    |

| I <sub>SHUTDOWN</sub>  | Shutdown Mode Supply Current         | PWMin = GND<br>Ambient temperature 25°C<br>STBY = 5 V                                                           |      |      | 12   | uA    |

| UVLO                   | Under Voltage Lockout<br>Threshold   | VIN Rising                                                                                                      | 7.5  | 8    | 8.5  | ٧     |

| ΔUVLO                  | UVLO Hysteresis                      |                                                                                                                 |      | 475  |      | mV    |

| T <sub>startup</sub>   | Startup time                         | Time from standby falling edge to steady-state V <sub>boost</sub> operation with 30% dimming pattern – (Note 6) |      |      | 100  | ms    |

| VREF (VREF F           | Pin)                                 |                                                                                                                 |      | •    | -    |       |

| VREF                   | Vref voltage                         | REF bypassed with a 1 μF capacitor to GND                                                                       | 4.95 | 5    | 5.05 | V     |

| Line_Reg               | Line Regulation                      | V <sub>IN</sub> = 8.5 V to 24 V at I_REF = 10 mA                                                                |      | 0.08 | 0.20 | %     |

| Load_Reg               | Load Regulation                      | 0 mA < I_REF < 10 mA at VIN = 12 V                                                                              |      |      | 0.6  | mV/mA |

| I <sub>CC</sub> (Vref) | Iref output current                  | VREF bypassed with a 1 μF capacitor to GND                                                                      |      |      | 10   | mA    |

| GATE (GATE,            | RT Pins)                             |                                                                                                                 |      |      |      |       |

| V <sub>OH_GATE</sub>   | GATE output high voltage             | V <sub>IN</sub> = 12 V                                                                                          | 7.5  | 10   | 15   | V     |

| I <sub>SOURCE</sub>    | GATE short circuit current           |                                                                                                                 |      | 0.33 | 0.45 | Α     |

| I <sub>SINK</sub>      | GATE sinking current                 |                                                                                                                 |      | 0.33 | 0.45 | Α     |

| T <sub>RISE</sub>      | GATE output rise time                | Output voltage rise-time @ C <sub>L</sub> = 1 nF, 10-90% of output signal (Note 6)                              | -    | 40   |      | ns    |

| T <sub>FALL</sub>      | GATE output fall time                | Output voltage fall-time @ C <sub>L</sub> = 1 nF,<br>90-10% of output signal (Note 6)                           | -    | 20   |      | ns    |

| R <sub>OH</sub>        | Source resistance                    |                                                                                                                 |      | 13   |      | Ω     |

| R <sub>OL</sub>        | Sink resistance                      |                                                                                                                 |      | 6.0  |      | Ω     |

| D <sub>LSS_MAX</sub>   | Maximum Duty Cycle                   | (Note 6)                                                                                                        | 93   | 95   |      | %     |

| Fosc                   | Boost Switching Frequency range      |                                                                                                                 | 100  |      | 500  | kHz   |

| ±ΔF <sub>OSC</sub>     | Frequency Accuracy                   |                                                                                                                 | -10  |      | +10  | %     |

| $V_{RT}$               | RT pin output voltage                |                                                                                                                 | 0.85 | 1    | 1.15 | V     |

| PWM DIMMING            | G (PWMin, PWMout Pins)               |                                                                                                                 |      |      |      |       |

| V <sub>OH_PWMout</sub> | PWMout output high voltage           | V <sub>IN</sub> = 12 V                                                                                          | 7.5  | 10   | 15   | V     |

| ΔD_DIM                 | PWMout/PWMin Duty cycle<br>Tolerance |                                                                                                                 | 0.98 | 1    | 1.02 | %     |

| T <sub>RISE</sub>      | PWMout output rise time              | Output voltage rise-time @ C <sub>L</sub> = 1 nF, 10-90% of output signal                                       | -    | _    | 2    | us    |

| T <sub>FALL</sub>      | PWMout output fall time              | Output voltage fall-time @ C <sub>L</sub> = 1 nF, 90-10% of output signal                                       | -    | _    | 2    | us    |

| I <sub>SOURCE</sub>    | PWMout short circuit current         |                                                                                                                 |      | 15   | 20   | mA    |

| I <sub>SINK</sub>      | PWMout sinking current               |                                                                                                                 |      | 15   | 20   | mA    |

| R <sub>OH</sub>        | Source resistance                    |                                                                                                                 |      | 270  |      | Ω     |

| R <sub>OL</sub>        | Sink resistance                      |                                                                                                                 |      | 230  |      | Ω     |

6. Guaranteed by characterization and design

## **ELECTRICAL SPECIFICATIONS** $V_{IN}$ = 12 V, $T_{AMB}$ = -40°C to 85°C; typical values are at 25°C

| Symbol               | Parameter                                                               | Condition | Min | Тур | Max | Unit |

|----------------------|-------------------------------------------------------------------------|-----------|-----|-----|-----|------|

| CURRENT SI           | ENSE (CS Pin)                                                           |           | •   | •   |     | •    |

| V <sub>CS</sub>      | Reference voltage threshold for current clamp monitoring OCP comparator |           |     | 0.5 | 0.6 | V    |

| I <sub>RAMP</sub>    | Slope compensation ramp                                                 |           |     | 130 |     | A/s  |

| PROTECTION           | N (OVP, FBP, FBN Pins)                                                  |           |     |     |     |      |

| V <sub>OVP</sub>     | Output Overvoltage Protection on OVP pin                                |           |     | 1.2 | 1.3 | V    |

| $V_{SCP}$            | Short Circuit Protection on OVP pin                                     |           | 60  | 75  |     | mV   |

| $V_{\text{UVPfb}}$   | Output Undervoltage Protection on FBN                                   |           | 60  | 75  |     | mV   |

| T <sub>SD</sub>      | Thermal Shutdown                                                        | (Note 6)  | 140 | 150 | 160 | °C   |

| $\DeltaT_{SD}$       | TSD hytheresis                                                          | (Note 6)  |     | 15  |     | °C   |

| STANDBY (S           | TBY Pin)                                                                |           | •   |     |     |      |

| T <sub>STANDBY</sub> | Standby mode delay                                                      | (Note 6)  |     | 50  |     | ms   |

<sup>6.</sup> Guaranteed by characterization and design

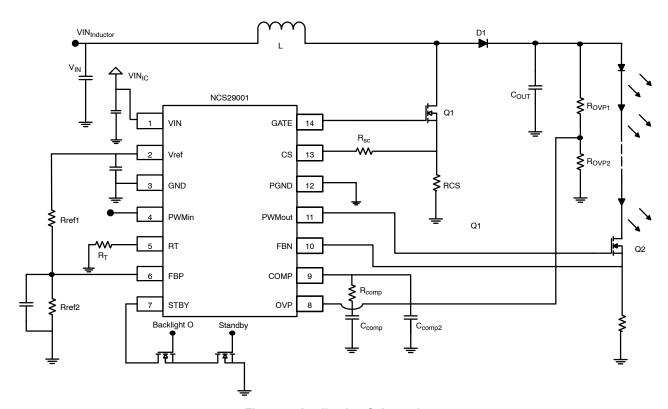

## **APPLICATION DIAGRAM**

Figure 3. Application Schematic

#### **APPLICATION CONDITIONS**

| Symbol                      | Parameter               | Condition                                                                                                                                                                                                                                                                     | Min | Тур      | Max | Unit |

|-----------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-----|------|

| VIN <sub>IC</sub>           | VIN pin voltage         |                                                                                                                                                                                                                                                                               | 8.5 | 12       | 18  | V    |

| VIN <sub>Inductor</sub>     | Inductor input voltage  |                                                                                                                                                                                                                                                                               | 8.5 |          | 80  |      |

| V <sub>OUT</sub>            | Output voltage range    | V <sub>OUT</sub> /VIN <sub>Inductor</sub> Max = 5<br>VIN <sub>Inductor</sub> = 8.5 to 24 V   V <sub>OUT</sub> = 50 to 80 V<br>VIN <sub>Inductor</sub> = 24 to 50 V   V <sub>OUT</sub> = 80 to 130 V<br>VIN <sub>Inductor</sub> = 50 to 80 V   V <sub>OUT</sub> = 130 to 240 V | 50  |          | 240 | ٧    |

| η                           | Peak efficiency         | VIN <sub>IC</sub> = 12 V, V <sub>OUT</sub> = 130 V, I <sub>OUT</sub> = 200 mA<br>VIN <sub>IC</sub> = 12 V, V <sub>OUT</sub> = 240 V, I <sub>OUT</sub> = 200 mA                                                                                                                |     | 95<br>95 |     | %    |

| $\Delta \varsigma_{ m OYT}$ | Output Voltage Accuracy | including voltage ripple, from –40°C to 85°C, VIN <sub>IC</sub> = 8.5 V to 18 V                                                                                                                                                                                               | -2  |          | 2   | %    |

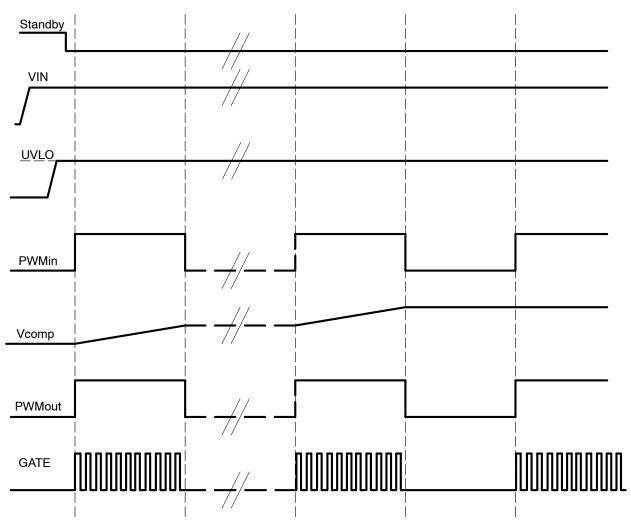

### **POWER UP SEQUENCE**

Figure 4. Soft Start Power Up from Standby

For the device to begin the soft start sequence the VIN pin voltage needs to be above the UVLO threshold and the OVP pin voltage needs to be above the  $V_{SCP}$  threshold. From standby mode soft start will begin when STBY pin goes low and PWMin pin goes high and lasts for a fixed number of clock cycles. This ensures that smooth start up if the device is powered on from standby with a PWM input.

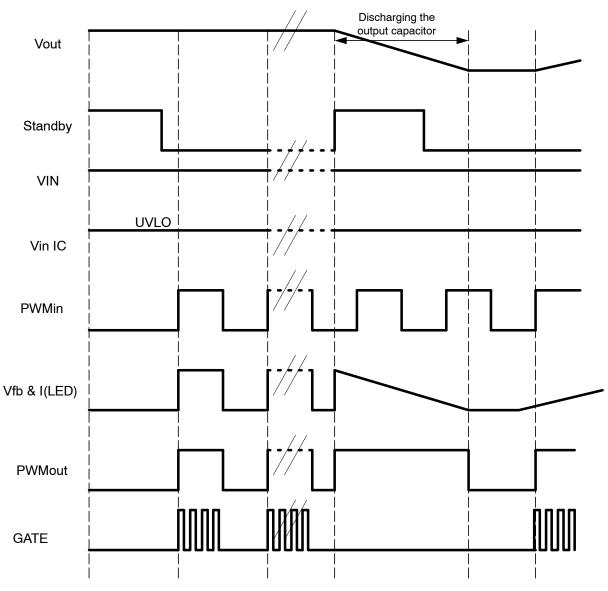

### STANDBY ON AND OFF SEQUENCE

Figure 5. Entering Standby Mode

The STBY pin contains an internal 5 M $\Omega$  pull-up resistor to VREF. This resistor limits current consumption when the device is in standby mode and also ensures the device will remain in standby if the STBY pin is left floating.

When the STBY goes high the boost converter will stop switching and the PWMout pin will switch, or remain high for 50 ms. This allows the output capacitor to discharge and the LED current to fall to zero. The device will be in a low power standby mode and can begin soft start from the next enable sequence.

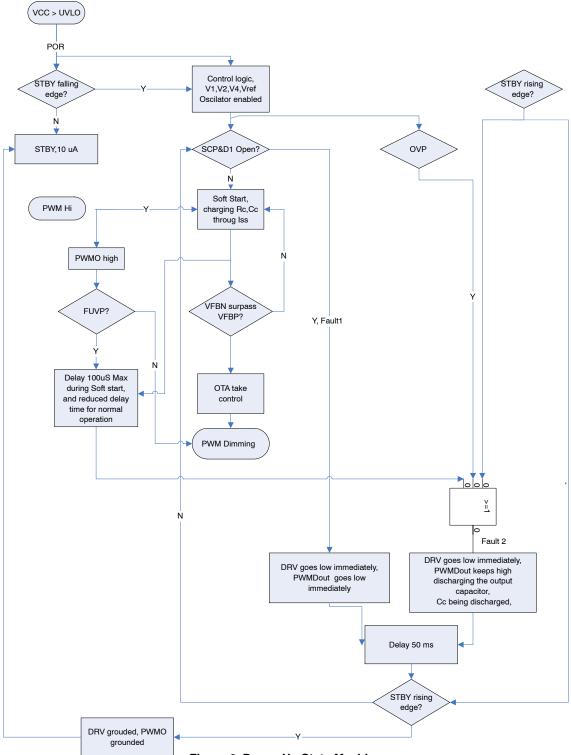

Figure 6. Power Up State Machine

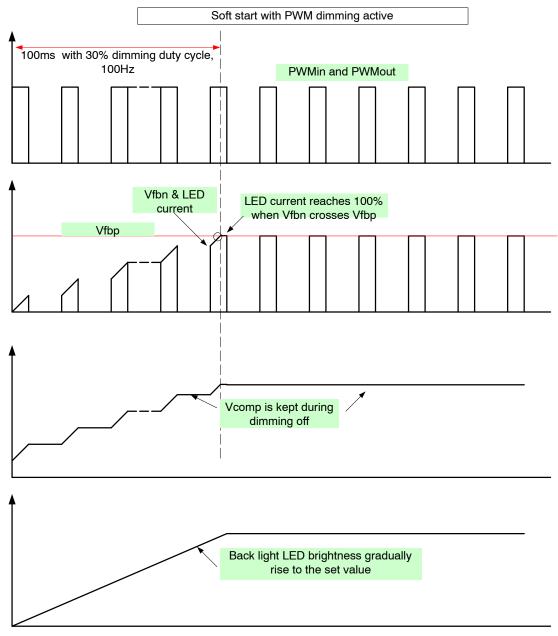

#### **SOFT START WITH PWM INPUT**

Figure 7 below shows an example of a soft start when the device is powered up from standby with a PWM input. The PWM signal here is at 100 Hz with a duty cycle of 30%. In this case the LED reaches 100% of its programmed value in 100 ms. This time can be decreased if the PWM signal runs at a higher duty cycle.

Figure 7. Soft Start with PWM Input

### **GATE AND PWMOUT PIN DRIVER CIRCUIT**

Since external transistors are required for the boost converter and PWM dimming functions, the device contains an internal 10 V regulator to drive the gate of these transistors. In the case of the PWM transistor this also functions as a level translator for the PWMin input pin. When selecting external components it is important that the transistor has enough gate drive to ensure low  $R_{DS(on)}$  for the expected current.

It should be noted that the internal 10 V regulator will start to drop when the VIN voltage is sufficiently low. When the  $V_{IN}$  voltage is 8.5 V the gate drivers will be limited to around 7.7 V.

#### **VREF REFERENCE VOLTAGE**

The device contains an accurate 5 V reference that can supply up to 10 mA and can be accessed through the VREF pin. It can be used to program the LED feedback voltage by using a resistor divider on the FBP pin. This reference is only active when STBY = low. When the device is in standby mode the VREF pin voltage will drop to 4.2 V typical with a minimum of 3.5 V. The VREF will return to 5 V immediately when STBY is driven high.

#### **MINIMUM ON & OFF TIME**

If the steady state duty cycle and switching frequency combine to generate short Ton times (low VOUT/VIN converter ratio), the converter will skip some cycles to regulate  $V_{OUT}$  which will increase output voltage ripple. The timing limit is set by the intrinsic loop propagation delay and the switching frequency will be limited by the minimum ON time and OFF time.

### THE INDUCTOR SELECTION

For a given application, it is necessary to know the input voltage at the inductor ( $VIN_{INDUCTOR}$ ), the output current ( $I_{OUT}$ ) set by RFBN and the voltage on the FBP pin, and the switching frequency ( $F_{sw}$ ). The inductor can be chosen using the formula below:

$$L_{\text{max}} < \frac{1}{2 \times F_{\text{sw}} \times I_{\text{OUT}}} \times \left(\frac{V_{\text{IN}}}{V_{\text{OUT}}}\right)^2 \times \left(V_{\text{OUT}} - V_{\text{IN}}\right) \tag{eq. 1}$$

The minimal inductor value is determined with the desired peak current flowing through the inductor. Using the chosen inductor value the steady state duty cycle and peak inductor current can be calculated:

$$D = \frac{\sqrt{2 \times L \times F_{sw} \times I_{OUT} \times (V_{OUT} - V_{IN})}}{V_{IN}}$$

(eq. 2)

And the inductor peak current is now:

$$I_{peak} = \frac{V_{IN} \times D}{L \times F_{sw}} = \sqrt{\frac{2 \times I_{OUT} \times (V_{OUT} - V_{IN})}{L \times F_{sw}}}$$

(eq. 3)

### THE CURRENT SENSE RESISTOR

Set a current limit between 2 and 2.5 times the peak inductor current to account for inductor tolerance:

$$I_{limit} = 2.5 \times I_{peak}$$

(eq. 4)

The current limit reference fixed on the over-current protection comparator is  $V_{CS} = 0.5 \text{ V}$  and the resistance can be calculated using following the equation:

$$R_{CS} = \frac{V_{CS}}{2.5 \times I_{peak}}$$

(eq. 5)

#### SLOPE COMPENSATION

After the current sense resistor is calculated additional calculations are needed for the external slope compensation ramp. Using the R<sub>SENSE</sub> value the typical slope of the compensation ramp can be calculated:

$$Mramp = \frac{1}{2}R_{SENSE} \frac{V_{OUT} - V_{IN}}{L}$$

(eq. 6)

Using the typical value for, the external compensation resistor can be calculated as follows:

$$R_{SC} = \frac{M_{RAMP}}{I_{RAMP}}$$

(eq. 7)

The slope compensation ramp has an offset current, , which is used to calculate the peak ramp current and finally the adjusted current sense resistor.

$$I_{\text{RAMP,peak}} = I_{\text{OFF}} + D \frac{I_{\text{RAMP}}}{R_{\text{SW}}}$$

(eq. 8)

$$R_{CS} = \frac{V_{CS} - R_{CS} \times I_{RAMP,peak}}{I_{limit} + I_{RAMP,peak}}$$

(eq. 9)

#### **OUTPUT CAPACITOR and OUTPUT VOLTAGE RIPPLE**

Calculating the output voltage ripple will size the output capacitor value. The output voltage ripple equation below takes into account the parasitic impedance (ESR) of this output capacitor:

$$\Delta V_{COUT} = \frac{I_{OUT} \times (1 - D_2)}{C_{OUT} \times F_{sw}} + ESR \times I_{OUT}$$

(eq. 10)

$$\Delta V_{COUT} = \frac{I_{OUT}}{C_{OUT} \times F_{sw}} \times \left(1 - \frac{I_{peak} \times L \times F_{sw}}{V_{OUT} - V_{IN}}\right) + ESR \times I_{OUT}$$

(eq. 11)

Without taking into account the ESR, the output capacitor becomes:

$$C_{OUT} > \frac{I_{OUT}}{\Delta V_{OUT} \times F_{sw}} \times \left(1 - \frac{I_{peak} \times L \times F_{sw}}{V_{OUT} - V_{IN}}\right)$$

(eq. 12)

If the ESR value of the selected output capacitor is high, the voltage ripple will increase. The error due to the ESR can be estimated follow the equation below:

$$\Delta V_{OUTESR} = ESR \times I_{peak}$$

(eq. 13)

#### SIZING THE COMP PIN CAPACITOR

The transistor Q1 is turned ON (reset of the duty cycle) when the Vf of the output current amplifier reaches the control output voltage  $V_c$ . The control voltage  $V_c$  is simply a reduced voltage out of the follower servicing the voltage on the COMP pin. In steady state, at  $DT_{sw}$ , the voltage at the current amplifier output is represented by the equation below:

$$V_C = I_{peak} \times R_{CS} \times G_i$$

(eq. 14)

$$V_{comp} = V_C + V_{OS}$$

(eq. 15)

$V_{comp} = COMP$  pin output voltage

$V_c$  = Voltage Control of the transconductance amplifier

$V_{os}$  = voltage offset of the transconductance amplifier

$$V_{f} = \frac{V_{IN} \times D \times R_{CS} \times G_{i}}{L \times F_{SW}}$$

(eq. 16)

$$i = C \times \frac{dV}{dt} \Rightarrow C_{comp} = \frac{i_{EA} \times t_{rise}}{V_{comp}} = \frac{i_{EA} \times t_{rise}}{V_{c} + V_{os}}$$

(eq. 17)

$i_{EA} = 4 \mu A$  error amplifier output current capability

$t_{rise} = soft start time$

$V_{os} = 0.9 \text{ V}$  voltage offset due to the follower

So

$$C_{comp} < \frac{i_{EA} \times t_{rise}}{V_C + V_{OS}}$$

(eq. 18)

$$C_{comp} = 0.7 \times \frac{i_{EA} \times 30 \text{ ms}}{\frac{V_{IN} \times D \times R_{CS} \times G_L}{L \times F_{sw}} + V_{OS}}$$

(eq. 19)

During the soft start and with the dimming function activated, the COMP pin voltage is rising during 30 ms within the 100 ms soft start time so  $V_{comp}$  holds for another during 70 ms afterwards. Attention needs to be brought to the DC voltage rating. As the capacitor value decreases and the DC voltage increases, the value chosen needs to be

### SIZING THE R<sub>comp</sub> RESISTOR for the LOOP STABILITY

Combining Equations 2 and 16 gives the following expression for I<sub>OUT</sub>:

$$I_{OUT} = \frac{V_f^2 \times L \times F_{sw}}{2 \times (V_{OUT} - V_{IN}) \times (R_{CS} \times G_i)^2}$$

(eq. 20)

To obtain the small signal equation, partial derivates of the output current are calculated with respect to the control voltage Vc and the output voltage VOUT.

$$\frac{\partial}{\partial V_{\text{OUT}}} = \frac{V_{\text{C}} \times L \times F_{\text{sw}}}{\left(V_{\text{OUT}} - V_{\text{IN}}\right) \times \left(R_{\text{CS}} \times G_{i}\right)^{2}}$$

(eq. 21)

$$\frac{\partial}{\partial V_{OUT}} \frac{I_{OUT}}{V_{OUT}} = \frac{V_C \times L \times F_{sw}}{\left(V_{OUT} - V_{IN}\right) \times \left(R_{CS} \times G_i\right)^2}$$

$$\frac{\partial}{\partial V_{OUT}} = \frac{V_C^2 \times L \times F_{sw}}{2 \times \left(V_{OUT} - V_{IN}\right)^2 \times \left(R_{CS} \times G_i\right)^2} = \frac{I_{OUT}}{V_{OUT} - V_{IN}}$$

(eq. 21)

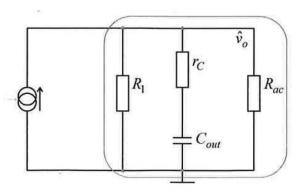

From the AC model below the control to output transfer function can be calculated:

Figure 8. Control to Output Transfer Function

$$H(s) = \frac{V_{OUT}(s)}{V_{C}(s)} = \frac{V_{OUT}(s)}{I_{(s)}} \times \frac{I_{OUT}(s)}{V_{C}(s)}$$

(eq. 23)

$$H(s) = Z_{OUT}(s) \times \frac{I_{OUT}(s)}{V_{C}(s)}$$

(eq. 24)

$$Z_{\text{OUT}}(s) = \frac{\left(\text{ESR} + \frac{1}{sC_{\text{OUT}}}\right) \times R_{\text{eq}}}{\left(\text{ESR} + \frac{1}{sC_{\text{OUT}}}\right) + R_{\text{eq}}} = R_{\text{eq}} \times \frac{1 + s \times \text{ESR} \times C_{\text{OUT}}}{1 + s \times C_{\text{OUT}}(\text{ESR} + R_{\text{eq}})}$$

(eq. 25)

Where

$$R_{eq} = \frac{R_{ac} \times R_1}{R_{ac} \times R_1}$$

$$R_1 = \frac{1}{\frac{I_{OUT}^{(s)}}{V_{OUT}^{(s)}}} = \frac{2 \times \left(V_{OUT} - V_{IN}\right)^2 \times \left(R_{cs} \times G_i\right)^2}{V_c^2 \times F_{sw} \times L} = \frac{V_{OUT} - V_{IN}}{I_{OUT}}$$

(eq. 26)

The dynamic resistance  $r_{AC(LED)}$  is evaluated using the LED specification.

$$R_{AC} = R_{sense} + r_{AC(LED)} \times nb_{LED}$$

(eq. 27)

#### Theory

The control to output transfer function is expressed following the formula below:

$$H(s) = H_0 \times \frac{1 + \frac{s}{w_z}}{1 + \frac{s}{s_p}}$$

(eq. 28)

Where

$$H_{o} = \frac{\partial I_{OUT}}{\partial V_{C}} \times R_{eq} = \frac{V_{C} \times L \times F_{sw}}{\left(V_{OUT} - V_{IN}\right) \times \left(R_{CS} \times G_{I}\right)^{2}} \times \frac{R_{AC} \times R_{1}}{R_{AC} + R_{1}}$$

(eq. 29)

$$H_{o} = \sqrt{\frac{2 \times I_{OUT} \times L \times F_{sw}}{\left(V_{OUT} - V_{IN}\right)}} \times \frac{1}{R_{CS} \times G_{i}} \times \frac{R_{AC} \times R_{1}}{R_{AC} + R_{1}}$$

(eq. 30)

$$f_{p} = \frac{1}{2\pi \times \left(\text{ESR} + R_{eq}\right) \times C_{OUT}}$$

(eq. 31)

There is also a right half plane zero:

$$f_z = \frac{1}{2\pi \times ESR \times C_{OUT}}$$

(eq. 32)

As the boost converter also operates in DCM, there is also a right half plane zero regulated to high frequency:

$$f_{\text{rhpz}} = \frac{2 \times f_{\text{sw}}}{2\pi \times D}$$

(eq. 33)

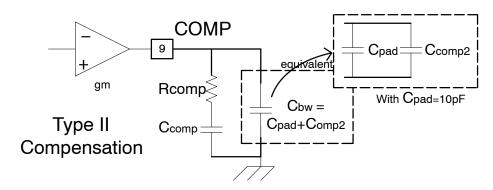

Type II compensation is used to compensate the two dominant poles  $f_p$  of the control to output transfer function. The compensator zero has to be placer at the  $f_p$  frequency of the transfer function.

$$f_p = \frac{1}{2\pi \times (\text{ESR} + R_{eq}) \times C_{OUT}} = f_z = \frac{1}{2\pi \times R_{comp} \times C_{comp}}$$

(eq. 34)

$$R_{comp} = \frac{(\text{ESR} + R_{eq}) \times C_{OUT}}{C_{comp}}$$

(eq. 35)

The dominant pole is expressed following the equation:

$$f_{p1} = \frac{1}{2\pi \times R_{FA} \times C_{comp}}$$

(eq. 36)

Figure 9. Slope Compensation Network

The natural second pole is expressed following the equation:

$$f_{p2} = \frac{1}{2\pi \times R_{comp} \times C_{bw}}$$

(eq. 37)

The zero is expressed following the equation:

$$f_z = \frac{1}{2\pi \times R_{comp} \times C_{comp}} \tag{eq. 38} \label{eq:fz}$$

#### **OSCILLATOR FREQUENCY SETTING**

The simplified equation to set the switching frequency using resistor R<sub>T</sub>:

$$f_{sw} = \frac{13750}{R_T + 5}$$

(eq. 39)

Where:

$R_T$  is expressed in  $k\Omega$ .  $f_{sw}$  us expressed in kHz

#### **FBP OPTIONS**

The FBP pin is used to program the feedback voltage that sets the LED current. Typically a resistor divider is used from VREF to set the voltage between 0.5 V and 3.0 V. Additionally, to save component costs, the feedback voltage can be programmed with internal 0.8 V ( $\pm 1.5\%$ ) by tying the FBP pin to ground.

#### **FAULT DETECTION:**

- Overvoltage Protection: A resistor divider from VOUT can be used to set the overvoltage protection on the OVP pin.

When the OVP pin rises above 1.2 V the converter will shut off immediately and PWMout will be held high for 50 ms to discharge the output capacitor. After this time the device will enter standby mode requires a high to low transition on the STBY pin to restart.

- Short Circuit Protection: A resistor divider from VOUT can be used to set the short circuit protection on the OVP pin.

When the OVP pin drops below 75 mV the converter will shut off immediately and enter standby mode. A high to low transition on the STBY pin is required to restart the device.

- Under Voltage Lockout (UVLO): The converter will immediately shut off and enter standby when the VIN pin voltage

drops below 7.5 V. When the UVLO condition is cleared, a high to low transition on the STBY pin is required to restart

the device.

- Temperature Shutdown: When the internal die temperature reaches 150°C, the device will behave the same as in the overvoltage condition.

#### **Layout Guidance**

In switching converters it is important to use wide, short traces for components in the main switching path. Resistor RCS, which is in the main switching path through transistor Q1, should be connected to power ground (PGND). Compensation network components, resistor dividers, and bypass capacitors should be referenced to quiet ground (GND). Bypass capacitors should be connected as close to the IC as possible.

### **ORDERING INFORMATION**

| Device       | Package              | Shipping <sup>†</sup> |

|--------------|----------------------|-----------------------|

| NCS29001DR2G | SOIC-14<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

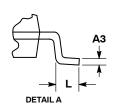

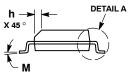

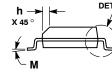

△ 0.10

SOIC-14 NB CASE 751A-03 ISSUE L

**DATE 03 FEB 2016**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994.

CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF AT

- MAXIMUM MATERIAL CONDITION.

DIMENSIONS D AND E DO NOT INCLUDE MOLD PROTRUSIONS.

- MAXIMUM MOLD PROTRUSION 0.15 PER SIDE

|     | MILLIN | IETERS | INC   | HES   |

|-----|--------|--------|-------|-------|

| DIM | MIN    | MAX    | MIN   | MAX   |

| Α   | 1.35   | 1.75   | 0.054 | 0.068 |

| A1  | 0.10   | 0.25   | 0.004 | 0.010 |

| АЗ  | 0.19   | 0.25   | 0.008 | 0.010 |

| b   | 0.35   | 0.49   | 0.014 | 0.019 |

| D   | 8.55   | 8.75   | 0.337 | 0.344 |

| Е   | 3.80   | 4.00   | 0.150 | 0.157 |

| е   | 1.27   | BSC    | 0.050 | BSC   |

| Н   | 5.80   | 6.20   | 0.228 | 0.244 |

| h   | 0.25   | 0.50   | 0.010 | 0.019 |

| Ĺ   | 0.40   | 1.25   | 0.016 | 0.049 |

| М   | 0 °    | 7°     | 0 °   | 7°    |

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code Α = Assembly Location

WL = Wafer Lot Υ = Year WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

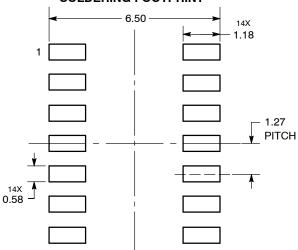

# **SOLDERING FOOTPRINT\***

DIMENSIONS: MILLIMETERS

C SEATING PLANE

### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42565B | Electronic versions are uncontrolled except when accessed directly from the Document Repositor Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-14 NB  |                                                                                                                                                                                | PAGE 1 OF 2 |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### SOIC-14 CASE 751A-03 ISSUE L

### DATE 03 FEB 2016

| STYLE 1: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. NO CONNECTION 5. ANODE/CATHODE 6. NO CONNECTION 7. ANODE/CATHODE 8. ANODE/CATHODE 9. ANODE/CATHODE 10. NO CONNECTION 11. ANODE/CATHODE 12. ANODE/CATHODE 13. NO CONNECTION 14. COMMON ANODE | STYLE 2:<br>CANCELLED                                                                                                                                         | STYLE 3: PIN 1. NO CONNECTION 2. ANODE 3. ANODE 4. NO CONNECTION 5. ANODE 6. NO CONNECTION 7. ANODE 8. ANODE 9. ANODE 10. NO CONNECTION 11. ANODE 12. ANODE 13. NO CONNECTION 14. COMMON CATHODE                                                                | STYLE 4: PIN 1. NO CONNECTION 2. CATHODE 3. CATHODE 4. NO CONNECTION 5. CATHODE 6. NO CONNECTION 7. CATHODE 8. CATHODE 9. CATHODE 10. NO CONNECTION 11. CATHODE 12. CATHODE 13. NO CONNECTION 14. COMMON ANODE                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE 6. NO CONNECTION 7. COMMON ANODE 8. COMMON CATHODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. ANODE/CATHODE 12. ANODE/CATHODE 13. NO CONNECTION 14. COMMON ANODE | STYLE 6: PIN 1. CATHODE 2. CATHODE 3. CATHODE 4. CATHODE 5. CATHODE 6. CATHODE 7. CATHODE 8. ANODE 9. ANODE 10. ANODE 11. ANODE 12. ANODE 13. ANODE 14. ANODE | STYLE 7: PIN 1. ANODE/CATHODE 2. COMMON ANODE 3. COMMON CATHODE 4. ANODE/CATHODE 5. ANODE/CATHODE 6. ANODE/CATHODE 7. ANODE/CATHODE 8. ANODE/CATHODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. COMMON CATHODE 12. COMMON ANODE 13. ANODE/CATHODE 14. ANODE/CATHODE | STYLE 8: PIN 1. COMMON CATHODE 2. ANODE/CATHODE 3. ANODE/CATHODE 4. NO CONNECTION 5. ANODE/CATHODE 6. ANODE/CATHODE 7. COMMON ANODE 8. COMMON ANODE 9. ANODE/CATHODE 10. ANODE/CATHODE 11. NO CONNECTION 12. ANODE/CATHODE 13. ANODE/CATHODE 14. COMMON CATHODE |

| DOCUMENT NUMBER: | 98ASB42565B | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DESCRIPTION:     | SOIC-14 NB  |                                                                                                                                                                                     | PAGE 2 OF 2 |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, Onsemi, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA class 3 medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase

#### ADDITIONAL INFORMATION

TECHNICAL PUBLICATIONS:

$\textbf{Technical Library:} \ \underline{www.onsemi.com/design/resources/technical-documentation}$

onsemi Website: www.onsemi.com

ONLINE SUPPORT: www.onsemi.com/support

For additional information, please contact your local Sales Representative at www.onsemi.com/support/sales