# High Speed Single-Ended PWM Controller

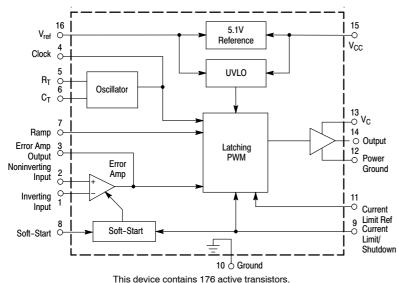

The MC34023 series are high speed, fixed frequency, single-ended pulse width modulator controllers optimized for high frequency operation. They are specifically designed for Off-Line and DC-to-DC converter applications offering the designer a cost-effective solution with minimal external components. These integrated circuits feature an oscillator, a temperature compensated reference, a wide bandwidth error amplifier, a high speed current sensing comparator, and a high current totem pole output ideally suited for driving a power MOSFET.

Also included are protective features consisting of input and reference undervoltage lockouts each with hysteresis, cycle-by-cycle current limiting, and a latch for single pulse metering.

The flexibility of this series allows it to be easily configured for either current mode or voltage mode control.

#### **Features**

- 50 ns Propagation Delay to Output

- High Current Totem Pole Output

- Wide Bandwidth Error Amplifier

- Fully-Latched Logic with Double Pulse Suppression

- Latching PWM for Cycle-By-Cycle Current Limiting

- Soft-Start Control with Latched Overcurrent Reset

- Input Undervoltage Lockout with Hysteresis

- Low Startup Current (500 μA Typ)

- Internally Trimmed Reference with Undervoltage Lockout

- 90% Maximum Duty Cycle (Externally Adjustable)

- Precision Trimmed Oscillator

- Voltage or Current Mode Operation to 1.0 MHz

- Functionally Similar to the UC3823

- These are Pb-Free Devices

This device contains 1/6 active transistors

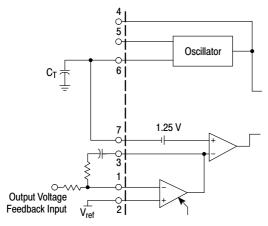

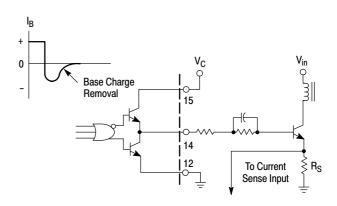

Figure 1. Simplified Application

## ON Semiconductor®

http://onsemi.com

PDIP-16 P SUFFIX CASE 648

SOIC-16W DW SUFFIX CASE 751G

#### MARKING DIAGRAMS

A = Assembly Location

WL = Wafer Lot

YY = Year

WW = Work Week

G = Pb-Free Package

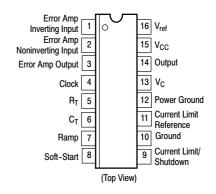

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **ORDERING INFORMATION**

| Device       | Package               | Shipping <sup>†</sup> |

|--------------|-----------------------|-----------------------|

| MC33023DWG   | SOIC-16W<br>(Pb-Free) | 47 Units / Rail       |

| MC33023DWR2G | SOIC-16W<br>(Pb-Free) | 1000 Units / Reel     |

| MC34023PG    | PDIP-16<br>(Pb-Free)  | 25 Units / Rail       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

## **MAXIMUM RATINGS**

| Rating                                                                                                                                                                                                                                                                        | Symbol                                                                   | Value                     | Unit                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------|-------------------------|

| Power Supply Voltage                                                                                                                                                                                                                                                          | V <sub>CC</sub>                                                          | 30                        | V                       |

| Output Driver Supply Voltage                                                                                                                                                                                                                                                  | V <sub>C</sub>                                                           | 20                        | V                       |

| Output Current, Source or Sink (Note 1) DC Pulsed (0.5 μs)                                                                                                                                                                                                                    | lo                                                                       | 0.5<br>2.0                | А                       |

| Current Sense, Soft-Start, Ramp, and Error Amp Inputs                                                                                                                                                                                                                         | V <sub>in</sub>                                                          | -0.3 to +7.0              | V                       |

| Error Amp Output and Soft-Start Sink Current                                                                                                                                                                                                                                  | I <sub>O</sub>                                                           | 10                        | mA                      |

| Clock and R <sub>T</sub> Output Current                                                                                                                                                                                                                                       | I <sub>CO</sub>                                                          | 5.0                       | mA                      |

| Power Dissipation and Thermal Characteristics SO-16L Package (Case 751G) Maximum Power Dissipation @ T <sub>A</sub> = +25°C Thermal Resistance, Junction-to-Air DIP Package (Case 648) Maximum Power Dissipation @ T <sub>A</sub> = +25°C Thermal Resistance, Junction-to-Air | P <sub>D</sub><br>R <sub>θJA</sub><br>P <sub>D</sub><br>R <sub>θJA</sub> | 862<br>145<br>1.25<br>100 | mW<br>°C/W<br>W<br>°C/W |

| Operating Junction Temperature                                                                                                                                                                                                                                                | TJ                                                                       | +150                      | °C                      |

| Operating Ambient Temperature (Note 2) MC34023 MC33023                                                                                                                                                                                                                        | T <sub>A</sub>                                                           | 0 to +70<br>-40 to +105   | °C                      |

| Storage Temperature Range                                                                                                                                                                                                                                                     | T <sub>stg</sub>                                                         | -55 to +150               | °C                      |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 15 V,  $R_T$  = 3.65 k $\Omega$ ,  $C_T$  = 1.0 nF, for typical values  $T_A$  = +25°C, for min/max values  $T_A$ is the operating ambient temperature range that applies [Note 2], unless otherwise noted.)

| Characteristic                                                                                                                     | Symbol                                     | Min        | Тур         | Max        | Unit  |

|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------|-------------|------------|-------|

| REFERENCE SECTION                                                                                                                  | · · · · · · · · · · · · · · · · · · ·      |            | •           | •          | •     |

| Reference Output Voltage (I <sub>O</sub> = 1.0 mA, T <sub>J</sub> = +25°C)                                                         | $V_{ref}$                                  | 5.05       | 5.1         | 5.15       | V     |

| Line Regulation (V <sub>CC</sub> = 10 V to 30 V)                                                                                   | Reg <sub>line</sub>                        | -          | 2.0         | 15         | mV    |

| Load Regulation (I <sub>O</sub> = 1.0 mA to 10 mA)                                                                                 | Reg <sub>load</sub>                        | 1          | 2.0         | 15         | mV    |

| Temperature Stability                                                                                                              | T <sub>S</sub>                             | -          | 0.2         | -          | mV/°C |

| Total Output Variation over Line, Load, and Temperature                                                                            | $V_{ref}$                                  | 4.95       | -           | 5.25       | V     |

| Output Noise Voltage (f = 10 Hz to 10 kHz, T <sub>J</sub> = +25°C)                                                                 | V <sub>n</sub>                             | -          | 50          | -          | μV    |

| Long Term Stability (T <sub>A</sub> = +125°C for 1000 Hours)                                                                       | S                                          | -          | 5.0         | -          | mV    |

| Output Short Circuit Current                                                                                                       | I <sub>SC</sub>                            | - 30       | - 65        | -100       | mA    |

| OSCILLATOR SECTION                                                                                                                 | <u>.</u>                                   |            |             |            |       |

| Frequency $T_J = +25^{\circ}C$ Line ( $V_{CC} = 10 \text{ V to } 30 \text{ V}$ ) and Temperature ( $T_A = T_{low}$ to $T_{high}$ ) | f <sub>osc</sub>                           | 380<br>370 | 400<br>400  | 420<br>430 | kHz   |

| Frequency Change with Voltage (V <sub>CC</sub> = 10 V to 30 V)                                                                     | $\Delta f_{\sf OSC}/\Delta V$              | -          | 0.2         | 1.0        | %     |

| Frequency Change with Temperature $(T_A = T_{low} \text{ to } T_{high})$                                                           | $\Delta f_{osc}/\Delta T$                  | -          | 2.0         | -          | %     |

| Sawtooth Peak Voltage                                                                                                              | V <sub>OSC(P)</sub>                        | 2.6        | 2.8         | 3.0        | V     |

| Sawtooth Valley Voltage                                                                                                            | V <sub>OSC(V)</sub>                        | 0.7        | 1.0         | 1.25       | V     |

| Clock Output Voltage<br>High State<br>Low State                                                                                    | V <sub>OH</sub><br>V <sub>OL</sub>         | 3.9<br>-   | 4.5<br>2.3  | -<br>2.9   | V     |

| ERROR AMPLIFIER SECTION                                                                                                            |                                            |            |             |            |       |

| Input Offset Voltage                                                                                                               | V <sub>IO</sub>                            | -          | -           | 15         | mV    |

| Input Bias Current                                                                                                                 | I <sub>IB</sub>                            | -          | 0.6         | 3.0        | μΑ    |

| Input Offset Current                                                                                                               | I <sub>IO</sub>                            | -          | 0.1         | 1.0        | μΑ    |

| Open-Loop Voltage Gain ( $V_0 = 1.0 \text{ V}$ to $4.0 \text{ V}$ )                                                                | A <sub>VOL</sub>                           | 60         | 95          | _          | dB    |

| Gain Bandwidth Product ( $T_J = +25^{\circ}C$ )                                                                                    | GBW                                        | 4.0        | 8.3         | _          | MHz   |

| Common Mode Rejection Ratio (V <sub>CM</sub> = 1.5 V to 5.5 V)                                                                     | CMRR                                       | 75         | 95          | _          | dB    |

| Power Supply Rejection Ratio (V <sub>CC</sub> = 10 V to 30 V)                                                                      | PSRR                                       | 85         | 110         | -          | dB    |

| Output Current, Source ( $V_O = 4.0 \text{ V}$ )<br>Sink ( $V_O = 1.0 \text{ V}$ )                                                 | I <sub>Source</sub><br>I <sub>Sink</sub>   | 0.5<br>1.0 | 3.0<br>3.6  | _<br>_     | mA    |

| Output Voltage Swing, High State ( $I_O = -0.5 \text{ mA}$ )<br>Low State ( $I_O = 1 \text{ mA}$ )                                 | V <sub>OH</sub><br>V <sub>OL</sub>         | 4.5<br>0   | 4.75<br>0.4 | 5.0<br>1.0 | V     |

| Slew Rate                                                                                                                          | SR                                         | 6.0        | 12          | -          | V/μs  |

| PWM COMPARATOR SECTION                                                                                                             |                                            |            |             |            |       |

| Ramp Input Bias Current                                                                                                            | I <sub>IB</sub>                            | -          | -0.5        | -5.0       | μΑ    |

| Duty Cycle, Maximum<br>Minimum                                                                                                     | DC <sub>(max)</sub><br>DC <sub>(min)</sub> | 80<br>-    | 90<br>-     | _<br>0     | %     |

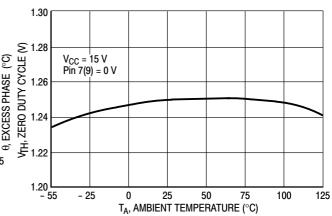

| Zero Duty Cycle Threshold Voltage Pin 3(4) (Pin 7(9) = 0 V)                                                                        | V <sub>th</sub>                            | 1.1        | 1.25        | 1.4        | V     |

| Propagation Delay (Ramp Input to Output, T <sub>J</sub> = +25°C)                                                                   | t <sub>PLH(in/out)</sub>                   | 1          | 60          | 100        | ns    |

| SOFT-START SECTION                                                                                                                 | <u>.</u>                                   |            |             |            |       |

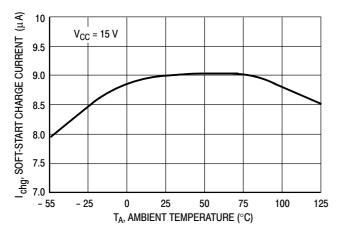

| Charge Current (V <sub>Soft-Start</sub> = 0.5 V)                                                                                   | I <sub>chg</sub>                           | 3.0        | 9.0         | 20         | μΑ    |

| Discharge Current (V <sub>Soft-Start</sub> = 1.5 V)                                                                                | I <sub>dischg</sub>                        | 1.0        | 4.0         | -          | mA    |

|                                                                                                                                    |                                            |            |             |            |       |

Maximum package power dissipation limits must be observed.

Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.

T<sub>low</sub> = 0°C for MC34023

= -40°C for MC33023

Thigh = +70°C for MC34023

= +105°C for MC33023

**ELECTRICAL CHARACTERISTICS** ( $V_{CC}$  = 15 V,  $R_T$  = 3.65 k $\Omega$ ,  $C_T$  = 1.0 nF, for typical values  $T_A$  = +25°C, for min/max values  $T_A$  is the operating ambient temperature range that applies [Note 3], unless otherwise noted.)

| Characteristic                                                                                                                                            | Symbol                             | Min                | Тур                       | Max                  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|---------------------------|----------------------|------|

| CURRENT SENSE SECTION                                                                                                                                     |                                    | •                  | •                         | •                    |      |

| Input Bias Current (Pin 9(12) = 0 V to 4.0 V)                                                                                                             | I <sub>IB</sub>                    | _                  | _                         | 15                   | μΑ   |

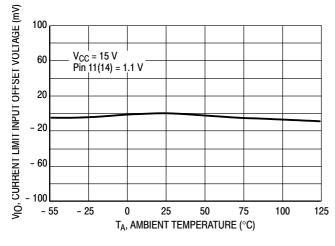

| Current Limit Comparator Input Offset Voltage (Pin 11(14) = 1.1 V)                                                                                        | V <sub>IO</sub>                    | -                  | _                         | 45                   | mV   |

| Current Limit Reference Input Common Mode Range (Pin 11(14)) T <sub>J</sub> = +25°C                                                                       | V <sub>CMR</sub>                   | 1.0                | -                         | 3.0                  | V    |

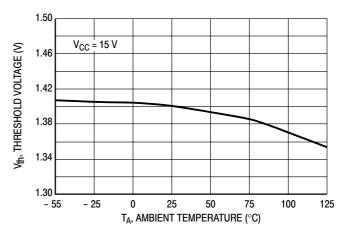

| Shutdown Comparator Threshold                                                                                                                             | V <sub>th</sub>                    | 1.25               | 1.40                      | 1.55                 | V    |

| Propagation Delay (Current Limit/Shutdown to Output, T <sub>J</sub> = +25°C)                                                                              | t <sub>PLH(in/out)</sub>           | -                  | 50                        | 80                   | ns   |

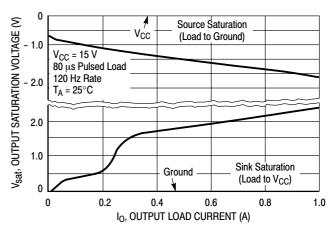

| OUTPUT SECTION                                                                                                                                            |                                    |                    |                           |                      |      |

| Output Voltage Low State (I <sub>Sink</sub> = 20 mA) (I <sub>Sink</sub> = 200 mA) High State (I <sub>Source</sub> = 20 mA) (I <sub>Source</sub> = 200 mA) | V <sub>OL</sub><br>V <sub>OH</sub> | -<br>-<br>13<br>12 | 0.25<br>1.2<br>13.5<br>13 | 0.4<br>2.2<br>-<br>- | V    |

| Output Voltage with UVLO Activated (V <sub>CC</sub> = 6.0 V, I <sub>Sink</sub> = 0.5 mA)                                                                  | V <sub>OL(UVLO)</sub>              | _                  | 0.25                      | 1.0                  | ٧    |

| Output Leakage Current (V <sub>C</sub> = 20 V)                                                                                                            | ΙL                                 | -                  | 100                       | 500                  | μΑ   |

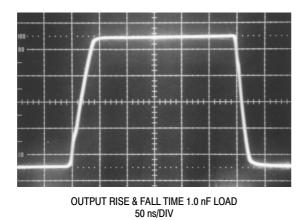

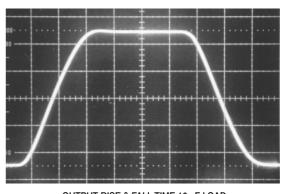

| Output Voltage Rise Time (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = +25°C)                                                                                | t <sub>r</sub>                     | -                  | 30                        | 60                   | ns   |

| Output Voltage Fall Time (C <sub>L</sub> = 1.0 nF, T <sub>J</sub> = +25°C)                                                                                | t <sub>f</sub>                     | -                  | 30                        | 60                   | ns   |

| UNDERVOLTAGE LOCKOUT SECTION                                                                                                                              |                                    |                    |                           |                      |      |

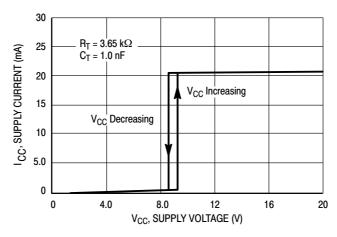

| Startup Threshold (V <sub>CC</sub> Increasing)                                                                                                            | V <sub>th(on)</sub>                | 8.8                | 9.2                       | 9.6                  | V    |

| UVLO Hysteresis Voltage (V <sub>CC</sub> Decreasing After Turn-On)                                                                                        | V <sub>H</sub>                     | 0.4                | 0.8                       | 1.2                  | V    |

| TOTAL DEVICE                                                                                                                                              |                                    | ÷.                 | -                         |                      |      |

| Power Supply Current Startup (VCC = 8.0 V) Operating                                                                                                      | I <sub>CC</sub>                    | _<br>_             | 0.5<br>20                 | 1.2<br>30            | mA   |

<sup>3.</sup> Low duty cycle pulse techniques are used during test to maintain junction temperature as close to ambient as possible.  $T_{low} = 0^{\circ}\text{C for MC34023} \qquad T_{high} = +70^{\circ}\text{C for MC34023} \\ = -40^{\circ}\text{C for MC33023} \qquad = +105^{\circ}\text{C for MC33023}$

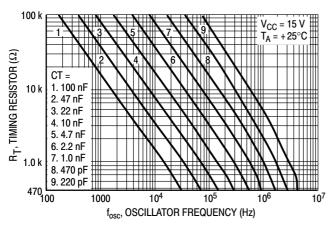

Figure 2. Timing Resistor versus Oscillator Frequency

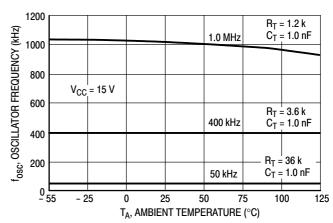

Figure 3. Oscillator Frequency versus Temperature

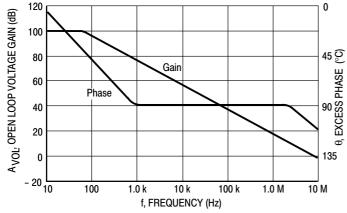

Figure 4. Error Amp Open Loop Gain and Phase versus Frequency

Figure 5. PWM Comparator Zero Duty Cycle Threshold Voltage versus Temperature

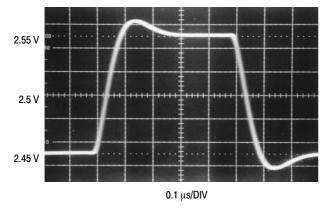

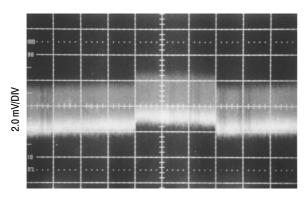

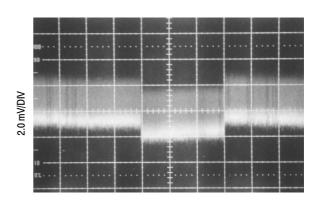

Figure 6. Error Amp Small Signal Transient Response

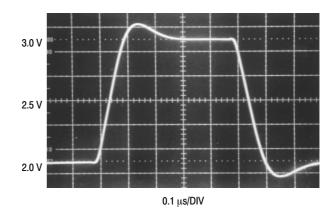

Figure 7. Error Amp Large Signal Transient Response

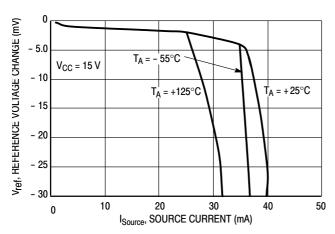

Figure 8. Reference Voltage Change versus Source Current

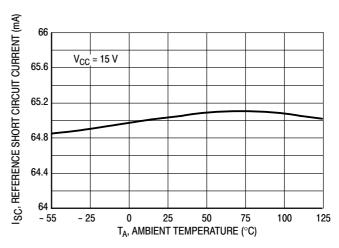

Figure 9. Reference Short Circuit Current versus Temperature

V<sub>ref</sub> LINE REGULATION 10 V to 24 V (2.0 ms/DIV)

V<sub>ref</sub> LOAD REGULATION 1.0 mA to 10 mA (2.0 ms/DIV)

Figure 10. Reference Line Regulation

Figure 12. Current Limit Comparator Input Offset Voltage versus Temperature

Figure 13. Shutdown Comparator Threshold Voltage versus Temperature

Figure 14. Soft-Start Charge Current versus Temperature

Figure 15. Output Saturation Voltage versus Load Current

Figure 16. Drive Output Rise and Fall Time

OUTPUT RISE & FALL TIME 10 nF LOAD 50 ns/DIV

Figure 17. Drive Output Rise and Fall Time

Figure 18. Supply Voltage versus Supply Current

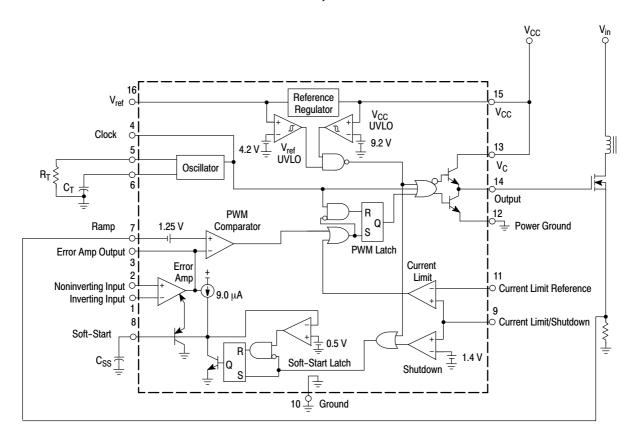

Figure 19. Representative Block Diagram

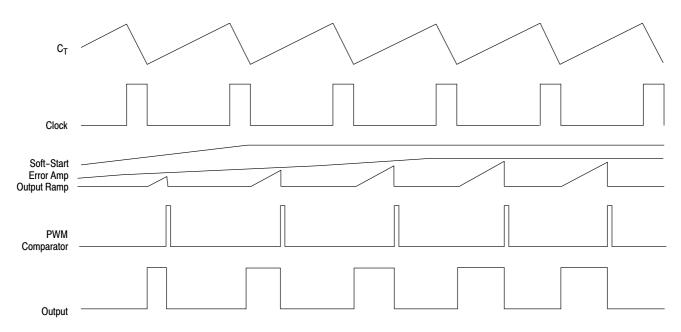

Figure 20. Current Limit Operating Waveforms

#### **OPERATING DESCRIPTION**

The MC33023 and MC34023 series are high speed, fixed frequency, single-ended pulse width modulator controllers optimized for high frequency operation. They are specifically designed for Off-Line and DC-to-DC converter applications offering the designer a cost effective solution with minimal external components. A representative block diagram is shown in Figure 19.

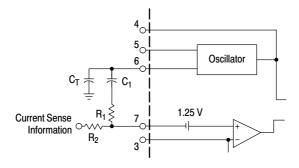

#### Oscillator

The oscillator frequency is programmed by the values selected for the timing components  $R_T$  and  $C_T$ . The  $R_T$  pin is set to a temperature compensated 3.0 V. By selecting the value of  $R_T$ , the charge current is set through a current mirror for the timing capacitor  $C_T$ . This charge current is ratioed to be 10 times the charge current, which yields the maximum duty cycle of 90%.  $C_T$  is charged to 2.8 V and discharged to 1.0 V. During the discharge of  $C_T$ , the oscillator generates an internal blanking pulse that resets the PWM Latch and, inhibits the outputs. The threshold voltage on the oscillator comparator is trimmed to guarantee an oscillator accuracy of 5.0% at 25°C.

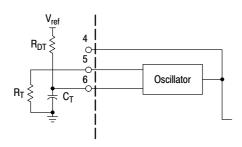

Additional dead time can be added by externally increasing the charge current to  $C_T$  as shown in Figure 24. This changes the charge to discharge ratio of  $C_T$  which is set internally to  $I_{charge}/10\ I_{charge}$ . The new charge to discharge ratio will be:

% Deadtime =

$$\frac{I_{additional} + I_{charge}}{10 (I_{charge})}$$

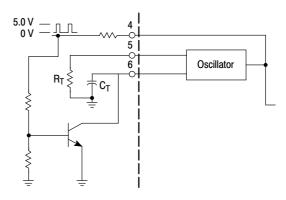

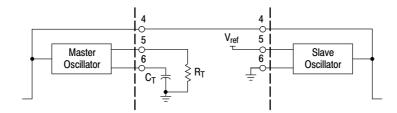

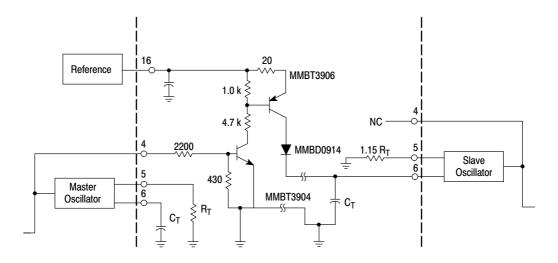

A bidirectional clock pin is provided for synchronization or for master/slave operation. As a master, the clock pin provides a positive output pulse during the discharge of  $C_T$ . As a slave, the clock pin is an input that resets the PWM latch and blanks the drive output, but does not discharge  $C_T$ . Therefore, the oscillator is not synchronized by driving the clock pin alone. Figures 28, 29 and 30 provide suggested synchronization.

#### **Error Amplifier**

A fully compensated Error Amplifier is provided. It features a typical DC voltage gain of 95 dB and a gain bandwidth product of 8.3 MHz with 75 degrees of phase margin (Figure 4). Typical application circuits will have the noninverting input tied to the reference. The inverting input will typically be connected to a feedback voltage generated from the output of the switching power supply. Both inputs have a common mode voltage ( $V_{\rm CM}$ ) input range of 1.5 V to 5.5 V. The Error Amplifier Output is provided for external loop compensation.

#### Soft-Start Latch

Soft-Start is accomplished in conjunction with an external capacitor. The Soft-Start capacitor is charged by an internal 9.0  $\mu$ A current source. This capacitor clamps the

output of the error amplifier to less than its normal output voltage, thus limiting the duty cycle. The time it takes for a capacitor to reach full charge is given by:

$$t \approx (4.5 \bullet 10^5) C_{Soft-Start}$$

A Soft–Start latch is incorporated to prevent erratic operation of this circuitry. Two conditions can cause the Soft–Start circuit to latch so that the Soft–Start capacitor stays discharged. The first condition is activation of an undervoltage lockout of either  $V_{CC}$  or  $V_{ref}$ . The second condition is when current sense input exceeds 1.4 V. Since this latch is "set dominant", it cannot be reset until either of these signals is removed and, the voltage at  $C_{Soft–Start}$  is less than 0.5 V.

#### **PWM Comparator and Latch**

A PWM circuit typically compares an error voltage with a ramp signal. The outcome of this comparison determines the state of the output. In voltage mode operation the ramp signal is the voltage ramp of the timing capacitor. In current mode operation the ramp signal is the voltage ramp induced in a current sensing element. The ramp input of the PWM comparator is pinned out so that the user can decide which mode of operation best suits the application requirements. The ramp input has a 1.25 V offset such that whenever the voltage at this pin exceeds the error amplifier output voltage minus 1.25 V, the PWM comparator will cause the PWM latch to set, disabling the outputs. Once the PWM latch is set, only a blanking pulse by the oscillator can reset it, thus initiating the next cycle.

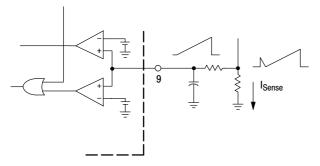

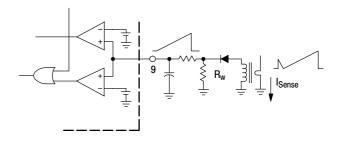

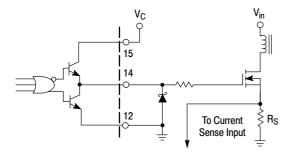

## **Current Limiting and Shutdown**

A pin is provided to perform current limiting and shutdown operations. Two comparators are connected to the input of this pin. The reference voltage for the current limit comparator is not set internally. A pin is provided so the user can set the voltage. When the voltage at the current limit input pin exceeds the externally set voltage, the PWM latch is set, disabling the output. In this way cycle-by-cycle current limiting is accomplished. If a current limit resistor is used in series with the power devices, the value of the resistor is found by:

$$R_{Sense} = \frac{I_{Limit Reference Voltage}}{I_{pk (switch)}}$$

If the voltage at this pin exceeds 1.4 V, the second comparator is activated. This comparator sets a latch which, in turn, causes the soft start capacitor to be discharged. In this way a "hiccup" mode of recovery is possible in the case of output short circuits. If a current limit resistor is used in series with the output devices, the peak current at which the controller will enter a "hiccup" mode is given by:

$$I_{\text{Shutdown}} = \frac{1.4 \text{ V}}{R_{\text{Sense}}}$$

In certain applications, it may be desirable to disable the current limit comparator. This can be accomplished by biasing pin 11 to a level greater than 1.4 V but less than 3.0 V. Under these conditions, the shutdown comparator and soft-start latch are activated during an overcurrent event causing the converter to enter an hiccup mode.

#### **Undervoltage Lockout**

There are two undervoltage lockout circuits within the IC. The first senses  $V_{CC}$  and the second  $V_{ref}$ . During power-up, V<sub>CC</sub> must exceed 9.2 V and V<sub>ref</sub> must exceed 4.2 V before the outputs can be enabled and the Soft-Start latch released. If  $V_{CC}$  falls below 8.4 V or  $V_{ref}$  falls below 3.6 V, the outputs are disabled and the Soft-Start latch is activated. When the UVLO is active, the part is in a low current standby mode allowing the IC to have an off-line bootstrap startup circuit. Typical startup current is 500 μA.

#### Output

The MC34023 has a high current totem pole output specifically designed for direct drive of power MOSFETs. It is capable of up to  $\pm$  2.0 A peak drive current with a typical rise and fall time of 30 ns driving a 1.0 nF load.

Separate pins for V<sub>C</sub> and Power Ground are provided. With proper implementation, a significant reduction of switching transient noise imposed on the control circuitry is possible. The separate V<sub>C</sub> supply input also allows the designer added flexibility in tailoring the drive voltage independent of V<sub>CC</sub>.

#### Reference

A 5.1 V bandgap reference is pinned out and is trimmed to an initial accuracy of ±1.0% at 25°C. This reference has short circuit protection and can source in excess of 10 mA for powering additional control system circuitry.

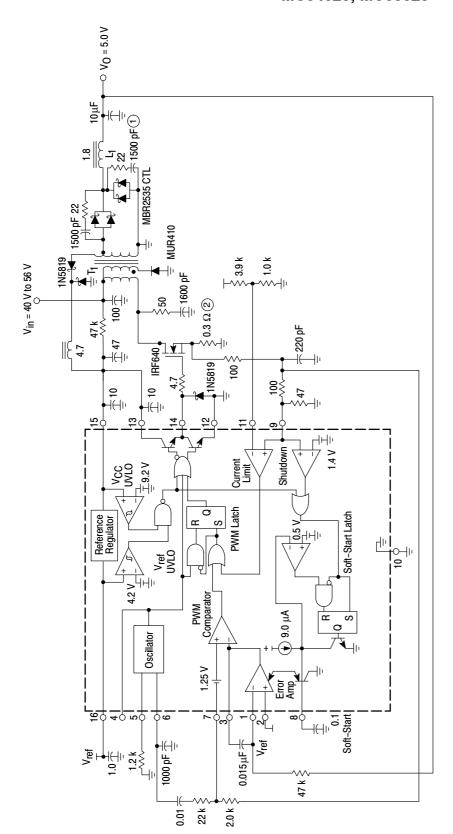

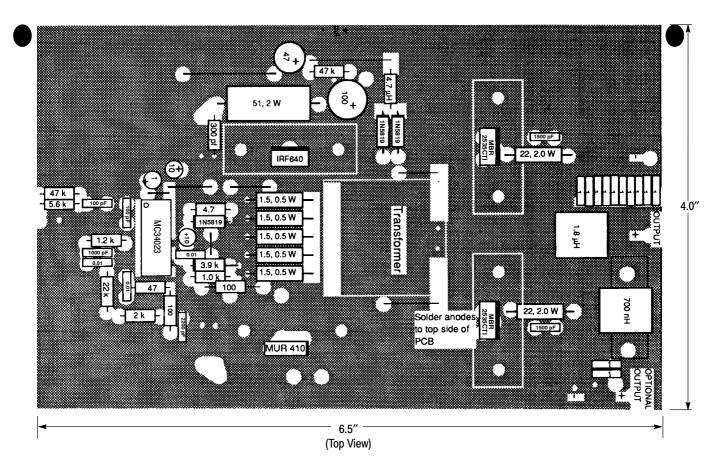

#### **Design Considerations**

Do not attempt to construct the converter on wire-wrap or plug-in prototype boards. With high frequency, high power, switching power supplies it is imperative to have separate current loops for the signal paths and for the power paths. The printed circuit layout should contain a ground plane with low current signal and high current switch and output grounds returning on separate paths back to the input filter capacitor. Shown in Figure 36 is a printed circuit layout of the application circuit. Note how the power and ground traces are run. All bypass capacitors and snubbers should be connected as close as possible to the specific part in question. The PC board lead lengths must be less than 0.5 inches for effective bypassing for snubbing.

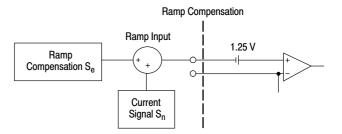

#### Instabilities

In current mode control, an instability can be encountered at any given duty cycle. The instability is caused by the current feedback loop. It has been shown that the instability is caused by a double pole at half the switching frequency. If an external ramp  $(S_e)$  is added to the on-time ramp  $(S_n)$ of the current-sense waveform, stability can be achieved.

One must be careful not to add too much ramp compensation. If too much is added the system will start to perform like a voltage mode regulator. All benefits of current mode control will be lost. Figure 26 is an example of one way in which external ramp compensation can be implemented.

Figure 21. Ramp Compensation

A simple equation can be used to calculate the amount of external ramp slope necessary to add that will achieve stability in the current loop. For the following equations, the calculated values for the application circuit in Figure 35 are also shown.

$$S_{e} = \frac{V_{O}}{L} \left( \frac{N_{S}}{N_{P}} \right) (R_{S}) A_{i}$$

V<sub>O</sub> = DC output voltage

$N_P$ ,  $N_S$  = number of power transformer primary or secondary turns

$A_i$  = gain of the current sense network (see Figures 24 and 25)

L = output inductor

R<sub>S</sub> = current sense resistance

For the application circuit:

$$S_e = \frac{5}{1.8 \,\mu} \left(\frac{2}{8}\right) (0.3) (0.55)$$

= 0.115 V/ms

## PIN FUNCTION DESCRIPTION

| Pin      |                                    |                                                                                                                                                                                                                                        |

|----------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP/SOIC | Function                           | Description                                                                                                                                                                                                                            |

| 1        | Error Amp<br>Inverting Input       | This pin is usually used for feedback from the output of the power supply.                                                                                                                                                             |

| 2        | Error Amp<br>Noninverting<br>Input | This pin is used to provide a reference in which an error signal can be produced on the output of the error amp. Usually this is connected to $V_{ref}$ , however an external reference can also be used.                              |

| 3        | Error Amp<br>Output                | This pin is provided for compensating the error amp for poles and zeros encountered in the power supply system, mostly the output LC filter.                                                                                           |

| 4        | Clock                              | This is a bidirectional pin used for synchronization.                                                                                                                                                                                  |

| 5        | R <sub>T</sub>                     | The value of $R_T$ sets the charge current through timing Capacitor, $C_T$ .                                                                                                                                                           |

| 6        | C <sub>T</sub>                     | In conjunction with R <sub>T</sub> , the timing Capacitor sets the switching frequency.                                                                                                                                                |

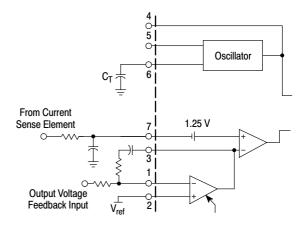

| 7        | Ramp Input                         | For voltage mode operation this pin is connected to C <sub>T</sub> . For current mode operation this pin is connected through a filter to the current sensing element.                                                                 |

| 8        | Soft-Start                         | A capacitor at this pin sets the Soft–Start time.                                                                                                                                                                                      |

| 9        | Current Limit/<br>Shutdown         | This pin has two functions. First, it provides cycle-by-cycle current limiting. Second, if the current is excessive, this pin will reinitiate a Soft-Start cycle.                                                                      |

| 10       | Ground                             | This pin is the ground for the control circuitry.                                                                                                                                                                                      |

| 11       | Current Limit<br>Reference Input   | This pin voltage sets the threshold for cycle-by-cycle current limiting.                                                                                                                                                               |

| 12       | Power Ground                       | This is a separate power ground return that is connected back to the power source. It is used to reduce the effects of switching transient noise on the control circuitry.                                                             |

| 13       | V <sub>C</sub>                     | This is a separate power source connection for the outputs that is connected back to the power source input. With a separate power source connection, it can reduce the effects of switching transient noise on the control circuitry. |

| 14       | Output                             | This is a high current totem pole output.                                                                                                                                                                                              |

| 15       | V <sub>CC</sub>                    | This pin is the positive supply of the control IC.                                                                                                                                                                                     |

| 16       | V <sub>ref</sub>                   | This is a 5.1 V reference. It is usually connected to the noninverting input of the error amplifier.                                                                                                                                   |

In voltage mode operation, the control range on the output of the Error Amplifier from 0% to 90% duty cycle is from 2.25 V to 4.05 V.

Figure 22. Voltage Mode Operation

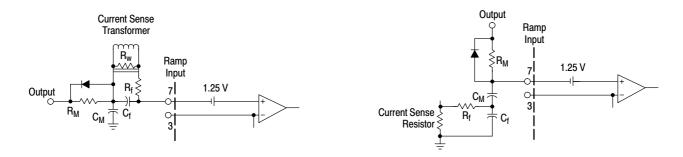

In current mode control, an RC filter should be placed at the ramp input to filter the leading edge spike caused by turn-on of a power MOSFET.

Figure 23. Current Mode Operation

The addition of an RC filter will eliminate instability caused by the leading edge spike on the current waveform. This sense signal can also be used at the ramp input pin for current mode control. For ramp compensation it is necessary to know the gain of the current feedback loop. If a transformer is used, the gain can be calculated by:

$$A_i = \frac{R_{Sense}}{turns ratio}$$

Figure 24. Resistive Current Sensing

The addition of an RC filter will eliminate instability caused by the leading edge spike on the current waveform. This sense signal can also be used at the ramp input pin for current mode control. For ramp compensation it is necessary to know the gain of the current feedback loop. The gain can be calculated by:

$$A_{i} = \frac{R_{w}}{turns\ ratio}$$

Figure 25. Primary Side Current Sensing

This method of slope compensation is easy to implement, however, it is noise sensitive. Capacitor  $C_1$  provides AC coupling. The oscillator signal is added to the current signal by a voltage divider consisting of resistors  $R_1$  and  $R_2$ .

Figure 26A. Slope Compensation (Noise Sensitive)

When only one output is used, this method of slope compensation can be used and it is relatively noise immune. Resistor  $R_M$  and capacitor  $C_M$  provide the added slope necessary. By choosing  $R_M$  and  $C_M$  with a larger time constant than the switching frequency, you can assume that its charge is linear. First choose  $C_M$ , then  $R_M$  can be adjusted to achieve the required slope. The diode provides a reset pulse at the ramp input at the end of every cycle. The charge current  $I_M$  can be calculated by  $I_M = V_M S_e$ . Then  $I_M$  can be calculated by  $I_M = V_C C/I_M$ .

Figure 26B. Slope Compensation (Noise Immune)

Additional dead time can be added by the addition of a dead time resistor from  $V_{\text{ref}}$  to  $C_{\text{T}}.$  See text on Oscillator section for more information.

Figure 27. Dead Time Addition

The sync pulse fed into the clock pin must be at least 3.9 V.  $R_{T}$  and  $C_{T}$  need to be set 10% slower than the sync frequency. This circuit is also used in Voltage Mode operation for master/slave operation. The clock signal would be coming from the master which is set at the desired operating frequency, while the slave is set 10% slower.

Figure 28. External Clock Synchronization

Figure 29. Current Mode Master/Slave Operation Over Short Distances

Figure 30. Synchronization Over Long Distances

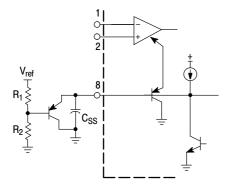

In voltage mode operation, the maximum duty cycle can be clamped. By the addition of a PNP transistor to buffer the clamp voltage, the Soft–Start current is not affected by  $R_1$ .

The new equation for Soft–Start is

$$t \approx \frac{V_{clamp} + 0.6}{9.0 \,\mu A} \, (C_{SS})$$

In current mode operation, this circuit will limit the maximum voltage allowed at the ramp input to end a cycle.

Figure 31. Buffered Maximum Clamp Level

A series gate resistor may be needed to dampen high frequency parasitic oscillation caused by the MOSFET's input capacitance and any series wiring inductance in the gate–source circuit. The series resistor will also decrease the MOSFET switching speed. A Schottky diode can reduce the driver's power dissipation due to excessive ringing, by preventing the output pin from being driven below ground. The Schottky diode also prevents substrate injection when the output pin is driven below ground.

Figure 33. MOSFET Parasitic Oscillations

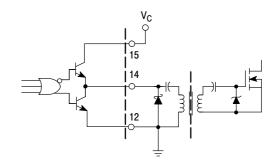

The totem pole output can furnish negative base current for enhanced transistor turn-off, with the addition of the capacitor in series with the base.

Figure 32. Bipolar Transistor Drive

The totem pole output can easily drive pulse transformers. A Schottky diode is recommended when driving inductive loads at high frequencies. The diode can reduce the driver's power dissipation due to excessive ringing, by preventing the output pin from being driven below ground.

Figure 34. Isolated MOSFET Drive

| Result    | $14 \text{ mV} = \pm 0.275\%$                                  | $54 \text{ mV} = \pm 1.0\%$                                | 10 mVp-p                                       | %8'69                                          |

|-----------|----------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|------------------------------------------------|

| Condition | $V_{in} = 40 \text{ V to } 56 \text{ V, I}_{O} = 7.5 \text{A}$ | $V_{in} = 48 \text{ V}$ , $I_{O} = 4.0 \text{ A to 7.5 A}$ | $V_{in} = 48 \text{ V}, I_{O} = 7.5 \text{ A}$ | $V_{in} = 48 \text{ V}, I_{O} = 7.5 \text{ A}$ |

| Test      | Line Regulation                                                | Load Regulation                                            | Output Ripple                                  | Efficiency                                     |

| Test            | Condition                                                  | æ       |

|-----------------|------------------------------------------------------------|---------|

| Line Regulation | $V_{in} = 40 \text{ V}$ to 56 V, $I_0 = 7.5 \text{A}$      | 14 mV = |

| Load Regulation | $V_{in} = 48 \text{ V}$ , $I_{O} = 4.0 \text{ A to 7.5 A}$ | 54 mV = |

| Output Ripple   | $V_{in} = 48 \text{ V, I}_{O} = 7.5 \text{ A}$             | 10 mVp- |

| Efficiency      | $V_{in} = 48 \text{ V}$ , $I_0 = 7.5 \text{ A}$            | %8'69   |

T<sub>1</sub> - Primary: 8 turns #48 AWG (1300 strands litz wire)

Secondary: 2 turns 0.003" (2 layers) copper foil Bootstrap: 1 turn added to secondary #36 AWG

Core: Philips 3F3, part #4312 020 4124 Bobbin: Philips part #4322 021 3525

Coilcraft P3269-A

<u>.</u>

Output Rectifiers: AAVID Heatsink #533402B02552 with clip Heatsinks - Power FET: AAVID Heatsink #533902B02552 with clip  $L = 1.8 \mu H$ Coilcraft P3270–A

.2 turns #48 AWG (1300 strands litz wire) Core: Philips 3F3, part #EP10-3F3 Bobbin: Philips part #EP10PCB1-8

Insulators - All power devices are insulated with Berquist Sil-Pad 150 (1) -10(1.0 µF) ceramic capacitors in parallel

(2) – 5(1.5  $\Omega$ ) resistors in parallel

Figure 35. Application Circuit

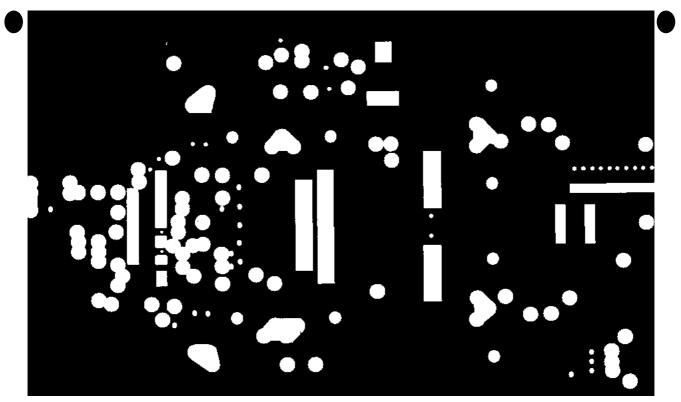

Figure 36. PC Board With Components

(Top View)

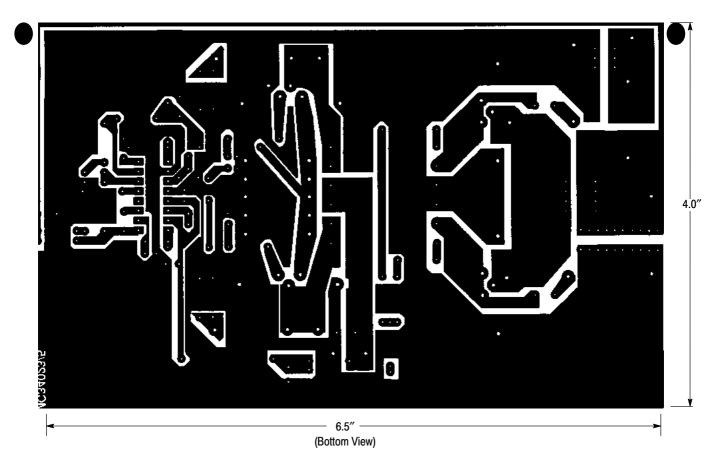

Figure 37. PC Board Without Components

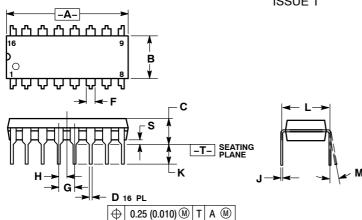

#### **PACKAGE DIMENSIONS**

#### PDIP-16 P SUFFIX CASE 648-08 ISSUE T

#### NOTES:

- DIMENSIONING AND TOLERANCING PER

ANSLY 14 5M 1082

- ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

- 3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

- DIMENSION B DOES NOT INCLUDE MOLD FLASH.

- 5. ROUNDED CORNERS OPTIONAL

|     | INCHES    |       | MILLIMETERS |       |

|-----|-----------|-------|-------------|-------|

| DIM | MIN       | MAX   | MIN         | MAX   |

| Α   | 0.740     | 0.770 | 18.80       | 19.55 |

| В   | 0.250     | 0.270 | 6.35        | 6.85  |

| C   | 0.145     | 0.175 | 3.69        | 4.44  |

| D   | 0.015     | 0.021 | 0.39        | 0.53  |

| F   | 0.040     | 0.70  | 1.02        | 1.77  |

| G   | 0.100 BSC |       | 2.54 BSC    |       |

| Н   | 0.050     | BSC   | 1.27        | BSC   |

| J   | 0.008     | 0.015 | 0.21        | 0.38  |

| K   | 0.110     | 0.130 | 2.80        | 3.30  |

| L   | 0.295     | 0.305 | 7.50        | 7.74  |

| М   | 0°        | 10 °  | 0 °         | 10 °  |

| S   | 0.020     | 0.040 | 0.51        | 1.01  |

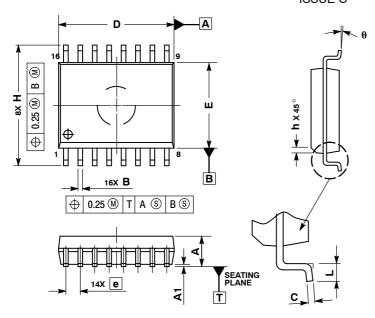

#### SOIC-16W DW SUFFIX CASE 751G-03 ISSUE C

#### NOTES:

- DIMENSIONS ARE IN MILLIMETERS.

- 2. INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 1994.

- DIMENSIONS D AND E DO NOT INLCUDE MOLD PROTRUSION.

- 4. MAXIMUM MOLD PROTRUSION 0.15 PER SIDE. 5. DIMENSION B DOES NOT INCLUDE DAMBAR

- 5. DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.35        | 2.65  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| В   | 0.35        | 0.49  |  |  |

| O   | 0.23        | 0.32  |  |  |

| D   | 10.15       | 10.45 |  |  |

| Е   | 7.40        | 7.60  |  |  |

| е   | 1.27        | BSC   |  |  |

| H   | 10.05       | 10.55 |  |  |

| h   | 0.25        | 0.75  |  |  |

| L   | 0.50        | 0.90  |  |  |

| q   | 0 °         | 7 °   |  |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada

Fax: 303-675-2173 or 800-344-3867 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative