Author: Mostafa Khazraei, Peter B. Green

#### **About this document**

#### **Scope and purpose**

The purpose of this document is to provide a comprehensive functional description and guide to the multilevel inverter demonstration board EVAL\_4KVA\_230VAC\_5LINV, based on the five-level active neutral point clamped flying capacitor topology using OptiMOS<sup>™</sup> 5 MOSFETs. The circuit functionality is discussed in detail. System implementation including converter architecture, control algorithms and firmware is also described in detail. Waveforms are shown under all operating conditions, and test measurement data is presented.

#### Intended audience

This application note is intended for design engineers, applications engineers and students.

#### Infineon components featured

- BSC093N15NS5 OptiMOS<sup>™</sup> 5 150 V N-channel in a SuperSO8 package

- IPT60R022S7 600 V CoolMOS™ S7 superjunction MOSFET in TO-Leadless (TOLL) package

- The EiceDRIVER™ 2EDF7275F dual-channel isolated MOSFET gate-driver IC

- XMC4700-F144F2048 32-bit microcontroller with ARM® Cortex-M4 (XMC™)

#### **Table of contents**

| Abou  | ıt this document                                   |    |

|-------|----------------------------------------------------|----|

| 1     | Introduction                                       | 3  |

| 1.1   | Switching cells                                    | 3  |

| 1.2   | Inverter types                                     | 3  |

| 1.3   | Evaluation board description                       |    |

| 2     | Evaluation board specifications                    | 13 |

| 3     | Evaluation board connections                       | 14 |

| 4     | Schematics                                         | 15 |

| 5     | Functional description                             | 28 |

| 5.1   | Differential five-level ANPC-FC inverter operation | 28 |

| 5.1.1 |                                                    |    |

| 5.1.2 |                                                    |    |

| 5.2   | Passive component selection                        | 33 |

| 5.2.1 | Output filter inductor design                      | 33 |

| 5.2.2 | Output filter capacitor design                     | 34 |

| 5.2.3 | Flying capacitor design                            | 34 |

| 5.2.4 |                                                    |    |

| 5.3   | Power loss analysis                                | 36 |

| 5.3.1  | Identifying the major sources of power loss          | 36 |

|--------|------------------------------------------------------|----|

| 5.3.2  | Analytical derivation of MOSFET RMS current          | 37 |

| 5.3.3  | Conduction loss calculation                          | 40 |

| 5.3.4  | Switching loss calculation                           |    |

| 5.3.5  | Input capacitor ESR loss calculation                 | 45 |

| 5.3.6  | Output inductor filter losses                        | 45 |

| 5.3.7  | Output capacitor damping resistor losses             | 45 |

| 5.3.8  | Pre-charging resistor losses                         | 46 |

| 5.3.9  | Snubber resistor losses                              | 46 |

| 5.3.10 | DCR switching losses                                 | 46 |

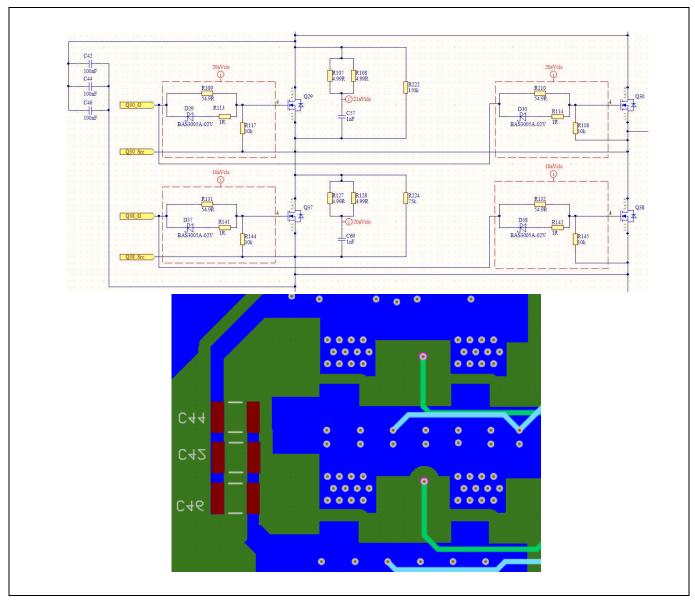

| 5.4    | Gate driver card design                              | 46 |

| 5.5    | Supervisory functions                                | 47 |

| 5.5.1  | DC input voltage sensing                             |    |

| 5.5.2  | AC output voltage sensing                            |    |

| 5.5.3  | Output current sensing                               | 48 |

| 6 Em   | nbedded firmware                                     | 50 |

| 6.1    | XMC <sup>™</sup> 4000 series microcontroller         | 50 |

| 6.2    | Digital control implementation                       | 52 |

| 6.3    | DAVE™ IDE                                            | 54 |

| 6.4    | Control algorithms                                   | 55 |

| 7 Bil  | l of Materials (BOM)                                 | 57 |

| 7.1    | Power board                                          | 57 |

| 7.2    | Control card                                         | 62 |

| 7.3    | Aux supply and gate driver card (center)             | 64 |

| 7.4    | Aux supply and gate driver card (sides)              | 65 |

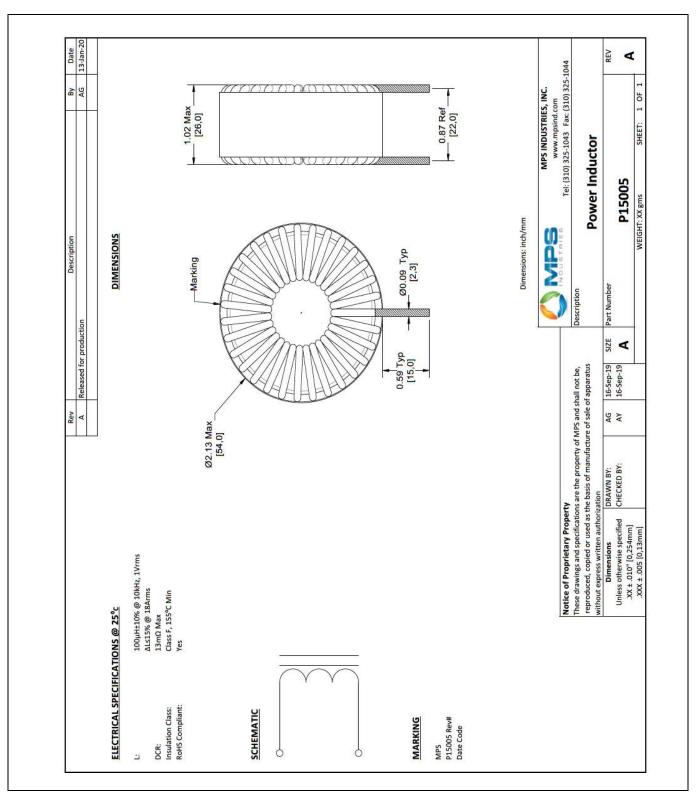

| 8 Inc  | ductor specifications                                | 67 |

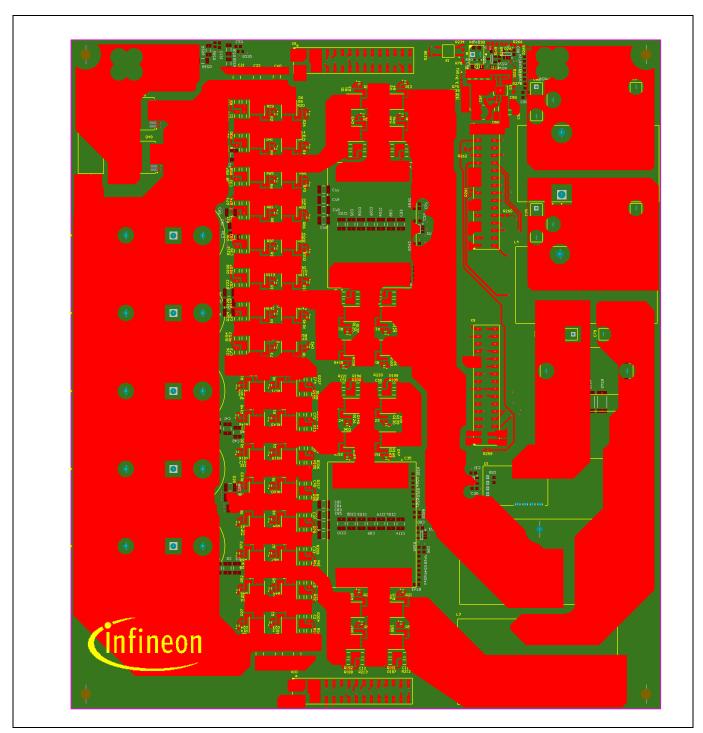

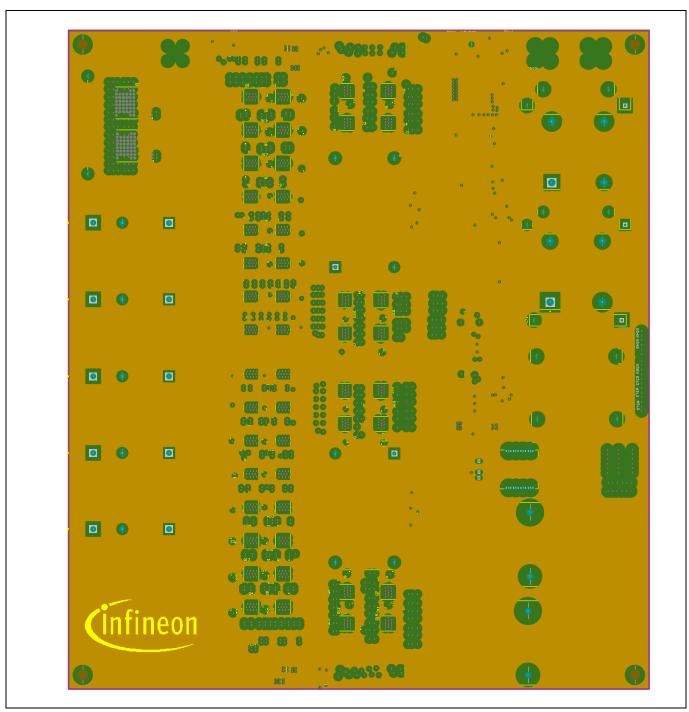

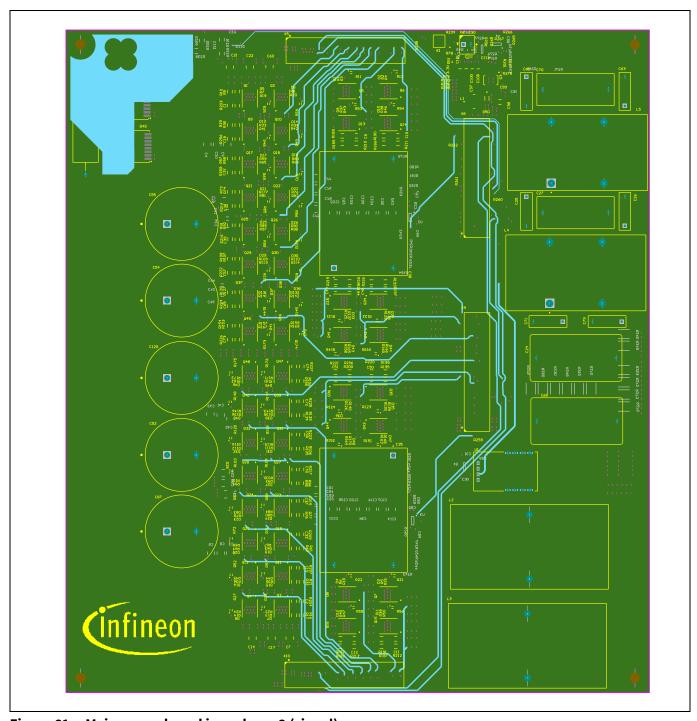

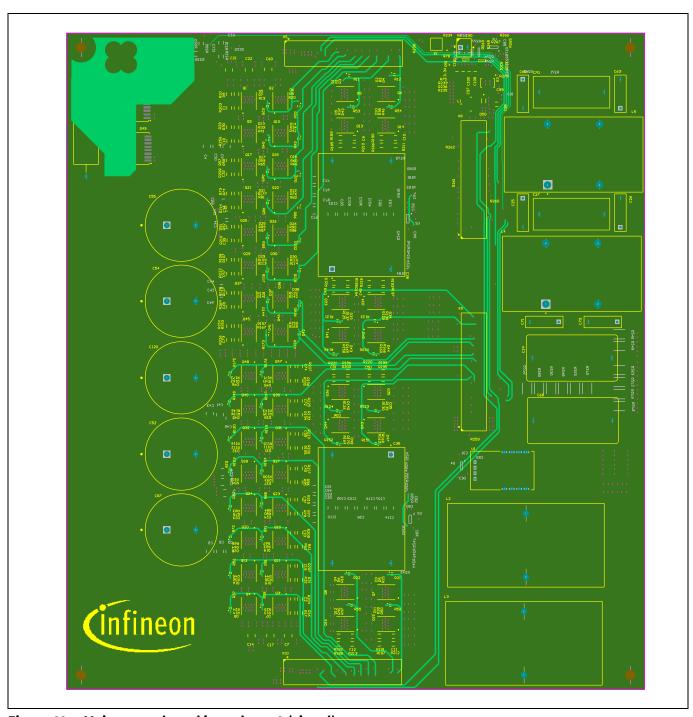

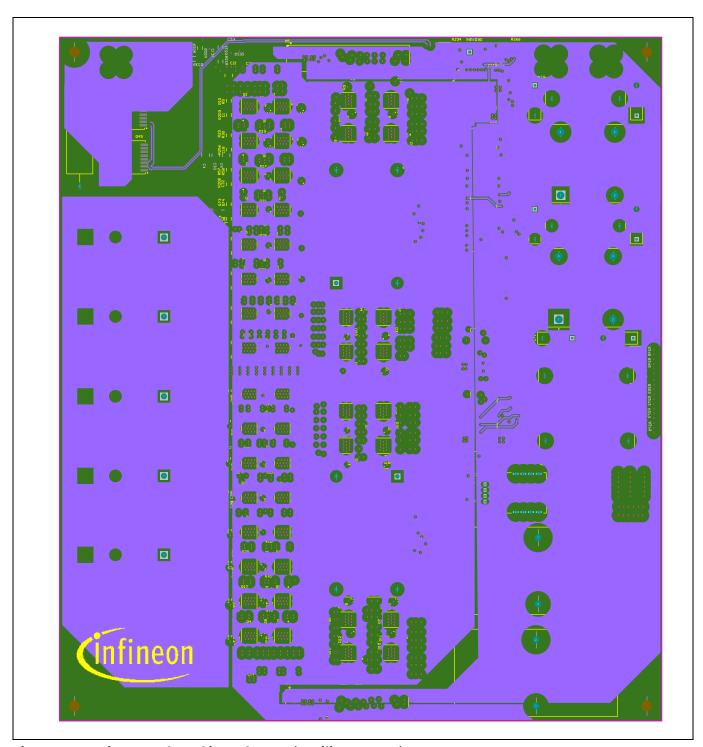

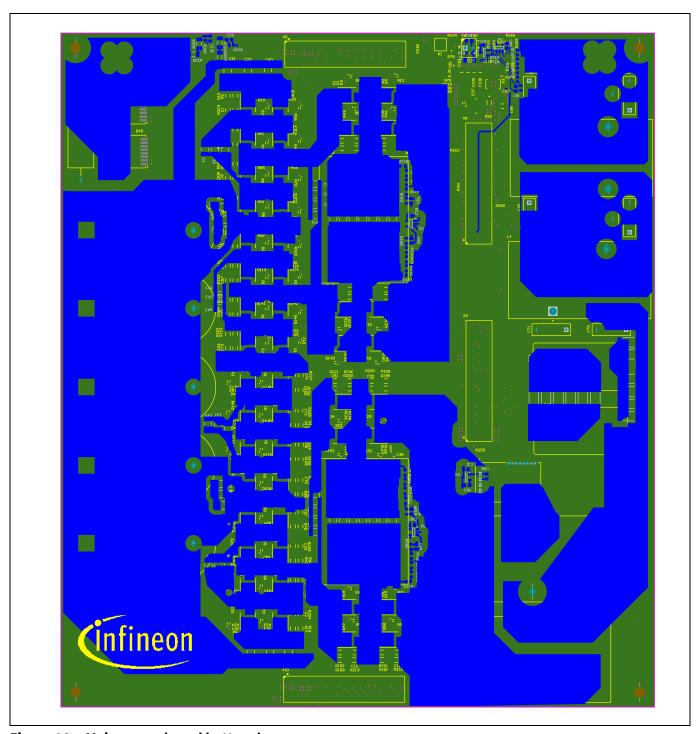

| 9 PC   | B layout                                             | 68 |

| 9.1    | Main power board PCB design                          |    |

| 10 Te: | st results                                           | 75 |

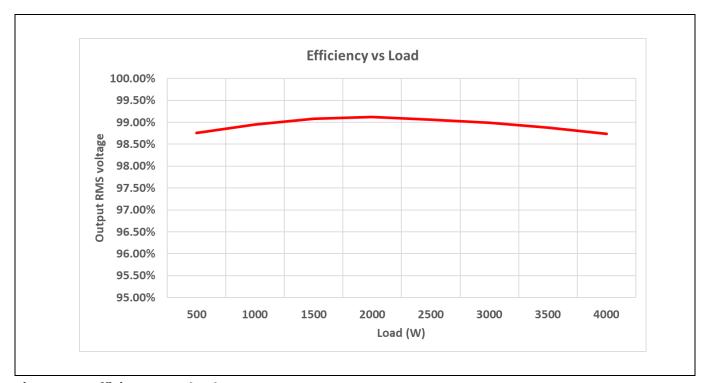

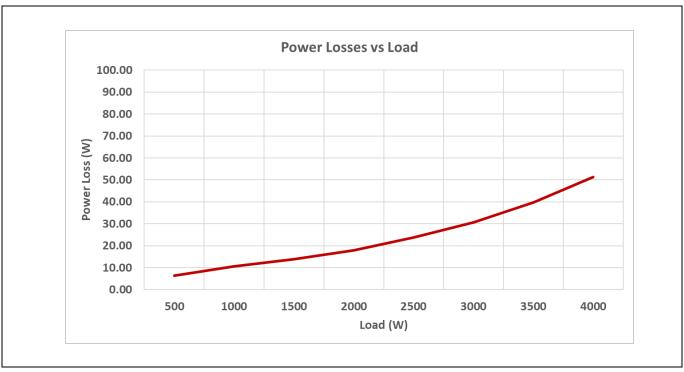

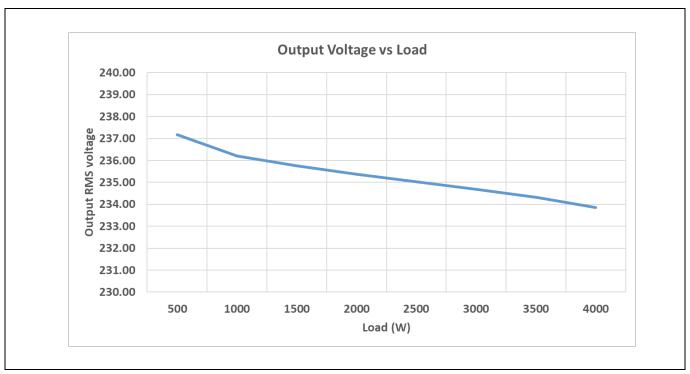

| 10.1   | Efficiency measurements                              | 75 |

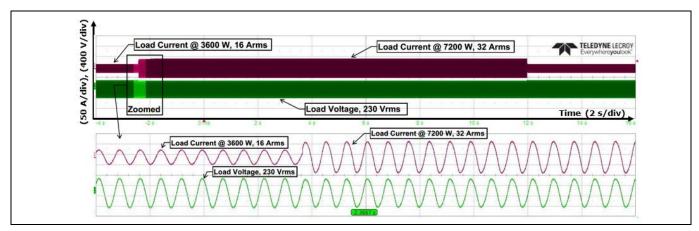

| 10.2   | Operating waveforms                                  |    |

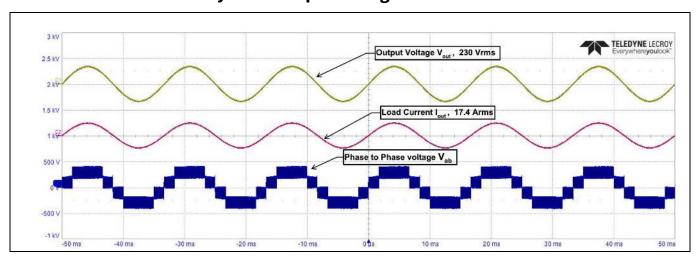

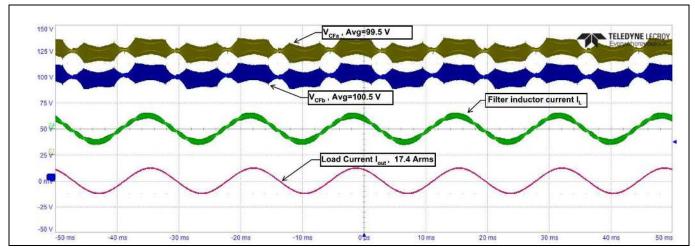

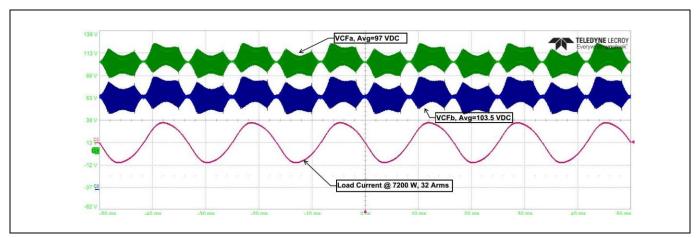

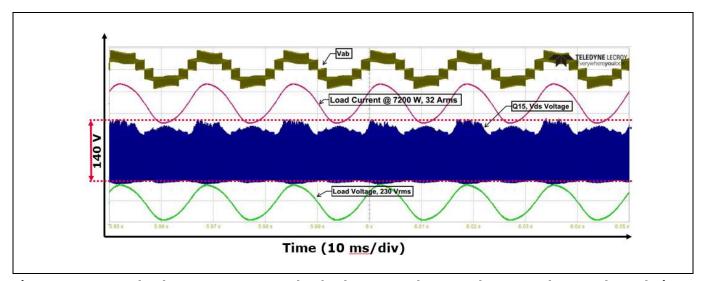

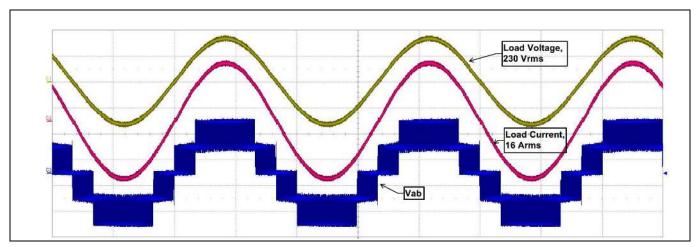

| 10.2.1 | Inverter steady-state output voltage                 | 77 |

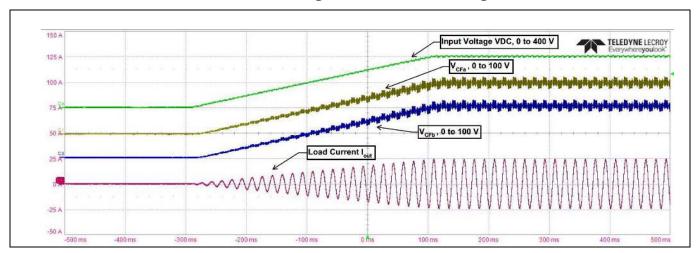

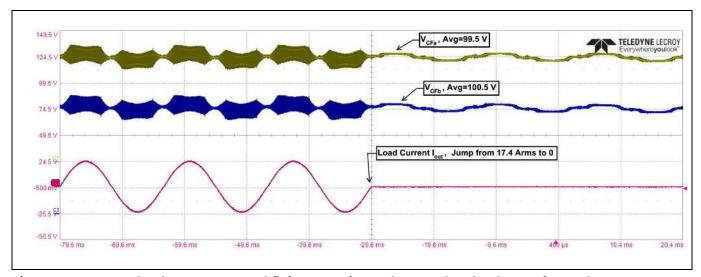

| 10.2.2 | Inverter start-up and flying capacitor pre-charge    |    |

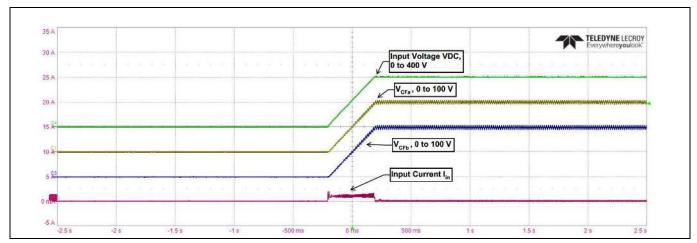

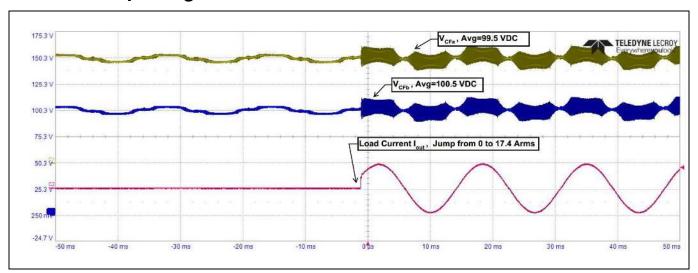

| 10.2.3 | Step-change in load                                  |    |

| 10.2.4 | Overload                                             | 80 |

| 10.3   | Thermal performance                                  | 82 |

| 10.3.1 | Component temperatures at maximum load               | 82 |

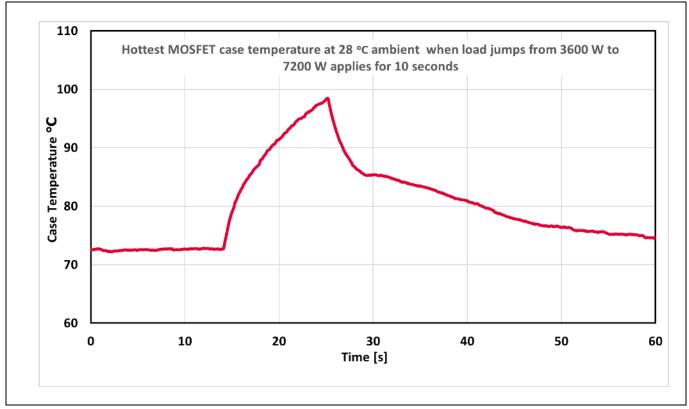

| 10.3.2 | Component temperature rise at twice maximum loadload | 83 |

| 11 Co  | nclusion                                             |    |

|        | ferences                                             |    |

|        | vicion history                                       |    |

Introduction

#### Introduction 1

#### 1.1 **Switching cells**

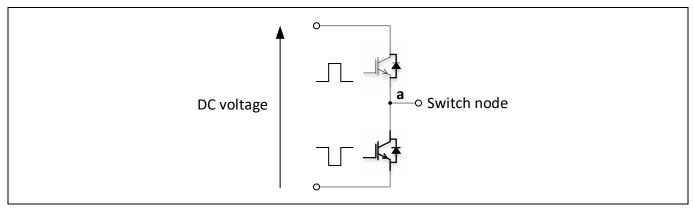

When discussing inverters, it is convenient to use the term switching cell to describe any combination of switches driven by a particular gate drive signal or its complement. A simple example is shown below.

Figure 1 A simple switching cell

In practice, a switching cell can be much more complicated than this example, consisting of several series and parallel MOSFET or IGBT power device blocks, which may be placed in different locations within the topology of the inverter. When driven by the same gate drive PWM signal or its complement, these combine to form switching cells. An individual switching cell has three states – that is, one switch on and the other off, the opposite or both switches off. An inverter is said to be multilevel if its topology contains more than one switching cell per halfbridge.

#### 1.2 **Inverter types**

A broad definition of an inverter is a power converter that converts a DC input to an AC output. For most applications, a pure sine wave output is desirable. Inverters cover many different applications, such as photovoltaic (PV) systems, energy storage systems (ESS) and motor drives covering power ratings ranging from tens of watts to megawatts and utilizing a variety of different architectures and topologies. Most PV and ESS inverters are grid-tied, requiring complex control of frequency, voltage, power factor and power flow. At higher power levels, three-phase inverters are used, which include three single-phase stages with output voltages synchronized at 120 degrees apart. This application note describes in detail the EVAL\_4KVA\_230VAC\_5LINV multilevel inverter designed to produce a single-phase line frequency sinusoidal output for connection to standard loads. The control strategies required for grid-tied operation are not covered, though the design could be upgraded to make this possible.

Modern inverter implementations are based on several different power semiconductor technologies, including silicon MOSFETs, IGBTs and also wide bandgap technologies such as SiC and GaN to form the switching cells that make up the topology. Choice of power switch type is determined by power, voltage, type of topology and cost/performance trade-offs. Inverters can be classified by the number of switching levels implemented.

#### Introduction

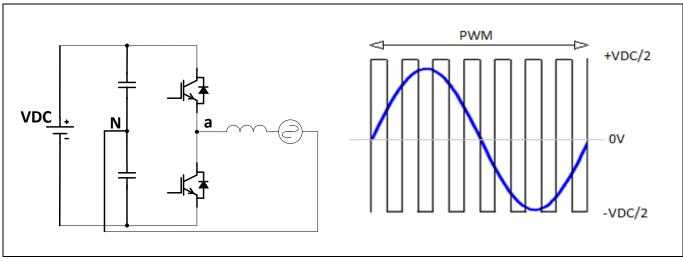

#### Two-level inverters

The most basic types of inverter use classic two-level topologies, in which there are only two possible voltage levels existing at the output of the power converter switching stage that feeds the output filter. The switching voltage is pulse width modulated using bipolar modulation at switching frequency F<sub>sw</sub> according to a sinusoidal reference. Frequency components of F<sub>sw</sub> are filtered out by the output filter to produce a sine wave output.

Figure 2 Two-level inverter basic schematic and operating waveforms

The figure above shows a simple half-bridge implementation of a two-level inverter containing one switching cell, where the switching node "a" can either be at +VDC/2 or -VDC/2 potential depending on which of the two switches is on. The output is returned to the mid-point of two series capacitors, which provides the 0 V neutral point. In applications like PV, ESS VDC is usually higher than 400 V. Therefore, high voltage (HV) switches must be used with their associated conduction and switching losses, which limits the overall efficiency. Furthermore, the output filter is necessarily large to remove enough of the high-frequency (HF) components to produce a clean sine wave output at the rated power.

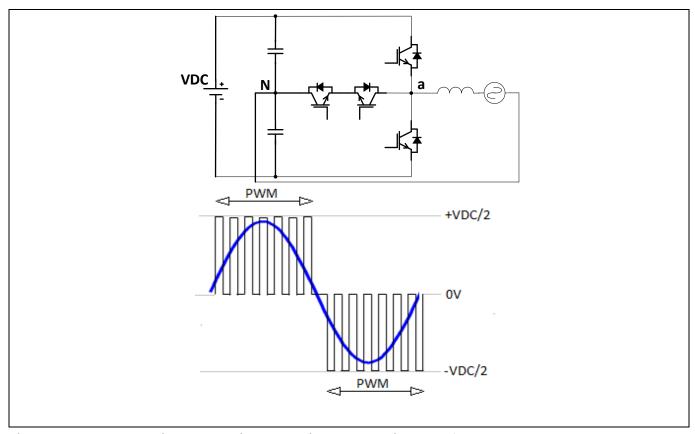

#### 2. Three-level inverters

In a three-level inverter, there are three possible voltage levels existing at the output of the power converter switching stage that feeds the output filter, which are +VDC/2, -VDC/2, and the 0 V mid-point. A bidirectional switch composed of two back-to-back power devices enables the switch node to be connected directly to 0 V again, provided by two series capacitors in the most basic implementation. This inverter still contains only a single switching cell and is not considered to be multilevel.

Introduction

Figure 3 Three-level inverter basic schematic and operating waveforms

The figure above shows a half-bridge implementation of a three-level transistor clamped T-type inverter where the switching node "a" can either be at +VDC/2 or -VDC/2 potential if one or other of the half-bridge switches is on and the other is off. Additionally, it can be connected to 0 V with the ability to transfer current in either direction through the bidirectional back-to-back switches. The output is returned to the same 0 V mid-point of the two series capacitors, which again provides the 0 V neutral point.

There are other implementations of the three-level inverter, including H-bridge topologies that can eliminate the need for the capacitor divider at higher power levels. There are also three-level inverter topologies that include more than one switching cell, which qualifies them as multilevel.

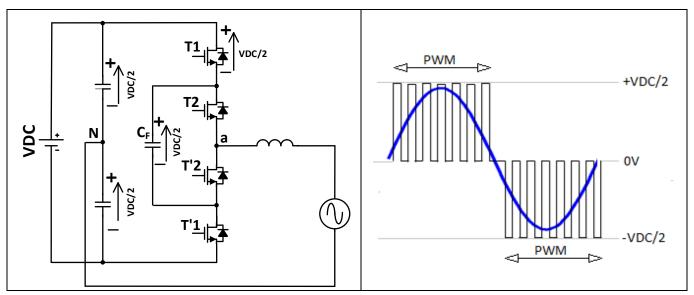

#### 3. Multilevel inverters

In multilevel inverters, there are at least three possible voltage levels existing at the output of the power converter switching stage that feeds the output filter including the 0 V mid-point and +VDC/2 and -VDC/2. The number of levels is always an odd number, since each level is available in either polarity with the exception of 0 V. Switching occurs during different time periods between two adjacent voltage levels to create a composite waveform, which contains HF components of amplitude VDC/(N-1) that requires less filtering to provide a sine wave output.

#### Introduction

Figure 4 Three-level flying capacitor inverter basic schematic and operating waveforms

Table 1 Three-level flying capacitor inverter switching states

| , , ,            |    |    |     |     |                 |  |  |  |  |

|------------------|----|----|-----|-----|-----------------|--|--|--|--|

| Switching states | T1 | T2 | T'1 | T'2 | V <sub>aN</sub> |  |  |  |  |

| 1                | 1  | 1  | 0   | 0   | +VDC/2          |  |  |  |  |

| 2                | 1  | 0  | 0   | 1   | 0               |  |  |  |  |

| 3                | 0  | 1  | 1   | 0   | 0               |  |  |  |  |

| 4                | 0  | 0  | 1   | 1   | -VDC/2          |  |  |  |  |

|                  |    |    |     |     |                 |  |  |  |  |

The above example shows a three-level inverter that is considered multilevel because there are two switching cells, one comprising T1 and T'1 and the other comprising T2 and T'2. There are four switching states used during operation – for all of which, two MOSFETs are on and two are off, as shown in Table 1.

Multilevel inverters are able to use lower-voltage trench MOSFET switches that offer very low  $R_{DS(on)}$  and body diode recovery charge  $Q_{rr}$  compared to HV superjunction MOSFETs or IGBTs. Greatly reduced conduction losses combined with reduced switching losses make it possible to reach very high efficiency. An inverter without the need for a heatsink or fan can then be designed. The multilevel inverter has become popular in medium- and high-power applications because of the reduced power dissipation of switching elements, smaller output filter size, lower harmonic content, and significantly lower EMI.

Some inverter designers may be concerned by the increased level of complexity involved in a multilevel design compared to traditional topologies, due to the higher number of switches and isolated gate drivers needed. However, above a certain power level, usually in the greater-than 3 kW range, the benefits of the multilevel approach such as reduction in size and weight combined with higher efficiency and power density can justify the additional complexity. As the power rating of power inverters increases, the share of mechanical parts such as heatsink and filter increase in size and cost compared to the semiconductor devices' portion. This is why a multilevel inverter will be even more beneficial as the power range increases.

There are several configurations of multilevel inverter, including:

- a. Diode clamped multilevel inverters (DC-MLI)

- b. Flying capacitor clamped multilevel inverters (FC-MLI)

- c. Cascaded H-bridge multilevel inverters (CHB-MLI)

#### Introduction

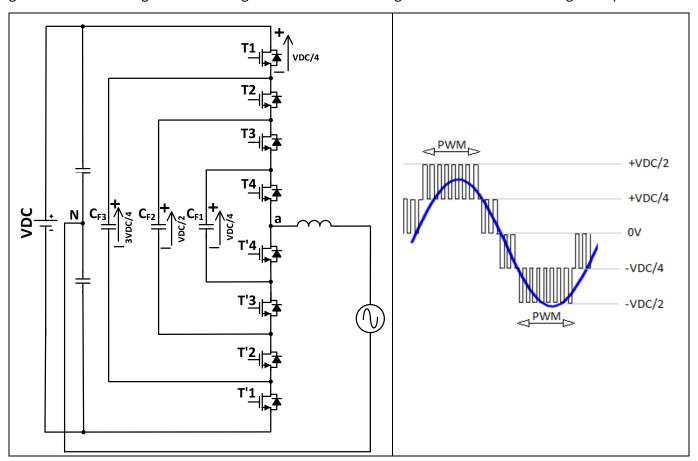

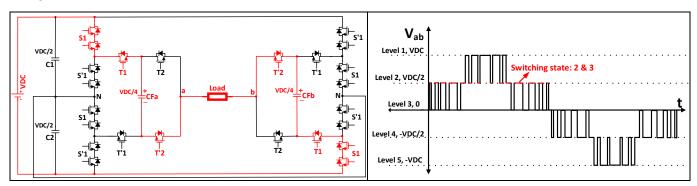

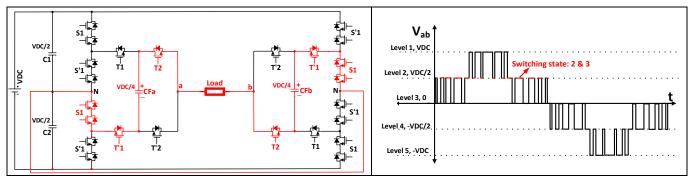

A further FC-MLI example is shown in **Figure 5** – in this case a five-level flying capacitor inverter. In FC-MLI the so-called "flying capacitors" (sometimes referred to as "floating capacitors") float with respect to ground potential. In the following example the five-level inverter utilizes the intermediate voltage levels +VDC/4 and -VDC/4 as well as +VDC/2, 0 V and -VDC/2. In this case, three flying capacitors are used, with voltage balance achieved by using *redundant switching states*, meaning combinations where the capacitors may be charged or discharged while the output node remains at the same potential in both states. In the **Figure 4** example switching states 2 and 3 are redundant, either adding or removing charge from the flying capacitor C<sub>F</sub> while the output node is held at 0 V. As will be explained later, phase-shifted pulse width modulation (PSPWM) is used to generate the switching states including the redundant switching states to balance the voltage of capacitors.

Figure 5 Five-level flying capacitor inverter basic schematic and operating waveforms

In the example above, there are four switching cells. The complexity has greatly increased from the three-level to the five-level implementation of the FC-MLI, which now requires three flying capacitors. The number of switching states required for operation has also increased to 16, calculated by the formula  $N_s = 2^{(N-1)}$  where N is the number of levels.

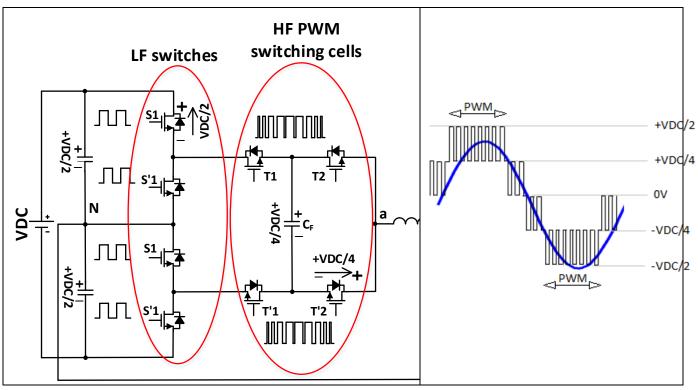

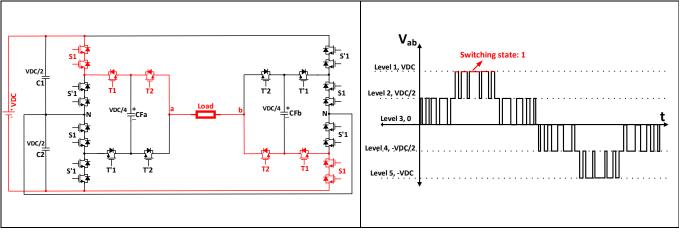

The topology shown in **Figure 6** is a derivative of the five-level inverter shown in **Figure 5**, which replaces three flying capacitors with only one. This is known as a *hybrid* multilevel inverter, which allows a five-level design to be realized with only two switching cells (HF PWM switching cells) combined with other MOSFETs switching at line frequency (low-frequency PWM switching cells) for polarity toggling. This hybrid topology is called active neutral point clamped flying capacitor inverter (ANPC-FC). The evaluation board EVAL\_4KVA\_230VAC\_5LINV described in this application note is based on this topology. The differences between two-level inverters, general multilevel inverters (Figure 5) and this hybrid multilevel inverter ANPC-FC are listed in Table 2. Please note that the information in Table 2 is based on the inverter in a half-bridge configuration.

Figure 6 Five-level ANPC-FC inverter basic schematic and operating waveforms

Table 2 Comparison of key parameters for multilevel vs. two-level inverters

|                                                 | Two-level           | N-level                           | ANPC-FC                          | Comment                                                                                              |

|-------------------------------------------------|---------------------|-----------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------|

| Number of HF switching cells<br>N <sub>sc</sub> | 1                   | N-1                               | (N-1)/2                          | Lower number of $N_{sc}$ for ANPC-FC for the same $N$ .                                              |

| FET blocking voltage                            | VDC                 | VDC/(N-1)                         | VDC/(N-1)                        | HV FET/IGBTs replaced with lower-<br>voltage FET. Significant reduction in<br>loss is achieved.      |

| Effective output frequency                      | F <sub>sw</sub>     | (N-1) × F <sub>sw</sub>           | (N-1)/2 ×<br>F <sub>sw</sub>     | Higher output frequencies with lower switching losses. F <sub>sw</sub> = MOSFET switching frequency. |

| Output inductor                                 | L                   | L/(N <sub>sc</sub> ) <sup>2</sup> | L/[N <sub>sc</sub> × (N-1)]      | Significant reduction in size and weight.                                                            |

| EMI                                             | Switching<br>at VDC | Switching<br>at<br>VDC/(N-1)      | Switching<br>at<br>VDC/(N-<br>1) | Improved due to reduced switching voltages.                                                          |

| Number of switches                              | 2                   | 2 × (N-1)                         | ≤2 × (N-1)                       | Lower number of MOSFETs needed for ANPC-FC if HV MOSFETs used as LF switches.                        |

Introduction

### 1.3 Evaluation board description

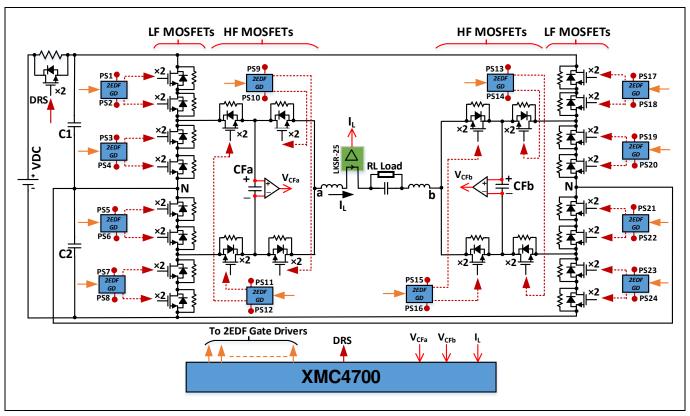

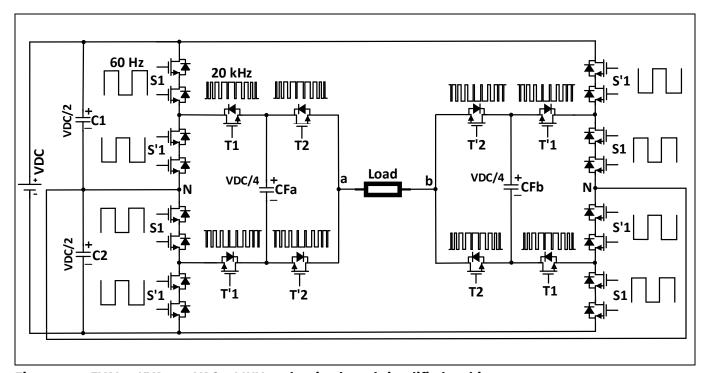

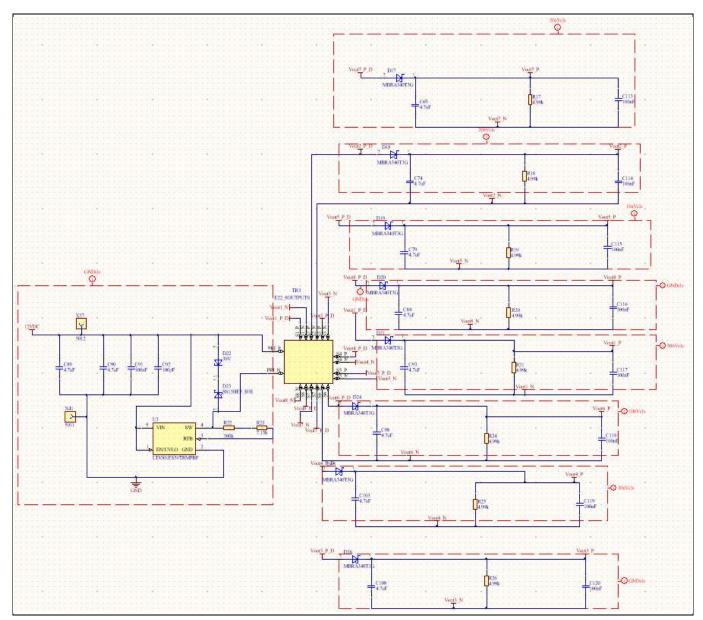

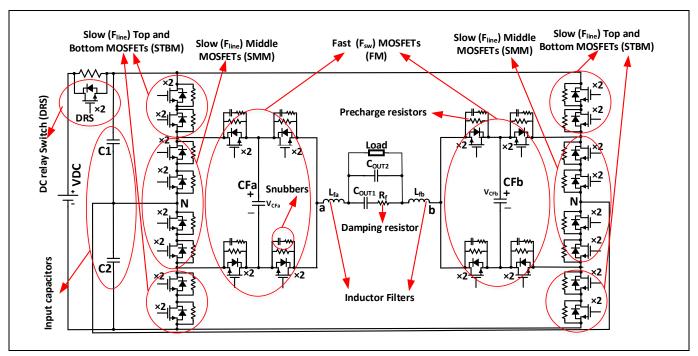

The EVAL\_4KVA\_230VAC\_5LINV evaluation board has a full-bridge configuration and consists of two five-level ANPC-FC half-bridge inverters operating 180 degrees out of phase with each other to provide a differential multilevel voltage output. The basic structure of this board is shown in Figure 7. The load is connected between points "a" and "b", via the output filter. Each half-bridge consists of 24 switches; 16 are switching at line frequency (these will be referred to as the low-frequency (LF) switches) and eight are switching at the high frequency (these will be referred to as the high-frequency (HF) switches). All these 48 MOSFETs are OptiMOS™ 5 150 V BSC093N15NS5 devices. This MOSFET has very low R<sub>DS(on)</sub>, Q<sub>g</sub> and Q<sub>rr</sub>. In an N-level ANPC-FC multilevel inverter the voltage of the flying capacitor is VDC/(N − 1). Then for a five-level inverter operating from a 400 VDC bus,  $V_{FC} = 400/(5-1) = 100 \text{ V}$ . That means the voltage each one of the HF switches has to withstand is only VDC/4 = 100 V. That is why 150 V MOSFETs can be used here. Also, to be able to use the same 150 V MOSFETs in LF sections, MOSFETs are installed in series, as seen in Figure 7. Each two MOSFETs that are in series are synchronized and only one single pulse from the microcontroller is needed to control them. When MOSFETs are installed in series, voltage sharing is a concern. However, OptiMOS™ 5 MOSFETs enjoy relatively linear output capacitance (Coss), which helps significantly with voltage sharing. Also, the series MOSFETs here are only switching at line frequency, 60 Hz. As shown later in the test results, the MOSFET voltage sharing is successfully achieved.

There are 12 gate driver ICs in the board, as shown in **Figure 7**. Each gate driver has two channels, and two isolated power supplies are needed per channel (PS1, PS2, ..., PS24). Later, it will be shown that these isolated power supplies can be easily implemented in a very cost effective manner using planar transformers with an integrated flyback controller. There are also two HV MOSFETs IPT60R022S7 (650 V, 22 m $\Omega$ ) that have been used to bypass the inrush current control resistor. These two MOSFETs have been installed in parallel to form the DC relay switch (DRC), as shown in **Figure 7**.

While there are lot of MOSFETs and gate drivers used in this design, the overall system control is not as complicated as it may initially appear. To better understand how this system is controlled, a simplified version of **Figure 7** has been shown in **Figure 8**, which shows the PWM control signals that are needed for the system to function. Only three PWM signals, S1, T1, T2, are necessary and all of the MOSFETs are controlled either with these three signals or their complimentaries: S'1, T'1, T'2. S1 is a LF pulse 60 Hz, and T1 and T2 are HF pulses in the 16 to 20 kHz range.

The effective output frequency is twice MOSFET frequency, equivalent to ~40 kHz. In this inverter the five-level output voltage between points "a" and "b" will be the following: +VDC, +VDC/2, 0 V, -VDC/2, -VDC. Section 4 of this application note explains how the five-level output waveform is generated.

Figure 7 EVAL\_4KVA\_230VAC\_5LINV evaluation board basic architecture

Figure 8 EVAL\_4KVA\_230VAC\_5LINV evaluation board simplified architecture

infineon

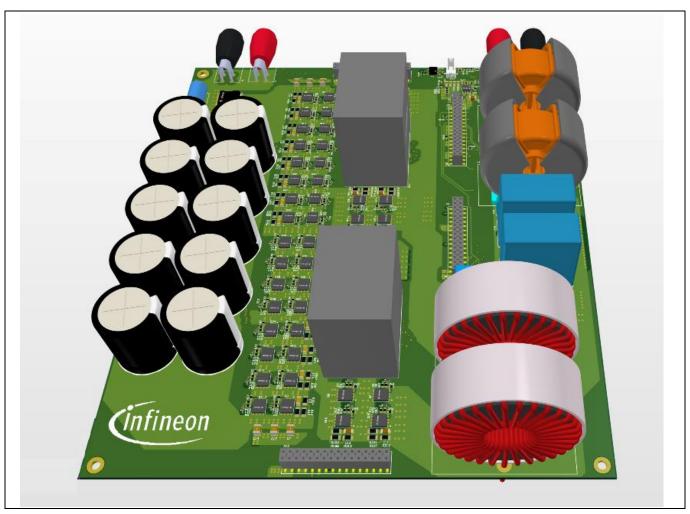

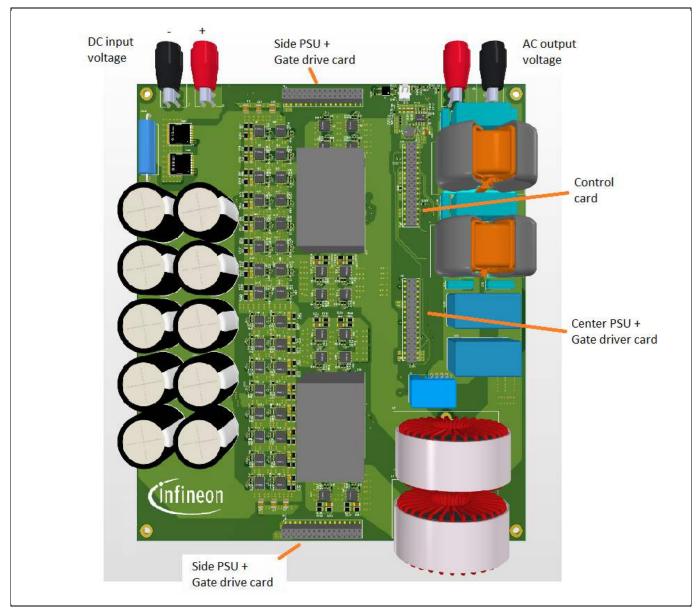

Figure 9 EVAL\_4KVA\_230VAC\_5LINV main board

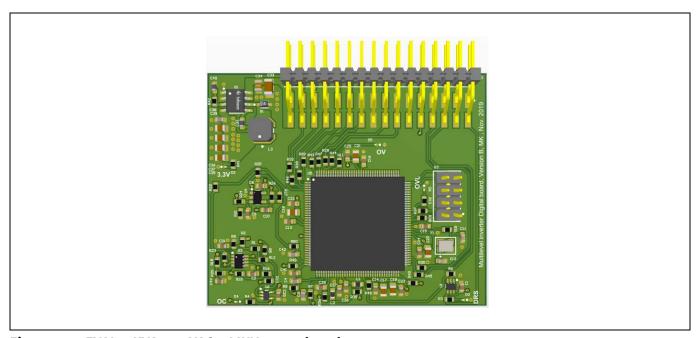

Figure 10 EVAL\_4KVA\_230VAC\_5LINV control card

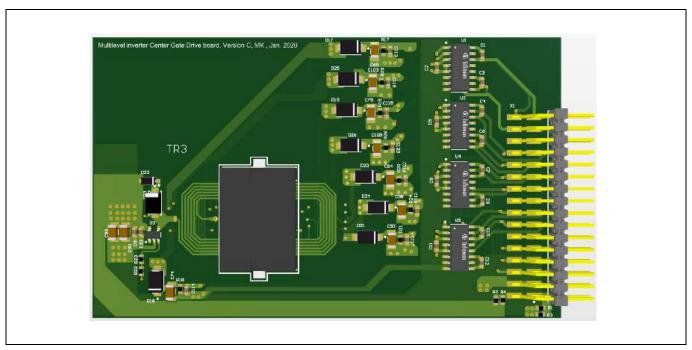

Figure 11 EVAL\_4KVA\_230VAC\_5LINV auxiliary power - gate driver cards (center)

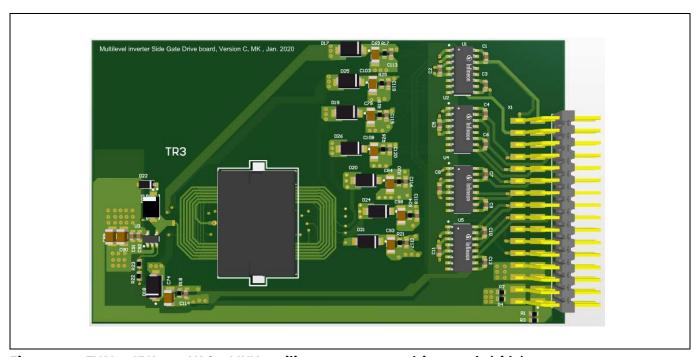

Figure 12 EVAL\_4KVA\_230VAC\_5LINV auxiliary power - gate driver cards (side)

**Evaluation board specifications**

### 2 Evaluation board specifications

#### Input and output in normal operation

- Input voltage 400 V DC nominal

- DC input voltage range: 380 V up to 420 V

- Nominal output voltage 230 V<sub>RMS</sub> (60 Hz)

- Maximum continuous average input current 12 A

- Maximum output continuous power 4.0 kVA

- Normal loads supported only. No grid-tied operation!<sup>1</sup>

- Pure sine wave output

- Inverter start-up time to reach the nominal output voltage during full-load or no-load condition less than 500 ms

#### **Protection features**

- DC input undervoltage and overvoltage protection (UVP/OVP)

- Over-load and short-circuit output protection.

Attention: It is <u>not</u> recommended to short-circuit the output!

#### **Board dimensions**

Main board:

Maximum width 8.95 inches (227 mm), max. length 7.88 inches (200 mm)

Control board:

Maximum width 2.36 inches (60 mm), max. length 1.97 inches (50 mm)

Auxiliary power boards:

• Maximum width 3.94 inches (100 mm), max. length 2.36 inches (60 mm)

Attention: HIGH VOLTAGE OUTPUT! Risk of electric shock.

Attention: The board should be tested only by qualified engineers and technicians.

<sup>1</sup> Grid-tied operation may be possible with a firmware upgrade but is NOT currently supported.

Application Note 13 of 87

**Evaluation board connections**

### 3 Evaluation board connections

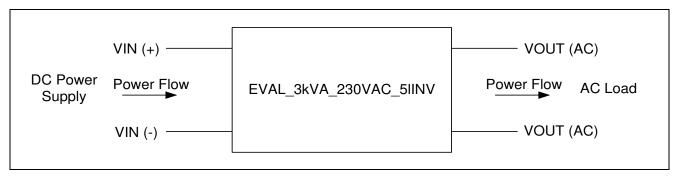

Figure 13 EVAL\_4KVA\_230VAC\_5LINV connections

Figure 14 EVAL\_4KVA\_230VAC\_5LINV connection diagram

**Schematics**

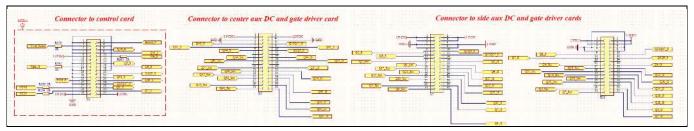

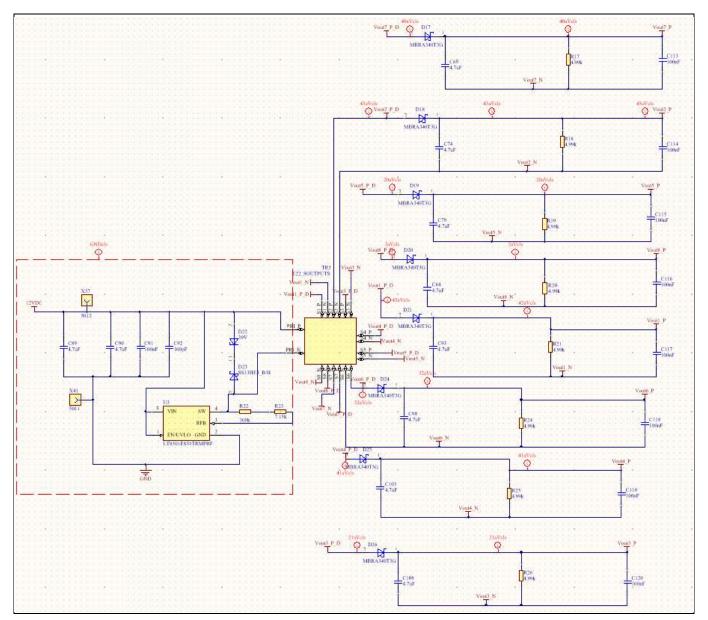

Figure 15 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - daughter card connectors

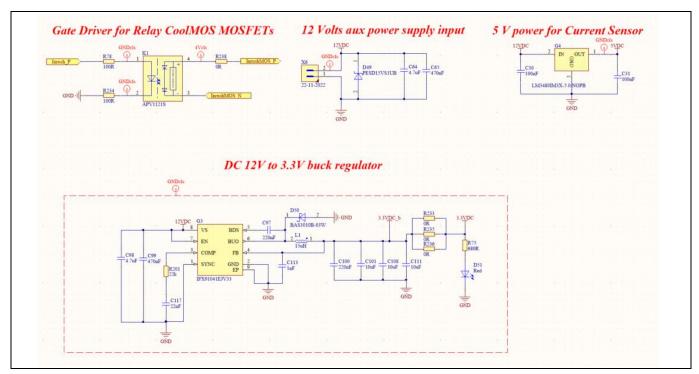

Figure 16 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - auxiliary power supplies

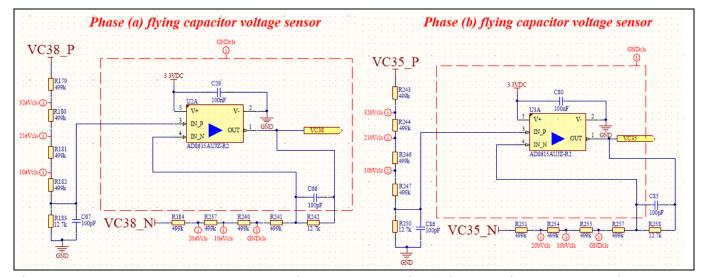

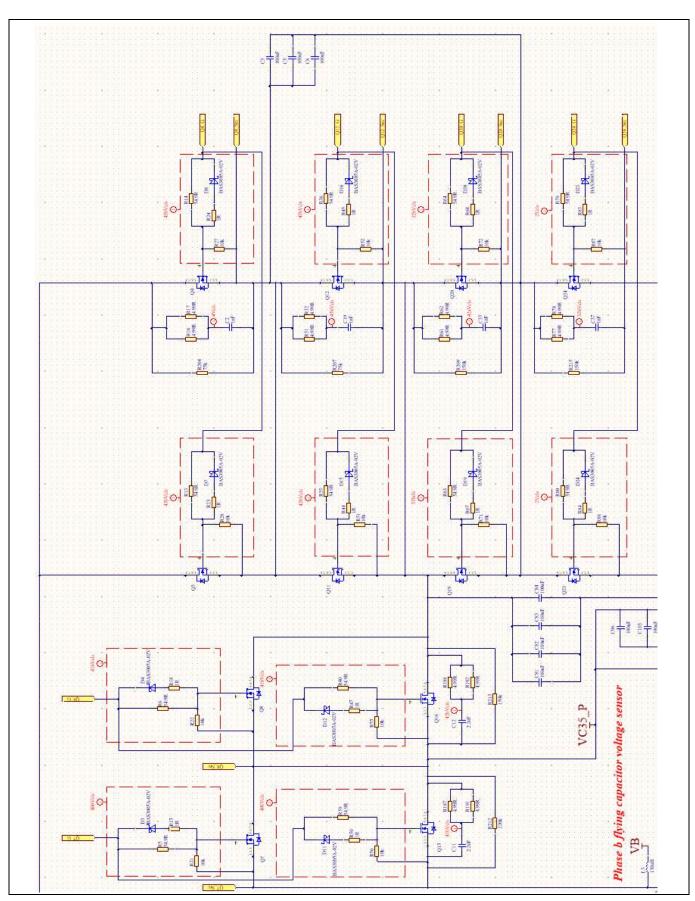

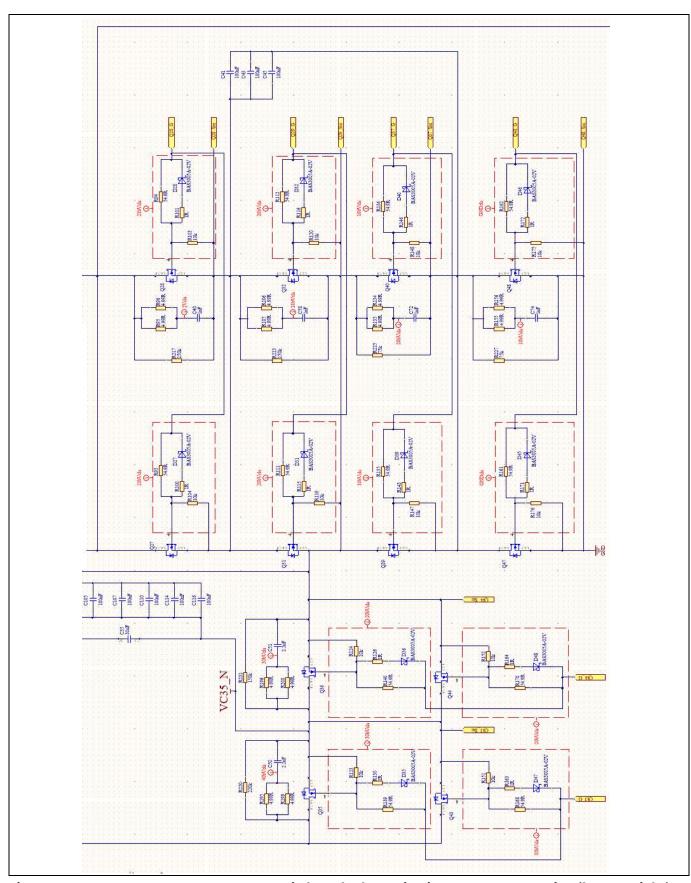

Figure 17 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - flying capacitor voltage sensing

**Schematics**

**Application Note**

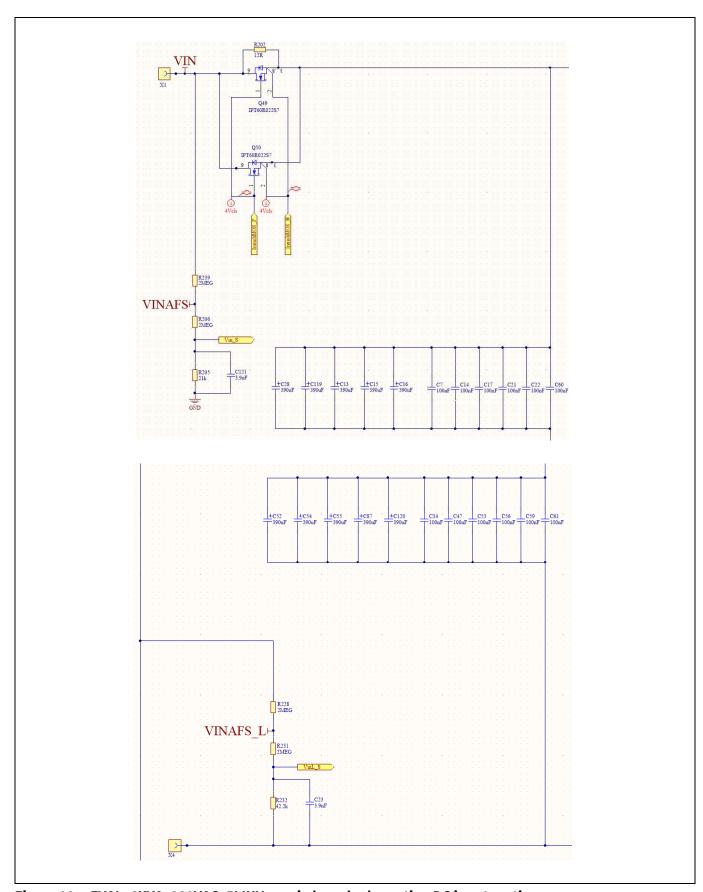

Figure 18 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - DC input section

Figure 19 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - inverter power section (top left)

Figure 20 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - inverter power section (bottom left)

**Schematics**

Figure 21 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - inverter power section (top right)

19 of 87

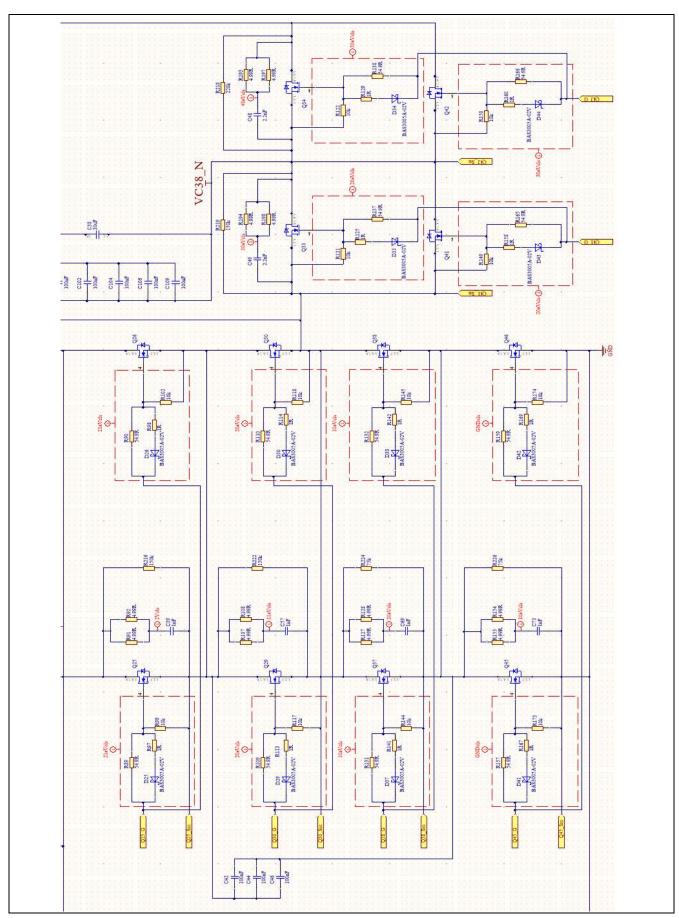

Figure 22 EVAL\_4KVA\_230VAC\_5LINV - main board schematic - inverter power section (bottom right)

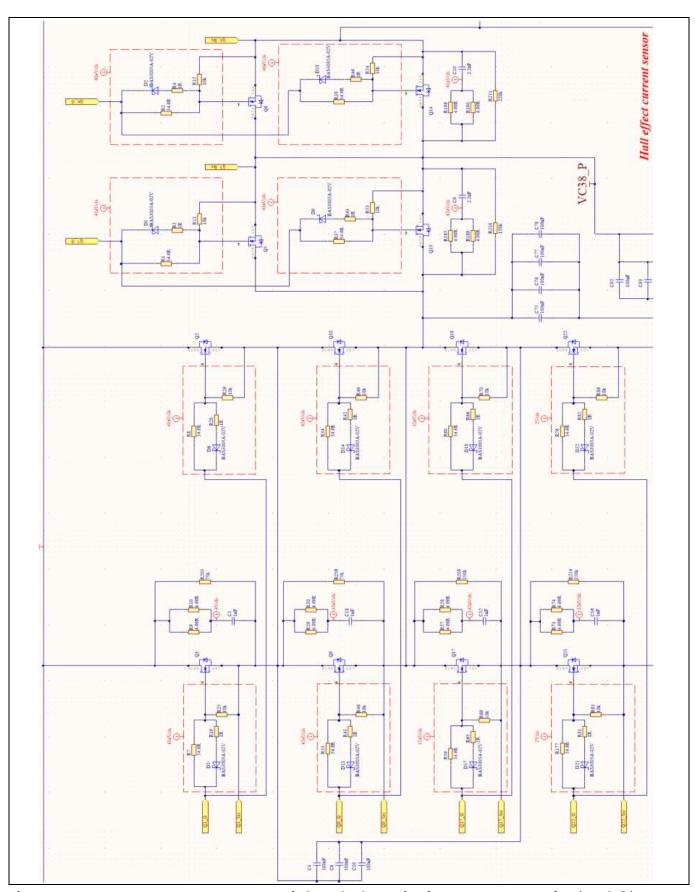

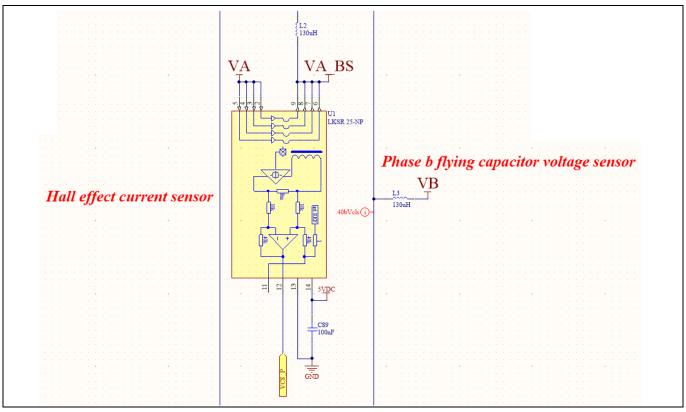

Figure 23 EVAL\_4KVA\_230VAC\_5LINV - hall effect current sensor

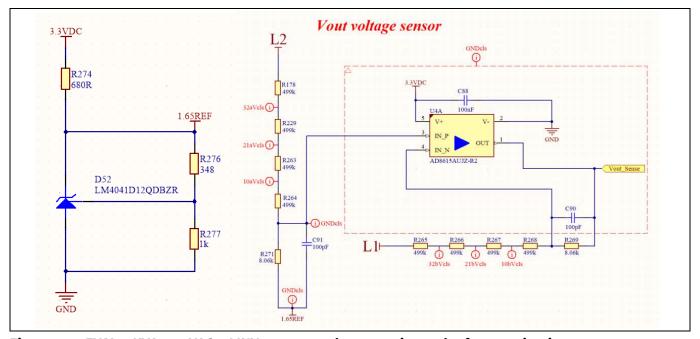

Figure 24 EVAL\_4KVA\_230VAC\_5LINV - output voltage sensing and reference circuit

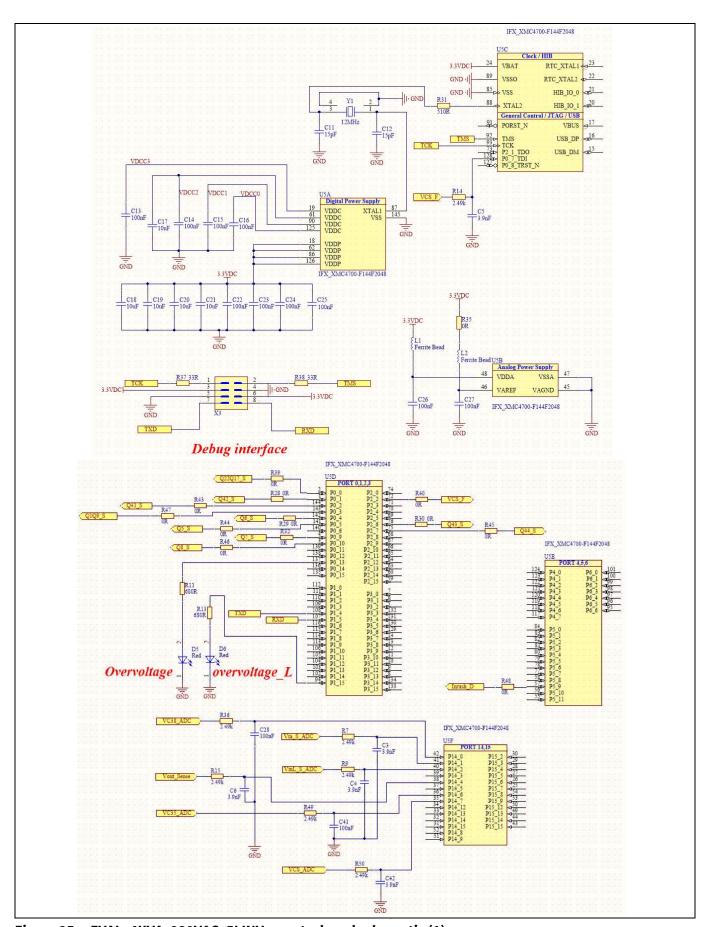

Figure 25 EVAL\_4KVA\_230VAC\_5LINV - control card schematic (1)

Figure 26 EVAL\_4KVA\_230VAC\_5LINV - control card schematic (2)

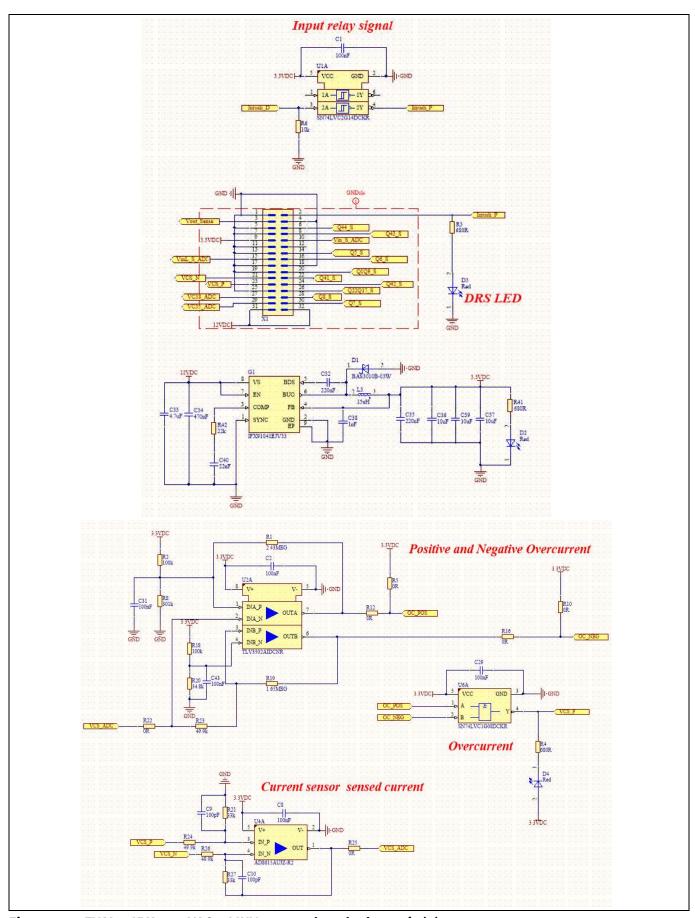

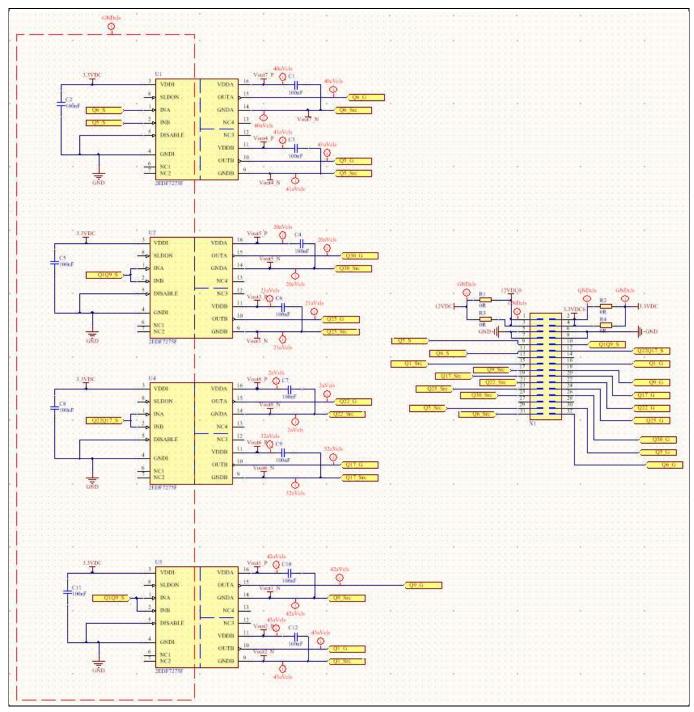

Figure 27 EVAL\_4KVA\_230VAC\_5LINV – auxiliary power supply and gate driver schematic (center) power supply section

Figure 28 EVAL\_4KVA\_230VAC\_5LINV - auxiliary power supply and gate driver schematic (center) gate driver section

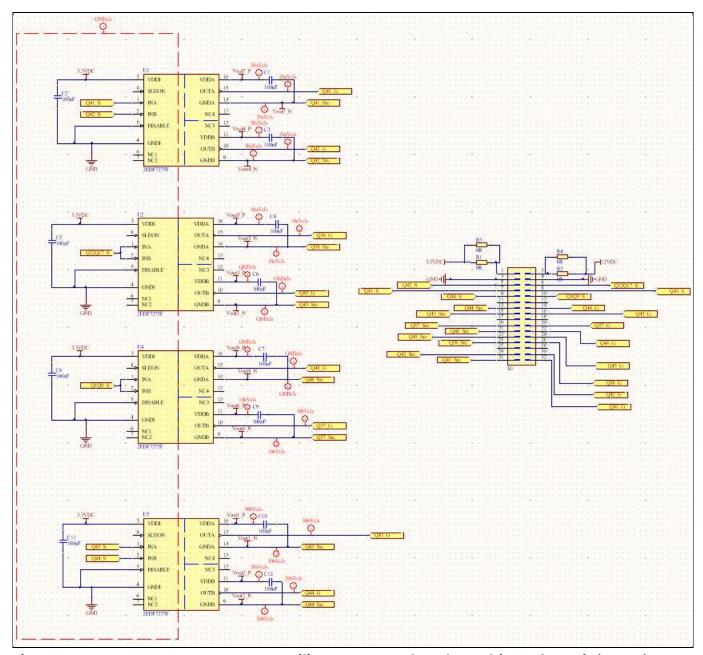

Figure 29 EVAL\_4KVA\_230VAC\_5LINV – auxiliary power supply and gate driver schematic (sides) power supply section

Figure 30 EVAL\_4KVA\_230VAC\_5LINV – auxiliary power supply and gate driver schematic (sides) gate driver section

**Functional description**

### 5 Functional description

### 5.1 Differential five-level ANPC-FC inverter operation

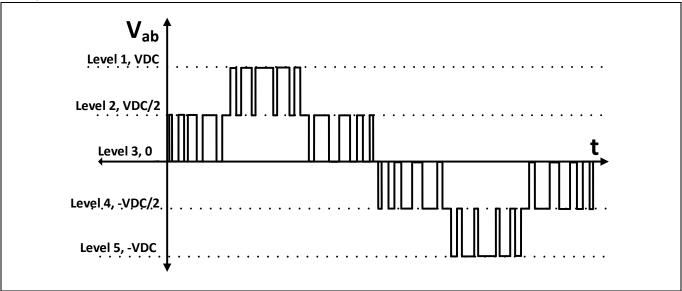

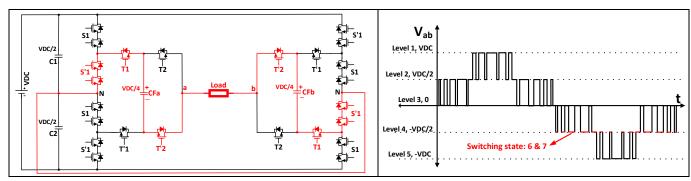

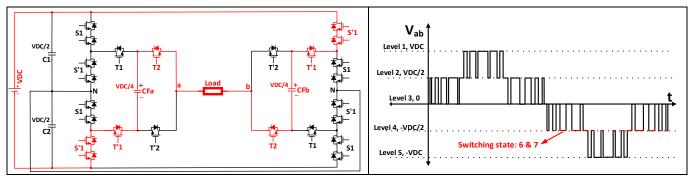

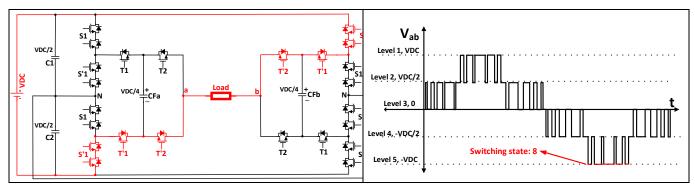

The main board contains the power conversion circuitry based on the circuit shown in **Figure 7**. As mentioned in section 1.2, the differential voltage between the switch nodes "a" and "b" (V<sub>ab</sub>) can be any one of five distinct levels, shown below.

Figure 31 EVAL\_4KVA\_230VAC\_5LINV switching node voltage

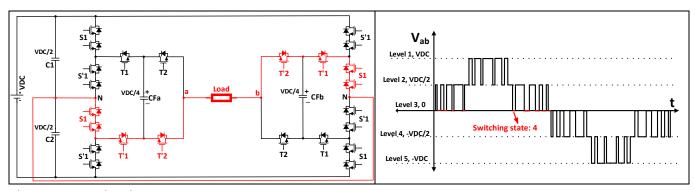

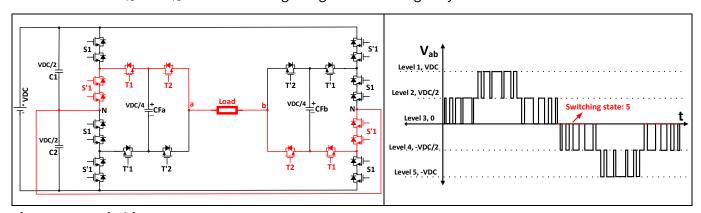

The sine wave output is constructed by various switching states, shown in Table 3. The differential voltage  $V_{ab}$  shown above is connected via an LC filter to the output, which removes the HF switching component to produce a line frequency sine wave output. Although there are five possible voltage levels available, there are actually eight switching states, as shown in the table below. Switching states 2 and 3, and 6 and 7 are redundant states, so for each of these pairs  $V_{ab}$  will be the same, but the flying capacitors  $C_{Fa}$  and  $C_{Fb}$  are either charging or discharging. By switching between redundant states, the flying capacitor charge balance is maintained. As seen in Table 3, only three independent switching signals, S1 (LF 60 Hz), T1 and T2 (HF PWM ~20 kHz) and their complements are needed to provide all the gate drive signals for this inverter. It will be explained later how by using PSPWM these eight switching states will be generated in hardware.

Table 3 Differential five-level inverter switching states

| Switching states | S1 | T1 | T2 | Va     | V <sub>b</sub> | V <sub>ab</sub> |

|------------------|----|----|----|--------|----------------|-----------------|

|                  |    |    |    |        |                |                 |

| 1                | 1  | 1  | 1  | VDC    | 0              | VDC             |

| 2                | 1  | 1  | 0  | 3VDC/4 | VDC/4          | VDC/2           |

| 3                | 1  | 0  | 1  | 3VDC/4 | VDC/4          | VDC/2           |

| 4                | 1  | 0  | 0  | VDC/2  | VDC/2          | 0               |

| 5                | 0  | 1  | 1  | VDC/2  | VDC/2          | 0               |

| 6                | 0  | 1  | 0  | VDC/4  | 3VDC/4         | -VDC/2          |

| 7                | 0  | 0  | 1  | VDC/4  | 3VDC/4         | -VDC/2          |

| 8                | 0  | 0  | 0  | 0      | VDC            | -VDC            |

**Functional description**

### 5.1.1 Switching states of the differential five-level ANPC-FC inverter

In this section, it is explained how output waveform is generated by applying various switching states from table 3. For the sake of simplicity, it is assumed that power factor is equal to 1 (no phase shift between output voltage and current). During switching state 1,  $V_{ab}$  is equal to VDC, the output inductor current is rising (energy transfer) and flying capacitors (CFa and CFb) are bypassed, neither being charged nor discharged by the load current.

Figure 32 Switching state 1

During switching state 2,  $V_{ab}$  is equal to VDC/2 because the flying capacitors are now introduced into the circuit, each blocking VDC/4. The inductor current is rising (energy transfer) with the load current increasing the FC charge.

Figure 33 Switching state 2

During switching state 3,  $V_{ab}$  is also equal to VDC/2; however, in this case the flying capacitors are still blocking VDC/4. The inductor current is now falling (freewheeling) with the load current discharging both CFa and CFb.

Figure 34 Switching state 3

#### **Functional description**

During switching state 4,  $V_{ab}$  is equal to 0 V. In this case the flying capacitors are bypassed. The inductor current falls (freewheeling) and  $C_{Fa}$  are neither being charged nor discharged by the load current.

Figure 35 Switching state 4

During switching state 5,  $V_{ab}$  is also equal to 0 V. In this case the flying capacitors remain bypassed. The inductor current rises and  $C_{Fa}$  and  $C_{Fb}$  are neither being charged nor discharged by the load current.

Figure 36 Switching state 5

During switching state 6,  $V_{ab}$  is equal to -VDC/2. The reverse inductor current is falling with the load current discharging  $C_{Fa}$  and  $C_{Fb}$  voltage.

Figure 37 Switching state 6

#### **Functional description**

During switching state 7, Vab is equal to -VDC/2. The reverse inductor current is falling with the load current charging C<sub>Fa</sub> and C<sub>Fb</sub> voltage.

Figure 38 **Switching state 7**

During switching state 8, Vab is equal to -VDC, the inductor current is falling and the flying capacitors CFa and CFb are neither being charged nor discharged by the load current.

**Switching state 8** Figure 39

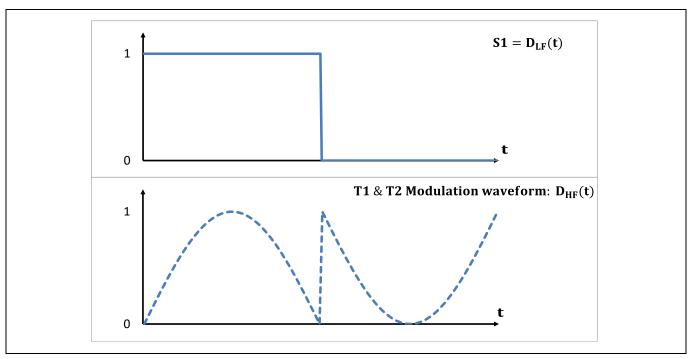

#### **Modulation scheme** 5.1.2

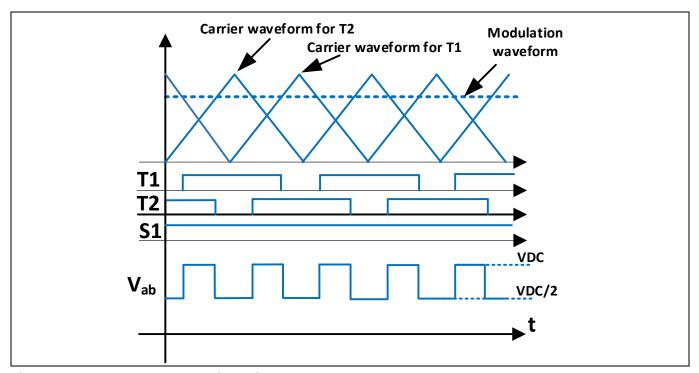

In previous section, it was shown how the V<sub>ab</sub> waveform is built by switching between various switching states, as listed in Table 3. In this section, it is explained how to generate the switching states using the PSPWM modulation scheme. In PSPWM, the modulation waveform described as  $D_{HF}(t)$  in Figure 40 and equation [12] is compared with carrier waveforms. In this five-level inverter there are two independent switching cells per half-bridge, so two carrier waveforms are needed with 360-degree/2 = 180-degree phase difference. Figure 41 shows how the Q1 and Q2 PWM pulses are generated by comparing carrier and modulation waveforms. Note that here the modulation waveform has been shown for only a small-time interval during the positive half-cycle (S1 = 1), which is why it appears flat and not sinusoidal in this figure. It is illustrated here how different switching states from Table 3 are generated. For example, when T1, T2 and S1 are all one (switching state 1, see Table 3)  $V_{ab} = V$  DC. Also, the existence of redundant switching states has been shown, T1 = 1, T2 = 0, S1 = 1 (switching state 2) and T1 = 0, T2 = 1, S1 = 1 (switching state 3). Both of these switching states give the same voltage level  $V_{ab} = VDC/2$ .

**Functional description**

Figure 40 Slow MOSFETs S1 signal and fast switches modulation waveform

Figure 41 T1, T2 pulse generation using PSPWM

**Functional description**

### 5.2 Passive component selection

In this section, it will be explained how to dimension and select major passive components in the multilevel inverter, including: output filter inductors ( $L_{fa}$  and  $L_{fb}$ ), output filter capacitor ( $C_{out}$ ), floating capacitors (CFa and CFb) and pre-charge resistors.

### 5.2.1 Output filter inductor design

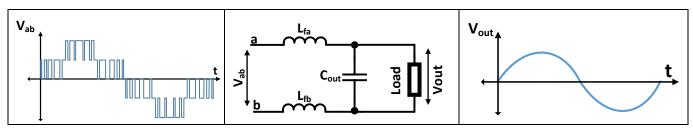

To generate the pure sinusoidal output voltage  $V_{out}$  from  $V_{ab}$ , this voltage is fed to an LC filter as shown in **Figure 42**. In this section, it is explained how to calculate the values of  $L_{fa}$  and  $L_{fb}$ .

Figure 42 Output filter configuration

To limit the current ripple the inductance value  $L_{fa}$  +  $L_{fb}$  must be sufficient. For the ANPC-FC inverter here, considering the design case:

Full-load power:  $S_{out} = 4000 \, VA$

Output voltage:  $V_{out(rms)} = 230 V$

Switching frequency:  $F_{SW} \approx 20 \ kHz$

Inductor peak-to-peak ripple:  $\Delta I_{pp} = 0.25 \times I_{pk}$

Where, as shown in **Figure 43**,  $I_{OUT}$  is the output (load) current, and  $I_L$  is the output filter inductor current assuming the output filter capacitor current is negligible to simplify the calculation.

Figure 43 Output current Iout, inductor filter IL

The inductance value is selected so that the inductor current maximum peak-to-peak ripple  $\Delta I_{pp}$  is limited to  $\Delta I_{pp} \leq 0.25 \cdot I_{pk}$  where  $I_{pk}$  is the peak of the sine wave output current at maximum rated load as calculated below:

$$I_{pk} = \frac{\sqrt{2}S_{out} \times \cos \varphi}{V_{out(rms)}} = \frac{\sqrt{2} \times 4000 \times \cos \theta}{230} = 24.6 A$$

[1]

#### **Functional description**

Where in [1] the power factor is assumed to be one (no phase shift between output current and output voltage  $\varphi$  = 0). The output capacitor in conjunction with the inductor needs to be large enough to filter out most of the ripple to provide a clean low frequency sine wave output. In a two-level inverter in full bridge configuration and with bipolar modulation, the output phase-to-phase voltage (Vab) switches between VDC and -VDC, therefore the peak-to-peak switched voltage across the output filter inductor is 2 VDC. For the two-level inverter the minimum inductance value necessary to limit peak-to-peak ripple to  $\Delta I_{pp}$  is given by:

$$L_{fil\_2level} \ge \frac{V_{DC}}{2 \times F_{sw} \times \Delta I_{pp}}$$

[2]

The derivation for this formula can be found in reference [6].

In the EVAL\_4KVA\_230VAC\_5LINV design, the effective output frequency will be twice the switching frequency because there are two switching cells. Also, while for a two-level inverter the amplitude of switched voltage is 2 VDC for a five-level inverter this value is VDC/2. Therefore, the minimum inductance will be:

$$L_{fil\_5level} = \frac{L_{fil\_2level}}{2(twice the switching frequncy) \times 4(lower switched voltage)}$$

[3]

$$L_{fil\_5level} \ge \frac{v_{DC}}{_{16 \times F_{SW} \times \Delta I_{pp}}}$$

[4]

Therefore, in the current design:

$$L_{fil\_5level} \ge \frac{400}{16 \times 20000 \times (0.25 \times 24.6)} = 203 \times 10^{-6} = 203 \,\mu H$$

[5]

The output inductance will therefore be divided between two 100  $\mu H$  filter inductors  $L_{Fa}$  and  $L_{Fb}$ .

#### **Output filter capacitor design** 5.2.2

Now that inductor filter value is known, output filter capacitor can be determined. The output filter cut-off frequency is set at one-tenth of effective output switching frequency. The output capacitor frequency can then be calculated as below:

$$C_{out} > (\frac{1}{2 \times \pi \times f_{cut}})^2 \times \frac{1}{L_{fil}} = (\frac{1}{2 \times \pi \times 4000 \, Hz})^2 \times \frac{1}{200 \times 10^{-6} H} = 7.9 \, \mu F$$

[6]

10 μF is a standard value that is selected here. Two 5 μF film capacitors will be connected in parallel.

#### Flying capacitor design **5.2.3**

Since all load currents go through flying capacitors, film-type capacitors must be used. Film capacitors have much lower ESR than electrolytic capacitors but are bulkier. The required minimum value of the flying capacitors depends on the allowed maximum voltage ripple, effective output switching frequency and capacitor current. Larger values of flying capacitors provide more robust performance but slow down the dynamic response of the system. The floating capacitor value must be large enough to limit the maximum voltage ripple that appears across it. This can be calculated as follows:

$$\Delta V_{FC\_max} = \frac{max[D_{FC} \times I_{FC}]}{C_{FC} \times 2 \times F_{SW}}$$

[7]

#### **Functional description**

where I<sub>FC</sub> is the floating capacitor current and D<sub>FC</sub> is the duty cycle of the floating capacitor current. As shown, the maximum ripple occurs at a switching period where  $D_{FC} \times I_{FC}$  is maximum. The exact value of  $\Delta V_{FC\ max}$  can only be calculated if the instantaneous value of DFC and IFC as functions of time and power factor are substituted into the above equation and  $\frac{d\Delta V_{FC\_max}}{dt}=0$  is then solved. To simplify the design process, the worst-case scenario for maximum voltage ripple is considered and used to approximate the floating capacitor value.

There will be a power factor value in which the maximum voltage ripple happens, and it can be approximated as follows:

$$\Delta V_{FC\_max}(worst\ case) = \frac{max[D_{FC}] \times max[I_{FC}]}{C_{FC} \times 2 \times F_{SW}} \approx \frac{1 \times I_{pk}}{C_{FC} \times 2 \times F_{SW}}$$

[8]

Therefore, the minimum possible floating capacitor value is calculated as:

$$C_{FC} \ge \frac{I_{pk}}{\Delta V_{FC\_max}(worst\ case) \times 2F_{sw}}$$

[9]

Assuming the maximum voltage ripple to be 20 percent of the steady state value of CFC voltage (100 V):

$$C_{FC} \ge \frac{24.6 \, A}{0.2 \times 100 \, V \times 2 \times 20000 \, W} \approx 30 \, \mu F$$

[10]

30 μF, 250 V film capacitors are selected as the floating capacitors for CFa (phase a floating capacitor) and CFb (phase b floating capacitor).

#### 5.2.4 **Pre-charging resistor selection**

Once the input voltage is applied to the inverter and before the MOSFETs start switching the flying capacitor and input capacitors must have been pre-charged to a value close enough to their steady-state value. Otherwise, some of the MOSFETs may have to withstand higher voltage and experience avalanche breakdown while other MOSFETs are withstanding much less voltage. To pre-charge the flying capacitors, resistors are installed in parallel with MOSFETs. There is no specific formula to calculate these resistor values but they should be selected so that when no MOSFET is switching and the overall inverter behavior is similar to a RC network, the steady-state value of flying capacitor voltage is within 10 percent of their nominal value (100 V in this case). Too-high resistor values would result in a long pre-charging time, and too-low values would contribute to unacceptable resistive power loss. In this inverter 75 k $\Omega$ , 150 k $\Omega$  and 220 k $\Omega$  are used. Refer to the schematic to see the location of these resistors in the inverter circuit.

**Functional description**

### 5.3 Power loss analysis

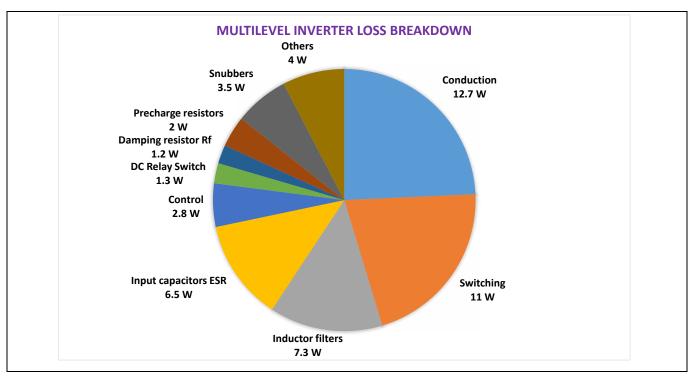

In this section of the application note, the major sources of power loss are identified. It will be shown using a pie chart how the total losses are distributed among all these sources. The numerical value of power loss contributed by each one of these sources is then calculated. To calculate the conduction loss of each MOSFET the RMS current value is needed, which will be analytically derived.

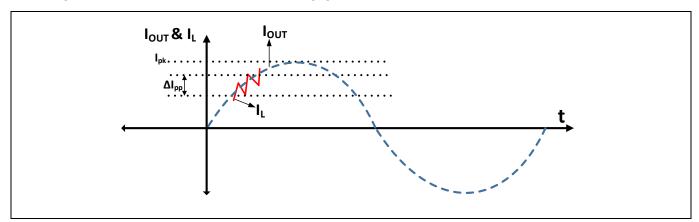

### 5.3.1 Identifying the major sources of power loss

In order to perform the power loss analysis, the major sources of loss must first be identified. These sources are shown in the figure below and listed in Table 4. MOSFETs in the system are classified as either slow (switching at line frequency,  $F_{line}$ ) or fast (switching at switch cell PWM frequency,  $F_{sw}$ ).

Figure 44 Main sources of inverter power loss

Table 4 Summary of power loss sources

| Fast MOSFETs                  | Slow<br>MOSFETs | DC relay<br>switch | Input<br>capacitor | Inductor<br>filters | Pre-charge resistors | Snubbers       | Damping resistors |

|-------------------------------|-----------------|--------------------|--------------------|---------------------|----------------------|----------------|-------------------|

| Conduction and switching loss | Conduction loss | Conduction loss    | ESR loss           | Copper loss         | Resistive<br>loss    | Resistive loss | Resistive loss    |

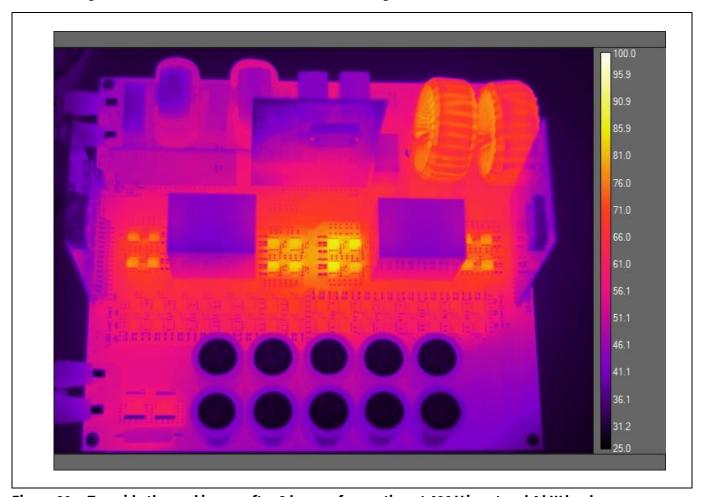

It can be seen in the loss breakdown pie chart shown below that the losses are distributed among many sources of power dissipation. This is the main reason why this design doesn't need heatsink or fan for thermal management. While in a traditional two-level inverter most power dissipation is concentrated in the power semiconductors, in this design the semiconductor loss is only around 0.5 percent of total power.

#### **Functional description**

Figure 45 Multilevel inverter loss breakdown at 4 kW load

### 5.3.2 Analytical derivation of MOSFET RMS current

In this section, duty cycle and MOSFET RMS current are calculated for phase a. Due to the symmetrical nature of this topology the same values can also be applied to phase b.

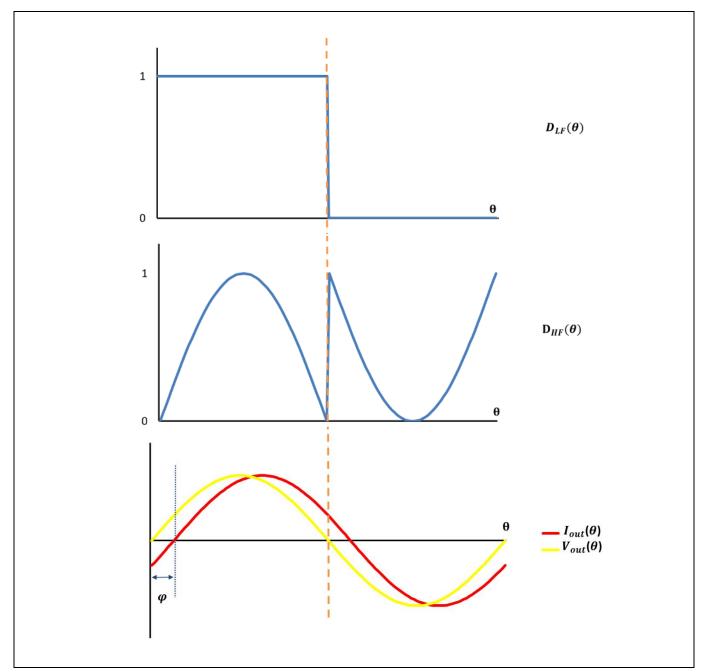

The slow MOSFETs duty cycle D<sub>LF</sub> (see **Figure 40** and **Figure 46**) is considered as an ideal square waveform.

$$D_{LF}(\theta) = \begin{cases} 1, & 0 \le \theta < \pi \\ 0, & \pi \le \theta < 2\pi \end{cases}$$

[11]

The long-term average of fast MOSFETs duty cycle is equal to modulation waveform D<sub>HF</sub> and can be written as below:

$$D_{HF}(\theta) = \begin{cases} m\sin(\theta), & 0 \le \theta < \pi \\ 1 + m\sin(\theta), & \pi \le \theta < 2\pi \end{cases}$$

[12]

Where m is the modulation index and  $\theta = \omega t$ ,  $\omega = 2\pi \cdot F_{line}$ , and  $F_{line}$  is line frequency equal to 60 Hz.

The output load current and output voltage are assumed to be fully sinusoidal and can be described using the below equations:

$$I_{out}(t) = I_{pk}\sin(\theta - \varphi)$$

[13]

$$V_{out}(t) = V_m \sin(\theta) \tag{14}$$

For simplicity, the output current  $I_{OUT}$  is assumed to be equal to inductor filter current, disregarding the filter capacitor current.

#### **Functional description**

There are 48 MOSFETs in the EVAL\_4KVA\_230VAC\_5LINV inverter design (other than the inrush current resistor bypass HV MOSFET). The RMS current value of all the fast MOSFETs is identical. However, the slow MOSFETs are divided into two separate groups:

- 1. The slow MOSFETs in top and bottom position (STBM).

- 2. The slow MOSFETs in the middle position (SMM).

The current values of all MOSFETs in STBM positions are equal to each other. The same is true for all the MOSFETs in SMM positions. However, the current value of STBM MOSFETs is different from SMM MOSFETs.

Figure 46 a) Slow MOSFET duty cycle, b) fast MOSFETs duty cycle, c) output load current and voltage

#### **Functional description**

In a simple buck converter or a two-level inverter, the RMS current of each MOSFET depends only on the load current and duty cycle of that specific MOSFET. However, in the multilevel inverter the current that is passing through each MOSFET not only depends on the load current and duty cycle of that specific MOSFET but also the duty cycle of all the other MOSFETs in the current path. The term "effective duty cycle" is used here to account for this. The effective duty cycle of one the fast MOSFETs,  $(D_{FM})$   $T_1$  (see **Figure 8**) is derived here. The amplitude of effective duty cycle of all other fast MOSFETs are the same as  $T_1$ . The effective duty cycle of  $T_1$  can be calculated as below: as below [8]:

$$D_{FM}(\theta) = \begin{cases} D_{HF}(\theta) \times D_{LF}(\theta), & 0 \le \theta < \pi \\ D_{HF}(\theta) \times (1 + D_{LF}(\theta)), & \pi \le \theta < 2\pi \end{cases}$$

[15]

By applying equations [11] and [12]:

$$D_{FM}(\theta) = \begin{cases} m \sin(\theta), & 0 \le \theta < \pi \\ 1 + m \sin(\theta), & \pi \le \theta < 2\pi \end{cases}$$

[16]

The effective duty cycle of slow top MOSFETs (D<sub>STM</sub>) can be written as below:

$$D_{STM}(\theta) = \begin{cases} D_{HF}(\theta) \times D_{LF}(\theta), & 0 \le \theta < \pi \\ D_{HF}(\theta) \times D_{LF}(\theta), & \pi \le \theta < 2\pi \end{cases}$$

[17]

By applying equations [11] and [12]:

$$D_{STM}(\theta) = \begin{cases} m\sin(\theta), & 0 \le \theta < \pi \\ 0, & \pi \le \theta < 2\pi \end{cases}$$

[18]

The effective duty cycle of slow middle MOSFETs (D<sub>SMM</sub>) can be written as below:

$$D_{SMM}(t) = \begin{cases} (D_{HF}(\theta))' \times D_{LF}(\theta), & 0 \le \theta < \pi \\ 0, & \pi \le \theta < 2\pi \end{cases}$$

[19]

By applying equations [11] and [12]:

$$D_{SMM}(t) = \begin{cases} 1 - m\sin(\theta), & 0 \le \theta < \pi \\ 0, & \pi \le \theta < 2\pi \end{cases}$$

[20]

The fast MOSFET RMS current equation is derived as follows:

$$I_{FM(RMS)} = \sqrt{\frac{1}{2\pi}} \int_0^{2\pi} [I_{FM}(\theta)]^2 d\theta = \sqrt{\frac{1}{2\pi}} \int_0^{2\pi} [I_{out}(\theta)]^2 D_{FM}(\theta) dt$$

[21]

$$= \sqrt{\frac{1}{2\pi} \int_0^{\pi} I_{pk}^2 (\sin(\theta - \varphi))^2 m \sin(\theta) d\theta + \frac{1}{2\pi} \int_{\pi}^{2\pi} I_{pk}^2 (\sin(\theta - \varphi))^2 (1 + m \sin(\theta)) d\theta} = \frac{I_{pk}}{2}$$

For slow top and bottom MOSFETs the current value is [8]:

$$I_{STM(RMS)} = \sqrt{\frac{1}{2\pi}} \int_0^{2\pi} [I_{STM}(\theta)]^2 d\theta = \sqrt{\frac{1}{2\pi}} \int_0^{2\pi} [I_{out}(\theta)]^2 D_{STM}(\theta) dt$$

[22]

$$= \sqrt{\frac{1}{2\pi} \int_0^{\pi} I_{pk}^2 (\sin(\theta - \varphi))^2 m \sin(\theta) d\theta} = \sqrt{\frac{m I_{pk}^2 (\cos^2 \varphi + 1)}{3\pi}}$$

$$I_{SMM(RMS)} = \sqrt{\frac{1}{2\pi} \int_0^{2\pi} [I_{SMM}(\theta)]^2 dt} = \sqrt{\frac{1}{2\pi} \int_0^{\pi} I_{pk}^2 (\sin(\theta - \varphi))^2 (1 - m\sin(\theta)) d\theta}$$

[23]

#### **Functional description**

$$= \sqrt{\frac{{I_{pk}}^2}{4} + \frac{m{I_{pk}}^2(\sin^2\varphi - 2)}{3\pi}}$$

Note that as can be seen in the multilevel inverter schematic, each MOSFET is paralleled with another MOSFET. The derived MOSFET equations therefore represent the total current shared between two parallel MOSFETs. All information needed to calculate conduction loss is now available. The equations above will be used in the following section to determine conduction loss.

#### 5.3.3 Conduction loss calculation

Now that MOSFETs RMS current expressions are available, the corresponding conduction losses can be calculated. First modulation index is calculated as shown below:

$$m = \frac{\sqrt{2} \times V_{out(rms)}}{V_{DC}} = \frac{\sqrt{2} \times 230 \text{ V}}{400 \text{ V}} = 0.81$$

[24]

The fast MOSFET RMS current is therefore:

$$I_{FM(RMS)} = \frac{I_{pk}}{2} = \frac{24.6 \,A}{2} = 12.3 \,A$$

[25]

Now assuming the power factor is ( $\varphi = 0$ ), then for the top and bottom MOSFETs the RMS current is:

$$I_{STM(RMS)} = \sqrt{\frac{mI_{pk}^{2}(\cos^{2}\varphi + 1)}{3\pi}} = \sqrt{\frac{0.81 \times (24.6 A)^{2}(\cos^{2}\theta + 1)}{3\pi}} = 10.2 A$$

[26]

The slow middle MOSFET RMS current is:

$$I_{SMM(RMS)} = \sqrt{\frac{I_{pk}^2}{4} + \frac{mI_{pk}^2(\sin^2\varphi - 2)}{3\pi}} = \sqrt{\frac{(24.6 \text{ A})^2}{4} + \frac{0.81 \times (24.6 \text{ A})^2(\sin^2\theta - 2)}{3\pi}} = 6.87 \text{ A}$$

[27]

Now to calculate total conduction loss, remember the following points:

- The calculated RMS values in equations (25), (26) and (27) give the current through one pair of parallel MOSFETs.

- As can be seen in the thermal image shown in the results section, the slow MOSFET steady-state

temperature at full power reaches 70°C and the fast MOSFET temperature reaches 85°C. Therefore, it is

necessary to use the corresponding drain-to-source on-resistance at those temperatures to calculate

conduction loss.

- From the datasheet  $R_{ds(on)@85^{\circ}C} = 11 \, m\Omega$  and  $R_{ds(on)@70^{\circ}C} = 10 \, m\Omega$ .

- There are 16 fast MOSFETs, 16 slow MOSFETs in the top and bottom positions, and 16 slow MOSFETs in middle positions.

Considering the above mentioned points, total MOSFET-related conduction loss is given by:

$$P_{CON} = 16 \times \left[ R_{ds(on)@85^{\circ}C} \times \left( \frac{I_{FM(RMS)}}{2} \right)^{2} \right] + 16 \times \left[ R_{ds(on)@70^{\circ}C} \times \left( \frac{I_{STBM(RMS)}}{2} \right)^{2} \right]$$

$$+ 16 \times \left[ R_{ds(on)@70^{\circ}C} \times \left( \frac{I_{SMM(RMS)}}{2} \right)^{2} \right]$$

[28]

#### **Functional description**

$$= 16 \times \left[11 \ m\Omega \times \left(\frac{12.3 \ A}{2}\right)^{2}\right] + 16 \times \left[10 \ m\Omega \times \left(\frac{10.2 \ A}{2}\right)^{2}\right] + 16 \times \left[10 \ m\Omega \times \left(\frac{6.87 \ A}{2}\right)^{2}\right] = 12.7 \ W$$

#### 5.3.4 **Switching loss calculation**

Calculation of switching loss is more challenging than conduction loss. Layout design heavily affects switching loss, and circuit parasitic cannot be easily quantified. Also, unlike conduction loss where the RMS value of MOSFET current suffices for the calculations, for switching loss the instantaneous current value is needed. Therefore, it would be very difficult to accurately calculate switching loss values. In this section the goal is to show how to obtain reasonable estimates of the switching loss. For more detailed and more accurate measurement of switching loss in a multilevel inverter (or a general inverter), see reference [9].

As stated, there are 48 MOSFETs in this inverter. 32 of these are switching at line frequency with negligible switching loss (slow MOSFETs). In this section the focus is therefore on calculating the switching loss contributed by the 16 fast MOSFETs.

To calculate the switching loss, gate driver IC, MOSFET and gate driving circuit parameters need to be considered. The 2EDF7275F gate driver IC parameters are as follows:

| $R_{dr\_on} = 0.85 \Omega$  | Gate driver IC internal resistor, source path |

|-----------------------------|-----------------------------------------------|

| $R_{dr\_off} = 0.35 \Omega$ | Gate driver IC internal resistor, sink path   |

| $V_{*} = 12 V_{*}$          | Driving voltage                               |

From the BSC093N15NS5 datasheet, the following parameters are extracted:

| $V_{plateau} = 5.7 V$          | Plateau voltage                                                                          |

|--------------------------------|------------------------------------------------------------------------------------------|

| $Q_{sw} = 13.4  nC$            | Switching charge; this is the amount of charge needed to be transferred during switching |

|                                | transient                                                                                |

| $R_{g\ internal} = 0.9 \Omega$ | Internal MOSFET gate resistance                                                          |

From the multilevel inverter circuit:

| $R_{gon} = 54.6 \Omega$ | Gate driving resistor in the turn-on path. This resistor is selected to be large enough to |

|-------------------------|--------------------------------------------------------------------------------------------|

|                         | mitigate ringing and improve EMI.                                                          |

| $R_{goff} = 1 \Omega$   | Gate driving resistance in the turn-off path. This resistor is selected to be small enough |

|                         | to minimize turn-off switching loss.                                                       |

MOSFET turn-on time can be calculated as follows:

$$I_{g\_on} = \frac{V_{dri} - V_{plateau}}{R_{g_{on}} + R_{dr\_on} + R_{g\_internal}} = \frac{12 \, V - 5.7 \, V}{54.6 \, \Omega + 0.85 \, \Omega + 0.9 \, \Omega} = 0.11 \, A \tag{29}$$

$$t_{on} = \frac{Q_{SW}}{I_{Q_{on}}} = \frac{13.4 \, nC}{0.11 \, A} = 122 \, ns$$

[30]

Turn-off time can be calculated as follows:

#### **Functional description**

$$I_{g\_off} = \frac{v_{plateau}}{R_{g_{off}} + R_{dr\_off} + R_{g\_internal}} = \frac{5.7 \, V}{1 \, \Omega + 0.35 \, \Omega + 0.9 \, \Omega} = 2.5 \, A \tag{31}$$

2EDF7275F gate driver sink capability is 4 A. Since one gate driver channel drives two MOSFETs in parallel, sink capability per MOSFET will be capped at 2 A.

$$t_{off} = \frac{Q_{sw}}{I_{g off}} = \frac{13.4 \, nC}{2 \, A} = 6.7 \, ns$$

[32]

Note that due to the existence of parasitic inductance the real t<sub>off</sub> is most likely higher than 6.7 ns. To calculate switching loss, other than calculating turn-on and turn-off time,  $Q_{oss}$  and  $Q_{rr}$  parameters also need to be estimated. From the datasheet  $Q_{oss}(@75V) = 91 \, nC$ . Assuming the  $C_{oss}$  curve in the 75 V to 100 V region is approximately linear:

$$Q_{oss}(@100 V) \approx Q_{oss}(@75 V) \times \frac{100 V}{75 V} \approx 121 nC$$

[33]

Also from the datasheet:

$$Q_{rr}\left(@I_F=44~A, @\frac{dI_F}{dt}=100~\frac{A}{\mu s}\right)=58~nC$$

.

In the datasheet, the Q<sub>rr</sub> value is given only at this specific test condition. However, the value of di/dt is highly dependent on circuit and layout parameters like R<sub>gon</sub> and parasitic inductance. Furthermore, note that in an inverter the body diode current (I<sub>F</sub>) is not a constant DC value but follows a sinusoidal form. This means at each switching instance depending on the value of load current the Q<sub>rr</sub> value is going to be different. This makes the accurate calculation of Q<sub>rr</sub>-related loss in inverters somewhat challenging. However, since the switching frequency is relatively low (20 kHz), and R<sub>gon</sub> is high (so dIF/dt is low) the Q<sub>rr</sub>-related loss is not a significant portion of the overall loss. As a result, error in loss calculation due to the rough approximation of  $Q_{rr}$  is not substantial. Therefore, the datasheet value of  $Q_{rr} = 58 \text{ nC}$  may be used in the loss calculation.

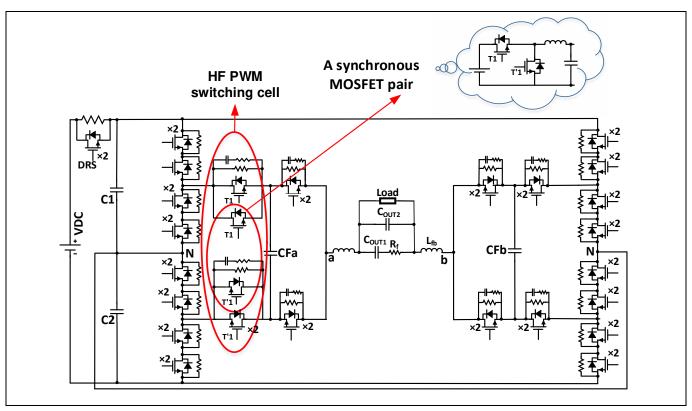

To simplify switching loss calculation the 16 fast MOSFETs are considered as four identical HF switching cells. Since MOSFETs have been used in parallel, each cell consists of two synchronous MOSFET pairs, as shown in Figure 47. To calculate the total switching loss the switching loss of a synchronous MOSFET pair is calculated similar to the way it is done in a synchronous buck converter. The results can then be multiplied by 8 (4 cells  $\times$  2 synchronous pairs).

#### **Functional description**

**Demonstration of cells and synchronous MOSFET pairs** Figure 47

The top MOSFET in the synchronous pair at the positive half-cycle of load current experiences a hard-switching turn-on transient while the bottom MOSFETs turn on and off with its body conducting. That means the bottom MOSFET overlap switching loss (overlap of current and voltage) is negligible due to zero voltage switching (ZVS). However, the bottom MOSFET body diode experiences hard commutation and its Q<sub>rr</sub> is dissipated in the top MOSFET. During the negative half-cycle of load current, the bottom MOSFET experiences hard-switching and the top MOSFET enjoys ZVS. However, due to the symmetrical structure of the inverter the switching loss calculations can be written with the assumption that current is always in the positive half-cycle. The table below summarizes the switching loss calculations for a synchronous pair, assuming the current is positive:

| Switching loss              | Formula                                                           | Calculation                                                                                                   | Comment                                                                                                                                                                        |

|-----------------------------|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $P_{SW\_TOP\_ON\_overlap}$  | $V_{ds} \frac{(\frac{2I_{pk}}{\pi})}{2} \frac{t_{on}}{2} F_{sw}$  | $100 V \frac{\left(\frac{2 \times 24.6 A}{\pi}\right)}{2} \frac{122 ns}{2} \times 20000 Hz$ $= 0.96 W$        | To consider the shape of current which is sinusoidal its average value $\frac{2I_{pk}}{\pi}$ is used. Also, a division by 2 is needed since there are two MOSFETs in parallel. |

| $P_{SW\_TOP\_OFF\_overlap}$ | $V_{ds} \frac{(\frac{2I_{pk}}{\pi})}{2} \frac{t_{off}}{2} F_{sw}$ | $100 V \frac{\left(\frac{2 \times 24.6 A}{\pi}\right)}{2} \times \frac{6.7 ns}{2} \times 20000 Hz$ $= 0.05 W$ | Turn-off loss due to overlap of<br>voltage and current is much<br>smaller then turn-on overlap<br>loss                                                                         |

| $P_{SW\_TOP\_Qoss}$         | $\frac{Q_{oss}V_{ds}F_{sw}}{2}$                                   | $\frac{121  nC  \times 100  V  \times 20000  Hz}{2} = 0.12  W$                                                | C <sub>oss</sub> -related charge for top<br>MOSFET                                                                                                                             |

### **Functional description**

| $P_{SW\_BOT\_Qoss}$  | $\frac{Q_{oss}V_{ds}F_{sw}}{2}$ | $\frac{121  nC \times 100  V \times 20000  Hz}{2} = 0.12  W$ | C <sub>oss</sub> -related charge for bottom<br>MOSFET                   |

|----------------------|---------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------|

| $P_{SW\_Qrr}$        | $Q_{rr}V_{ds}F_{sw}$            | $58  nC \times 100  V \times 20000  Hz = 0.12  W$            | Q <sub>rr</sub> of the bottom MOSFET is<br>dissipated in the top MOSFET |

| P <sub>SW_Gate</sub> | $Q_g V_{dri} F_{sw}$            | $33  nC \times 12  V \times 20000  Hz = 0.008  W$            | This is per MOSFET loss, not per synch pair.                            |

The total switching loss per synchronous pair is:

$$P_{SW\_one\_pair} = P_{SW\_TOP\_ON\_overlap} + P_{SW\_TOP\_OFF\_overlap} + P_{SW\_TOP\_Qoss} + P_{SW\_BOT\_Qoss} + P_{SW\_Orr} + 2 \times P_{SW\_Gate} = 1.38 \, W$$

[34]

There are eight pairs, therefore the total switching loss of the inverter is:

$$P_{SW\_total} = 8 \times P_{SW\_one\_pair} = 11 W$$

[35]

Also note that due to the small dead-time and relatively low switching frequency the body diode conduction loss is insignificant and is not calculated here.

**Functional description**

#### 5.3.5 Input capacitor ESR loss calculation

One major source of loss is the input capacitor ESR loss. To determine this loss first the input capacitor RMS current is calculated as follows, see reference [10]:

$$I_{Cin(RMS)} = \sqrt{mI_{pk}^{2} \left( \left( \frac{3 + \cos 2\varphi}{3\pi} \right) - \left( \frac{m\cos^{2}\varphi}{4} \right) \right)}$$

[36]

$$= \sqrt{0.81 \times (24.6 \, A)^2 \left( \left( \frac{3 + \cos 0}{3\pi} \right) - \left( \frac{0.81 \times \cos^2 0}{4} \right) \right)} = 10.43 \, A$$

The capacitor ESR calculated from the datasheet yields a very conservative value. To acquire more realistic ESR values, a network analyzer should be used. Using a network analyzer, the ESR value for the LGW2E391MELA30 390  $\mu$ F, 250 V electrolytic capacitor from Nichicon is measured to be approximately 150 m $\Omega$ . There are a total of ten electrolytic capacitors at the input of the EVAL\_4KVA\_230VAC\_5LINV inverter, installed in parallel and series as shown in the schematic. Hence, the total ESR is:

$$ESR_{eqv} = \frac{2 \times ESR}{5} = 0.06 \,\Omega \tag{37}$$

From equations [36] and [37], the total ESR loss at the input electrolytic capacitors is calculated as:

$$P_{ESR(Cin)} = ESR_{eav} \times (I_{Cin(RMS)})^2 = 6.52 W$$

[38]

#### **Output inductor filter losses** 5.3.6

The power loss at the filter inductors consists of copper loss and core loss. The core loss is much smaller than copper loss and is not calculated here. The DC series resistance of inductors  $R_L$  is around 12 m $\Omega$  per inductor at 70°C (70°C is the inductor winding temperature at steady-state full power, as displayed in the thermal picture in Figure 79). To calculate the inductor copper loss, the output filter capacitor current can be neglected so that the inductor current can be assumed equal to the output current.

$$I_{out(rms)} = \frac{I_{pk}}{\sqrt{2}} = 17.4 A$$

[39]

Total copper loss in inductor filters is therefore:

$$P_L = 2 \times R_{L@70^{\circ}C} \times (I_{out(rms)})^2 = 2 \times 12 \ m\Omega \times (17.4 \ A)^2 = 7.3 \ W$$

[40]

#### **Output capacitor damping resistor losses** 5.3.7

As explained in the passive component selection section, two 5 µF film capacitors are used in parallel at the output. A resistor ( $R_f = 6.6 \Omega$ ) is included in series with one of these 5  $\mu$ F capacitors ( $C_{OUT1}$ ) to dampen the resonance effect of the output filter. The conduction loss due to this resistor is calculated as follows:

$$I_{R\_damp} = \frac{V_{out}}{\left(\frac{1}{C_{out1} \times 2 \times \pi \times f_{line}}\right)} = V_{out} \times C_{out1} \times 2 \times \pi \times f_{line} = 0.43 A$$

[41]

**Functional description**

$$P_{R\_damp} = R_f \times (I_{R\_damp})^2 = 6.6 \,\Omega \times (0.43 \,A)^2 = 1.2 \,W$$

[42]

### 5.3.8 Pre-charging resistor losses

There are 24 pre-charging resistors in this inverter. Eight are 75 k $\Omega$ , 12 are 150 k $\Omega$  and four are 220 k $\Omega$ . Total resistive loss due to pre-charge resistors is calculated as:

$$P_{pre\_charge} = \sum_{i=1}^{i=24} \frac{(V_{ds})^2}{R_{pre}(i)} = 8 \times \frac{(100 \, V)^2}{75 \, k\Omega} + 12 \times \frac{(100 \, V)^2}{150 \, k\Omega} + 4 \times \frac{(100 \, V)^2}{220 \, k\Omega} = 2.05 \, W$$

[43]

### 5.3.9 Snubber resistor losses

There are eight snubbers installed in parallel with the 16 fast MOSFETs. The corresponding power loss is:

$$P_{Snubber} = 8 \times C_{Snub}(V_{ds})^2 F_{SW} = 8 \times 2.2 \, nF \times (100)^2 \times 20000 \, Hz = 3.52 \, W$$

[44]

### 5.3.10 DCR switching losses

The DC relay switch (DCR) is used to bypass the inrush current limiting resistor. It also contributes to inverter total power loss. Because this switch turns off only infrequently the contributed losses are only conductive. To calculate this loss the inverter input current is first calculated:

$$I_{in\_DC} = \frac{S_{out} \times \cos \varphi}{V_{DC}} = \frac{4000 \text{ W} \times \cos \theta}{400 \text{ V}} = 10 \text{ A}$$

[45]

There are two IPT60R022S7 MOSFETs installed in parallel to form the DRC switch. From the datasheet:  $R_{ds\_DRS(on)@25^{\circ}\text{C}} = 20~m\Omega$  and  $R_{ds\_DRS(on)@60^{\circ}\text{C}} = 26~m\Omega$ , where 60°C is the steady-state temperature of these two MOSFETs at full power. Also, it is assumed that the input current is pure RMS,  $I_{in\_DC} = I_{in\_rms}$ . Now the conduction loss can be calculated as follows:

$$P_{DRS} = \frac{R_{ds\_DRS(on)@60^{\circ}C}}{2} \times (I_{in\_}rms)^2 = \frac{26 \, m\Omega}{2} \times (10 \, A)^2 = 1.3 \, W$$

[46]

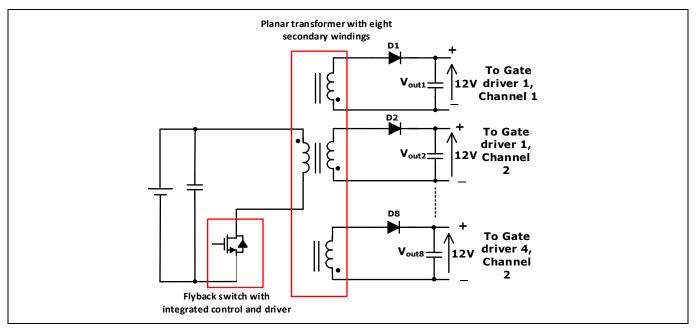

### 5.4 Gate driver card design

Designers may be concerned by the need for a high number of isolated gate drivers in multilevel inverters and the fact that for each isolated gate driver channel one isolated power supply is required. However, in this section it is explained how a cost effective simple flyback-based power supply (less than 1 W) with eight outputs is used to power four dual-channel isolated gate drivers. This eight-output power supply is incorporated with four isolated gate driver 2EDF7275F ICs on one single daughter board. For the complete system, three daughter boards are needed. **Figure 48** shows the basic schematic of the eight-output auxiliary power supply. **Figure 29** shows the detailed schematic. A planar transformer simplifies the design, reducing cost and improving manufacturability.

To accommodate the eight outputs for creepage and clearance, the flyback power supply is laid out on a six-layer PCB. On each middle layer the secondary windings for two outputs are placed. The primary winding is located on the top layer. The primary winding has six turns, while each one of the secondary windings has three turns. The LT8301 is used as for the flyback switch. More detailed information on designing this flyback power supply can be found in reference [11].

**Functional description**

Figure 48 Flyback-based less-than 1 W power supply with eight outputs on gate driver board

#### 5.5 **Supervisory functions**

#### 5.5.1 DC input voltage sensing

The inverter is designed to operate over a specified DC input range indicated in section 2. It is therefore necessary to monitor the input voltage to prevent operation outside of these limits by disabling all PWM gate drives and waiting until the correct voltage input is available. The DC bus is capacitively divided to provide the neutral point for each side of the multilevel inverter. Two separate resistor dividers monitor the total input bus DC voltage to provide input Vin\_S to the U5 and the split rail DC voltage from 0 V to the neutral point to provide VinL\_S. The firmware is therefore able to monitor the input voltage and neutral point. LEDs located on the control card indicate if either of these voltages are outside the correct range.

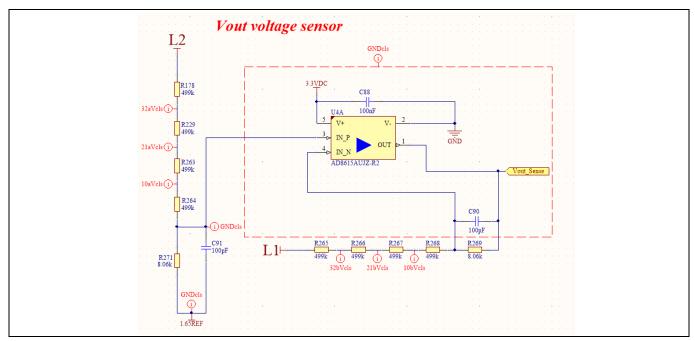

#### 5.5.2 AC output voltage sensing

The AC output of the inverter appears after LC filter and EMI filter stage between the node L1 and L2, as shown in Figure 49. Resistor dividers referenced to 0 V are used to scale down these two voltages (L1 and L2), which are then fed to a differential amplifier based around U4A to produce a differential signal with a 1.65 V offset, scaled so as not to exceed 0 V or 3.3 V. This signal Vout\_Sense is fed to an ADC input of U5 so that the firmware is able to periodically sample this LF sine wave signal. The results can be used to calculate the inverter RMS output voltage and also determine phase shift. This could be used to regulate AC real and reactive power components in a grid-tied scenario; however, the basic firmware installed in the inverter does NOT support this.

### **Functional description**

Figure 49 AC output voltage monitoring circuit

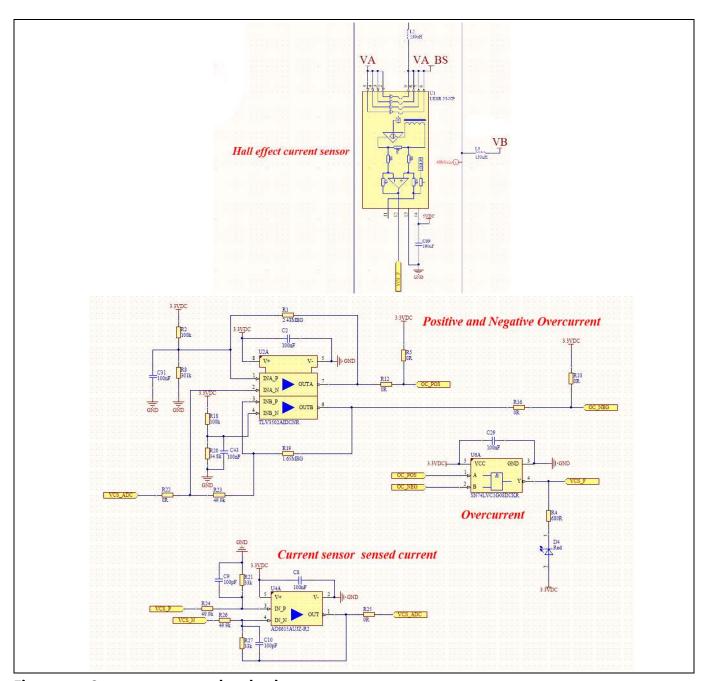

#### 5.5.3 **Output current sensing**

The EVAL\_4KVA\_230VAC\_5LINV uses a Hall sensor U1 (LKSR 25-NP) to detect the AC output current, which is nominally rated at 25 A<sub>RMS</sub> but can measure up to +/-85 A and withstand up to 20 x 25 A<sub>RMS</sub> before sustaining damage. The number of primary turns is one, since all of the four primary windings are connected in parallel to support maximum current. The secondary supply voltage is 5 V with a 2.5 V internal reference so that the galvanically isolated output voltage will be 2.5 V at zero input current. The sensitivity is of 25 mV/A, which allows sensing of more than 50 A<sub>RMS</sub> without reaching the upper and lower voltage limits 0 V and 5 V.

The output from U1 (shown as VCS\_P on the schematics) is connected from the power board to the control card through connector X8, where it is then connected to an amplifier circuit that scales it down through U4A to shift the offset down to 1.675 V, which is half the 3.3 V supply voltage of the microcontroller U5 that sets the maximum limit for analog inputs. The firmware samples the output current periodically, performing analog to digital conversions so that the instantaneous current can be sampled.

The scaled output current feedback signal to U5 is also fed to the dual comparator U2. One of the comparators detects a high positive peak and the other detects a high negative peak, with each output transitioning negative rapidly in the event of a high current peak. The two outputs (OC\_POS and OC\_NEG) are fed to an AND gate, whose output transitions low if either of the two signals goes low to provide a fast fault indication to U5. A high-to-low transition at this input triggers the U5 to shut off all of the PWM gate drive outputs much more rapidly than the time it would take for an analog to digital conversion and result check to take place.

### **Functional description**

Figure 50 Output current sensing circuits

**Embedded firmware**

#### **Embedded firmware** 6

#### 6.1 XMC<sup>™</sup> 4000 series microcontroller

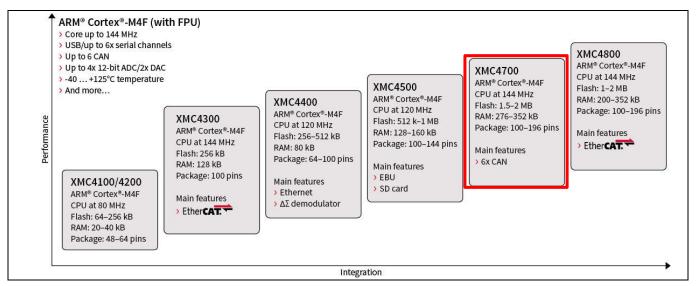

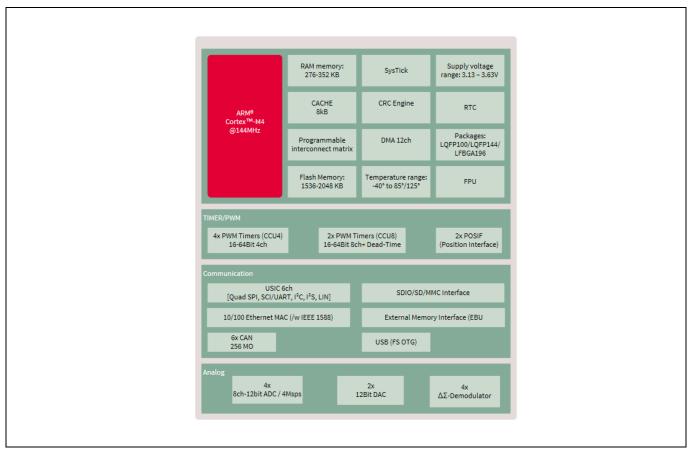

The XMC<sup>™</sup> microcontroller family based on ARM<sup>®</sup> Cortex<sup>®</sup>-M cores, is suitable for real-time critical applications where an industry-standard core is needed. It is dedicated to applications in the segments of power conversion, factory and building automation and transportation, as well as home appliances. All XMC4000 devices are powered by ARM® Cortex®-M4 with a built-in DSP instruction set. The single precision floating point unit, direct memory access (DMA) feature and memory protection unit (MPU) are state-of-the-art for all devices. XMC4000 series processors run with clock speeds ranging from 80 to 144 MHz for the core and a comprehensive set of common, fast, and precise analog/mixed-signal, timer/PWM and communication peripherals.

There are several variants of the XMC4000 series, shown below:

Figure 51 XMC4000 series sub-groups

The growing complexity of today's energy-efficient embedded control applications demands microcontroller solutions with higher-performance CPU cores featuring DSP and FPU capabilities. Power converter designs are subject to ever-increasing requirements fueled by customer demands or industry association guidelines (such as higher power density, communication, modularity or the 80 Plus Titanium efficiency standard). Semiconductor technology advances have allowed MCU manufacturers to develop a new class of MCUs, optimized for digital power conversion applications in terms of features and price point, motivating power supply designers to use digital control for SMPS. The XMC4700 family of microcontrollers takes advantage of Infineon's decades of experience in the industrial market to provide an optimized solution to meet the performance challenges of today's embedded control applications, which is why it is has been selected for this application.

#### Summary of features:

- 1536 to 2048 kB Flash, 276 to 352 kB RAM

- Supply voltage range: 3.13 to 3.63 V

- USIC 6-channel [quad SPI, SCI/UART, I<sup>2</sup>C, I<sup>2</sup>S, LIN]

- 2x PWM timers (CCU8), 16 to 64-bit 8-channel+ dead-time

- 6x CAN, 256 MO

#### **Embedded firmware**

- Peripherals clock: 144 [MHZ]

- Core frequency: 144 [MHZ]

- 4x ΔΣ-demodulator

- External memory interface (EBU)

- Package: LQFP144/LQFP100/LFBBGA196

- Temperature range: -40°C...85°C/125°C

- 10/100 Ethernet MAC (/w IEEE 1588)

- SDIO/SD/MMC interface

- Safety package supporting SIL-2/3

- Rich connectivity: 2x CAN nodes, 4-channel serial COM unit (configurable to SPI, I<sup>2</sup>C, I<sup>2</sup>S, UART), USB FS

- Up to 4 x 12-bit ADC with a sample time of 70 ns ensures fast reaction times and tighter control loops

- 4-channel 150 ps HRPWM timer (XMC4200/4400 series)

XMC4700 core and peripherals Figure 52

**Embedded firmware**

#### 6.2 **Digital control implementation**

The digital control daughter card designed for the five-level inverter provides the PWM signals to the gate drivers. These are derived from three of the PWM modules of the XMC4700. Analog inputs are used for sensing the DC input voltage and flying capacitor voltages. The output voltage is sensed via a differential amplifier and the output current is sensed via the hall effect current sensor located on the main power board, whose output is fed to the digital control board. Comparators are used to detect positive and negative over-currents, which are signaled to the microcontroller to trigger a rapid shutdown. The microcontroller also operates the inrush current bypass circuit.

The XMC4700 option was chosen because the functionality of the PWM modules is necessary to provide the required gate-drive signals. A clock speed of 144 MHz provides sufficient granularity of adjustment for the PWM outputs switching at 20 kHz or higher.

The 144-pin PG-LQFP-144 packaged XMC4700-F144F2048 variant has 32 kB of Flash memory and 2048 kB of SRAM, and more than enough I/O pins to support the required functions.

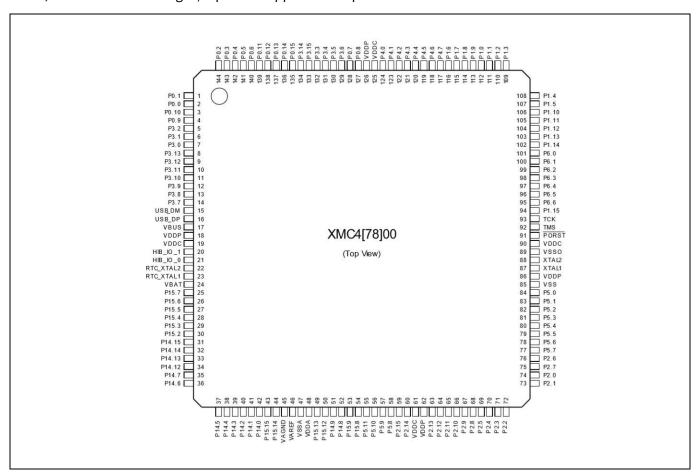

Figure 53 XMC4700 PG-LQFP-144 pin configuration (top view)

The diagram above shows the input and output connections listed in the following table:

**Embedded firmware**

XMC4700-F144F2048 I/O functions (unconnected pins are not included) Table 5

| Pin             | Name  | Function           | Description                                           |

|-----------------|-------|--------------------|-------------------------------------------------------|

| 18, 62, 86, 126 | VDDP  |                    | 3.3 V DC regulated                                    |

| 19, 61, 90, 125 | VDDC  |                    | 1.3 V DC regulated                                    |

| 46              | VDDA  |                    | 3.3 V DC regulated                                    |

| 48              | VAREF |                    | 3.3 V DC regulated                                    |

| 45              | VAGND |                    | 0 V                                                   |

| 85              | VSS   |                    | 0 V                                                   |

| 47              | VSSA  |                    | 0 V                                                   |

| 89              | VSSO  |                    | 0 V                                                   |

| 87              | XTAL1 | External clock     | Crystal oscillator                                    |

| 88              | XTAL2 | External clock     | Crystal oscillator                                    |

| 92              | TMS   |                    |                                                       |

| 93              | TCK   |                    |                                                       |

| 2               | P0.0  | Digital output/PWM | S'1 (Q17, Q22) LF gate drive (see Table 2)            |

| 1               | P0.1  | Digital output/PWM | T'2 (Q42) HF gate drive (see Table 2)                 |

| 144             | P0.2  | Digital output/PWM | T'1 (Q41) HF gate drive (see Table 2)                 |

| 143             | P0.3  | Digital output/PWM | S1 (Q1, Q9) LF gate drive (see Table 2)               |

| 142             | P0.4  | Digital output/PWM | T2 (Q6) HF gate drive (see Table 2)                   |

| 141             | P0.5  | Digital output/PWM | T1 (Q5) HF gate drive (see Table 2)                   |

| 128             | P0.7  | Digital input      | Output over-current positive or negative (active low) |

| 4               | P0.9  | Digital output/PWM | T'2 (Q7) HF gate drive (see Table 2)                  |

| 3               | P0.10 | Digital output/PWM | T'1 (Q8) HF gate drive (see Table 2)                  |

| 137             | P0.13 | Digital output     | Overvoltage warning LED                               |

| 108             | P1.4  | Digital output     | TXD                                                   |

| 107             | P1.5  | Digital input      | RXD                                                   |

| 94              | P1.15 | Digital output     | Overvoltage warning LED                               |

| 72              | P2.2  | Analog input       | Output current sense                                  |

| 76              | P2.6  | Digital output/PWM | T2 (Q43) HF gate drive (see Table 2)                  |

| 75              | P2.7  | Digital output/PWM | S1 (Q44) LF gate drive (see Table 2)                  |

| 57              | P5.9  | Digital output     | Inrush limiter bypass                                 |

| 42              | P14.0 | Analog input       | Phase "a" flying capacitor voltage (VC38)             |

| 41              | P14.1 | Analog input       | Input DC bus full voltage                             |

| 40              | P14.2 | Analog input       | Split-rail DC voltage (center-negative side)          |

| 36              | P14.6 | Analog input       | Phase "b" flying capacitor voltage (VC35)             |

| 35              | P14.7 | Analog input       | Output current sense                                  |

**Embedded firmware**

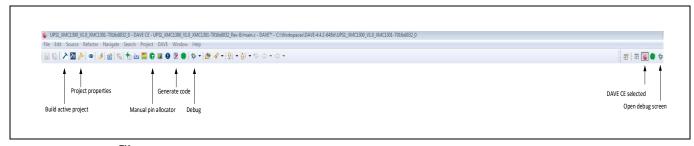

### 6.3 DAVE™ IDE

The firmware controlling this demo board was developed using the DAVE<sup>™</sup> IDE, which can be downloaded free of charge from the Infineon website. Programming and debugging was carried out via the XMC<sup>™</sup> Link isolated debug probe, which is connected to the daughter card through the larger ribbon cable to header P1 and to a computer via a USB cable (the smaller ribbon cable is not used).

Figure 54 XMC<sup>™</sup> Link isolated debugger probe

A project was created within the DAVE™ IDE containing the device definition, settings and source files required to compile and build the executable code, which can be downloaded into the Flash program memory of the XMC™ controller. There are several programming/debugging protocols available, which can be selected when first setting up the DAVE™ IDE to connect the daughter card before programming.

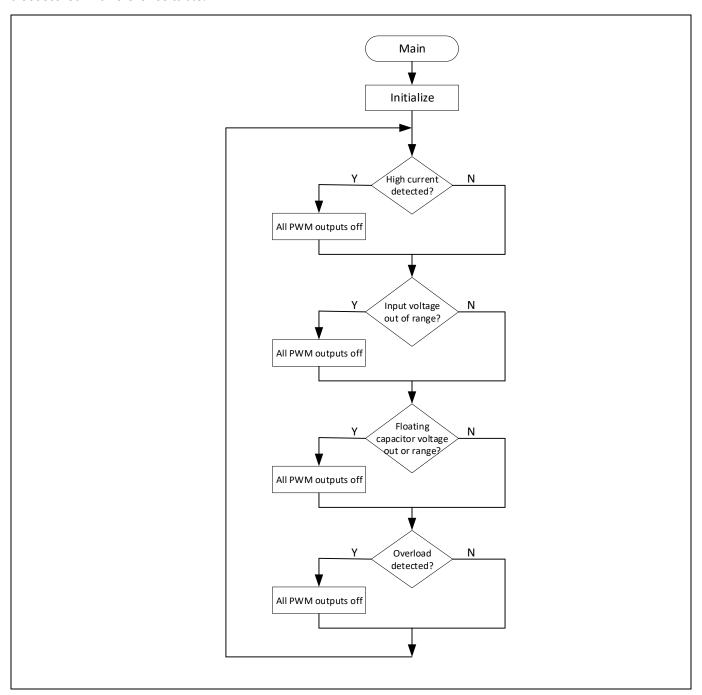

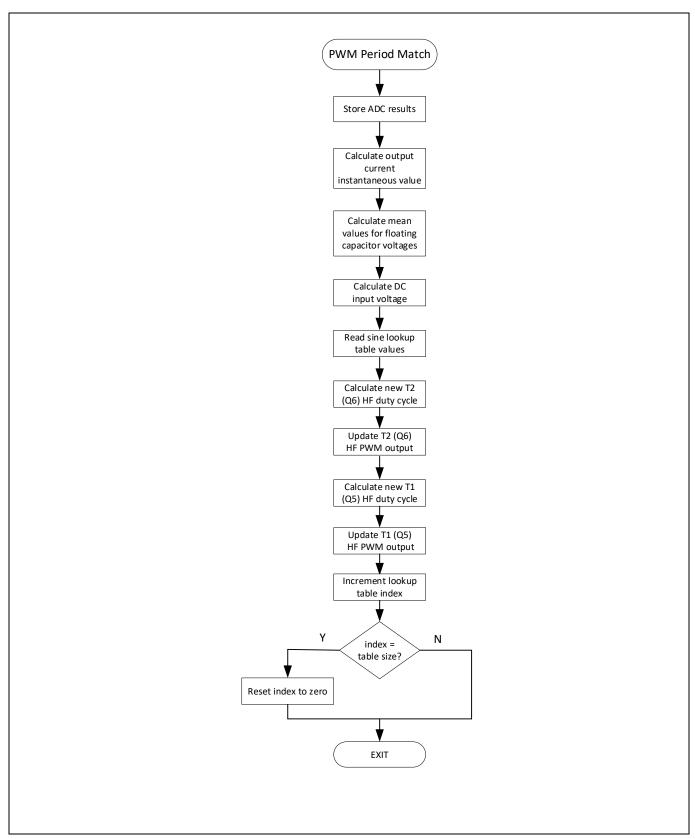

The I/O ports are configured for analog or digital input or output and mapped to the peripherals required by selecting the required DAVE™ apps and configuring these to provide the functions required for the application. These include analog inputs, digital inputs and outputs, and functions such as the PWM generators and timers.