to ramp up to maximum speed.

running operation via EEPROM.

The A89303 three-phase motor driver incorporates sensorless

drive intended to drive low power automotive BLDC motors.

A trapezoidal drive algorithm is implemented to minimize time

The device can be operated by PWM duty or I<sup>2</sup>C interface.

The I<sup>2</sup>C serial port can be used to customize the startup and

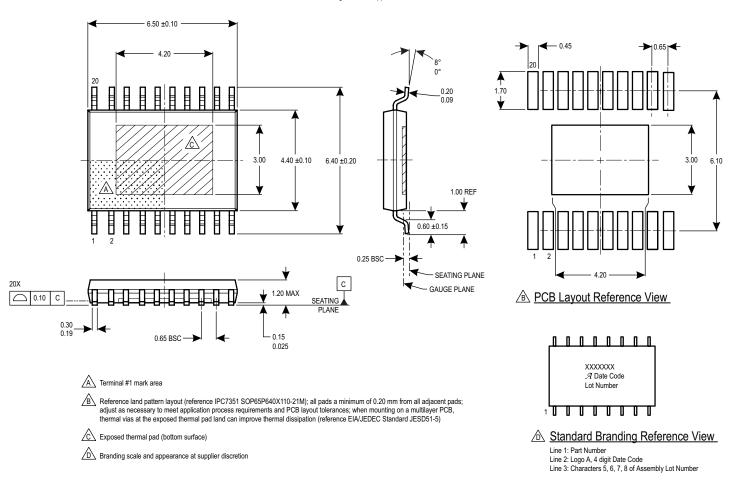

The A89303 is available in a 20-lead TSSOP with exposed

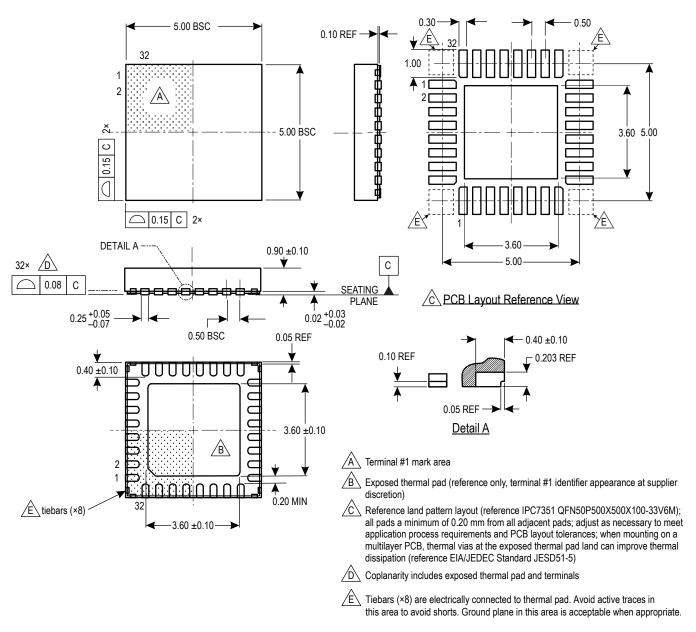

power pad (suffix LP) and a 32-contact 5 mm × 5 mm QFN

with exposed thermal pad and wettable flank (suffix ET).

**DESCRIPTION**

#### **FEATURES AND BENEFITS**

- · AEC-Q100 qualified

- I<sup>2</sup>C serial port control

- Fast startup features

- Trapezoidal drive

- Sensorless (no Hall sensors required)

- Low R<sub>DS(ON)</sub> power MOSFETs

- FG speed output

- Lock detection

- Soft start

- Overcurrent protection

- Overvoltage protection

- Diagnostic outputs

- Small form factor automotive pump

#### **PACKAGES:**

20-lead TSSOP with exposed thermal pad (LP package)

32-contact QFN with exposed thermal pad and wettable flank 5 mm × 5 mm × 0.90 mm (ET package)

Not to scale

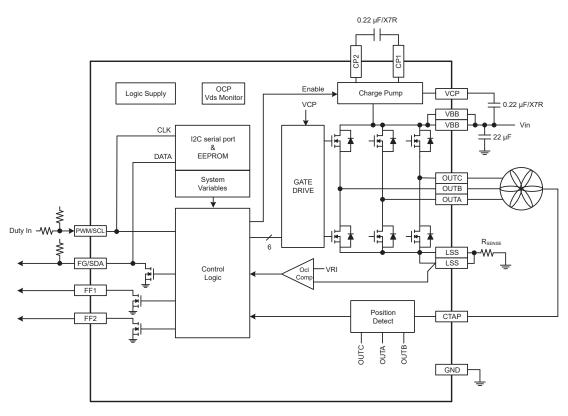

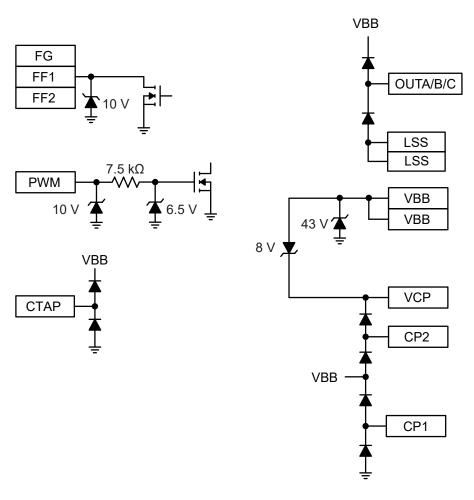

**Figure 1: Typical Application**

# **Three-Phase Sensorless Pump Driver IC**

#### **SPECIFICATIONS**

#### **SELECTION GUIDE**

| Part Number   | Operating Temperature<br>Range (T <sub>A</sub> ) (°C) | . Packaning                                                |                              |  |  |

|---------------|-------------------------------------------------------|------------------------------------------------------------|------------------------------|--|--|

| A89303KLPTR-T | -40 to 125                                            | 20-lead TSSOP with exposed thermal pad                     | 4000 pieces per 13-inch reel |  |  |

| A89303KETSR-J | -40 to 125                                            | 32-contact QFN with exposed thermal pad and wettable flank | 6000 pieces per 13-inch reel |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic              | Symbol                   | Notes            | Rating                                | Unit   |

|-----------------------------|--------------------------|------------------|---------------------------------------|--------|

| Supply Voltage              | V <sub>BB</sub>          |                  | -0.3 to 40                            | V      |

| Logic Input Voltage Range   | V <sub>IN</sub>          | PWM              | -0.3 to 6                             | V      |

| Logic Output                | Vo                       | FG, FF1, FF2     | -0.3 to 6                             | V      |

| Output Current              | I <sub>OUT</sub>         |                  | 3.6                                   | Α      |

| LSS                         |                          | DC               | ±0.36                                 | V      |

| 1 55                        | V <sub>LSS</sub>         | t < 200 ns       | ±2.5                                  | V      |

| Output Voltage              | V <sub>OUT</sub>         | OUTA, OUTB, OUTC | –1.5 to V <sub>BB</sub> + 1           | V      |

| CTAP                        |                          |                  | -0.6 to V <sub>BB</sub> + 0.6         | V      |

| VCP                         |                          |                  | $V_{BB} - 0.3 \text{ to } V_{BB} + 8$ | V      |

| CP1                         |                          |                  | -0.3 to V <sub>BB</sub> + 0.3         | V      |

| CP2                         |                          |                  | $V_{BB} - 0.3$ to $V_{CP} + 0.3$      | V      |

| Maximum EEPROM write cycles | EEPROM <sub>W(MAX)</sub> |                  | 1000                                  | cycles |

| Junction Temperature        | T <sub>J</sub>           |                  | 150                                   | °C     |

| Storage Temperature Range   | T <sub>stg</sub>         |                  | -55 to 150                            | °C     |

| Operating Temperature Range | T <sub>A</sub>           |                  | -40 to 125                            | °C     |

#### THERMAL CHARACTERISTICS

| Characteristic             | Symbol          | Test Conditions*                                                     | Value | Unit |

|----------------------------|-----------------|----------------------------------------------------------------------|-------|------|

| Deckage Thermal Decistance | В               | 20-lead TSSOP (package LP), on 2-sided PCB 1-in. <sup>2</sup> copper | 35    | °C/W |

| Package Thermal Resistance | $R_{\theta JA}$ | 32-contact QFN (package ET), on 2-sided PCB 1-in.2 copper            | 40    | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website.

#### **TABLE OF CONTENTS**

| Features and Benefits                  | 1 | TSD/Fault Flag with PWM High Timing | 9  |

|----------------------------------------|---|-------------------------------------|----|

| Description                            | 1 | Power On / Power Off Timing         | 10 |

| Packages                               | 1 | Startup Sequence                    | 12 |

| Typical Application                    | 1 | PWM Control                         | 12 |

| Specifications                         | 2 | EEPROM Map                          | 13 |

| Selection Guide                        |   | Serial Port                         | 14 |

| Absolute Maximum Ratings               | 2 | I <sup>2</sup> C Timing Diagrams    | 14 |

| Recommended Operational Range          | 2 | Write Command                       |    |

| Thermal Characteristics                | 2 | Read Command                        | 15 |

| Pinout Diagram and Terminal List Table | 3 | Programming EEPROM                  | 16 |

| Electrical Characteristics             | 4 | Application Information             | 18 |

| Functional Description                 | 6 | Pin Diagrams                        |    |

| Basic Operation                        | 6 | Package Outline Drawings            | 20 |

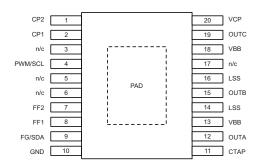

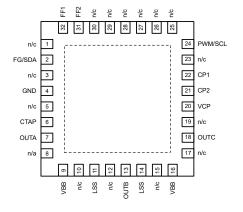

#### PINOUT DIAGRAMS AND TERMINAL LIST TABLE

**LP Package Pinout**

**ET Package Pinout**

#### **Terminal List Table**

| Name    | Nu | mber       | Description                                                      |

|---------|----|------------|------------------------------------------------------------------|

| Name    | LP | ET         | Description                                                      |

| CP2     | 1  | 21         | Charge pump capacitor                                            |

| CP1     | 2  | 22         | Charge pump capacitor                                            |

| n/c     | 3  | 23         |                                                                  |

| PWM/SCL | 4  | 24         | Logic input – PWM duty or I2C clock                              |

| n/c     | 5  | 25, 26, 27 |                                                                  |

| n/c     | 6  | 28, 29, 30 |                                                                  |

| FF2     | 7  | 31         | Logic output signal                                              |

| FF1     | 8  | 32         | Logic output signal                                              |

| n/c     | _  | 1          |                                                                  |

| FG/SDA  | 9  | 2          | I/O – Speed output signal or I2C data                            |

| n/c     | _  | 3          |                                                                  |

| GND     | 10 | 4          | Ground                                                           |

| n/c     | _  | 5          |                                                                  |

| CTAP    | 11 | 6          | Motor common                                                     |

| OUTA    | 12 | 7          | Motor terminal                                                   |

| n/c     | _  | 8          |                                                                  |

| VBB     | 13 | 9          | Input supply                                                     |

| n/c     | _  | 10         |                                                                  |

| LSS     | 14 | 11         | Low-side source connection                                       |

| n/c     | _  | 12         |                                                                  |

| OUTB    | 15 | 13         | Motor terminal                                                   |

| LSS     | 16 | 14         | Low-side source connection                                       |

| n/c     | 17 | 15         |                                                                  |

| VBB     | 18 | 16         | Input supply                                                     |

| n/c     | -  | 17         |                                                                  |

| OUTC    | 19 | 18         | Motor terminal                                                   |

| n/c     | _  | 19         |                                                                  |

| VCP     | 20 | 20         | Charge pump capacitor                                            |

| PAD     | _  | -          | Exposed pad for enhanced thermal dissipation; connect to GND pin |

# **Three-Phase Sensorless Pump Driver IC**

# **ELECTRICAL CHARACTERISTICS:** Valid for $T_J = -40^{\circ}\text{C}$ to 125°C and $V_{BB} = 5.5$ to 40 V, unless noted otherwise

| Characteristics Symbol                      |                                       | Test Conditions                                                          | Min. | Тур. | Max.              | Unit |

|---------------------------------------------|---------------------------------------|--------------------------------------------------------------------------|------|------|-------------------|------|

| GENERAL                                     |                                       |                                                                          | ,    |      | '                 | ,    |

| Load Supply Operating Range V <sub>BB</sub> |                                       | Driving                                                                  | 5.5  | _    | V <sub>BBOV</sub> | V    |

| Load Supply Operating Range                 | V <sub>BB</sub>                       | Operating                                                                | 5.5  | -    | 40                | V    |

| VBB Supply Current                          | I <sub>BB</sub>                       | Active mode (PWM duty < DC_ON)                                           | _    | 8.5  | 12                | mA   |

| Charge Dump                                 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Relative to V <sub>BB</sub> , V <sub>BB</sub> = 8 V                      | 6.5  | 7    | 7.7               | V    |

| Charge Pump                                 | V <sub>CP</sub>                       | Relative to V <sub>BB</sub> , V <sub>BB</sub> = 5.5 V                    | 4    | 5    | _                 | V    |

| POWER DRIVER                                |                                       |                                                                          |      |      |                   |      |

|                                             |                                       | I <sub>OUT</sub> = 1.5 A, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 12 V  | _    | 300  | _                 | mΩ   |

| Total Driver On-Resistance                  | <sub>D</sub>                          | I <sub>OUT</sub> = 1.5 A, T <sub>J</sub> = 125°C, V <sub>BB</sub> = 12 V | _    | 450  | 520               | mΩ   |

| (Sink + Source)                             | R <sub>DS(ON)</sub>                   | Source Driver, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 12 V             | _    | 150  | _                 | mΩ   |

|                                             |                                       | Sink Driver, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 12 V               | _    | 150  | _                 | mΩ   |

| Motor PWM Frequency                         | f <sub>PWM</sub>                      |                                                                          | 23.3 | 24.5 | 25.7              | kHz  |

| MOTOR CONTROL LOGIC                         |                                       |                                                                          |      |      |                   |      |

| PWM Input Frequency Range                   | f <sub>PWMIN</sub>                    |                                                                          | 2.1  | _    | 45                | kHz  |

| Duty Cycle On Threshold                     | DC <sub>ON</sub>                      |                                                                          | 9.5  | 10   | 10.5              | %    |

| Duty Cycle Off Threshold                    | DC <sub>OFF</sub>                     |                                                                          | 7    | 7.4  | 8                 | %    |

| External PWM Delay ON                       | t <sub>PWM_ON</sub>                   |                                                                          | 494  | 520  | 546               | μs   |

| External PWM Delay OFF                      | t <sub>PWM_OFF</sub>                  |                                                                          | 494  | 520  | 546               | μs   |

| PROTECTION CIRCUITS                         |                                       |                                                                          |      |      |                   |      |

| VBB Undervoltage Threshold                  | V <sub>BBUVLO</sub>                   | V <sub>BB</sub> rising                                                   | 4.7  | 4.85 | 5                 | V    |

| VBB Undervoltage Hysteresis                 | V <sub>BBHYS</sub>                    |                                                                          | 400  | 500  | 600               | mV   |

| VBB Overvoltage                             | V <sub>BBOV</sub>                     | V <sub>BB</sub> rising                                                   | 29   | _    | 31.5              | V    |

| VBB Overvoltage Hysteresis                  | V <sub>BBOVHYS</sub>                  |                                                                          | 1.5  | 2    | 2.5               | V    |

| VCP UVLO                                    | V <sub>CPUVLO</sub>                   | V <sub>CP</sub> rising                                                   | 3.6  | 3.85 | 4.1               | V    |

| VCP UVLO Hysteresis                         | V <sub>CPUVHYS</sub>                  |                                                                          | 200  | _    | 400               | mV   |

| Charge Pump Power Up Time [2]               | t <sub>VCPUV</sub>                    |                                                                          | _    | 80   | 400               | μs   |

| POR Delay Time [2]                          | t <sub>POR_DELAY</sub>                |                                                                          | _    | 80   | 90                | μs   |

| Overcurrent Threshold                       | V <sub>OCL</sub>                      | V <sub>RI</sub> = 160 mV                                                 | -5   | 0    | 5                 | %    |

| Overcurrent Protection                      | I <sub>OCP</sub>                      |                                                                          | 5    | _    | _                 | Α    |

| Thermal Shutdown Temperature                | T <sub>JTSD</sub>                     | Temperature increasing                                                   | 165  | 175  | 185               | °C   |

| Thermal Shutdown Hysteresis                 | ΔT <sub>J</sub>                       | Recovery = $T_{JTSD} - \Delta T_{J}$                                     |      | 20   | _                 | °C   |

<sup>[1]</sup> Specified limits are tested at a single temperature and assured over temperature range by design and characterization.

Continued on next page...

<sup>[2]</sup> Ensured by design and characterization, not production tested

# **Three-Phase Sensorless Pump Driver IC**

# **ELECTRICAL CHARACTERISTICS (continued):** Valid for $T_J = -40^{\circ}\text{C}$ to 125°C and $V_{BB} = 5.5$ to 40 V, unless noted otherwise

| Characteristics                     | Symbol              | Test Conditions              | Min. | Тур. | Max. | Unit |

|-------------------------------------|---------------------|------------------------------|------|------|------|------|

| LOGIC/INPUT OUTPUT/I <sup>2</sup> C |                     |                              |      | `    |      |      |

| Input Current (PWM, FG)             | I <sub>IN</sub>     | V <sub>IN</sub> = 0 to 5.5 V | -5   | <1   | 5    | μA   |

| Logic Input Low Level               | $V_{IL}$            |                              | 0    | _    | 0.8  | V    |

| Logic Input High Level              | $V_{IH}$            |                              | 2    | _    | 5.5  | V    |

| Logic Input Hysteresis              | $V_{HYS}$           |                              | 200  | 300  | 600  | mV   |

| Output Saturation Voltage           | V <sub>SAT</sub>    | I = 5 mA                     | _    | _    | 0.3  | V    |

| Logic Output Leakage (FG, FF1, FF2) | I <sub>FG</sub>     | V = 5.5 V, switch OFF        | _    | _    | 5    | μA   |

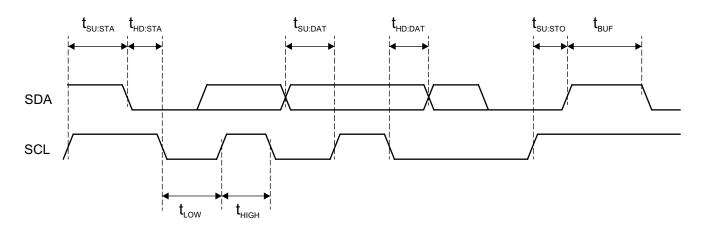

| I <sup>2</sup> C TIMING             |                     |                              |      |      |      |      |

| SCL Clock Frequency                 | f <sub>CLK</sub>    |                              | 8    | -    | 400  | kHz  |

| Bus Free-Time Between Stop/Start    | t <sub>BUF</sub>    |                              | 1.3  | _    | _    | μs   |

| Hold Time Start Condition           | t <sub>HD:STA</sub> |                              | 0.6  | _    | _    | μs   |

| Setup Time for Start Condition      | t <sub>SU:STA</sub> |                              | 0.6  | _    | _    | μs   |

| SCL Low Time                        | $t_{LOW}$           |                              | 1.3  | _    | _    | μs   |

| SCL High Time                       | t <sub>HIGH</sub>   |                              | 0.6  | _    | _    | μs   |

| Data Setup Time                     | t <sub>SU:DAT</sub> |                              | 100  | _    | _    | ns   |

| Data Hold Time                      | t <sub>HD:DAT</sub> |                              | 0    | _    | 900  | ns   |

| Setup Time for Stop Condition       | t <sub>SU:STO</sub> |                              | 0.6  | _    | _    | μs   |

<sup>[1]</sup> Specified limits are tested at a single temperature and assured over temperature range by design and characterization.

#### **FUNCTIONAL DESCRIPTION**

# **Basic Operation**

The A89303 targets automotive pump BLDC applications to meet the objectives of fast startup, high efficiency, and robust protection features.

The speed of the fan is typically controlled by variable duty cycle PWM input. The duty cycle is measured and converted to a 9-bit

number. This 9-bit "demand" is translated to a PWM duty cycle applied to the motor windings, effectively a percentage of the power supply voltage.

Protection features include lock detection with restart, overcurrent limit, overvoltage protection, motor output short-circuit protection (OCP), thermal shutdown, and undervoltage monitors (VBB, VCP).

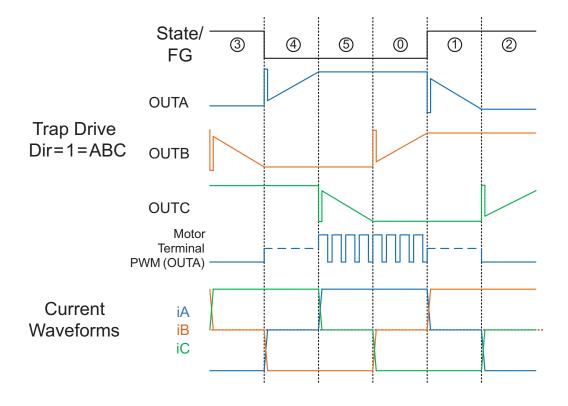

Figure 2: Trapezoidal Drive Sequence

# Three-Phase Sensorless Pump Driver IC

**FG.** Open-drain output. Represents electrical frequency of the motor. Additionally, the FG pin serves as the data line (SDA) for I<sup>2</sup>C communication.

**PWM.** Speed demand input. The demand can be in the form of duty cycle, or direct  $I^2C$  command. The PWM pin also is the  $I^2C$  clock input (SCL). The allowable frequency range for duty input is 2.1 to 45 kHz. There is a 520  $\mu$ s delay after PWM changes for logic to detect a valid ON or OFF command.

**LOCK DETECT.** During motor operation, the core logic will check to see if motor is synchronized based on comparison of expected back-EMF zero crossing to the actual back-EMF zero crossing. If it is determined the rotor has lost synchronization, the A89303 will disable the outputs before attempting a motor restart.

**CTAP.** Connection for the motor common. This pin must be left open if not connected.

**CHARGE PUMP (VCP, CP1, CP2).** A charge pump is used to generate a gate supply 7 V greater than  $V_{BB}$  in order to drive the source side DMOS gates. Two 0.22  $\mu F$  ceramic capacitors are required for this function, connected as shown in application diagram. The charge pump is disabled when the PWM input is less than duty cycle thresholds. The charge pump circuit also integrates an undervoltage monitor to protect against turning on DMOS outputs when VCP is too low.

**OVP.** The outputs can be disabled if power supply voltage exceeds threshold  $V_{\mbox{\footnotesize BBOV}}$ .

**Motor Lead Fault (OCP).** Overcurrent Protection,  $V_{DS}$  monitor. To protect from short to ground, shorted load, or short to battery conditions for the motor lines, the voltage across the power outputs are always monitored when the MOSFET is turned ON. There will be a short blank time before the motor outputs are disabled if the overcurrent protection limit  $I_{OCP}$  is exceeded. The fault is latched off and can only be reset by power cycle or PWM on/off cycle.

Note: During the shorted event, the absolute maximum ratings may be exceeded for the blank time.

**OCL.** Overcurrent Limit. The voltage on LSS pin is monitored to limit current in the motor outputs. The overcurrent threshold voltage VRI can be programmed via EEPROM.

$$I_{OCL} = V_{RI} / R_{SENSE}$$

where

$$V_{RI} = (Code + 1) \times 10 \text{ mV}$$

;  $Code = [15..31]$

# **Three-Phase Sensorless Pump Driver IC**

**Fault Flags.** Two open drain fault pins indicate status as follows.

| FF2                                                                                | FF1                             | Fault Condition                                                                |  |  |

|------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------|--|--|

| 0                                                                                  | 0 0 No Fault – Normal operation |                                                                                |  |  |

| 0                                                                                  | 1                               | Temperature Fault [1]                                                          |  |  |

| 1 0 Motor Lead Fault – Short to Ground, Short to Battery, Shorted load, Rotor Lock |                                 | Motor Lead Fault – Short to Ground, Short to Battery, Shorted load, Rotor Lock |  |  |

| 1                                                                                  | 1                               | Voltage Fault – VBB UVLO, VBB OVP, VCP UVLO [2]                                |  |  |

<sup>[1]</sup> TSD with PWM = high results in rotor lock fault. Rotor lock fault has priority. To check TSD when motor running, drive PWM low to observe FF change from 10 to 01.

<sup>[2]</sup> If PWM is below DCON/DCOFF threshold, VCP UVLO fault will be masked.

| Fault            | Fault Action                       | Latched | Reset Method                              |

|------------------|------------------------------------|---------|-------------------------------------------|

| VBB Undervoltage | Disable Outputs [1]                | N       | Restart attempted when VBB in valid range |

| TSD              | Disable Outputs, start TLOCK timer | N       | Motor restart after TLOCK Timeout         |

| VCP Undervoltage | Disable Outputs                    | N       | Restart attempted when VCP in valid range |

| VBB Overvoltage  | Disable Outputs                    | N       | Restart attempted when VBB in valid range |

| VDS Fault (OCP)  | Disable Outputs                    | Υ       | Latch reset by PWM OFF→ON transition      |

| Loss of Sync     | Disable Outputs, start TLOCK timer | N       | Motor Restart after TLOCK Timeout         |

<sup>[1]</sup> Output disable based on VBB UVLO can be masked by EEPROM bit UVMASK. In this case, the outputs will be protected by the charge pump UVLO function.

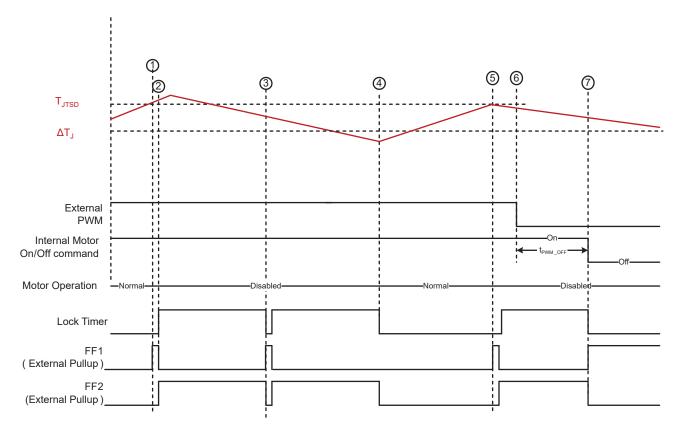

# TSD/Fault Flag with PWM High Timing

Figure 3: TSD/ Fault Flag with PWM High Timing

#### Description of events:

- 1. TSD threshold exceeded, short pulse on FF1, FF = 01

- 2. TSD triggers lock detect timer, FF = 10.

- 3. At end of lock timer. Since TSD condition still exists, Lock timer triggered again, FF = 10.

- 4. At end of lock timer, TSD is OK, normal motor operation can resume, FF = 00.

- 5. TSD threshold exceeded, short pulse on FF1, FF = 01, shortly followed by FF = 10.

- 6. Upon detection of FF = 10, controller wants to determine fault caused by motor lead fault or TSD. Method is to drive PWM low

- 7. Short delay (t<sub>PWM\_OFF</sub>) before internal on/off signal changes state. This signal resets lock timer (will not reset OCP fault). FF changes to 01.

# VCP uvlo VBB uvlo Internal Logic Supply uvlo Internal Motor On/Off command (External Pullup) (External Pullup) (External Pullup)

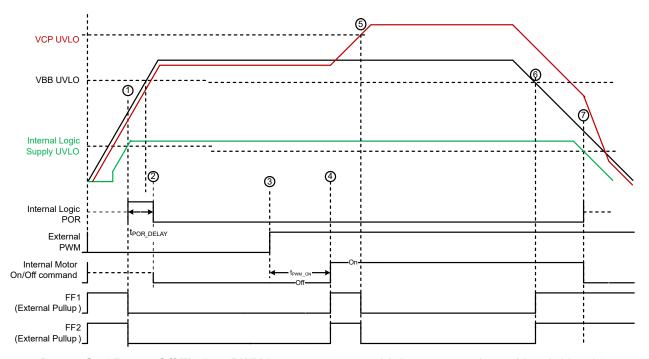

# Power On / Power Off Timing

Figure 4: Power On / Power Off Timing, PWM high on power up, low on power down

Conditions: PWM high on power up, low on power down.

#### Description of events:

- POR delay signal (t<sub>POR\_DELAY</sub>) triggered by UV signal on internal 3p3 power supply. Fault signals driven low during this delay.

- 2. At end of delay, logic is valid. FF = 11, voltage fault due to  $V_{BB}$  below undervoltage level. At this point, logic circuit is running PWM signal is checked.

- 3. FF = 00 voltage fault is released as  $V_{BB}$  rises over  $V_{BBUVLO}$ .

- 4. PWM logic high is detected after  $t_{PWM\_ON}$ . Charge pump is enabled. FF = 11 while VCP is below UVLO level. The time for VCP to rise over its UVLO level is  $t_{VCPUV}$ .

- 5. V<sub>CP</sub> rises over UVLO level and motor outputs turn on, FF back to 00.

- 6. PWM off starts t<sub>PWM OFF</sub> timer.

- 7. PWM recognized low to turn off motor and charge pump. Fault flag does not check  $V_{CP}$  UV when PWM = low.

- 8. Power down UV fault, FF = 11, when  $V_{BB}$  falls below  $(V_{BBUVLO} V_{BBHYS})$ .

- 9. Internal logic reset when below internal  $V_{3p3}$  UVLO. This occurs when  $V_{BB}$  is approximately 3.6 V.

# Power On / Power Off Timing (continued)

Figure 5: Power On / Power Off Timing, PWM low on power up, high on power down, VBB dv/dt < 80 µs

Conditions: PWM low on power up, high on power down,  $V_{BB}\,dv/dt\,{<}80~\mu s.$

#### Description of events:

- 1. POR delay signal (t<sub>POR\_DELAY</sub>) triggered by UV signal on internal 3p3 power supply. Fault signals driven low during this delay.

- 2. At end of delay, logic is valid. Fault flag = 00, due to  $V_{BB}$  above undervoltage level.

- 3. PWM ON starts  $t_{PWM\ ON}$  timer.

- 4. PWM recognized High to Turn On motor and Charge pump. Fault flag checks VCP UV and pulse high for charge pump power up time. The time for V<sub>CP</sub> to rise over its UVLO level is t<sub>VCPUV</sub>.

- 5. FF = 00 after  $V_{CPUVLO}$  is exceeded.

- 6. Power down UV fault, FF = 11, when  $V_{BB}$  falls below  $(V_{BBUVLO} V_{BBHYS})$

- 7. Internal logic reset when below internal  $V_{3p3}$  UVLO. This occurs when  $V_{BB}$  is approximately 3.6 V.

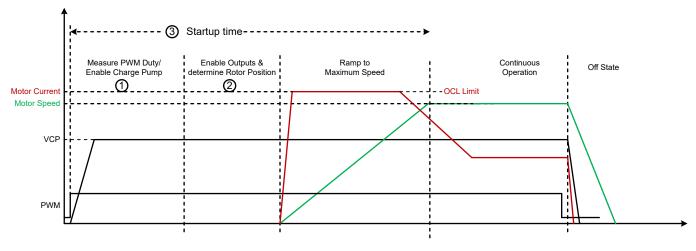

# **Startup Sequence**

Figure 6: Startup Sequence

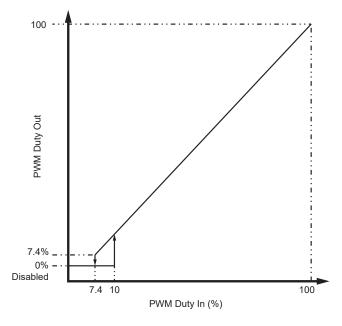

#### **PWM Control**

Motor will be disabled if PWM duty below DCON threshold of 10%. There is 2.6% hysteresis to DCOFF threshold of 7.4%.

Figure 7: PWM Control

# **EEPROM MAP**

Table 1: EEPROM Map. Refer to application note and user interface for additional detail.

| I2C Register | EE Address | Bits  | Name     | Description                              | Default Setting |  |  |  |

|--------------|------------|-------|----------|------------------------------------------|-----------------|--|--|--|

| 64           | 0          | 15:0  | Dev1     | Allegro Reserved                         | n/a             |  |  |  |

| 65           | 1          | 15:0  | Dev1     | Allegro Reserved                         | n/a             |  |  |  |

| 66           | 2          | 15:0  | Dev1     |                                          |                 |  |  |  |

| 67           | 3          | 15:0  | Dev1     | <u> </u>                                 |                 |  |  |  |

| 68           | 4          | 15:0  | Dev1     | Dev1 Allegro Reserved                    |                 |  |  |  |

| 69           | 5          | 15:0  | Dev1     |                                          |                 |  |  |  |

| 70           | 6          | 15:0  | Dev1     |                                          |                 |  |  |  |

| 71           | 7          | 15:0  | Trim1    | Allegro Reserved                         | n/a             |  |  |  |

| 72           | 8          | 15:0  | Trim2    | Allegro Reserved                         | n/a             |  |  |  |

|              |            | 0     | UVMASK   | 0 = Normal 1 = Mask                      |                 |  |  |  |

|              |            | 1     | OVPDIS   | 0 = Normal, 1 = Disable                  |                 |  |  |  |

| 70           |            | 2     | RETRY    | 0 = Disable, 1 = Enable                  | 00050           |  |  |  |

| 73           | 9          | 3     | OVERLAP  | 0 = Disable, 1 = Enable                  | 0x005C          |  |  |  |

|              |            | 4     | Dev2     | Allegro Reserved – Set to 1              |                 |  |  |  |

|              |            | 6:5   | Dev2     | Allegro Reserved – Set to 10             |                 |  |  |  |

|              |            | 0     | DIR      | 0 = ACB, 1 = ABC                         |                 |  |  |  |

|              |            | 1     | FGSTRT   | 0 = Disable 1 = Enable                   |                 |  |  |  |

|              |            | 4:2   | BEMFILT  | Select Bemf Filter                       |                 |  |  |  |

|              |            | 6:5   | BEMFHYS  | Select Bemf Hysteresis                   |                 |  |  |  |

|              |            | 7     | WIND     | 0 = Disable, 1 = Enable                  |                 |  |  |  |

| 74           | 10         | 8     | IPDENB   | 0 = Disable, 1 = Enable                  | 0x480C          |  |  |  |

|              |            | 9     | IPDDECAY | 0 = SLOW, 1 = FAST                       |                 |  |  |  |

|              |            | 10    | Dev2     | Allegro Reserved – Set to 0              |                 |  |  |  |

|              |            | 13:11 | STEPS    | Select trap states before BEMF detection |                 |  |  |  |

|              |            | 14    | OCL      | 0 = PWM cycle, 1 = Fixed off-time        |                 |  |  |  |

|              |            | 15    | ALIGNOCL | 0 = OCL level, 1 = IPDINI step           |                 |  |  |  |

| 75           | 11         | 5:0   | ALIGN    | Align Time                               | 0x0001          |  |  |  |

| 76           | 12         | 5:0   | LOCK     | Lock Time                                | 0x002A          |  |  |  |

|              |            | 1:0   | TOFF     | Fixed Off time Current Limit             |                 |  |  |  |

|              |            | 7:2   | OSC      | Startup Osc                              | 0.5045          |  |  |  |

| 77           | 13         | 9:8   | Unused   | n/a                                      | 0cFC4B          |  |  |  |

|              |            | 15:10 | COMST    | Com State Stall Limit                    |                 |  |  |  |

|              |            | 4:0   | IPDINI   | IPD Start Level                          |                 |  |  |  |

| 78 14        |            | 7:5   | IPDSTEP  | Select IPD steps                         | 0x148D          |  |  |  |

|              |            | 12:8  | OCL      | Select Current Limit                     |                 |  |  |  |

| 79           | 15         | 15:0  | Trim2    | Allegro Reserved                         | n/a             |  |  |  |

#### **Serial Port**

The A89303 uses standard fast mode I<sup>2</sup>C serial port format to program the EEPROM or to control the IC speed serially. The PWM pin functions as the clock (SCL) input, and the FG pin is the data line (SDA). No special sequence is needed to begin transferring data. If the motor is running, the FG may then pull the data line low while trying to initialize into serial port mode. Once an I<sup>2</sup>C command is sent, the PWM input is ignored, and the motor will turn off as if a PWM duty command of 0% was sent.

The A89303 7-bit slave address is 0x55.

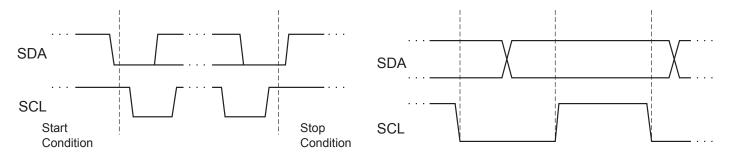

# I<sup>2</sup>C Timing Diagrams

Figure 8: Start and Stop Conditions

Figure 9: Clock and Data Bit Synchronization

Figure 10: I<sup>2</sup>C-Compatible Timing Requirements

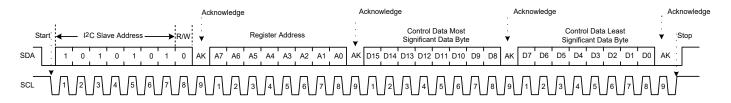

#### **Write Command**

- 1. Start Condition

- 2. 7-bit I<sup>2</sup>C Slave Address (Device ID) 1010101, R/W Bit = 0

- 3. Internal Register Address

- 4. 2 data bytes, MSB first

- 5. Stop Condition

Figure 11: Write Command

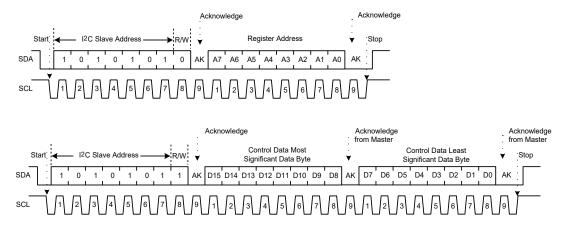

# **Read Command: Two Step Process**

- 1. Start Condition

- 2. 7-bit I<sup>2</sup>C Slave Address (Device ID) 1010101, R/W Bit = 0

- 3. Internal Register Address to be read

- 4. Stop Condition

- 5. Start Condition

- 6. 7-bit I<sup>2</sup>C Slave Address (Device ID) 1010101, R/W Bit = 1

- 7. Read 2 data bytes

- 8. Stop Condition

Figure 12: Read Command

# **Three-Phase Sensorless Pump Driver IC**

# **Programming EEPROM**

The A89303 contains 16 words of 16-bit length. The EEPROM is controlled with the following  $I^2C$  registers. Refer to application note for EEPROM definition.

#### Table 2: EEPROM Control – Register 161 (Used to control programming of EEPROM)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3  | 2  | 1  | 0  |

|----|----|----|----|----|----|---|---|---|---|---|---|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | 0 | RD | WR | ER | EN |

| Bit  | Name | Description                                               |  |

|------|------|-----------------------------------------------------------|--|

| 0    | EN   | et EEPROM voltage required for writing or erasing         |  |

| 1    | ER   | Sets mode to erase                                        |  |

| 2    | WR   | Sets mode to write                                        |  |

| 3    | RD   | Sets mode to read                                         |  |

| 15:4 | n/a  | Do not use; always set to zero during programming process |  |

#### Table 3: EEPROM Address - Register 162 (Used to set the EEPROM address to be altered)

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4         | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|---|---|---|---|---|-----------|---|---|---|---|

| 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | 0 | eeADDRESS |   |   |   |   |

| Bit  | Name Description |                                                                      |  |  |

|------|------------------|----------------------------------------------------------------------|--|--|

| 4:0  | eeADDRESS        | Used to specify EEPROM address to be changed; there are 16 addresses |  |  |

| 15:5 | n/a              | Do not use; always set to zero during programming process            |  |  |

#### Table 4: EEPROM DataIn - Register 163 (Used to set the EEPROM new data to be programmed)

| 15 | 14       | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | eeDATAin |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit  | Name                                                       | Description |  |  |  |

|------|------------------------------------------------------------|-------------|--|--|--|

| 15:0 | eeDATAin Used to specify the new EEPROM data to be changed |             |  |  |  |

# **Three-Phase Sensorless Pump Driver IC**

#### Table 5: DataOUT - Register 164 (Used for read operations)

| 15 | 14        | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|-----------|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | eeDATAout |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

| Bit  | Name      | Description                                                       |

|------|-----------|-------------------------------------------------------------------|

| 15:0 | eeDATAout | Used to readback EEPROM data from address defined in register 162 |

There are 3 basic commands: Read, Erase, and Write. To change the contents of a memory location, the word must be first erased. The EEPROM programming process (writing or erasing) takes 12 ms per word.

Each word must be written individually.

Example #1: Write EEPROM address 9 to 261 (0x0105)

1) Erase the word

I<sup>2</sup>C Write REGADDR[Data] ; comment

a. 162[9] ; set EEPROM address to erase

b. 163[0] ; set 0000 as Data In

c. 161[3] ; set control to Erase and Voltage Highd. Wait 12 ms ; required 12 ms High Voltage Pulse to Write

2) Write the new data

a. 162[9] ; set EEPROM address to write

b. 163[261] ; set Data In = 261

c. 161[5] ; set control to Write and Set Voltage Highd. Wait 12 ms ; required 12 ms High Voltage Pulse to Write

Example #2: Read EEPROM address 9 to confirm correct data properly programmed

1) Read the word

a. 9[I<sup>2</sup>C Read] ; read register 9; this will be the contents of EEPROM

# POM POM POM CAICH CONCESS OF THE POM POM CAICH CONCESS OF THE POM CAICH

# **APPLICATION INFORMATION**

Figure 13: Typical Application Circuit

**Table 6: Typical Application Components**

| Name                               | Suggested Value | Comment                                                                                  |

|------------------------------------|-----------------|------------------------------------------------------------------------------------------|

| C <sub>VBB1</sub>                  | 0.22 μF         | Ceramic capacitor required                                                               |

| C <sub>VBB2</sub>                  | 22 to 220 μF    | Power supply stabilization – electrolytic or ceramic OK.                                 |

| C <sub>VCP</sub>                   | 0.22 μF         | Ceramic capacitor required                                                               |

| C <sub>CP</sub>                    | 0.22 μF         | Ceramic capacitor required                                                               |

| D1                                 | B24013F         | Required to isolate motor for reverse polarity protection                                |

| TVS                                | SMBJ33A         | TVS to limit max V <sub>BB</sub> due to transients due to motor generation on power line |

| R <sub>FG</sub> , R <sub>PWM</sub> | 500 Ω           | Isolate IC pin from noise or overvoltage transients or protect from connector issues     |

| R <sub>SENSE</sub>                 | 100 mΩ          | Resistor for current sensing                                                             |

#### Layout Notes:

- 1. Add thermal vias to exposed pad area.

- 2. Add ground plane on top and bottom of PCB.

- 3. Place C<sub>VBB1</sub> as close as possible to IC, connected to GND plane.

# **PIN DIAGRAMS**

Figure 14: Pin Diagrams

#### PACKAGE OUTLINE DRAWINGS

For Reference Only – Not for Tooling Use (Reference JEDEC MO-153ACT; Allegro DWG-0000379, Rev. 3) NOTTO SCALE

Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

Figure 15: Package LP, 20-Lead TSSOP with Exposed Pad

#### For Reference Only - Not for Tooling Use

(Reference Allegro DWG-0000378, Rev. 3 and JEDEC MO-220VHHD-5)

Dimensions in millimeters – NOT TO SCALE

Exact case and lead configuration at supplier discretion within limits shown

Figure 16: Package ET, 32-Contact QFN with Exposed Pad and Wettable Flank

# **Three-Phase Sensorless Pump Driver IC**

#### **Revision History**

| Number | Date               | Description                                                                                                                                                                                                                                                                                                                                                 |

|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| _      | August 27, 2020    | Initial release                                                                                                                                                                                                                                                                                                                                             |

| 1      | March 10, 2021     | Updated product title, typical application (page 1), Logic Input Voltage Range, Logic Output (page 2); added EEPROM Cycles (page 2); corrected CP1 and CP2 pin order in LP pinout diagram (page 3); updated Duty Cycle Off Threshold (page 4), Setup Time for Stop Condition (page 5), DataOUT EEPROM section (page 17), and other minor editorial updates. |

| 2      | November 5, 2021   | Updated EEPROM map (page 13) and ET-32 package drawing (page 21); corrected typos on pages 16 and 17                                                                                                                                                                                                                                                        |

| 3      | September 16, 2022 | Updated EEPROM map (page 13, I2C Register 73, Bit 1 Description), Table 6 (page 18), and LP-20 package drawing (page 20)                                                                                                                                                                                                                                    |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com