### Low Voltage 32K x 8 SRAM

#### **Features**

###

☐ ESD protection > 2000 V

(MIL STD 883C M3015.7)

☐ Package: SOP28 (300/330 mil)

☐ Latch-up immunity >100 mA

Description

The AS62V256A-70SIN is a static RAM manufactured using a CMOS pro-cess technology with the following operating modes:

- Read - Standby

- Write - Data Retention

The memory array is based on a 6-Transistor cell.

The circuit is activated by the falling edge of  $\overline{E}$ . The address and control inputs open simultaneously. According to the information of  $\overline{W}$  and  $\overline{G}$ , the data inputs, or outputs, are active. In a Read cycle, the data outputs are activated by the falling edge of  $\overline{G}$ , afterwards the data word will be available at the outputs DQ0-DQ7. After the address change, the data outputs

go High-Z until the new information is available. The data outputs have no preferred state. The Read cycle is finished by the falling edge of  $\overline{\mathbf{W}}$ , or by the rising edge of  $\overline{\mathbf{E}}$ , respectively.

Data retention is guaranteed down to 2 V. With the exception of  $\overline{E}$ , all inputs consist of NOR gates, so that no pull-up/pull-down resistors are required.

#### **Pin Configuration**

#### 28 VCC A14 $\overline{\mathsf{w}}$ A12 2 27 Α7 3 26 A13 A6 25 Α8 A5 Α9 5 24 23 A4 6 A11 А3 22 G SOP A2 8 21 A10 Α1 9 20 E A0 19 DQ7 10 DQ0 11 18 DQ6 DQ1 12 17 DQ5 DQ2 13 16 DQ4 VSS 15 DQ3

#### Pin Description

| Signal Name | Signal Description      |

|-------------|-------------------------|

| A0 - A14    | Address Inputs          |

| DQ0 - DQ7   | Data In/Out             |

| Ē           | Chip Enable             |

| G           | Output Enable           |

| W           | Write Enable            |

| vcc         | Power Supply<br>Voltage |

| VSS         | Ground                  |

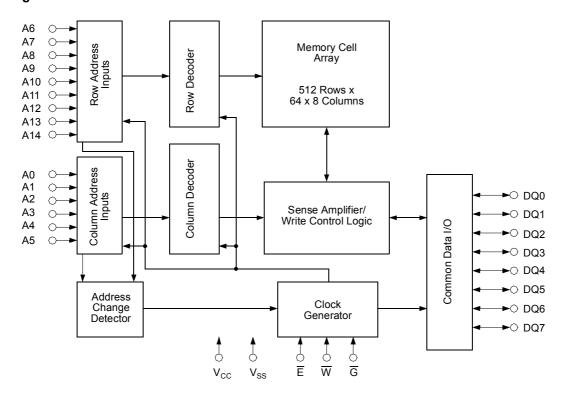

### **Block Diagram**

#### **Truth Table**

| Operating Mode       | Ē | w | G | DQ0 - DQ7          |

|----------------------|---|---|---|--------------------|

| Standby/not selected | Н | * | * | High-Z             |

| Internal Read        | L | Н | Н | High-Z             |

| Read                 | L | Н | L | Data Outputs Low-Z |

| Write                | L | L | * | Data Inputs High-Z |

<sup>\*</sup> H or L

#### **Characteristics**

All voltages are referenced to  $V_{\rm SS}$  = 0 V (ground).

All characteristics are valid in the power supply voltage range and in the operating temperature range specified. Dynamic measurements are based on a rise and fall time of  $\leq$  5 ns, measured between 10 % and 90 % of  $V_I$ , as well as input levels of  $V_{IL}$  = 0.2 V and  $V_{IH}$  = 2.8 V. The timing reference level of all input and output signals is 1.5 V, with the exception of the  $t_{dis}$ -times and  $t_{en}$ -times, in which cases transition is measured  $\pm$ 200 mV from steady-state voltage.

| Absolute Maximum Ratings <sup>a</sup>                                     | Symbol           | Min. | Max.                               | Unit |

|---------------------------------------------------------------------------|------------------|------|------------------------------------|------|

| Power Supply Voltage                                                      | V <sub>CC</sub>  | -0.3 | 4.6                                | V    |

| Input Voltage                                                             | V <sub>I</sub>   | -0.5 | V <sub>CC</sub> + 0.5 <sup>b</sup> | V    |

| Output Voltage                                                            | V <sub>O</sub>   | -0.5 | V <sub>CC</sub> + 0.5 <sup>b</sup> | V    |

| Power Dissipation                                                         | P <sub>D</sub>   | -    | 1                                  | W    |

| Operating Temperature                                                     | Та               | -40  | 85                                 | °C   |

| Storage Temperature                                                       | T <sub>stg</sub> | -65  | 150                                | °C   |

| Output Short-Circuit Current at $V_{CC}$ = 3.3 V and $V_{O}$ = 0 V $^{c}$ | I <sub>os</sub>  |      | 100                                | mA   |

<sup>&</sup>lt;sup>a</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability

<sup>&</sup>lt;sup>c</sup> Not more than 1 output should be shorted at the same time. Duration of the short circuit should not exceed 30 s.

| Recommended Operating Conditions | Symbol          | Conditions | Min. | Max.                  | Unit |

|----------------------------------|-----------------|------------|------|-----------------------|------|

| Power Supply Voltage             | V <sub>CC</sub> |            | 2.5  | 3.6                   | V    |

| Input Low Voltage d              | V <sub>IL</sub> |            | -0.3 | 0.5                   | V    |

| Input High Voltage               | V <sub>IH</sub> |            | 2.0  | V <sub>CC</sub> + 0.3 | V    |

d -2 V at Pulse Width 30 ns

b Maximum voltage is 4.6 V

| Electrical Characteristics                   | Symbol               | Co                                                                       | nditions                                                      | Min. | Max.     | Unit     |

|----------------------------------------------|----------------------|--------------------------------------------------------------------------|---------------------------------------------------------------|------|----------|----------|

| Supply Current - Operating Mode              | I <sub>CC(OP)</sub>  | V <sub>CC</sub><br>V <sub>IL</sub><br>V <sub>IH</sub><br>t <sub>cW</sub> | = 3.6 V<br>= 0.5 V<br>= 2.0 V<br>= 70 ns<br>= 70 ns           |      | 90<br>70 | mA<br>mA |

| Supply Current - Standby Mode (CMOS level)   | I <sub>CC(SB)</sub>  | V <sub>CC</sub><br>V <sub>E</sub><br>I-Type                              | = $3.6 \text{ V}$<br>= $\text{V}_{\text{CC}} - 0.2 \text{ V}$ |      | 10       | μΑ       |

| Supply Current - Standby Mode<br>(TTL level) | I <sub>CC(SB)1</sub> | V <sub>CC</sub><br>V <sub>E</sub><br>I-Type                              | = 3.6 V<br>= 2.0 V                                            |      | 10       | mA       |

| Output High Voltage                          | V <sub>OH</sub>      | V <sub>CC</sub>                                                          | = 2.5 V                                                       | 2.2  |          | V        |

| Output Low Voltage                           | V <sub>OL</sub>      | I <sub>OH</sub><br>V <sub>CC</sub><br>I <sub>OL</sub>                    | = -1.0 mA<br>= 2.5 V<br>= 2.1 mA                              |      | 0.4      | V        |

| Input High Leakage Current                   | I <sub>IH</sub>      | V <sub>CC</sub>                                                          | = 3.6 V<br>= 3.6 V                                            |      | 2        | μΑ       |

| Input Low Leakage Current                    | I <sub>IL</sub>      | V <sub>IH</sub><br>V <sub>CC</sub><br>V <sub>IL</sub>                    | = 3.6 V<br>= 0 V                                              | -2   |          | μA       |

| Output High Current                          | Іон                  | V <sub>CC</sub>                                                          | = 2.5 V<br>= 2.2 V                                            |      | -1.0     | mA       |

| Output Low Current                           | I <sub>OL</sub>      | V <sub>OH</sub><br>V <sub>CC</sub><br>V <sub>OL</sub>                    | = 2.5 V<br>= 0.4 V                                            | 2.1  |          | mA       |

| Output Leakage Current                       |                      | .,                                                                       | 0.01/                                                         |      |          |          |

| High at Three-State Outputs                  | I <sub>OHZ</sub>     | V <sub>CC</sub><br>V <sub>OH</sub>                                       | = 3.6 V<br>= 3.6 V                                            |      | 2        | μA       |

| Low at Three-State Outputs                   | I <sub>OLZ</sub>     | V <sub>CC</sub><br>V <sub>OL</sub>                                       | = 3.6 V<br>= 0 V                                              | -2   |          | μA       |

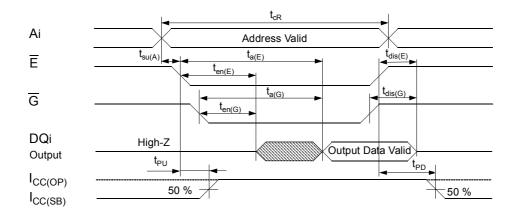

| Switching Characteristics             | Syn               | nbol                | 7    | Unit |       |

|---------------------------------------|-------------------|---------------------|------|------|-------|

| Read Cycle                            | Alt.              | IEC                 | Min. | Max. | Oilit |

| Read Cycle Time                       | t <sub>RC</sub>   | t <sub>cR</sub>     | 70   |      | ns    |

| Address Access Time to Data Valid     | t <sub>AA</sub>   | t <sub>a(A)</sub>   |      | 70   | ns    |

| Chip Enable Access Time to Data Valid | t <sub>ACE</sub>  | t <sub>a(E)</sub>   |      | 70   | ns    |

| G LOW to Data Valid                   | t <sub>OE</sub>   | t <sub>a(G)</sub>   |      | 25   | ns    |

| EHIGH to Output in High-Z             | t <sub>HZCE</sub> | t <sub>dis(E)</sub> |      | 15   | ns    |

| G HIGH to Output in High-Z            | t <sub>HZOE</sub> | t <sub>dis(G)</sub> |      | 15   | ns    |

| ELOW to Output in Low-Z               | t <sub>LZCE</sub> | t <sub>en(E)</sub>  | 3    |      | ns    |

| G LOW to Output in Low-Z              | t <sub>LZOE</sub> | t <sub>en(G)</sub>  | 0    |      | ns    |

| Output Hold Time from Address Change  | t <sub>OH</sub>   | t <sub>v(A)</sub>   | 3    |      | ns    |

| ELOW to Power-Up Time                 | t <sub>PU</sub>   |                     | 0    |      | ns    |

| E HIGH to Power-Down Time             | t <sub>PD</sub>   |                     |      | 70   | ns    |

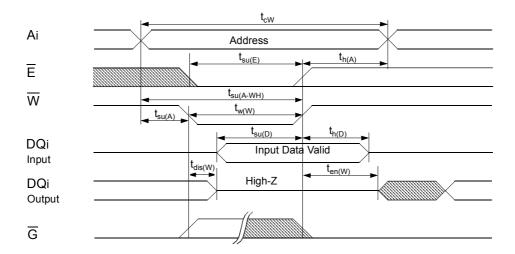

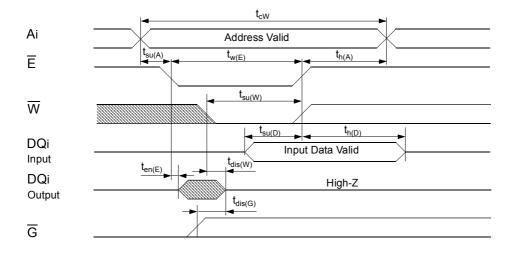

| Switching Characteristics               | Syr               | mbol                  | 7    | Unit |      |

|-----------------------------------------|-------------------|-----------------------|------|------|------|

| Write Cycle                             | Alt.              | IEC                   | Min. | Max. | Unit |

| Write Cycle Time                        | t <sub>WC</sub>   | t <sub>cW</sub>       | 70   |      | ns   |

| Write Pulse Width                       | t <sub>WP</sub>   | t <sub>w(W)</sub>     | 35   |      | ns   |

| Write Setup Time                        | t <sub>WP</sub>   | t <sub>su(W)</sub>    | 35   |      | ns   |

| Address Setup Time                      | t <sub>AS</sub>   | t <sub>su(A)</sub>    | 0    |      | ns   |

| Address Valid to End of Write           | t <sub>AW</sub>   | t <sub>su(A-WH)</sub> | 40   |      | ns   |

| Chip Enable Setup Time                  | t <sub>CW</sub>   | t <sub>su(E)</sub>    | 40   |      | ns   |

| Pulse Width Chip Enable to End of Write | t <sub>CW</sub>   | t <sub>w(E)</sub>     | 40   |      | ns   |

| Data Setup Time                         | t <sub>DS</sub>   | t <sub>su(D)</sub>    | 25   |      | ns   |

| Data Hold Time                          | t <sub>DH</sub>   | t <sub>h(D)</sub>     | 0    |      | ns   |

| Address Hold from End of Write          | t <sub>AH</sub>   | t <sub>h(A)</sub>     | 0    |      | ns   |

| W LOW to Output in High-Z               | t <sub>HZWE</sub> | t <sub>dis(W)</sub>   |      | 20   | ns   |

| G HIGH to Output in High-Z              | t <sub>HZOE</sub> | t <sub>dis(G)</sub>   |      | 15   | ns   |

| WHIGH to Output in Low-Z                | t <sub>LZWE</sub> | t <sub>en(W)</sub>    | 0    |      | ns   |

| G LOW to Output in Low-Z                | t <sub>LZOE</sub> | t <sub>en(G)</sub>    | 0    |      | ns   |

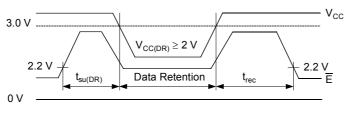

#### **Data Retention Mode**

### E - controlled

$$V_{CC(DR)} \text{ - } 0.2 \text{ V} \leq V_{\overline{E}(DR)} \leq V_{CC(DR)} \text{ + } 0.3 \text{ V}$$

| Data Retention                | Symbol           |                     | Conditions                                                | N4:             | T    | Max     | 11:4     |

|-------------------------------|------------------|---------------------|-----------------------------------------------------------|-----------------|------|---------|----------|

| Characteristics               | Alt.             | IEC                 | Conditions                                                | Min.            | Тур. | Max.    | Unit     |

| Data Retention Supply Voltage |                  | V <sub>CC(DR)</sub> |                                                           | 2               |      |         | V        |

| Data Retention Supply Current |                  | I <sub>CC(DR)</sub> | $V_{CC(DR)} = 2V$ $V_{\overline{E}} = V_{CC(DR)} - 0.2 V$ |                 |      | 5<br>20 | μΑ<br>μΑ |

| Data Retention Setup Time     | t <sub>CDR</sub> | t <sub>su(DR)</sub> | See Data Retention                                        | 0               |      |         | ns       |

| Operating Recovery Time       | t <sub>R</sub>   | t <sub>rec</sub>    | Waveforms (above)                                         | t <sub>cR</sub> |      |         | ns       |

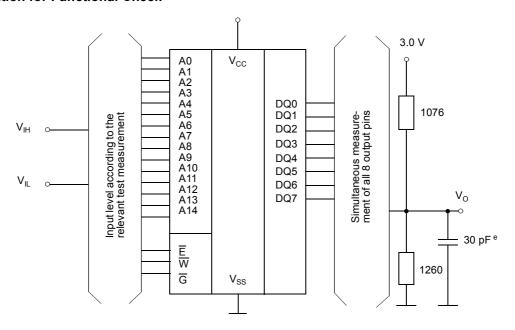

### **Test Configuration for Functional Check**

$<sup>^{\</sup>rm e}$  In measurement of  $t_{\rm dis(E)}$ ,  $t_{\rm dis(W)}$ ,  $t_{\rm en(E)}$ ,  $t_{\rm en(W)}$ ,  $t_{\rm en(G)}$  the capacitance is 5 pF.

| Capacitance        | Conditions                                | Symbol | Min. | Max. | Unit |

|--------------------|-------------------------------------------|--------|------|------|------|

| Input Capacitance  | $V_{CC} = 3.3V$ $V_{I} = V_{SS}$          | Cı     |      | 7    | pF   |

| Output Capacitance | $t = 1 \text{ MHz}$ $T_a = 25 \text{ °C}$ | Co     |      | 7    | pF   |

All pins not under test must be connected with ground by capacitors.

| Alliance        | Organization | VCC Range   | Package         | Operating<br>Temp            | Speed<br>ns |

|-----------------|--------------|-------------|-----------------|------------------------------|-------------|

| AS62V256A-70SIN | 32K x 8      | 2.7V – 3.6V | SOP28 (330 mil) | Industrial ~<br>-40°C - 85°C | 70          |

Sept 2012 7

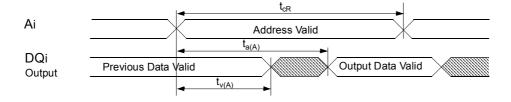

# Read Cycle 1: $A_i$ -controlled (during Read Cycle : $\overline{E} = \overline{G} = V_{IL}$ , $\overline{W} = V_{IH}$ )

## Read Cycle 2: $\overline{G}$ -, $\overline{E}$ -controlled (during Read Cycle: $\overline{W} = V_{IH}$ )

### Write Cycle1: W-controlled

### Write Cycle 2: E-controlled

The information describes the type of component and shall not be considered as assured characteristics. Terms of delivery and rights to change design reserved.

ALLIANCE M E M O R Y

#### LIFE SUPPORT POLICY

Alliance Memory products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Alliance Memory product could create a situation where personal injury or death may occur. Components used in life-support devices or systems must be expressly authorized by Alliance Memory for such purpose.

#### LIMITED WARRANTY

The information in this document has been carefully checked and is believed to be reliable. However Alliance Memory makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon it. The information in this document describes the type of component and shall not be considered as assured characteristics. Alliance Memory does not guarantee that the use of any information contained herein will not infringe upon the patent, trade-mark, copyright, mask work right or other rights of third parties, and no patent or licence is implied hereby. This document does not in any way extent Alliance Memory's warranty on any product beyond that set forth in its standard terms and conditions of sale.

Alliance Memory reserves terms of delivery and reserves the right to make changes in the products or specifications, or both, presented in this publication at any time and without notice.