# TPS62842EVM-103 User's Guide

The TPS62842EVM-103 facilitates the evaluation of the TPS62842DGR of 750-mA, step-down converter with 60-nA  $I_{Q}$  in a DGR package. The EVM has output voltages between 1.8 V and 3.6 V from higher input voltages between 1.8 V and 6.5 V. Due to its extremely low  $I_{Q}$ , the TPS6284x provides a long battery lifetime for systems which have very low current consumption states such as building automation, metering, and the Internet of Things (IoT).

#### Contents

| 1 | Introduction                    | 2  |

|---|---------------------------------|----|

| 2 | Setup                           | 4  |

| 3 | TPS62842EVM-103 Test Results    | 5  |

| 4 | Board Layout                    | 6  |

| 5 | Schematic and List of Materials | 10 |

#### List of Figures

| 1  | Loop Response Measurement Modification                                                                      | 3  |

|----|-------------------------------------------------------------------------------------------------------------|----|

| 2  | TPS62842 Thermal Performance (V <sub>IN</sub> = 6.5 V, V <sub>OUT</sub> = 3.6 V, I <sub>OUT</sub> = 750 mA) | 5  |

| 3  | Top Assembly                                                                                                | 6  |

| 4  | Top Layer                                                                                                   | 6  |

| 5  | Internal Layer 1                                                                                            |    |

| 6  | Internal Layer 2                                                                                            | 7  |

| 7  | Bottom Layer                                                                                                | 8  |

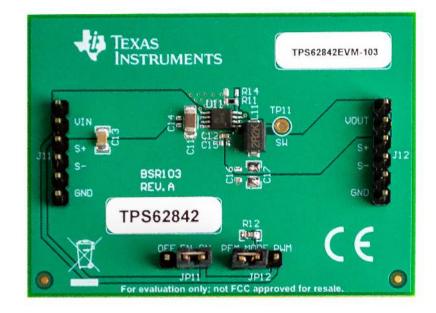

| 8  | TPS62842EVM-103 Angled View                                                                                 | 8  |

| 9  | TPS62842EVM-103 Top View                                                                                    | 9  |

| 10 | TPS62842EVM-103 Schematic                                                                                   | 10 |

|    |                                                                                                             |    |

#### List of Tables

| 1 | Performance Specification Summary | 2  |

|---|-----------------------------------|----|

| 2 | TPS62842EVM-103 List of Materials | 10 |

## Trademarks

## 1 Introduction

The TPS6284x is a family of synchronous, step-down converters in different packages. The TPS62842EVM-103 contains the TPS62842DGR device in a DGR package. The DGR package is a bigger package than DLC (SON) and YBG (WCSP) packages but it has better thermal performance.

## 1.1 Performance Specification

Table 1 provides a summary of the TPS62842EVM-103 performance specifications.

| SPECIFICATION  | MIN | ТҮР | МАХ | UNIT |

|----------------|-----|-----|-----|------|

| Input voltage  | 1.8 | 3.6 | 6.5 | V    |

| Output voltage |     | 3.3 |     | V    |

| Output current | 0   |     | 750 | mA   |

#### **Table 1. Performance Specification Summary**

## 1.2 Modifications

The printed-circuit board (PCB) for this EVM uses the adjustable output voltage version of this integrated circuit (IC). Additional input and output capacitors can also be added. Finally, the loop response of the IC can be measured.

## 1.2.1 Adjusting the Output Voltage

The output voltage is adjusted though the choice of R11 and R14 resistors. Since R11 and R14 are in parallel, only R11 or R14 should be installed at the same time. R11 and R14 are 0603 sizes to make it easy to change the output voltage by replacing them. However, 0201 size resistors can also be used to reduce the total solution size.

## 1.2.2 Input and Output Capacitors

C14 is provided for an additional input capacitor. This capacitor is not required for proper operation but can be used to reduce the input voltage ripple.

C15, C16, and C17 are provided for additional output capacitors. These capacitors are not required for proper operation but can be used to reduce the output voltage ripple and to improve the load transient response. The total output capacitance must remain within the recommended range in the data sheet for proper operation.

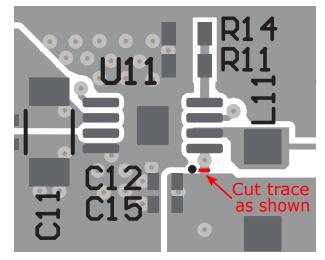

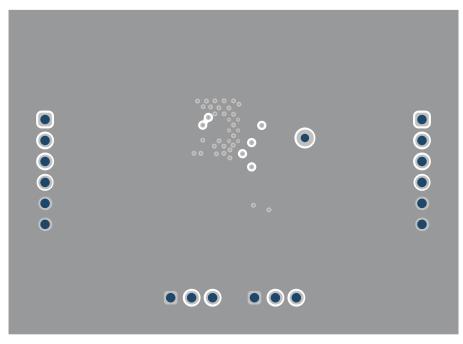

## 1.2.3 Loop Response Measurement

The loop response of the EVM can be measured with two simple changes to the circuitry. First, cut the trace between the VOS pin and the output capacitor on the top layer. This change is shown in Figure 1. Second, install a 10- $\Omega$  resistor across the resistor pads on the back of the PCB at R13. The pads are spaced to allow installation of an 0603-sized resistor. With these changes, an ac signal (10-mV, peak-to-peak amplitude recommended) can be injected into the control loop across the added resistor. Details of measuring the control loop of DCS-Control devices are found in *How to Measure the Control Loop of DCS-Control*<sup>TM</sup> Devices.

Figure 1. Loop Response Measurement Modification

TEXAS INSTRUMENTS

www.ti.com

Setup

## 2 Setup

This section describes how to properly use the TPS62842EVM-103.

## 2.1 Input/Output Connector Descriptions

| J11, Pin 1 and 2 – VIN   | Positive input connection from the input supply for the EVM.                                                                                                                                                                             |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J11, Pin 3 and 4 – S+/S- | Input voltage sense connections. Measure the input voltage at this point.                                                                                                                                                                |

| J11, Pin 5 and 6 – GND   | Input return connection from the input supply for the EVM.                                                                                                                                                                               |

| J12, Pin 1 and 2 – VOUT  | Output voltage connection.                                                                                                                                                                                                               |

| J12, Pin 3 and 4 – S+/S- | Output voltage sense connections. Measure the output voltage at this point.                                                                                                                                                              |

| J12, Pin 5 and 6 – GND   | Output return connection.                                                                                                                                                                                                                |

| JP11 – EN                | EN pin input jumper. Place the supplied jumper across ON and EN to turn on the IC. Place the jumper across OFF and EN to turn off the IC.                                                                                                |

| JP12 – MODE              | MODE pin input jumper. Place the supplied jumper across PWM and MODE to operate in forced PWM mode. Place the jumper across PFM and MODE to operate in power save mode with an automatic transition to PWM mode at higher load currents. |

## 2.2 Setup

To operate the EVM, set jumpers JP11 through JP13 to the desired position per Section 2.1. Connect the input supply to J11 and connect the load to J12.

# 3 TPS62842EVM-103 Test Results

The TPS62842EVM-103 was used to take all the data in the 1.8V-6.5V, 750mA, 60nA  $I_{Q}$  Step-Down Converter data sheet. See the device data sheet for the performance of this EVM.

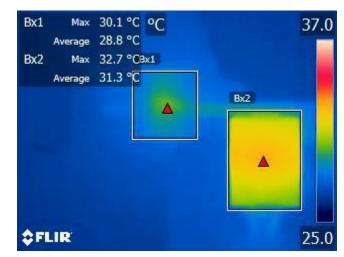

Figure 2 shows the thermal performance of the EVM.

Figure 2. TPS62842 Thermal Performance ( $V_{IN}$  = 6.5 V,  $V_{OUT}$  = 3.6 V,  $I_{OUT}$  = 750 mA)

Board Layout

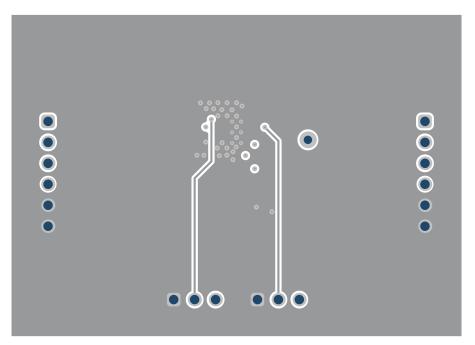

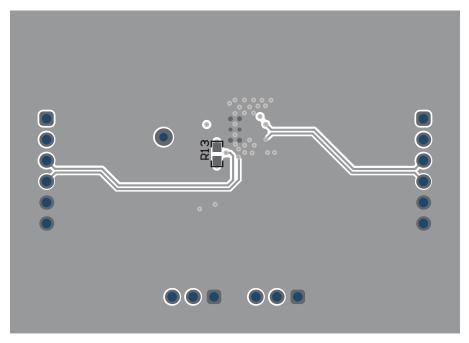

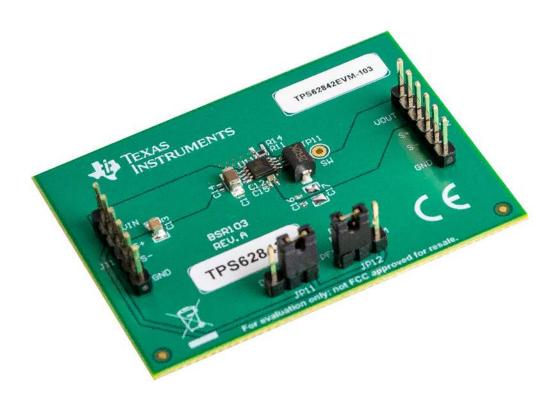

## 4 Board Layout

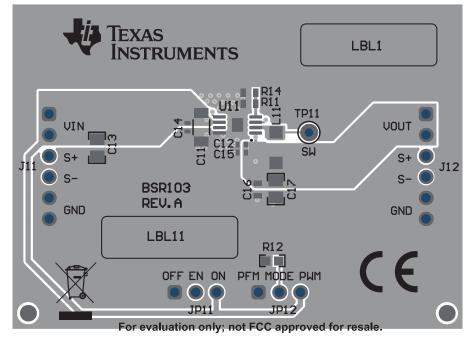

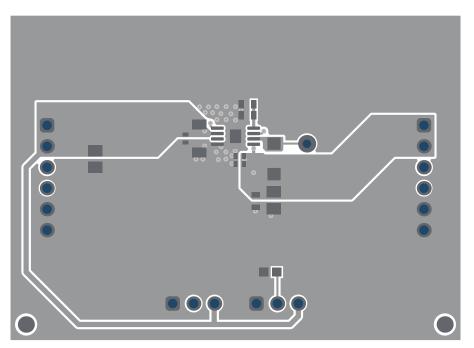

This section provides the TPS62842EVM-103 board layout and illustrations in Figure 3 through Figure 9.

Figure 3. Top Assembly

Figure 4. Top Layer

Figure 5. Internal Layer 1

Figure 6. Internal Layer 2

Figure 7. Bottom Layer

Figure 8. TPS62842EVM-103 Angled View

Figure 9. TPS62842EVM-103 Top View

# 5 Schematic and List of Materials

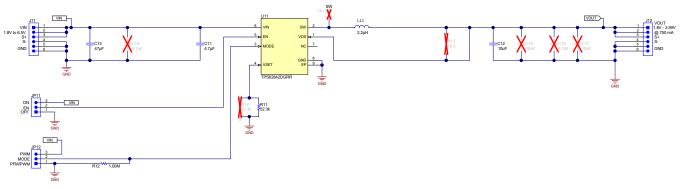

This section provides the TPS62842EVM-103 schematic and List of Materials.

# 5.1 Schematic

Figure 10 illustrates the TPS62842EVM-103 schematic.

Figure 10. TPS62842EVM-103 Schematic

## 5.2 List of Materials

Table 2 lists the TPS62842EVM-103 list of materials.

| REF DES | QTY | DESCRIPTION                                                                     | PART NUMBER        | MANUFACTURER      |

|---------|-----|---------------------------------------------------------------------------------|--------------------|-------------------|

| C11     | 1   | Capacitor, ceramic, 4.7 µF, 50 V, ±20%, X7R, 1206                               | GRM31CR71H475MA12L | Murata            |

| C12     | 1   | Capacitor, ceramic, 10 µF, 6.3 V, ±20%, X5R, 0402                               | GRM155R60J106ME15D | Murata            |

| C13     | 1   | Capacitor, ceramic, 47 µF, 10 V, ±20%, X5R, 0805                                | GRM21BR61A476ME15L | Murata            |

| L11     | 1   | Inductor, Unshielded, metal composite, 2.2 $\mu H,$ 850 mA, 180 m $\Omega,$ SMD | CC453232-2R2KL     | Bourns            |

| R11     | 1   | Resistor, 52.3 kΩ, 1%, 0.05 W, 0201                                             | Std                | Std               |

| R12     | 1   | Resistor, 1.00 MΩ, 1%, 0.1 W, 0603                                              | Std                | Std               |

| U11     | 1   | 1.8 V to 6.5 V, 750 mA, 60 nA $\rm I_Q$ Step Down Converter in DGR Package      | TPS62842DGR        | Texas Instruments |

#### Table 2. TPS62842EVM-103 List of Materials

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated