Data Sheet

SST12LP14A is a versatile power amplifier based on the highly-reliable InGaP/ GaAs HBT technology. Easily configured for high-power applications with good power-added efficiency while operating over the 2.4-2.5 GHz frequency band, it typically provides 29 dB gain with 23% power-added efficiency at 22 dBm. SST12LP14A has excellent linearity while meeting 802.11g spectrum mask at 23 dBm. The excellent on-chip power detector provides a reliable solution to boardlevel power control. SST12LP14A is offered in 16-contact VQFN package.

#### **Features**

- · High Gain:

- Typically 29 dB gain across 2.4~2.5 GHz over temperature 0°C to +85°C

- High linear output power:

- ->28 dBm P1dB

- Please refer to "Absolute Maximum Stress Ratings" on

- Meets 802.11g OFDM ACPR requirement up to 23 dBm

- ∼3% added EŬM up to 21 dBm for

- 54 Mbps 802.11g signal

Meets 802.11b ACPR requirement up to 23 dBm

- High power-added efficiency/Low operating current for both 802.11g/b applications

- ~23%/210 mA @ P<sub>OUT</sub> = 22 dBm for 802.11g ~25%/240 mA @ P<sub>OUT</sub> = 23 dBm for 802.11b

- Single-pin low I<sub>REF</sub> power-up/down control

- $-I_{RFF}$  < 2 mA

- Low idle current

- -~70 mA Ico

- High-speed power-up/down

- Turn on/off time (10%- 90%) <100 ns

- Typical power-up/down delay with driver delay included <200 ns

- · High temperature stability

- ~1 dB gain/power variation between 0°C to +85°C

- Low shut-down current (< 0.1 μA)

- Excellent On-chip power detection

- -<+/- 0.3dB variation between 0°C to +85°C

- -<+/- 0.4dB variation with 2:1 VSWR mismatch

- -<+/- 0.3dB variation Ch1 through Ch14

- 20 dB dynamic range on-chip power detection

- Simple input/output matching

- Packages available

- 16-contact VQFN 3mm x 3mm

- All non-Pb (lead-free) devices are RoHS compliant

#### **Applications**

- WLAN (IEEE 802.11b/g/n)

- Home RF

- Cordless phones

- 2.4 GHz ISM wireless equipment

**Data Sheet**

#### **Product Description**

SST12LP14A is a versatile power amplifier based on the highly-reliable InGaP/GaAs HBT technology.

The SST12LP14A can be easily configured for high-power applications with good power-added efficiency while operating over the 2.4- 2.5 GHz frequency band. It typically provides 29 dB gain with 23% power-added efficiency @  $P_{OUT}$  = 22 dBm for 802.11g and 25% power-added efficiency @  $P_{OUT}$  = 23 dBm for 802.11b.

The SST12LP14A has excellent linearity, typically ~3% added EVM at 21 dBm output power with 54 Mbps 802.11g operation while meeting 802.11g spectrum mask at 23 dBm. The SST12LP14A can also be configured for high-efficiency operation (typically 85 mA total power consumption at 17 dBm linear 54 Mbps 802.11g output power) which is desirable in embedded applications such as in handheld units.

The SST12LP14A also features easy board-level usage along with high-speed power-up/down control through a single combined reference voltage pin. Ultra-low reference current (total I<sub>REF</sub> ~2 mA) makes the SST12LP14A controllable by an on/off switching signal directly from the baseband chip. These features coupled with low operating current make the SST12LP14A ideal for the final stage power amplification in battery-powered 802.11b/g/n WLAN transmitter applications.

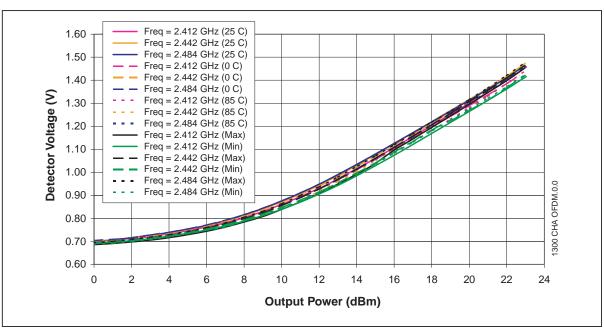

SST12LP14A has an excellent on-chip, single-ended power detector, which features a wide dynamic-range (>15 dB) with dB-wise linear operation and high stability over temperature (< +/-0.3 dB 0°C to +85°C), frequency (<+/-0.3 dB across Channels 1 through 14), and output load (<+/-0.4 dB with 2:1 output VSWR all phases). The excellent on-chip power detector provides a reliable solution to board-level power control.

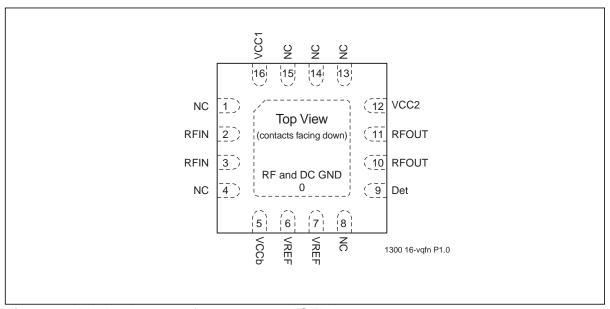

The SST12LP14A is offered in 16-contact VQFN package. See Figure 2 for pin assignments and Table 1 for pin descriptions.

Data Sheet

#### **Functional Blocks**

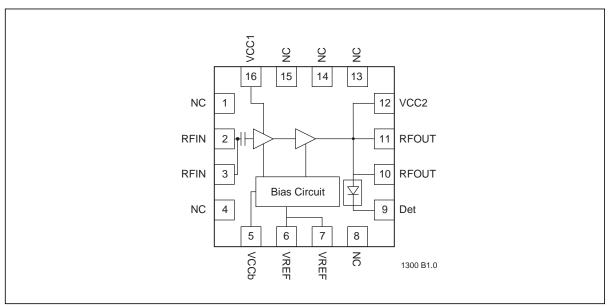

Figure 1: Functional Block Diagram

Data Sheet

### **Pin Assignments**

Figure 2: Pin Assignments for 16-contact VQFN

### **Pin Descriptions**

Table 1: Pin Description

| Symbol | Pin No. | Pin Name      | Type <sup>1</sup> | Function                                                                                         |

|--------|---------|---------------|-------------------|--------------------------------------------------------------------------------------------------|

| GND    | 0       | Ground        |                   | The center pad should be connected to RF ground with several low inductance, low resistance vias |

| NC     | 1       | No Connection |                   | Unconnected pin                                                                                  |

| RFIN   | 2       |               | I                 | RF input, DC decoupled                                                                           |

| RFIN   | 3       |               | I                 | RF input, DC decoupled                                                                           |

| NC     | 4       | No Connection |                   | Unconnected pin                                                                                  |

| VCCb   | 5       | Power Supply  | PWR               | Supply voltage for bias circuit                                                                  |

| VREF   | 6       |               | PWR               | 1 <sup>st</sup> and 2 <sup>nd</sup> stage idle current control                                   |

| VREF   | 7       |               | PWR               | 1st and 2nd stage idle current control                                                           |

| NC     | 8       | No Connection |                   | Unconnected pin                                                                                  |

| Det    | 9       |               | 0                 | On-chip power detector                                                                           |

| RFOUT  | 10      |               | 0                 | RF output                                                                                        |

| RFOUT  | 11      |               | 0                 | RF output                                                                                        |

| VCC2   | 12      | Power Supply  | PWR               | Power supply, 2 <sup>nd</sup> stage                                                              |

| NC     | 13      | No Connection |                   | Unconnected pin                                                                                  |

| NC     | 14      | No Connection |                   | Unconnected pin                                                                                  |

| NC     | 15      | No Connection |                   | Unconnected pin                                                                                  |

| VCC1   | 16      | Power Supply  | PWR               | Power supply, 1 <sup>st</sup> stage                                                              |

1. I=Input, O=Output

T1.0 75045

**Data Sheet**

#### **Electrical Specifications**

The AC and DC specifications for the power amplifier interface signals. Refer to Table 3 for the DC voltage and current specifications. Refer to Figures 3 through 18 for the RF performance.

**Absolute Maximum Stress Ratings** (Applied conditions greater than those listed under "Absolute Maximum Stress Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.)

| Input power to pins 2 and 3 (P <sub>IN</sub> )          | +5 dBm               |

|---------------------------------------------------------|----------------------|

| Average output power (P <sub>OUT</sub> ) <sup>1</sup>   | +26 dBm              |

| Supply Voltage at pins 5, 12, and 16 (V <sub>CC</sub> ) | 0.3V to +4.6V        |

| Reference voltage to pins 6 and 7 (V <sub>REF</sub> )   | 0.3V to +3.3V        |

| DC supply current (I <sub>CC</sub> )                    | 400 mA               |

| Operating Temperature (T <sub>A</sub> )                 | 40°C to +85°C        |

| Storage Temperature (T <sub>STG</sub> )                 | 40°C to +120°C       |

| Maximum Junction Temperature (T <sub>J</sub> )          | +150°C               |

| Surface Mount Solder Reflow Temperature                 | 260°C for 10 seconds |

<sup>1.</sup> Never measure with CW source. Pulsed single-tone source with <50% duty cycle is recommended. Exceeding the maximum rating of average output power could cause permanent damage to the device.

Table 2: Operating Range

| Range      | Ambient Temp   | V <sub>DD</sub> |

|------------|----------------|-----------------|

| Industrial | -40°C to +85°C | 3.3V            |

T2.1 75045

Table 3: DC Electrical Characteristics

| Symbol           | Parameter                                        | Min. | Тур  | Max. | Unit | Test Conditions |

|------------------|--------------------------------------------------|------|------|------|------|-----------------|

| $V_{CC}$         | Supply Voltage at pins 5, 12, 16                 | 3.0  | 3.3  | 4.2  | V    |                 |

| Icc              | Supply Current                                   |      |      |      |      |                 |

|                  | for 802.11g, 22 dBm                              |      | 210  |      | mΑ   |                 |

|                  | for 802.11b, 23 dBm                              |      | 230  |      | mΑ   |                 |

| Icq              | Idle current for 802.11g to meet EVM<4% @ 21dBm  |      | 70   |      | mA   |                 |

| I <sub>OFF</sub> | Shut down current                                |      |      | 0.1  | μΑ   |                 |

| V <sub>REG</sub> | Reference Voltage for, with $110\Omega$ resistor | 2.75 | 2.85 | 2.95 | V    |                 |

T3.1 75045

**Data Sheet**

Table 4: AC Electrical Characteristics for Configuration

| Symbol            | Parameter                                     | Min. | Тур | Max. | Unit |

|-------------------|-----------------------------------------------|------|-----|------|------|

| F <sub>L-U</sub>  | Frequency range                               | 2400 |     | 2485 | MHz  |

| Pout              | Output power                                  |      |     |      |      |

|                   | @ PIN = -6 dBm 11b signals                    | 22   |     |      | dBm  |

|                   | @ PIN = -7 dBm 11g signals                    | 21   |     |      | dBm  |

| G                 | Small signal gain                             | 28   | 29  |      | dB   |

| G <sub>VAR1</sub> | Gain variation over band (2400~2485 MHz)      |      |     | ±0.5 | dB   |

| G <sub>VAR2</sub> | Gain ripple over channel (20 MHz)             |      | 0.2 |      | dB   |

| ACPR              | Meet 11b spectrum mask                        | 22   | 23  |      | dBm  |

|                   | Meet 11g OFDM 54 Mbps spectrum mask           | 22   | 23  |      | dBm  |

| Added EVM         | @ 21 dBm output with 11g OFDM 54 Mbps signal  |      | 3   |      | %    |

| 2f, 3f, 4f, 5f    | Harmonics at 22 dBm, without external filters |      |     | -40  | dBc  |

T4.2 75045

**Data Sheet**

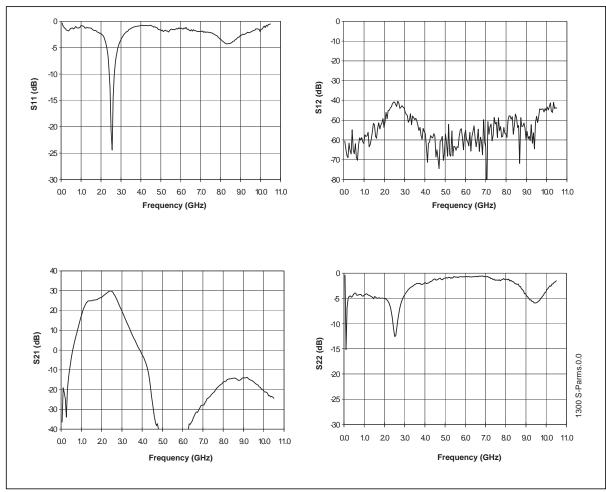

### **Typical Performance Characteristics**

Test Conditions:  $V_{CC} = 3.3V$ ,  $T_A = 25$ °C, unless otherwise specified

Figure 3: S-Parameters

**Data Sheet**

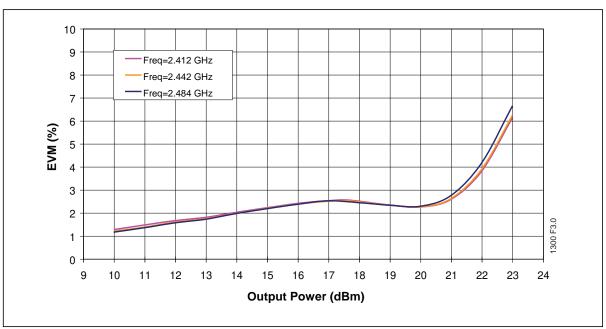

### **Typical Performance Characteristics**

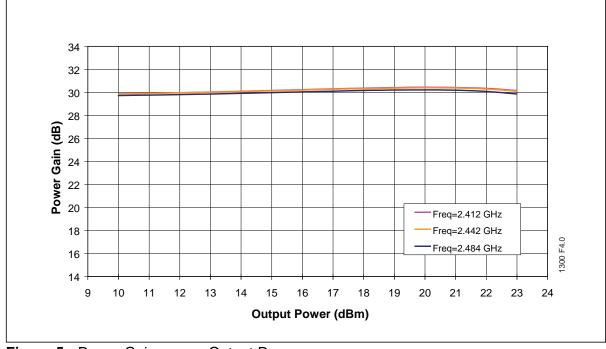

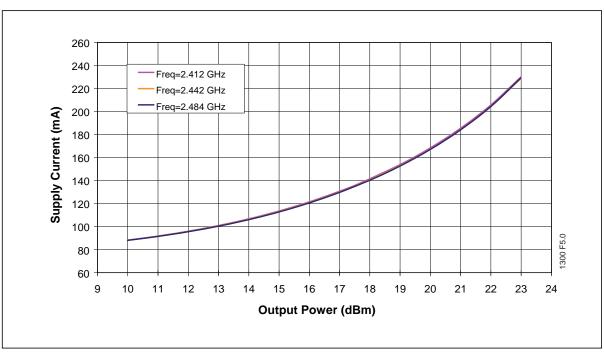

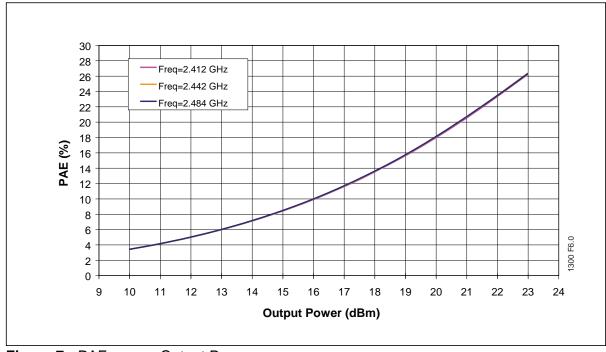

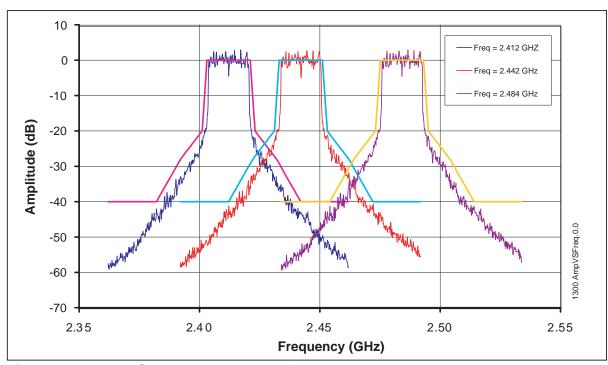

Test Conditions: V<sub>CC</sub> = 3.3V, T<sub>A</sub> = 25°C, 54 Mbps 802.11g OFDM signal

Figure 4: EMV versus Output Power using Sequence plus Equalizer Channel Estimation

Figure 5: Power Gain versus Output Power

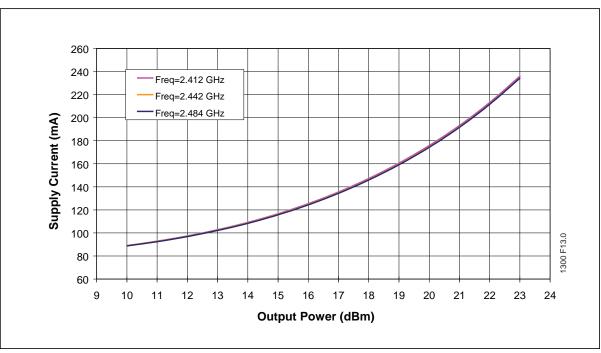

Figure 6: Total Current Consumption for 802.11g operation versus Output Power

Figure 7: PAE versus Output Power

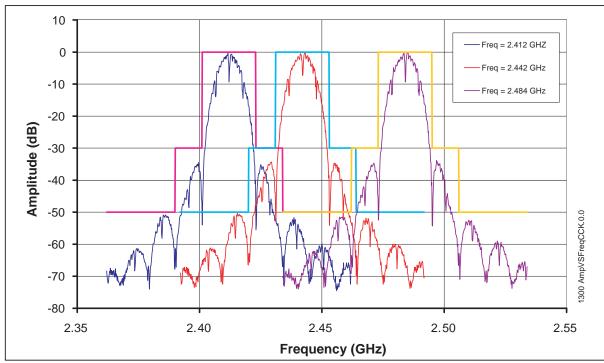

Figure 8: 802.11g Spectrum Mask at 23 dBm

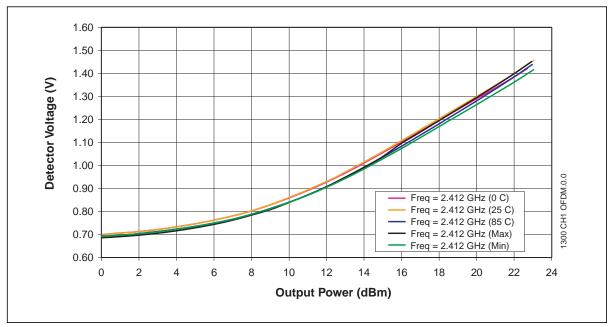

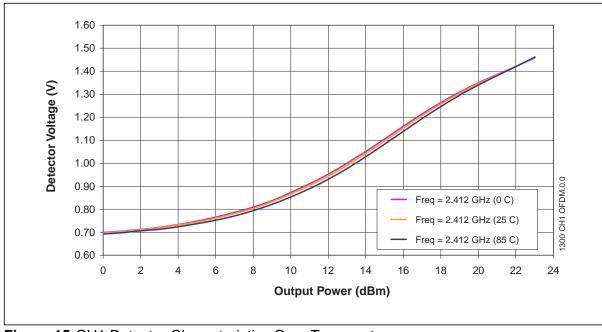

Figure 9: CH1 Detector Characteristics Over Temperature with 2:1 Output VSWR All Phases

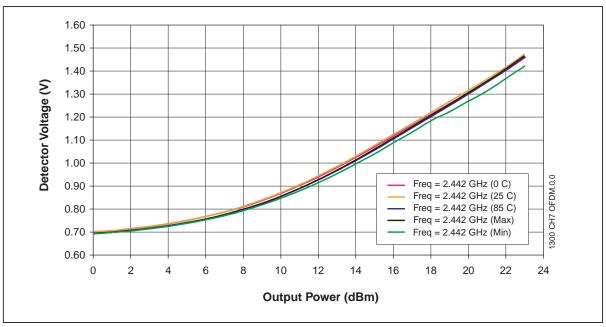

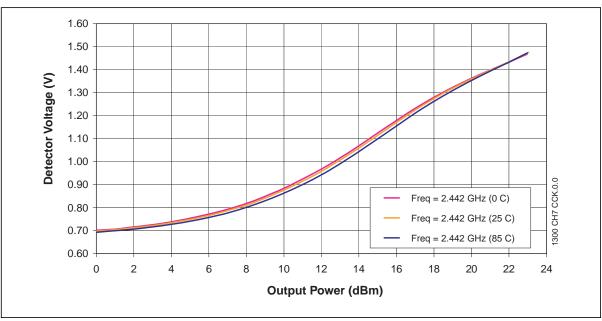

Figure 10:CH7 Detector Characteristics Over Temperature with 2:1 Output VSWR All **Phases**

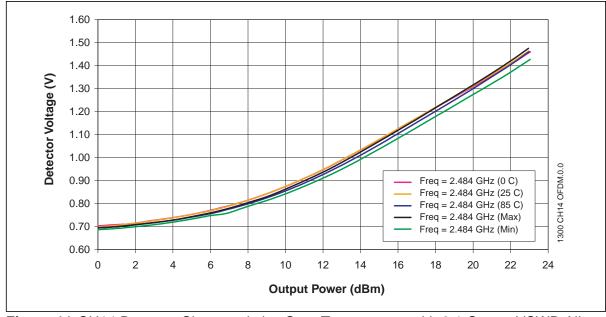

Figure 11:CH14 Detector Characteristics Over Temperature with 2:1 Output VSWR All **Phases**

**Figure 12:** Detector Characteristics Over Temperature and Over Frequency with 2:1 Output VSWR All Phases

**Data Sheet**

### **Typical Performance Characteristics**

Test Conditions: V<sub>CC</sub> = 3.3V, T<sub>A</sub> = 25°C, 1 Mbps 802.11B CCK signal

Figure 13:802.11B Spectrum Mask at 23 dBm

Figure 14: Total Current Consumption for 802.11B Operation versus Output Power

Figure 15:CH1 Detector Characteristics Over Temperature

Figure 16:CH7 Detector Characteristics Over Temperature

**Data Sheet**

### **Typical Performance Characteristics**

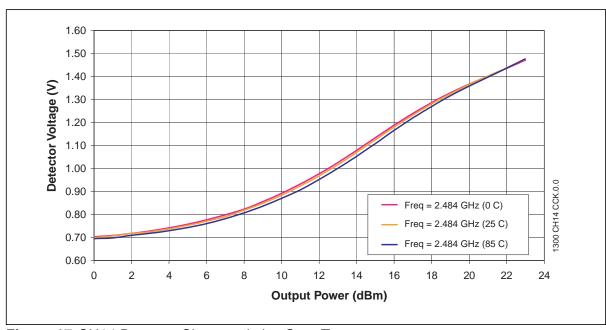

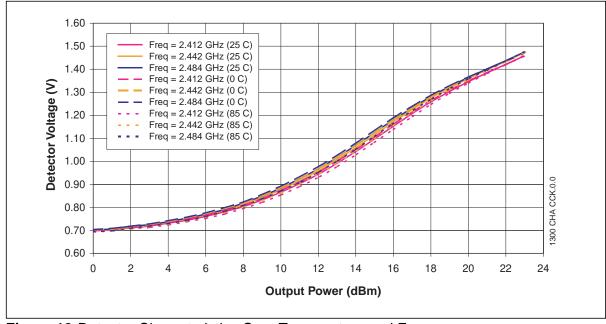

Test Conditions: V<sub>CC</sub> = 3.3V, T<sub>A</sub>=25°C, 1 Mbps 802.11B CCK signal

Figure 17:CH14 Detector Characteristics Over Temperature

Figure 18: Detector Characteristics Over Temperature and Frequency

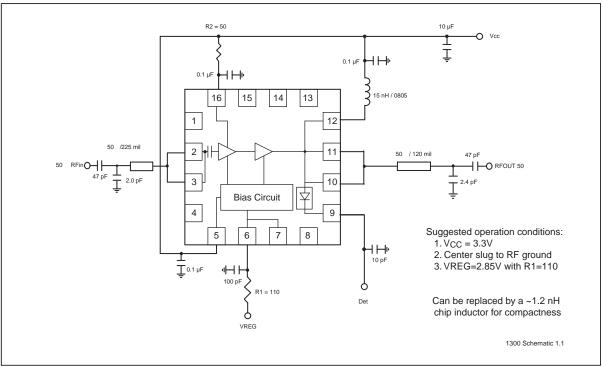

Figure 19: Typical Schematic for High-Power/High-Efficiency 802.11b/g Applications

**Data Sheet**

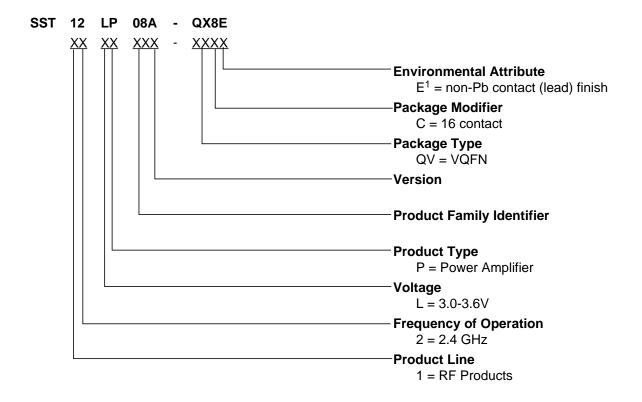

### **Product Ordering Information**

Environmental suffix "E" denotes non-Pb solder. SST non-Pb solder devices are "RoHS Compliant".

#### Valid combinations for SST12LP14A

SST12LP14A-QVCE

#### SST12LP14A Evaluation Kits

SST12LP14A-QVCE-K

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your SST sales representative to confirm availability of valid combinations and to determine availability of new combinations.

**Data Sheet**

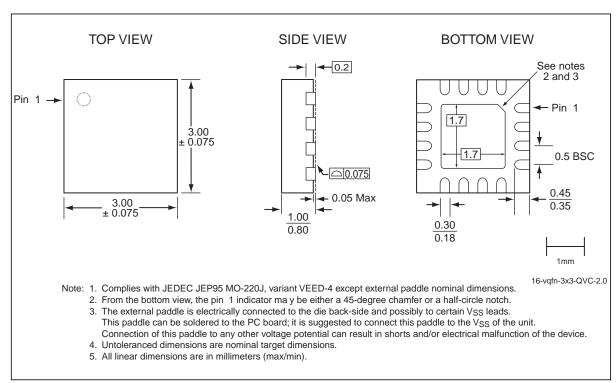

#### **Packaging Diagrams**

**Figure 20:**16-Contact Very-thin Quad Flat No-lead (VQFN) SST Package Code: QVC

**Data Sheet**

#### Table 5: Revision History

| Revision | Description                                                          | Date     |

|----------|----------------------------------------------------------------------|----------|

| 00       | Initial release of data sheet                                        | Jun 2005 |

| 01       | Removed Stability and Ruggedness parms from Table 4 on page 6        | Sep 2005 |

|          | <ul> <li>Updated the schematic in Figure 19 on page 17</li> </ul>    |          |

| 02       | Updated the schematic in Figure 19 on page 17                        | Mar 2006 |

|          | • Updated Figures 4, 5, 6, 7, and 14                                 |          |

|          | Made minor updates to the "Features" section                         |          |

|          | Made minor updates to the "Electrical Specifications" section        |          |

|          | Applied new format.                                                  |          |

| 03       | Updated document status from Preliminary Specification to Data Sheet | Apr 2008 |

| 04       | Updated "Contact Information" on page 18.                            | Feb 2009 |

| А        | Updated "Features" and "Electrical Specifications"                   | Feb 2012 |

|          | <ul> <li>Updated maximum voltage from 4.2V to 4.6V.</li> </ul>       |          |

|          | Applied new document format                                          |          |

|          | Released document under letter revision system                       |          |

|          | Updated Spec number from S71300 to DS75045                           |          |

#### ISBN:978-1-61341-844-4

© 2012 Silicon Storage Technology, Inc-a Microchip Technology Company. All rights reserved.

SST, Silicon Storage Technology, the SST logo, SuperFlash, MTP, and FlashFlex are registered trademarks of Silicon Storage Technology, Inc. MPF, SQI, Serial Quad I/O, and Z-Scale are trademarks of Silicon Storage Technology, Inc. All other trademarks and registered trademarks mentioned herein are the property of their respective owners.

Specifications are subject to change without notice. Refer to www.microchip.com for the most recent documentation. For the most current package drawings, please see the Packaging Specification located at http://www.microchip.com/packaging.

Memory sizes denote raw storage capacity; actual usable capacity may be less.

SST makes no warranty for the use of its products other than those expressly contained in the Standard Terms and Conditions of Sale.

For sales office locations and information, please see www.microchip.com.

Silicon Storage Technology, Inc. A Microchip Technology Company www.microchip.com