## TERASIC

# USERMANUAL

XTS-FMC

Copyright © Terasic Inc. All Rights Reserved.

# TABLE OF CONTENTS

| Chapter 1     | Introduction2                                     |

|---------------|---------------------------------------------------|

| 1.1 Features  | 2                                                 |

| 1.2 The Pack  | kage Contents                                     |

| 1.3 Assembl   | e XTS-FMC with FPGA Main board                    |

| 1.4 Getting I | Help5                                             |

| Chapter 2     | Board Specification6                              |

| 2.1 Layout a  | and Components                                    |

| 2.2 Block Di  | iagram7                                           |

| 2.3 Mechani   | cal Specifications                                |

| 2.4 How to c  | distinguish the board revision9                   |

| Chapter 3     | Board Components11                                |

| 3.1 FMC Ex    | pansion Connector                                 |

| 3.2 2x6 TMI   | D GPIO Expansion Header15                         |

| Chapter 4     | Demonstrations                                    |

| 4.1 XTS-FM    | IC Loopback on the TR517                          |

| 4.2 XTS-FM    | IC Loopback on the Han Pilot Platform20           |

| 4.3 XTS-FM    | IC SuperLite Loopback on the Han Pilot Platform23 |

| Appendix      | 27                                                |

| Revision History | 27 |

|------------------|----|

|------------------|----|

1

www.terasic.com

## Chapter 1 *Introduction*

The XTS-FMC daughter card is designed to convert FPGA transceiver channels to SMA connectors through a FPGA Mezzanine Card(FMC) interface. It is intended to allow users to evaluate the performance of transceiver-based host boards with FMC interface specifically the Stratix, Arria and Cyclone FPGA with integrated transceivers. Through the SMA connectors, the FPGA transceiver signals can be easily connected to measurement instruments as well as allowing gigabit data rate communication between multiple FPGA boards.

The XTS-FMC daughter card is the ideal platform to allow users to prototype and test their high-speed interfaces quickly and easily in support of transceiver performance for jitter, protocol compliance, and equalization.

### **1.1 Features**

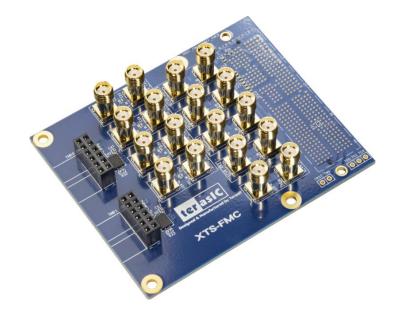

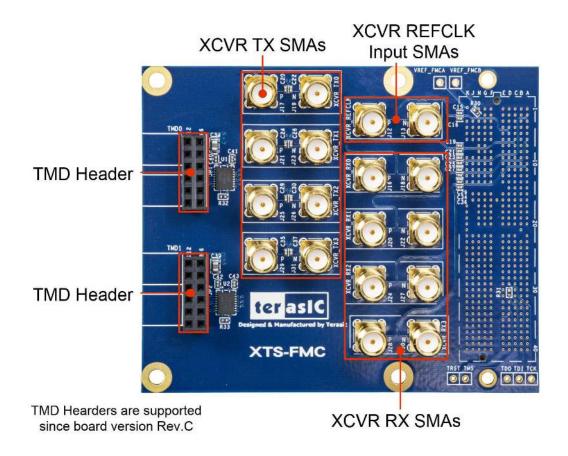

**Figure 1-1** shows the photo of the XTS-FMC card. The important functions of the XTS-FMC card are listed below:

- Convert FPGA transceiver channels to SMA connectors through FMC connector

- Support maximum 4 transceiver channels (Depend on the FPGA host board)

- SMA connectors for external clock input

- Two 2x6 TMD( Terasic Mini Digital ) Expansion Headers (since board version Rev.C)

Figure 1-1 The XTS-FMC Card.

XTS-FMC User Manual 2

## **1.2 The Package Contents**

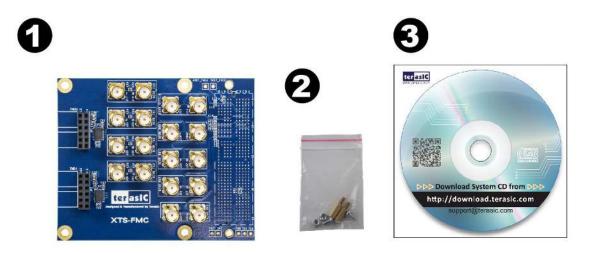

The XTS-FMC kit comes with the following items (see Figure 1-2):

- 1. **XTS-FMC** Daughter Card

- 2. Screw & Copper Pillar Package

- 3. CD Download Guide

The system CD contains technical documents of the XTS-FMC card, which include component datasheets, demonstrations, schematic and user manual. Users can download the CD from the link below:

#### http://xts-fmc.terasic.com/cd

Figure 1-2 The contents of the XTS-FMC card.

### **1.3 Assemble XTS-FMC with FPGA Main board**

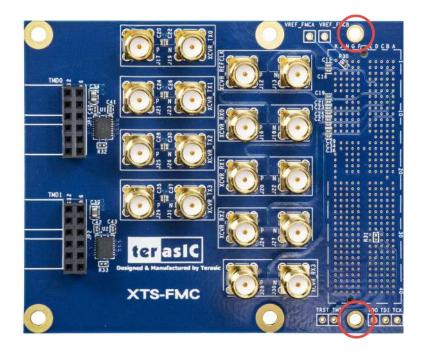

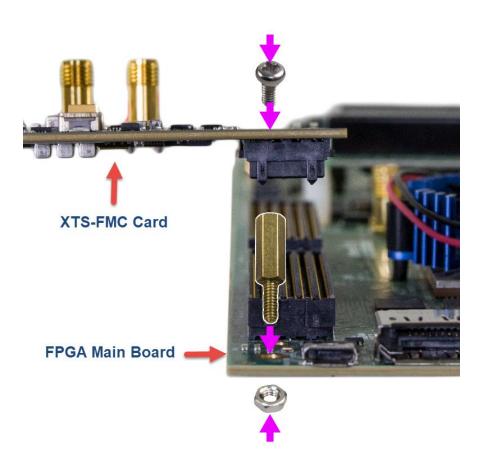

In order to make the XTS-FMC daughter card and the FMC connector on the FMC card with more secure hookup, the FMC side of the XTS-FMC daughter card has reserved two screw holes, as shown in Figure 1-3. Users can use the screws, copper pillars, and nuts that come with the XTS-FMC, to secure the XTS-FMC on the FPGA main board, as shown in Figure 1-4. Because transceiver is mostly used for high-speed transmission applications, we strongly recommend that users use the screws to secure the connection between the FPGA main board and the XTS-FMC card.

Figure 1-3 The two screw holes on XTS-FMC card.

Figure 1-4 Secure the XTS-FMC on the FPGA main board

XTS-FMC User Manual 4

www.terasic.com

## **1.4 Getting Help**

Here are the addresses where you can get help if you encounter any problems: Terasic Technologies 9F., No.176, Sec.2, Gongdao 5th Rd, East Dist, Hsinchu City, 30070. Taiwan Email: support@terasic.com Tel.: +886-3-575-0880 Website: xts-fmc.terasic.com

www.terasic.com

# Chapter 2 *Board Specification*

This chapter describes the architecture of the XTS card including block diagram and components.

#### **2.1 Layout and Components**

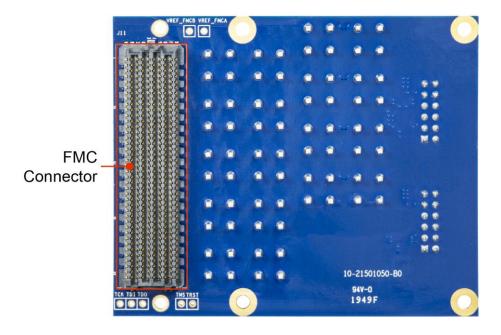

The picture of the XTS-FMC card is shown in **Figure 2-1** and **Figure 2-2**. It depicts the layout of the board and indicates the locations of the connectors and key components.

Figure 2-1 Mechanical Layout of the XTS-FMC card

www.terasic.com

Figure 2-2 Mechanical Layout of the XTS-FMC card

The following components are provided on the XTS-FMC card:

- FMC expansion connector (J11)

- TX SMAs (J17/J19,J21/J23,J25/J26,J29/J31)

- RX SMAs (J16/J18,J20/J22,J24/J27,J28/J30)

- XCVR reference input SMAs (J12/J13)

- TMD Headers(JP1/JP2)

#### **2.2 Block Diagram**

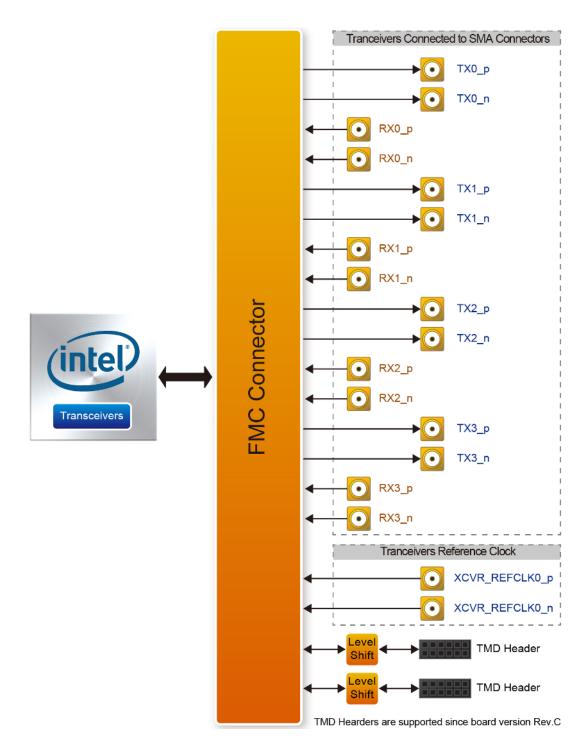

Figure 2-3 is the block diagram of the XTS-FMC card.

Figure 2-3 Block diagram of the XTS-FMC card

### **2.3 Mechanical Specifications**

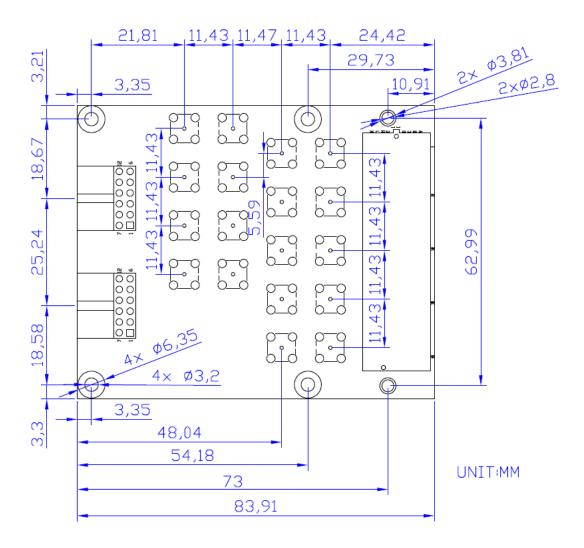

Figure 2-3 is the mechanical layout of the XTS-FMC board.

terasic XTS-FMC User Manual 8

Figure 2-4 The mechanical layout of the XTS-FMC card

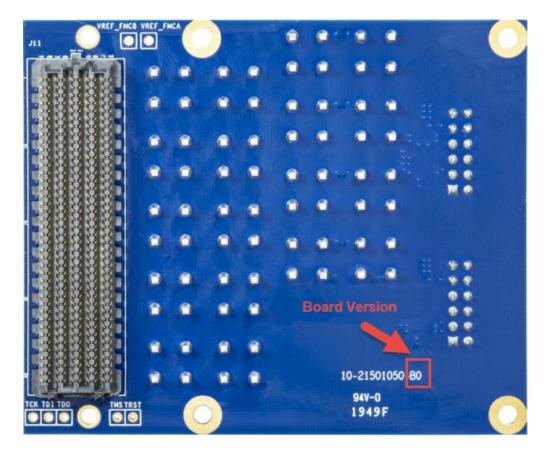

### 2.4 How to distinguish the board revision

On the bottom view of the PCB, there is a seal mark for the board hardware version. As shown in the figure below, if the letter inside the red circle is "B", it means that the PCB version is Rev. B.

Figure 2-5 The mechanical layout of the XTS-FMC card

# **Chapter 3 Board Components**

This chapter will describe the detailed information of the components, connector interface, and the pin mappings on the XTS-FMC card.

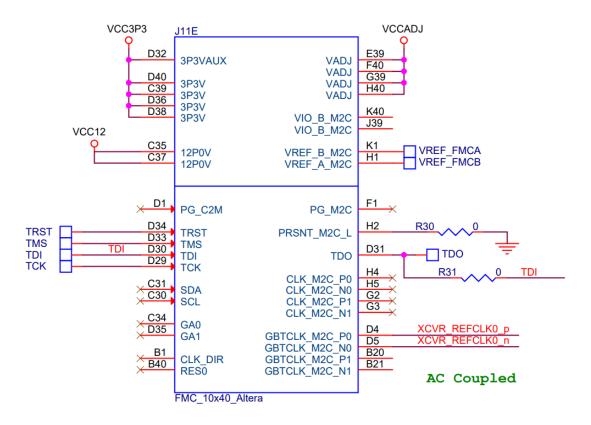

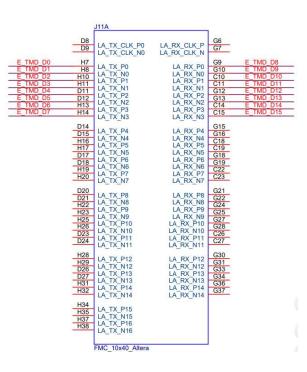

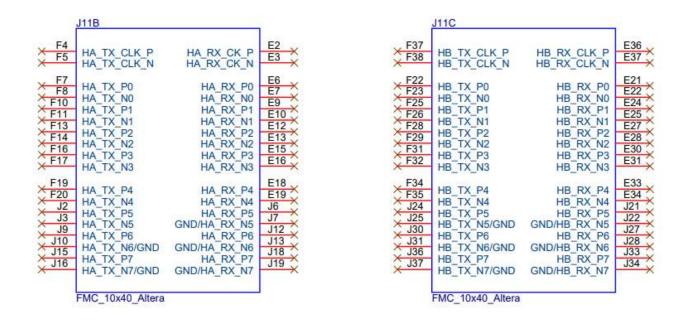

### **3.1 FMC Expansion Connector**

The XTS-FMC card contains an FPGA Mezzanine Card (FMC) connector. All the other interfaces on the XTS-FMC card are connected to the FMC connector. Figure 3-1, Figure 3-2, Figure 3-4, and show the pin-outs of the FMC connector and Table 3-1 lists the description of each signals corresponding to the FMC connector.

|            |              | J11D                   | 1                      | 1 and      |            |

|------------|--------------|------------------------|------------------------|------------|------------|

| XCVR_TX0_p | C2 ,         | DP C2M P0              | DP M2C P0              | C6         | XCVR_RX0_p |

| XCVR_TX0_n | C3           |                        | DP M2C P0              | C7         | XCVR_RX0_n |

| XCVR_TX1_p | A22          | DP_C2M_N0<br>DP_C2M_P1 | DP M2C P1              | A2         | XCVR_RX1_p |

| XCVR_TX1_n | A23          | DP C2M N1              | DP M2C PI              | A3         | XCVR_RX1_n |

| XCVR_TX2_p | A26          | DP C2M P2              | DP M2C P2              | A6         | XCVR_RX2_p |

| XCVR_TX2_n | A27          | DP C2M N2              | DP M2C N2              | A7         | XCVR_RX2_n |

| XCVR_TX3_p | A30          | DP C2M P3              | DP M2C P3              | A10        | XCVR RX3 p |

| XCVR_TX3_n | A31          | DP C2M N3              | DP M2C N3              | A11        | XCVR_RX3_n |

|            |              | DF_CZM_N5              | DF_WZG_WS              | 1000       |            |

|            | × A34        | DP C2M P4              | DP M2C P4              | A14        |            |

|            | A35          | DP C2M N4              | DP M2C N4              | A15 ×      |            |

|            | A38          | DP C2M P5              | DP M2C P5              | A18 ×      |            |

|            | A39<br>B36   | DP C2M N5              | DP M2C N5              | A19        |            |

|            | × B30<br>B37 | DP C2M P6              | DP M2C P6              | B16<br>B17 |            |

|            | × B37        | DP C2M N6              | DP M2C N6              | B12        |            |

|            | B33          | DP C2M P7              | DP M2C P7              | B13        |            |

|            | X DOD        | DP_C2M_N7              | DP_M2C_N7              | BISX       |            |

|            | B28          |                        | 55 M00 50              | B8 🗸       |            |

|            | C B29        | DP_C2M_P8              | DP_M2C_P8              | B9 ×       |            |

|            | C B24        | DP_C2M_N8<br>DP_C2M_P9 | DP_M2C_N8              | D4 V       |            |

|            | C B25        | DP_C2M_P9<br>DP_C2M_N9 | DP_M2C_P9<br>DP_M2C_N9 | D3 V       |            |

|            | C K22        | DP C2M P10/HB TX P8    | DP M2C P10/HA TX P8    | N4 V       |            |

|            | C K23        | DP C2M N10/HB TX N8    | DP M2C N10/HA TX N8    | K5 X       |            |

|            | C K25        | DP C2M P11/HB RX P8    | DP M2C P11/HA RX P8    | N          |            |

|            | × K26        | DP C2M N11/HB RX N8    | DP M2C N11/HA RX N8    | K8 🔶       |            |

|            | VK28         |                        |                        | K10 V      |            |

|            | × K20        | DP C2M P12/HB TX P9    | DP M2C P12/HA TX P9    | K11        |            |

|            | × K31        | DP C2M N12/HB TX N9    | DP M2C N12/HA TX N9    | K13        |            |

|            | × K32        | DP_C2M_P13/HB_RX_P9    | DP_M2C_P13/HA_RX_P9    | K14        |            |

|            | × K34        | DP_C2M_N13/HB_RX_N9    | DP_M2C_N13/HA_RX_N9    | K16        |            |

|            | × K35        | DP_C2M_P14/HB_TX_P10   | DP_M2C_P14/HA_TX_P10   | K17 X      |            |

|            | K37          | DP_C2M_N14/HB_TX_N10   | DP_M2C_N14/HA_TX_N10   | K19        |            |

|            | × K38        | DP_C2M_P15/HB_RX_P10   | DP_M2C_P15/HA_RX_P10   | K20        |            |

|            | XIII         | DP_C2M_N15/HB_RX_N10   | DP_M2C_N15/HA_RX_N10   | X          |            |

|            |              |                        |                        | 1. C       |            |

Figure 3-1 Signal names of XTS-FMC connector part 1

Figure 3-2 Signal names of XTS-FMC connector part 2

Figure 3-3 Signal names of XTS-FMC connector part 3

12

Figure 3-4 Signal names of XTS-FMC connector part 4

| Signal Name | FMC Pin | Direction | FMC Pin   | I/O Standard | Description             |

|-------------|---------|-----------|-----------|--------------|-------------------------|

|             | No.     |           |           |              |                         |

| XCVR_TX0_p  | PIN_C2  | Output    | DP_C2M_P0 | 1.4-V PCML   | SMA Transceiver         |

|             |         |           |           |              | Output Port0, connected |

|             |         |           |           |              | to J17(SMA)             |

| XCVR_TX0_n  | PIN_C3  | Output    | DP_C2M_N0 | 1.4-V PCML   | SMA Transceiver         |

|             |         |           |           |              | Output Port0, connected |

|             |         |           |           |              | to J19(SMA)             |

| XCVR_TX1_p  | PIN_A22 | Output    | DP_C2M_P1 | 1.4-V PCML   | SMA Transceiver         |

|             |         |           |           |              | Output Port1, connected |

|             |         |           |           |              | to J21(SMA)             |

| XCVR_TX1_n  | PIN_A23 | Output    | DP_C2M_N1 | 1.4-V PCML   | SMA Transceiver         |

|             |         |           |           |              | Output Port1, connected |

|             |         |           |           |              | to J23(SMA)             |

| XCVR_TX2_p  | PIN_A26 | Output    | DP_C2M_P2 | 1.4-V PCML   | SMA Transceiver         |

|             |         |           |           |              | Output Port2, connected |

|             |         |           |           |              | to J25(SMA)             |

| XCVR_TX2_n  | PIN_A27 | Output    | DP_C2M_N2 | 1.4-V PCML   | SMA Transceiver         |

|             |         |           |           |              | Output Port2, connected |

|             |         |           |           |              | to J26(SMA)             |

| XCVR_TX3_p  | PIN_A30 | Output    | DP_C2M_P3 | 1.4-V PCML   | SMA Transceiver         |

Table 3-1 FMC Pin Assignments

www.terasic.com

|                    |         |        |                   |            | Output Port3, connected<br>to J29(SMA)                      |

|--------------------|---------|--------|-------------------|------------|-------------------------------------------------------------|

| XCVR_TX3_n         | PIN_A31 | Output | DP_C2M_N3         | 1.4-V PCML | SMA Transceiver<br>Output Port3, connected<br>to J31(SMA)   |

| XCVR_RX0_p         | PIN_C6  | Input  | DP_M2C_P0         | 1.4-V PCML | SMA Transceiver<br>Input Port0, connected to<br>J16(SMA)    |

| XCVR_RX0_n         | PIN_C7  | Input  | DP_M2C_N0         | 1.4-V PCML | SMA Transceiver<br>Input Port0, connected to<br>J18(SMA)    |

| XCVR_RX1_p         | PIN_A2  | Input  | DP_M2C_P1         | 1.4-V PCML | SMA Transceiver<br>Input Port1, connected to<br>J20(SMA)    |

| XCVR_RX1_n         | PIN_A3  | Input  | DP_M2C_N1         | 1.4-V PCML | SMA Transceiver<br>Input Port1, connected to<br>J22(SMA)    |

| XCVR_RX2_p         | PIN_A6  | Input  | DP_M2C_P2         | 1.4-V PCML | SMA Transceiver<br>Input Port2, connected to<br>J24(SMA)    |

| XCVR_RX2_n         | PIN_A7  | Input  | DP_M2C_N2         | 1.4-V PCML | SMA Transceiver<br>Input Port2, connected to<br>J27(SMA)    |

| XCVR_RX3_p         | PIN_A10 | Input  | DP_M2C_P3         | 1.4-V PCML | SMA Transceiver<br>Input Port3, connected to<br>J28(SMA)    |

| XCVR_RX3_n         | PIN_A11 | Input  | DP_M2C_N3         | 1.4-V PCML | SMA Transceiver<br>Input Port3, connected to<br>J30(SMA)    |

| XCVR_REFCL<br>K0_p | PIN_D4  | Input  | GBTCLK_M2C<br>_P0 | LVDS       | External reference<br>clock input, connected to<br>J12(SMA) |

| XCVR_REFCL<br>K0_n | PIN_D5  | Input  | GBTCLK_M2C<br>_N0 | LVDS       | External reference<br>clock input, connected to<br>J13(SMA) |

| TMD_D0             | PIN_H7  | Inout  | LA_TX_P0          | 3.3V       | <b>JP1</b> TMD GPIO<br>Connection [0]                       |

| TMD_D1             | PIN_H8  | Inout  | LA_TX_N0          | 3.3V       | JP1 TMD GPIO<br>Connection [1]                              |

| TMD_D2             | PIN_H10 | Inout  | LA_TX_P1          | 3.3V       | JP1 TMD GPIO<br>Connection [2]                              |

| TMD_D3             | PIN_H11 | Inout  | LA_TX_N1          | 3.3V       | JP1 TMD GPIO<br>Connection [3]                              |

www.terasic.com

| N_D11 Inou | t LA_TX_P2                                                                                                                                                       | 3.3V                                                                                                                                                              | JP1 TMD GPIO                                                                                                                                                                                          |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [4]                                                                                                                                                                                        |

| N_D12 Inou | t LA_TX_N2                                                                                                                                                       | 3.3V                                                                                                                                                              | JP1 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [5]                                                                                                                                                                                        |

| N_H13 Inou | t LA_TX_P3                                                                                                                                                       | 3.3V                                                                                                                                                              | JP1 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [6]                                                                                                                                                                                        |

| N_H14 Inou | t LA_TX_N3                                                                                                                                                       | 3.3V                                                                                                                                                              | JP1 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [7]                                                                                                                                                                                        |

| N_G9 Inou  | t LA_RX_P0                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [0]                                                                                                                                                                                        |

| N_G10 Inou | t LA_RX_N0                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [1]                                                                                                                                                                                        |

| N_C10 Inou | t LA_RX_P1                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [2]                                                                                                                                                                                        |

| N_C11 Inou | t LA_RX_N1                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [3]                                                                                                                                                                                        |

| N_G12 Inou | t LA_RX_P2                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [4]                                                                                                                                                                                        |

| N_G13 Inou | t LA_RX_N2                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [5]                                                                                                                                                                                        |

| N_C14 Inou | t LA_RX_P3                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [6]                                                                                                                                                                                        |

| N_C15 Inou | t LA_RX_N3                                                                                                                                                       | 3.3V                                                                                                                                                              | JP2 TMD GPIO                                                                                                                                                                                          |

|            |                                                                                                                                                                  |                                                                                                                                                                   | Connection [7]                                                                                                                                                                                        |

|            | N_D12     Inou       N_H13     Inou       N_H14     Inou       N_G9     Inou       N_G10     Inou       N_C11     Inou       N_G12     Inou       N_C14     Inou | N_D12InoutLA_TX_N2N_H13InoutLA_TX_P3N_H14InoutLA_TX_N3N_G9InoutLA_RX_P0N_G10InoutLA_RX_N0N_C10InoutLA_RX_N1N_G12InoutLA_RX_P2N_G13InoutLA_RX_N2N_C14InoutLA_RX_P3 | N_D12InoutLA_TX_N23.3VN_H13InoutLA_TX_P33.3VN_H14InoutLA_TX_N33.3VN_G9InoutLA_RX_P03.3VN_G10InoutLA_RX_N03.3VN_C10InoutLA_RX_P13.3VN_G12InoutLA_RX_P23.3VN_G13InoutLA_RX_N23.3VN_C14InoutLA_RX_P33.3V |

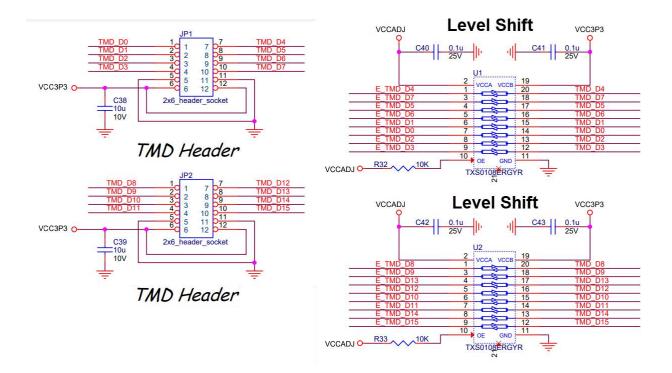

### **3.2 2x6 TMD GPIO Expansion Header**

The board has two 2x6 TMD (Terasic Mini Digital) expansion headers. The TMD header has 8 digital GPIO user pins connected to the FMC connector, two 3.3V power pins and two ground pins. In addition, a voltage level shift is left between the TMD and the FMC connector to allow the various VCCIO voltage level of different FPGA motherboards to be converted to 3.3v to the TMD header. Figure 2 24 shows the connection between the TMD header and FMC connector.

Figure 3-5 SMA loopback setup

## Chapter 4 *Demonstrations*

This chapter illustrates the transcevier loopback reference design for the XTS-FMC card.

### **4.1 XTS-FMC Loopback on the TR5**

The transceiver test code is used to verify 4 transceiver channels of the FMC connector through the XTS-FMC card and SMA cables. The transceiver channels are verified with PRBS31 test pattern and with the data rates. For 5SGXEA7N2F45C2 Device of the TR5 board, the data rate of the transceiver channel on the FMC connector runs at 12.5G bps.

#### Required Equipments

To enable an external loopback of transceiver channels, the following fixtures are required:

- TR5 board and XTS-FMC card.

- 8 SMA cables for loopback the TX and RX port on the XTS-FMC card.

#### Demonstration Setups

The transceiver test code is available in the folder System CD\Demonstrations\TR5\demo\_batch. Here are the procedures to perform transceiver channel test:

1. Use the SMA cables to connect the TX ports and the RX ports on the XTS-FMC card to implement the loopback function (See **Figure 4-1**, **Figure 4-2**). There are four channels in total, note the difference between positive and negative ports.

Figure 4-1 SMA loopback setup

XTS-FMC User Manual www.terasic.com

2. Connect the XTS-FMC card to the FMC D or FMC A connector of the TR5 board. Make sure the FMC connector between the two boards is locked with copper posts and screws (See section 1.3).

Figure 4-2 The Connections between the XTS-FMC card and TR5 board

- 3. Connect your TR5 board to your PC with a mini USB cable.

- 4. Connect Power to the TR5 board.

- 5. Copy the demo\_batch folder (from System CD) to your local disk.

- 6. Power on the TR5 board.

- 7. Execute 'test.bat" in the demo\_batch folder under your local disk.

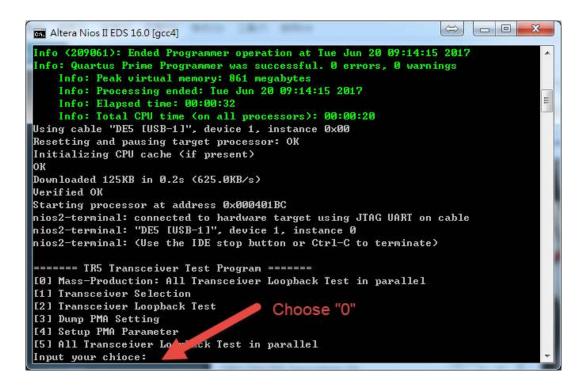

- 8. The batch file will download .sof and .elf files, and start the test. The Nios-Terminal as shown in **Figure 4-3** will appear and choose "0" to test all the transceiver loopback test.

#### **Figure 4-3 Choose the Test function**

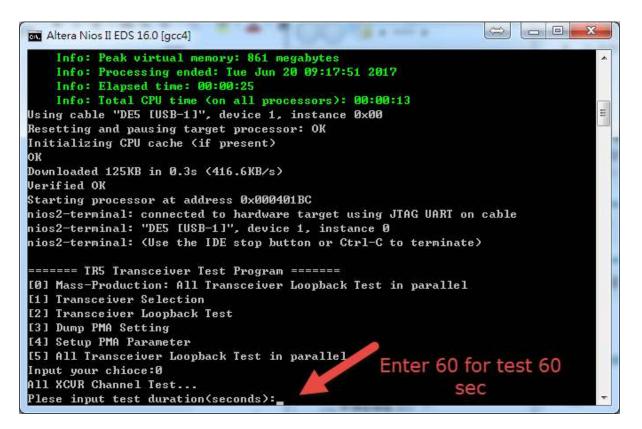

9. Then enter how many seconds you want to test the transmission (See Figure 4-4). For example, enter "60" for test 60 second.

Figure 4-4 Choose test duration

10. The test result will be displayed after the test time has elapsed (See Figure 4-5). It should be noted that this test code will test all the transceivers of the FMC A and FMC D connectors on the TR5 board (8 pairs of transceivers for each connector). Since XTS-FMC card can only test 4 pairs of transceivers. So the test result will only show the first four transceivers (0~3) of FMC A or FMC D are PASS or NG. Other transceiver test results can be ignored.

| FMCB_XCVR_0=NG                       |

|--------------------------------------|

| FMCD_XCUR_Ø=PASS                     |

| FMCD_XCUR_1=PASS<br>FMCD_XCUR_2=PASS |

| FMCD_XCVR_2=FH88<br>FMCD_XCVR_3=PASS |

| FMCD_XCVR_4=NG                       |

| FMCD_XCVR_5=NG                       |

| FMCD_XCVR_6=NG                       |

| FMCD_XCVR_7=NG                       |

| FMCD_XCVR_8=NG                       |

| FMCD XCUR 9=NG                       |

Figure 4-5 The test result of the transceiver loopback

### **4.2 XTS-FMC Loopback on the Han Pilot Platform**

This section describes the use of the XTS-FMC card to test the FPGA's transceiver loopback on the HAN pilot platform. The basic operation is roughly the same as section 4.1, except that the FPGA board is replaced. The following is a detailed test procedure.

#### Required Equipments

To enable an external loopback of transceiver channels, the following fixtures are required:

- HAN Pilot Platform and XTS-FMC card.

- 8 SMA cables for loopback the TX and RX ports on the XTS-FMC card.

#### Demonstration Setups

The transceiver test code is available in the folder System CD\Demonstrations\HAN\XCVT loopback. Here are the procedures to perform transceiver channel test:

- 1. Use the SMA cables to connect the TX ports and the RX ports on the XTS-FMC card to implement the loopback function (See Figure 4-6).

- 2. Connect the XTS-FMC card to the FMC connector of the HAN Pilot Platform board. Make sure the FMC connector between the two boards is locked with copper posts and screws (See section **1.3**).

Figure 4-6 The Connections between the XTS-FMC and HAN Pilot Platform board

- 3. Connect your HAN board to your PC with a mini USB cable.

- 4. Connect Power to the HAN Pilot Platform board.

- 5. Copy the demo\_batch folder (from System CD) to your local disk.

- 6. Power on the HAN Pilot Platform board.

- 7. Execute 'test.bat" in the demo\_batch folder under your local disk.

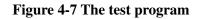

- 8. The batch file will download .sof and .elf files, and start the test in the Nios-Terminal as shown in **Figure 4-7**. When the menu option appears, you can choose 0 for starting test. The program will automatically start the test and report the test results every five seconds until the user closes the window (see **Figure 4-8**).

21

Altera Nios II EDS 18.0 [acc4] × \_ Info: Quartus Prime Programmer was successful. 0 errors, 0 warnings Info: Peak virtual memory: 5218 megabytes Info: Processing ended: Thu Apr 25 16:50:22 2019 Info: Elapsed time: 00:00:25 Info: Total CPU time (on all processors): 00:00:12 Using cable "DE10-Advanced [USB-1]", device 1, instance 0x00 Peactting and pausing target processor: 0K Resetting and pausing target processor: OK Initializing CPU cache (if present) OK Downloaded 126KB in 0.1s Verified OK Starting processor at address 0x00040244 nios2-terminal: "DE10-Advanced [USB-1]", device 1, instance 0 nios2-terminal: "Use the IDE stop button or Ctrl-C to terminate) ======= Transceiver Test Program ======= [0]Test with default settings. Press any key on the board to abort testing. 1]Test with default settings in given time duration 2]Test with current settings. Press any key on the board to abort testing. [3]Dump current settings [4]Apply default settings 99: Quit Please input your selection:

| Altera Nios II EDS 18.0 [gcc4]                 | - 🗆 | Х      |

|------------------------------------------------|-----|--------|

| XTS_FMC_x4-3: PASS, XferCnt:14016478976        |     | ^      |

| ===== Time Elapsed: 1 Minutes 15 Seconds ===== |     |        |

| XTS FMC x4-0: PASS, XferCnt:15026130560        |     |        |

| XTS_FMC_x4-1: PASS, XferCnt:15026306688        |     |        |

| XTS_FMC_x4-2: PASS, XferCnt:15026441984        |     |        |

| XTS_FMC_x4-3: PASS, XferCnt:14993065600        |     |        |

| ===== Time Elapsed: 1 Minutes 20 Seconds ===== |     |        |

| XTS FMC x4-0: PASS, XferCnt:16002717184        |     |        |

| XTS_FMC_x4-1: PASS, XferCnt:16002894336        |     |        |

| XTS_FMC_x4-2: PASS, XferCnt:16003027328        |     |        |

| XTS_FMC_x4-3: PASS, XferCnt:15969652096        |     |        |

| ===== Time Elapsed: 1 Minutes 25 Seconds ===== |     |        |

| XTS_FMC_x4-0: PASS, XferCnt:16979205888        |     |        |

| XTS_FMC_x4-1: PASS, XferCnt:16979384448        |     |        |

| XTS_FMC_x4-2: PASS, XferCnt:16979518592        |     |        |

| XTS_FMC_x4-3: PASS, XferCnt:16946142080        |     |        |

| ===== Time Elapsed: 1 Minutes 30 Seconds ===== |     |        |

| XTS_FMC_x4-0: PASS, XferCnt:17955792384        |     |        |

| XTS_FMC_x4-1: PASS, XferCnt:17955970816        |     |        |

| XTS_FMC_x4-2: PASS, XferCnt:17956105088        |     |        |

| XTS_FMC_x4-3: PASS, XferCnt:17922728448        |     |        |

| ===== Time Elapsed: 1 Minutes 35 Seconds ===== |     |        |

| XTS_FMC_x4-0: PASS, XferCnt:18932379008        |     |        |

| XTS_FMC_x4-1: PASS, XferCnt:18932557696        |     |        |

| XTS_FMC_x4-2: PASS, XferCnt:18932691712        |     |        |

| XTS_FMC_x4-3: PASS, XferCnt:18899315328        |     |        |

|                                                |     | $\sim$ |

Figure 4-8 Test result

### **4.3 XTS-FMC SuperLite Loopback on the Han Pilot**

#### Platform

This section also describes the use of the XTS-FMC card to test the FPGA's RX/TX transceiver loopback on the HAN pilot platform, this XTS-FMC SuperLite Loopback demonstration is created based on Intel High Speed Transceiver Demo Designs, we ported it to HAN Pilot Platform combined with XTS-FMC card, the data rate of the transceiver channel on the FMC connector runs at 12.5Gbps.

User can refer to A10GX\_SIBoard\_SuperliteII\_V3\_4\_lanes\_10Gbps\_QSFP+.pdf document in the folder:

*System CD\Demonstrations\HAN\A10GX\_SIBoard\_SuperliteII\_V3\_4\_lanes\_10Gbps\_QSFP+.pdf f or detail description.*

#### **Demonstration Setups**

The transceiver test code is available in the folder System CD\Demonstrations\HAN\ SuperLite Loopback\demo\_batch. Here are the procedures to perform transceiver channel test:

- 1. Use the SMA cables to connect the TX ports and the RX ports on the XTS-FMC card to implement the loopback function (See Figure 4-9).

- Connect the XTS-FMC card to the FMC connector of the HAN Pilot Platform board. Make sure the FMC connector between the two boards is locked with copper posts and screws (See section 1.).

Figure 4-9 The Connections between the XTS-FMC and HAN Pilot Platform board

- 3. Connect your HAN board to your PC with a mini USB cable.

- 4. Connect Power to the HAN Pilot Platform board.

- 5. Copy the demo\_batch folder (from System CD) to your local disk.

- 6. Power on the HAN Pilot Platform board.

- 7. Execute 'test.bat" in the demo\_batch folder under your local disk.

- 8. The batch file will download .sof and .elf files, and start the test in the Nios-Terminal as shown in Figure 4-10. When the menu option appears, use can choose C to start the test, if the Nios-Terminal shows '0' all the time, it means that the loopback test is passed without error.

| Altera Nios II ED | 16.1 [gcc4]                           |                     |

|-------------------|---------------------------------------|---------------------|

| Select Action     |                                       |                     |

|                   |                                       |                     |

| 1. Set all char   | nels back to default and toggle Reset | t                   |

| 2. Force Re-Al:   | gnment on Rx Path                     |                     |

| 3. Select Chanr   |                                       |                     |

| 4. Show/Control   | Transceiver PMA Settings on Links     |                     |

| 5. Insert Biter   | rors on Link (4 at a time)            |                     |

| 6. Reset Error(   | ounter                                |                     |

| 7. Show Status    |                                       |                     |

| 8. Control Ser:   | al loopback                           |                     |

| C. Refresh BER    | every 1 seconds                       |                     |

| D. Input new Bl   | R Time Interval                       |                     |

|                   | iver PMA Settings on all channels     |                     |

| G. Input new Ey   | eqInterval time                       |                     |

| S. Store all cl   | annel information in memory of Select | ted Channel         |

| T. Store and co   | mpare with values stored in process § | S                   |

| X. Toggle XOFF    | to partner to stop/start sending traf | ffic at remote side |

| Z. Dump channe:   | content of selected channel           |                     |

| O. Perform ODI    | on selected channel                   |                     |

| 0. Stop Test      |                                       |                     |

|                   |                                       |                     |

| Enter Choice      | •c                                    |                     |

| Show BER + Erro   | rCount every 1 seconds                |                     |

| Press any key 🖞   | Enter to stop the loop                |                     |

|                   | ================================      |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

| Link : BER        | : 0                                   |                     |

|                   |                                       |                     |

Figure 4-10 Start the test in the Nios-Terminal

9. The signal XCVR quality depends on the device (such as scope, SMA cables) which is connected to the XCVR REFCLK Input SMA connector, user needs to modify the PMA parameters. Choose the action 3 (Select Channel to Control) in the Nios-Terminal to change channel, then choose action 4 (Show/Control Transceiver PMA Settings on Links) to modify the PMA parameters. Based on our actual experiment, we provided a group of PMA parameters as shown in Table 4-1, user can modify the PMA parameters by referring the values in.

| VOD     | 29      |

|---------|---------|

| PostTap | -9      |

| PreTap  | -1      |

| other   | Default |

Table 4-1 PMA parameters based on our actual experiment

www.terasic.com

# Appendix

## **Revision History**

| Version | Change Log                     |

|---------|--------------------------------|

| V1.0    | Initial Version (Preliminary)  |

| V1.1    | Add section 2.3                |

| V1.2    | Add section 4.3                |

| V2.0    | Modify by XTS-FMC Rev B board  |

| V3.0    | Add TMD header for rev.C board |

Copyright © Terasic Inc. All rights reserved.

27