#### **FEATURES**

- Integrated 6.8V/0.8A Buck Regulator provides bias to Control and Driver IC(s)

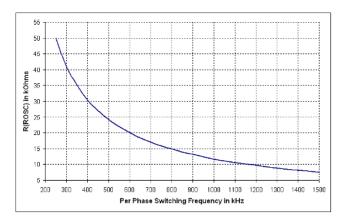

- Adjustable switching frequency from 250 KHz up to 1.5MHz per phase based on the synchronization SCLK input

- Sink and source tracking capability

- · Margining via SVID for both rails

- Pre-bias compatible

- Soft Stop capability

- 0.5% overall system set point accuracy

- Voltage Mode Modulation for excellent transient performance

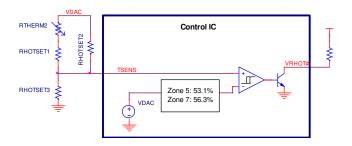

- Single NTC thermistor for current reporting, OC Threshold, and Load Line thermal compensation

- Complete protection including over-current, over-voltage, over-temperature, open remote sense and open control loop

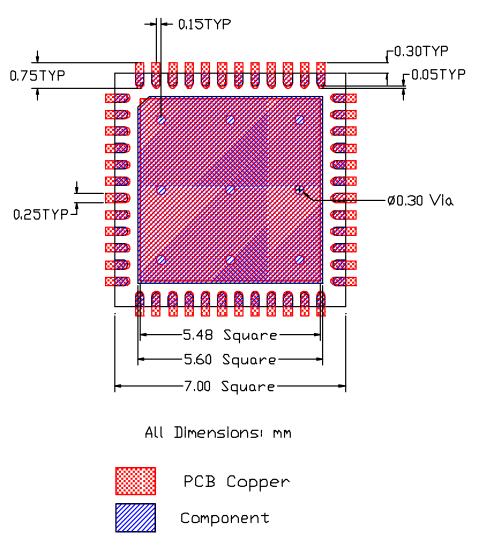

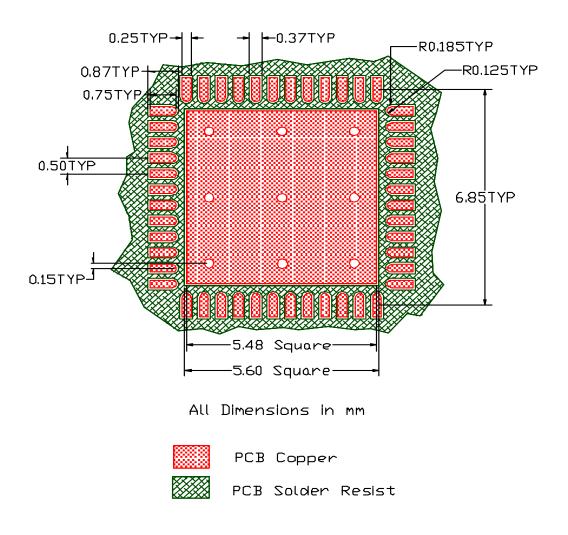

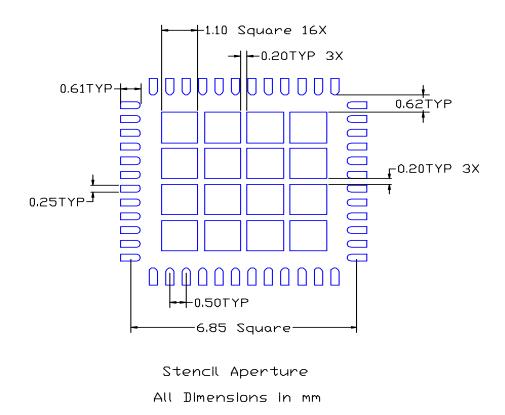

- Thermally enhanced 48L 7mm x 7mm MLPQ package

- · RoHS compliant

## **DESCRIPTION**

The IR3531 control IC provides all the necessary control, communication and protection to support compact dual output power solutions up to 210W. The IR3531 can be combined with either discrete IR3535 driver ICs and Direct Fets<sup>™</sup> or our IR35XX family of footprint compatible and scalable PowIRstages<sup>™</sup> which integrate the MOSFETs and driver into the same package.

The IR3531 provides overall system control and current sharing while the Driver IC or power stages senses perphase current locally and communicates it to the Control IC. The IR3531 has tri-state PWM outputs to allow diode emulation during light load events.

The IR3531 provides a high performance transient solution through classic voltage mode control and our non-linear transient solutions, Turbo<sup>™</sup> and Body Braking<sup>™</sup>. Turbo<sup>™</sup> automatically turns on all phases to minimize load turn-on transients while Body Braking<sup>™</sup> automatically turns off the low-side MOSFET to help dissipate stored inductor energy at load turn-off.

#### **BASIC APPLICATION CIRCUIT**

# PHOFILIA IRAS50 Pow FStage Sync In TRACK PHOFILIA IRAS51 IRAS51 IRAS51 IRAS531 IRAS530 Pow FStage IRAS530 I

Figure 1: IR3531 Basic Application Circuit, showing a 4+1 Configuration

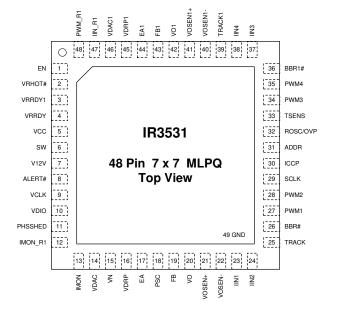

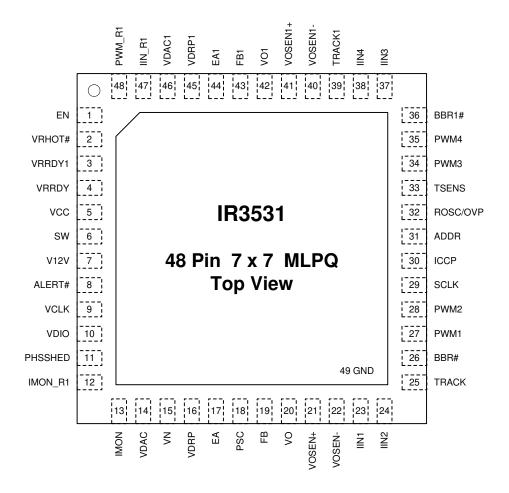

## **PIN DIAGRAM**

Figure 2: IR3531 Package Top View

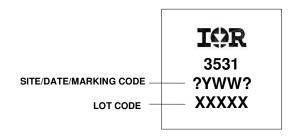

## **ORDERING INFORMATION**

| Package T                     | ape & Reel Qty | Part Number                |

|-------------------------------|----------------|----------------------------|

| 48 Lead MLPQ<br>(7x7 mm body) | 100            | IR3531-MPBF                |

| 48 Lead MLPQ<br>(7x7 mm body) | 3000           | IR3531-MTRPBF <sup>1</sup> |

Note <sup>1</sup>: Samples only.

Figure 3: Package Top View, Enlarged

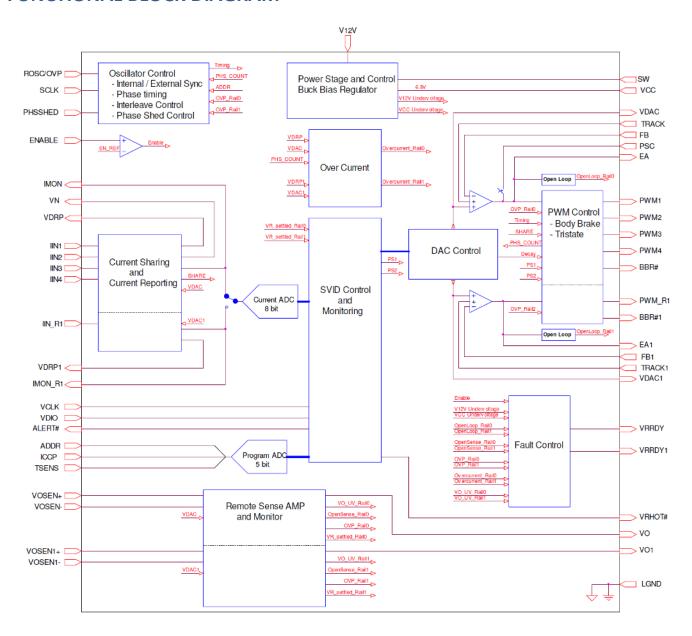

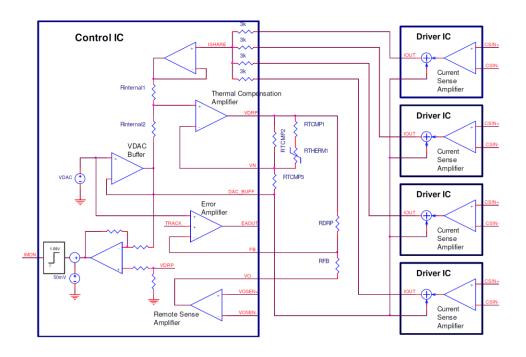

## **FUNCTIONAL BLOCK DIAGRAM**

Figure 4: IR3531 Block Diagram

## TYPICAL APPLICATION DIAGRAM

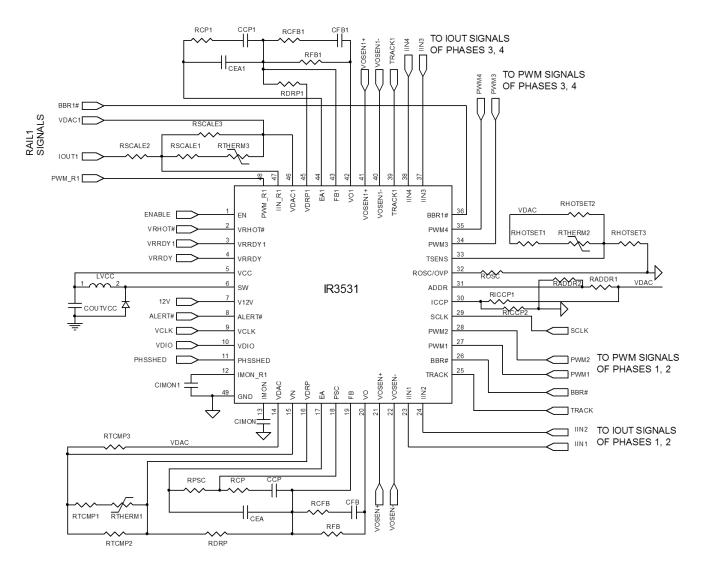

Figure 5: IR3531 Typical Application Diagram

## **PIN DESCRIPTIONS**

| PIN#              | PIN NAME | PIN DESCRIPTION                                                                                                                                                                                                            |

|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | EN       | Enable input. Grounding this pin shuts down the voltage regulators. Do not float this pin as the logic state will be undefined.                                                                                            |

| 2                 | VRHOT#   | Open collector output of the VRHOT# comparator which drives low if Rail0 temperature exceeds the programmed threshold. Connect external pull-up to bias.                                                                   |

| 3                 | VDRRY1   | Open collector output that drives low during startup and under any external fault condition for Rail1 regulator. Connect external pull-up to bias.                                                                         |

| 4                 | VDRRY    | Open collector output that drives low during startup and under any external fault condition for Rail0 regulator. Connect external pull-up to bias.                                                                         |

| 5                 | vcc      | Bias buck regulator output, feedback pin, and bias input for internal circuitry.                                                                                                                                           |

| 6                 | SW       | Switching node for bias buck regulator.                                                                                                                                                                                    |

| 7                 | V12V     | Power Supply input supply rail.                                                                                                                                                                                            |

| 8                 | ALERT#   | Output pin for SVID Alert# interrupt. Open collector output that drives low to notify the master.                                                                                                                          |

| 9                 | VCLK     | SVID Clock Input. Clock is a high impedance input pin. It is driven by the open collector output of a microprocessor and requires a pull-up resistor.                                                                      |

| 10                | VDIO     | SVID Data Input/Output. High impedance input when address, command or data bits are shifted in, open drain output when acknowledging or sending data back to the microprocessor. Pin requires a pull up resistor.          |

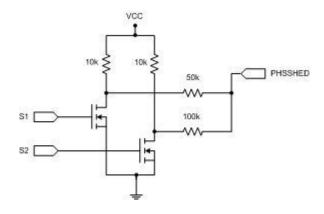

| 11                | PHSSHED  | Analog signal that represents the number of phases to be disabled. 0% to 25% VCC, no phases disabled. 25% to 50% VCC, disable 1 phase. 50% to 75% VCC, disable 2 phases. 75% to 100% VCC, disable 3 phases (if available). |

| 12                | IMON_R1  | Voltage at this pin is proportional to Rail1 load current. It is also the input to the ADC for output current register.                                                                                                    |

| 13                | IMON     | Voltage at this pin is proportional to RailO load current. It is also the input to the ADC for output current register.                                                                                                    |

| 14                | VDAC     | Voltage Regulator Rail 0 reference voltage programmed by SVID. VDAC is also used as the A/D reference during power up for pins ADDR/PSN, TSENS and ICCP.                                                                   |

| 15                | VN       | Node for DCR thermal compensation network.                                                                                                                                                                                 |

| 16                | VDRP     | Buffered, scaled and thermally compensated current signal for RailO. Connect an external resistor to FB to program converter output impedance.                                                                             |

| 17                | EA       | Output of the error amplifier for RailO.                                                                                                                                                                                   |

| 18                | PSC      | Node for Power Savings mode compensation input.                                                                                                                                                                            |

| 19                | FB       | Inverting input to the Error Amplifier for Rail0.                                                                                                                                                                          |

| 20                | VO       | Remote sense amplifier output for RailO.                                                                                                                                                                                   |

| 21                | VOSEN+   | Rail0 remote sense amplifier input. Connect to output at the load.                                                                                                                                                         |

| 22                | VOSEN-   | Rail0 remote sense amplifier input. Connect to ground at the load.                                                                                                                                                         |

| 23, 24, 37, 38    | IIN1-4   | Current signals from the driver IC-s of Rail0.                                                                                                                                                                             |

| 25                | TRACK    | External tracking reference for Rail0.                                                                                                                                                                                     |

| 26                | BBR#     | Body-braking <sup>™</sup> bus for Rail0 driver ICs to disable synchronous switches.                                                                                                                                        |

| 27, 28,<br>34, 35 | PWM1-4   | PWM outputs for RailO. Each output is connected to the input of the driver IC. Connecting the PWMx output to LGND disables the phase, allowing the IR3531 to operate as a 1, 2, 3, or 4 phase controller.                  |

| 29                | SCLK     | Synchronization clock input. Program ROSC using ROSC vs. Frequency to match the SCLK frequency.                                                                                                                            |

| PIN# | PIN NAME | PIN DESCRIPTION                                                                                                                                                                            |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30   | ICCP     | Program maximum load current for both Rail0 and Rail1.                                                                                                                                     |

| 31   | ADDR     | Programs SVID address for Rail0 and Rail1, discrete or coupled inductor operation for Rail0, enable/disable turbo function for Rail0.                                                      |

| 32   | ROSC/OVP | Connect a resistor to LGND to program oscillator frequency. Oscillator frequency equals switching frequency per phase. ROSC/OVP pin is pulled up to VCC when an over voltage event occurs. |

| 33   | TSENS    | Pin for thermal network that senses the temperature of RailO and Rail1.                                                                                                                    |

| 36   | BBR1#    | Body-braking <sup>™</sup> bus for Rail1 driver ICs to disable synchronous switches.                                                                                                        |

| 39   | TRACK1   | External tracking reference for Rail1.                                                                                                                                                     |

| 40   | VOSEN1-  | Rail1 remote sense amplifier input. Connect to ground at the load.                                                                                                                         |

| 41   | VOSEN1+  | Rail1 remote sense amplifier input. Connect to output at the load.                                                                                                                         |

| 42   | VO1      | Remote sense amplifier output for Rail1.                                                                                                                                                   |

| 43   | FB1      | Inverting input to the Error Amplifier for Rail1.                                                                                                                                          |

| 44   | EA1      | Output of the error amplifier for Rail1.                                                                                                                                                   |

| 45   | VDRP1    | Buffered, scaled and thermally compensated current signal for Rail1. Connect an external resistor to FB1 to program converter output impedance.                                            |

| 46   | VDAC1    | Buffered Rail1 reference voltage. Voltage can be margined via SVID.                                                                                                                        |

| 47   | IIN_R1   | Current signal from Rail1 driver IC.                                                                                                                                                       |

| 48   | PWM_R1   | PWM output for Rail1.                                                                                                                                                                      |

| 49   | GND      | Local Ground for internal circuitry and IC substrate connection.                                                                                                                           |

## **ABSOLUTE MAXIMUM RATINGS**

| Storage Temperature Range      | -65°C To 150°C              |

|--------------------------------|-----------------------------|

| Operating Junction Temperature | 0°C To 150°C                |

| ESD Rating                     | HBM Class 1C JEDEC Standard |

| MSL Rating                     | 2                           |

| Reflow Temperature             | 260°C                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications are not implied.

| PIN Number | PIN NAME | V <sub>MAX</sub> | V <sub>MIN</sub> | I <sub>SOURCE</sub> | I <sub>sink</sub> |

|------------|----------|------------------|------------------|---------------------|-------------------|

| 1          | EN       | 3.5V             | -0.3V            | 25mA                | 1mA               |

| 2          | VRHOT#   | VCC              | -0.3V            | 1mA                 | 50mA              |

| 3          | VDRRY1   | VCC              | -0.3V            | 1mA                 | 20mA              |

| 4          | VDRRY    | VCC              | -0.3V            | 1mA                 | 20mA              |

| 5          | VCC      | 8V               | -0.3V            | 1mA                 | 20mA              |

| 6          | SW       | 16V              | -1.0V            | 3A                  | 1mA               |

| 7          | V12V     | 16V              | -0.5V            | 1mA                 | 1.5A              |

| 8          | ALERT#   | 3.5V             | -0.3V            | 1mA                 | 50mA              |

| 9          | VCLK     | 3.5V             | -0.3V            | 1mA                 | 1mA               |

| 10         | VDIO     | 3.5V             | -0.3V            | 1mA                 | 50mA              |

| 11         | PHSSHED  | VCC              | -0.3V            | 1mA                 | 1mA               |

| 12         | IMON_R1  | 3.5V             | -0.3V            | 25mA                | 1mA               |

| 13         | IMON     | 3.5V             | -0.3V            | 25mA                | 1mA               |

| 14         | VDAC     | 3.5V             | -0.3V            | 5mA                 | 35mA              |

| 15         | VN       | vcc              | -0.3V            | 1mA                 | 1mA               |

| 16         | VDRP     | vcc              | -0.3V            | 35mA                | 1mA               |

| 17         | EA       | vcc              | -0.3V            | 35mA                | 5mA               |

| 18         | PSC      | VCC              | -0.3V            | 1mA                 | 1mA               |

| 19         | FB       | vcc              | -0.3V            | 1mA                 | 1mA               |

| 20         | VO       | vcc              | -0.3V            | 35mA                | 5mA               |

| 21         | VOSEN+   | vcc              | -0.5V            | 5mA                 | 1mA               |

| 22         | VOSEN-   | 1.0V             | -0.5V            | 5mA                 | 1mA               |

| 23         | IIN1     | VCC              | -0.3V            | 1mA                 | 1mA               |

| 24         | IIN2     | VCC              | -0.3V            | 1mA                 | 1mA               |

| 25         | TRACK    | VCC              | -0.3V            | 1mA                 | 1mA               |

| 26         | BBR#     | VCC              | -0.3V            | 1mA                 | 5mA               |

| 27         | PWM1     | VCC              | -0.3V            | 1mA                 | 5mA               |

| PIN Number | PIN NAME | V <sub>MAX</sub> | V <sub>MIN</sub> | I <sub>SOURCE</sub> | I <sub>SINK</sub> |

|------------|----------|------------------|------------------|---------------------|-------------------|

| 28         | PWM2     | VCC              | -0.3V            | 1mA                 | 5mA               |

| 29         | SCLK     | 3.5V             | -0.3V            | 1mA                 | 5mA               |

| 30         | ICCP     | 3.5V             | -0.3V            | 1mA                 | 1mA               |

| 31         | ADDR     | 3.5V             | -0.3V            | 1mA                 | 1mA               |

| 32         | ROSC     | VCC              | -0.3V            | 1mA                 | 1mA               |

| 33         | TSEN     | 3.5V             | -0.3V            | 1mA                 | 1mA               |

| 34         | PWM3     | VCC              | -0.3V            | 1mA                 | 5mA               |

| 35         | PWM4     | VCC              | -0.3V            | 1mA                 | 5mA               |

| 36         | BBR1#    | VCC              | -0.3V            | 1mA                 | 5mA               |

| 37         | IIN3     | VCC              | -0.3V            | 1mA                 | 1mA               |

| 38         | IIN4     | VCC              | -0.3V            | 1mA                 | 1mA               |

| 39         | TRACK1   | VCC              | -0.3V            | 1mA                 | 1mA               |

| 40         | VOSEN1-  | 1.0V             | -0.5V            | 5mA                 | 1mA               |

| 41         | VOSEN1+  | VCC              | -0.5V            | 5mA                 | 1mA               |

| 42         | VO1      | VCC              | -0.5V            | 35mA                | 5mA               |

| 43         | FB1      | VCC              | -0.3V            | 1mA                 | 1mA               |

| 44         | EA1      | VCC              | -0.3V            | 35mA                | 5mA               |

| 45         | VDRP1    | VCC              | -0.3V            | 35mA                | 1mA               |

| 46         | VDAC1    | 3.5V             | -0.3V            | 1mA                 | 35mA              |

| 47         | IIN_R1   | VCC              | -0.3V            | 1mA                 | 1mA               |

| 48         | PWM_R1   | VCC              | -0.3V            | 1mA                 | 1mA               |

| 49         | GND      | N/A              | N/A              | 20mA                | 1mA               |

## **ELECTRICAL SPECIFICATIONS**

## RECOMMENDED OPERATING CONDITIONS FOR RELIABLE OPERATION WITH MARGIN

The electrical characteristics table lists the spread of values guaranteed within the recommended operating conditions. Typical values represent the median values, which are related to 25°C. Unless otherwise specified, these specifications apply over:  $-0.3V \le VOSEN - \le 0.3V$ ,  $7.75K\Omega \le ROSC \le 50.0 K\Omega$

| Recommended V12V Range                     | 10.8V | 12  | 13.2V | V  |

|--------------------------------------------|-------|-----|-------|----|

| Recommended VCC Range                      | 6.6   | 6.8 | 7.0   | V  |

| VOSEN- and VOSEN1- to LGND offset          | -0.3  | 0   | 0.3   | V  |

| ROSC Resistor Programming Range            | 7.75  |     | 50    | ΚΩ |

| Recommended Operating Junction Temperature | 0     | Tj  | 100   | ōС |

## **ELECTRICAL CHARACTERISTICS**

| PARAMETER                        | SYMBOL     | CONDITIONS                                                                                  | MIN   | ТҮР   | MAX   | UNIT  |

|----------------------------------|------------|---------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| VDAC Reference                   |            |                                                                                             |       |       |       |       |

| System Set-Point Accuracy        | SETACC     | VID ≥ 1V                                                                                    | -0.5  | -     | 0.5   | %     |

|                                  |            | 0.8 ≤ VID < 1V                                                                              | -5    | -     | +5    | mV    |

|                                  |            | 0.25V ≤ VID < 0.8V                                                                          | -8    | -     | +8    | mV    |

| Slew Rate – Fast Mode            | VIDFAST    |                                                                                             | 15    | 20    | 25    | mV/μs |

| Slew Rate – Slow Mode            | VIDSLOW    |                                                                                             | 3.75  | 5     | 6.25  | mV/μs |

| Default VBOOT Rail 0             | VBOOT0     | Note 3                                                                                      | -     | 1.5   | -     | V     |

| Default VBOOT Rail 1             | VBOOT1     | Note 3                                                                                      | -     | 1.5   | -     | V     |

| Oscillator (Note 4)              |            |                                                                                             |       |       |       |       |

| ROSC Voltage                     | VROSC      | ROSC = 24.5 KΩ                                                                              | 0.570 | 0.595 | 0.620 | V     |

| VDAC Buffer Amplifier            |            |                                                                                             |       |       |       |       |

| Input Outset Voltage             | DACOFF     | V(VDAC, VDAC1) — VID code +<br>VID offset, 0.25V ≤<br>V(VDAC, VDAC1) ≤ 1.52V,<br>< 1mA load | -15   | 0     | 15    | mV    |

| Source Current                   | DACSRC     | 0.25V ≤ V(VDAC1) ≤ 1.52V                                                                    | 0.3   | 0.44  | 0.6   | _     |

|                                  |            | 0.25V ≤ V(VDAC) ≤ 1.52V                                                                     | 0.9   | 1.65  | 2.4   | mA    |

| Sink Current                     | DACSNK     | 0.5V ≤ V(VDAC1) ≤ 1.52V                                                                     | 2     | 13    | 20    |       |

|                                  |            | V(VDAC1) = 0.25V                                                                            | 0.5   | 1.5   | 2     |       |

|                                  |            | 0.5V ≤ V(VDAC) ≤ 1.52V                                                                      | 3     | 15    | 30    | mA    |

|                                  |            | V(VDAC) = 0.25V                                                                             | 0.5   | 1.5   | 3     |       |

| Unity Gain Bandwidth             |            |                                                                                             | -     | 3.5   | -     | MHz   |

| Slew Rate                        |            |                                                                                             | -     | 1.5   | -     | V/µs  |

| Thermal Compensation Amplifier ( | VDRP)      |                                                                                             | •     |       |       |       |

| Output Offset Voltage            | VDRPOUTOFF | 0V ≤ V(IIN) − V(VDAC) ≤ 1.52V,<br>0.25V ≤ V(VDAC) ≤ 1.52V,                                  | -14   | 0     | 14    | mV    |

| PARAMETER                                       | SYMBOL     | CONDITIONS                                                                 | MIN   | ТҮР      | MAX   | UNIT         |

|-------------------------------------------------|------------|----------------------------------------------------------------------------|-------|----------|-------|--------------|

|                                                 |            | Req/R2 = 2                                                                 |       |          |       |              |

| Source Current                                  | VDRPSRC    | 0.25V ≤ V(VDAC) ≤ 1.52V                                                    | 3     | 8        | 15    | mA           |

| Sink Current                                    | VDRPSNK    | 0.5V ≤ V(VDRP) ≤ 1.52V                                                     | 0.2   | 0.4      | 0.7   |              |

|                                                 |            | V(VDRP) = 0.25V                                                            | 0.175 | 0.25     | 0.4   | mA           |

| Unity Gain Bandwidth                            |            | Req/R2 = 2, Note 1                                                         | 2     | 4.5      | 7     | MHz          |

| Slew Rate                                       |            |                                                                            | -     | 5.5      | -     | V/µs         |

| VN Bias Current                                 |            | V(VN) = 2 V                                                                | -2    | 0        | 2     | μА           |

| Power Savings Mode Operation                    |            | .()                                                                        |       | <u> </u> | _     | μι           |

| PS2/PS3 Turn-on Threshold                       | PS2THRSH   | VID = 250 mV                                                               | 250   | 350      | 385   | mV           |

| . <b>52</b> , 1 <b>5</b> 5                      |            | VID = 1.52 V                                                               | 2     | 2.15     | 2.26  | V            |

| PS2/PS3 Pulse Width Rail0                       | PS2COT0    | VID = 250 mV, SF = 500 kHz                                                 | 60    | 151      | 200   | v            |

| . <b>52</b> , 1 <b>5</b> 5 1 also 11 al. 11 al. | . 5255.5   | VID = 1.52 V, SF = 500 kHz                                                 | 220   | 409      | 480   | ns           |

| PS2/PS3 Pulse Width Rail1                       | PS2COTMIN1 | VID = 250 mV, SF = 500 kHz                                                 | 50    | 100      | 200   |              |

|                                                 | PS2COTMAX1 | VID = 1.52 V, SF = 500 kHz                                                 | 220   | 358      | 480   | ns           |

| PS Mode Enter Delay                             | PS1DELAY   | PS0 to PS1 only                                                            | -     | 8        | -     | PWM<br>Cycle |

| Enable Input                                    |            | <b>'</b>                                                                   |       |          |       | ,            |

| Rising Threshold                                | ENRISE     |                                                                            | 625   | 650      | 675   | mV           |

| Falling Threshold                               | ENFALL     |                                                                            | 575   | 600      | 625   | mV           |

| Hysteresis                                      | ENHYST     |                                                                            | 25    | 50       | 75    | mV           |

| Bias Current                                    | ENBIAS     | 0V ≤ V(ENABLE) ≤ 3.3V                                                      | -5    | 0        | 5     | μΑ           |

| Blanking Time                                   |            | Noise Pulse < 100ns will not register an ENABLE state change. Note 1       | 75    | 250      | 400   | ns           |

| IMONx Current Report Amplifier                  |            |                                                                            |       |          |       |              |

| Output Offset Voltage                           | IMONOFF    | VDRP-VDAC = 0, 225, 450,<br>900mV                                          | 15    | 50       | 90    | mV           |

| Unity Gain Bandwidth                            |            | Note 1                                                                     | -     | 1        | -     | MHz          |

| Input Filter Time Constant                      |            |                                                                            | -     | 1        | -     | μs           |

| Max Output Voltage                              | IMONMAX    |                                                                            | 1.00  | 1.09     | 1.145 | V            |

| Current Report A/D Accuracy                     | IMONACC    | VDRP-VDAC = 900mV                                                          | -2    | 0        | 2     | %            |

| Rail1 VDRP Amplifier                            |            |                                                                            |       |          |       |              |

| Output Outset Voltage                           | VDRP1OFF   | 0V≤ V(IIN_R1) - V(VDAC1) ≤ 0.2V<br>0.25V ≤ V(IIN_R1) - V(VDAC1) ≤<br>1.52V | -75   | 0        | 75    | mV           |

| Source Current                                  | VDRP1SRC   | 0.25V ≤ V(VDAC1) ≤ 1.52V                                                   | 3     | 8        | 15    | mA           |

| Sink Current                                    | VDRP1SNK   | 0.5V≤ V(VDRP1) ≤ 1.52V                                                     | 0.2   | 0.4      | 0.6   | A            |

|                                                 |            | V(VDRP1) = 0.25V                                                           | 0.175 | 0.25     | 0.375 | mA           |

| Closed Loop Gain                                |            | Note 1                                                                     | -     | 9        | -     | V/V          |

| Unity Gain Bandwidth                            |            | Note 1                                                                     | 0.8   | 1.5      | 3     | MHz          |

| Slew Rate                                       |            | Note 1                                                                     | -     | 5.5      | -     | V/µs         |

| Error Amplifier                                 |            | I                                                                          |       |          |       | ,,           |

| PARAMETER                                | SYMBOL     | CONDITIONS                                                                                                          | MIN   | ТҮР  | MAX  | UNIT       |

|------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------|-------|------|------|------------|

| Input Offset Voltage                     |            | Note 2 (test mode only)                                                                                             | -     | 0    | -    | mV         |

| FB Bias Current                          |            |                                                                                                                     | -1    | 0    | 1    | μΑ         |

| DC Gain                                  |            | Note 1                                                                                                              | 100   | 110  | 120  | dB         |

| Unity Gain Bandwidth                     |            | Note 1                                                                                                              | 20    | 30   | 40   | MHz        |

| Slew Rate                                |            | Note 1                                                                                                              | 7     | 12   | 20   | V/µs       |

| Sink Current                             | EASRC      |                                                                                                                     | 0.40  | 0.85 | 1.35 | mA         |

| Source Current                           | EASNK      |                                                                                                                     | 5     | 8    | 12   | mA         |

| Maximum Voltage                          | EAMAX      | Measure V(VCC) – V(EA), V(EA1)                                                                                      | 500   | 925  | 1100 | mV         |

| Minimum Voltage                          | EAMIN      |                                                                                                                     | -     | 120  | 250  | mV         |

| Open Voltage Loop Detection<br>Threshold | EAOPENTHR  | Measure V(VCCx) - V(EA), V(EA1),<br>Relative to Error Amplifier<br>maximum voltage                                  | 100   | 300  | 1100 | mV         |

| Open Loop Detection Delay                | EAOPENDEL  | V(EA), V(EA1) = V(VCC) to<br>VRRDY = low                                                                            | -     | 8    | -    | PWM        |

| PS2 Clamp Voltage                        | EAPS2CLMP  | With respect to VDAC                                                                                                | -240  | -70  | -10  | mV         |

| Phase Firing Comparators                 |            |                                                                                                                     |       |      |      |            |

| Input Offset                             | KEEPOFF    |                                                                                                                     | -30   | 0    | 30   | mV         |

| Propagation Delay                        | KEEPDEL    |                                                                                                                     | -     | -    | 320  | ns         |

| Phase Shedding Comparators               |            |                                                                                                                     |       |      |      |            |

| Bias Current                             | PHSDBIAS   |                                                                                                                     | -2    | 0    | 2    | μΑ         |

| Threshold                                | PHSDTHRS   | Comparator 1                                                                                                        | 1.3   | 1.7  | 2.0  |            |

|                                          |            | Comparator 2                                                                                                        | 3.0   | 3.4  | 3.85 | V          |

|                                          |            | Comparator 3                                                                                                        | 4.8   | 5.1  | 5.55 |            |

| PWM Comparator                           |            |                                                                                                                     |       |      |      |            |

| PWM Ramp Slope                           | PWMSLP     | V12V= 12V                                                                                                           | 42    | 52.5 | 57   | mV/<br>%DC |

| Minimum Pulse Width                      | PWMMIN     | Note 1                                                                                                              |       | 55   | 70   | ns         |

| Input Offset Voltage                     | PWMOFF     | Note 1                                                                                                              | -5    | 0    | 5    | mV         |

| Share Adjust Amplifier                   | <u> </u>   |                                                                                                                     |       |      |      |            |

| Input Offset Voltage                     | SAAOFF     | Note 1                                                                                                              | -3    | 0    | 3    | mV         |

| Gain                                     | SAAGAIN    | CSIN+ = CSIN- = DACIN, Note 1                                                                                       | 4     | 5.0  | 6    | V/V        |

| Unity Gain Bandwidth                     |            | Note 1                                                                                                              | 4     | 8.5  | 17   | kHz        |

| Maximum PWM Ramp                         | MINFLOOR   | IOUT = DACIN – 200mV                                                                                                | 100   | 180  | 22 0 | mV         |

| Floor Voltage                            | 144V51 00D | Measure relative to floor voltage                                                                                   | 100   | 100  | 22 0 | 1110       |

| Minimum PWM Ramp<br>Floor Voltage        | MAXFLOOR   | IOUT = DACIN + 200mV<br>Measure relative to floor voltage                                                           | -220  | -160 | -100 | mV         |

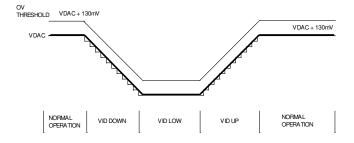

| Over Voltage Protection (OVP) Com        | parators   |                                                                                                                     |       |      |      |            |

| Threshold at Power-up                    | OVPPUP     |                                                                                                                     | 1.615 | 1.65 | 1.67 | V          |

| Threshold during Normal<br>Operation     | OVPTHR     | Compare to VID Voltage + VID offset                                                                                 | 100   | 130  | 150  | mV         |

| Propagation Delay to OVP                 | OVPPROP    | Measure time from V(FB), V(FB1) > VID voltage + VID offset (250mV overdrive) to V(PWM) transition to > 0.5 * V(VCC) | -     | 90   | 180  | ns         |

| PARAMETER                                                   | SYMBOL             | CONDITIONS                                                           | MIN    | TYP  | MAX   | UNIT |

|-------------------------------------------------------------|--------------------|----------------------------------------------------------------------|--------|------|-------|------|

| Turbo Circuit                                               | STIVIDOL           | CONDITIONS                                                           | IVIIIV | 1117 | IVIAA | ONII |

| Activation Threshold Voltage                                | TUDDAGT            | Compare to EA, Note 1                                                |        |      |       |      |

|                                                             | TURBACT<br>Note 1  | Compare to LA, Note 1                                                | -      | 390  | -     | mV   |

| Turbo Comparator Hysteresis                                 | TURBHYST<br>Note 1 | Note 1                                                               | -      | 90   | -     | mV   |

| Filter Time Constant                                        | TURBTIME<br>Note 1 | Note 1                                                               | -      | 8    | -     | μs   |

| Turbo Pulse Width                                           | TURBPW             | 500kHz 600mV Peak sine wave<br>on EAIN, measure GATEH pulse<br>width | 115    | 230  | 280   | ns   |

| Peak Detect Reset<br>Time Constant                          | TURBRESET          |                                                                      | -      | 400  | -     | ns   |

| Over-Current Comparator                                     |                    |                                                                      |        |      |       |      |

| Input Filter Time Constant                                  |                    |                                                                      | -      | 2    | -     | μs   |

| Over-Current Threshold                                      | OCTHRSH            | VDRP-VDAC, VDRP1-VDAC1                                               | 0.94   | 1.08 | 1.18  | V    |

| OC Threshold PSI Reduction                                  | OCPSI              | PSI mode, 4ph to 2ph, 2ph to 1ph                                     | 450    | 540  | 610   |      |

| Factor                                                      |                    | PSI mode, 3ph to 1ph                                                 | 310    | 360  | 410   |      |

|                                                             |                    | 3ph to 2ph                                                           | 640    | 720  | 800   | mV   |

|                                                             |                    | PSI mode, 4ph to 1ph                                                 | 220    | 270  | 310   |      |

|                                                             |                    | 4ph to 3ph                                                           | 690    | 800  | 900   |      |

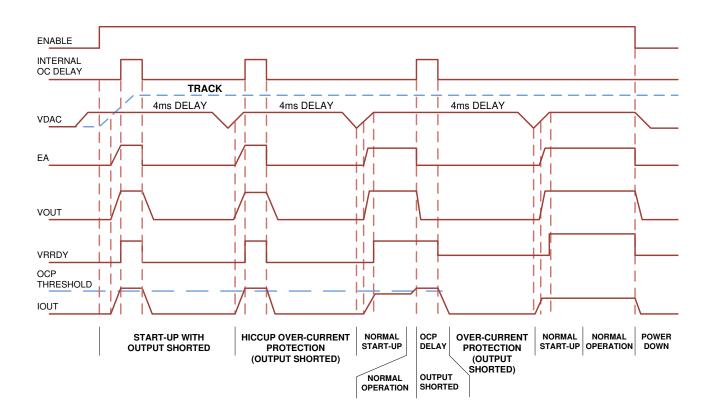

| OC Delay Time                                               | OCDELAY            | Delay to OC shutdown                                                 |        |      |       |      |

| OC Hiccup Time                                              | OCDELAT            | Relaxation Delay                                                     | 225    | 256  | 285   | μs   |

| <u> </u>                                                    |                    | Relaxation Delay                                                     | -      | 4096 | -     | μs   |

| VCC Undervoltage                                            | LYCOSTART          | 1                                                                    |        | ı    | ı     |      |

| VCC UVL Start                                               | VCCSTART           |                                                                      | 5.5    | 5.85 | 6.4   | V    |

| VCC UVL Stop                                                | VCCSTOP            |                                                                      | 4.85   | 5.2  | 5.65  | V    |

| VCC UVL Hysteresis                                          | VCCHYST            |                                                                      | 515    | 650  | 830   | mV   |

| VRRDY Output                                                |                    |                                                                      |        |      |       |      |

| Output Voltage                                              | VRRDYLO            | I(VRRDY, VDRRY1) = 4mA                                               | -      | 150  | 300   | mV   |

| Leakage Current                                             | VRRDYLEAK          | V(VRRDY, VDRRY1) = 5.5V                                              | -      | 0    | 10    | μΑ   |

| VCC Activation Voltage                                      | VRRDYVCC           | I(VDRRY, VDRRY1) = 4mA,<br><300mV                                    | 1      | 2    | 3.6   | V    |

| VO-VDAC Undervoltage<br>Threshold                           | VOUVRISE           | Reference to VDAC                                                    | -340   | -290 | -230  | mV   |

| Open Sense Line Detection                                   |                    |                                                                      |        |      |       |      |

| Sense Line Detection Active<br>Comparator Threshold Voltage | OPENACT            |                                                                      | 100    | 150  | 200   | mV   |

| Sense Line Detection Active<br>Comparator Offset Voltage    | OPENOFF            | V(VO) < [V(VOSEN+) –<br>V(LGND)] / 2                                 | 25     | 60   | 80    | mV   |

| VOSEN+ Open Sense Line<br>Comparator Threshold              | OPENCOMP+          | Compare to V(VCC)                                                    | 82     | 90   | 92    | %    |

| VOSEN- Open Sense Line<br>Comparator Threshold              | OPENCOMP-          |                                                                      | 0.36   | 0.40 | 0.44  | V    |

| Sense Line Detection Source Currents                        | OPENSRC            | V(VO) = 100mV                                                        | 200    | 500  | 700   | μΑ   |

| VCC Buck Regulator                                          |                    |                                                                      |        |      |       |      |

| VCC Output Voltage                                          | VCC100             | 100–400 mA load current                                              | 6.5    | 6.8  | 7.1   | V    |

| PARAMETER                                 | SYMBOL       | CONDITIONS                                                                                | MIN  | TYP  | MAX  | UNIT |

|-------------------------------------------|--------------|-------------------------------------------------------------------------------------------|------|------|------|------|

| Switch Node Rise Time                     | SWRISE       | Note 1                                                                                    | -    | 5    | -    | ns   |

| Switch Node Fall Time                     | SWFALL       | Note 1                                                                                    | -    | 15   | -    | ns   |

| A/D Program Inputs                        |              |                                                                                           |      |      |      |      |

| ADDR Pin Bias Current                     | ADDRBIAS     |                                                                                           | -2   | 0    | 2    | μΑ   |

| ICCP Pin Bias Current                     | ICCPBIAS     |                                                                                           | -2   | 0    | 2    | μΑ   |

| TSENS Pin Bias Current                    | TSENBIAS     |                                                                                           | -2   | 0    | 2    | μΑ   |

| A/D Comparator Offset                     | ADOFFSET     |                                                                                           | -5   | 0    | 5    | mV   |

| V12V Undervoltage                         |              |                                                                                           |      |      |      |      |

| VCC V12V Start                            | VCCSTART     |                                                                                           | 8.8  | 9.6  | 10.2 | V    |

| VCC V12V Stop                             | VCCSTOP      |                                                                                           | 7.8  | 8.6  | 9.2  | V    |

| VCC V12V Hysteresis                       | VCCHYST      |                                                                                           | 0.8  | 1    | 1.3  | V    |

| SerialVID                                 |              |                                                                                           |      |      |      |      |

| ALERT#, VDIO Buffer On                    | ALERTRES     |                                                                                           |      |      | 14.2 | _    |

| Resistance                                |              |                                                                                           | -    | -    | 14.3 | Ω    |

| ALERT#, VDIO Leakage Current              | ALERTLEAK    |                                                                                           | -10  | 0    | 10   | μΑ   |

| VCLK Bias Current                         | VCLKBIAS     |                                                                                           | -1   | 0    | 1    | μΑ   |

| VDIO Bias Current                         | VDIOBIAS     |                                                                                           | -1   | 0    | 1    | μΑ   |

| Transmit Data Prop Delay                  | XMITDELAY    | VCLK rising to VDIO change                                                                | 4    | 6    | 12   | ns   |

| Comparator Threshold                      | SVIDTHRSH    | VCLK, VDIO rising                                                                         | 500  | 590  | 650  | mV   |

|                                           |              | VCLK, VDIO falling                                                                        | 450  | 515  | 650  | 1117 |

| Comparator Hysteresis                     | SVIDHYST     |                                                                                           | 50   | 75   | -    | mV   |

| Link States Reset Timer                   | SVIDTIME     |                                                                                           | 200  | -    | 600  | ns   |

| PWMx Outputs                              |              |                                                                                           |      |      |      |      |

| Source Resistance                         | PWMSRCR      |                                                                                           | 50   | 144  | 500  | Ω    |

| Sink Resistance                           | PWMSNKR      |                                                                                           | 75   | 117  | 290  | Ω    |

| Tri-state Source Impedance                | PWMTRIZ      |                                                                                           | 2.0  | 5.4  | 7.5  | ΚΩ   |

| Tri-state Bias Current                    | PWMTRIBIAS   | V(PWMx) = 1.65V                                                                           | -5   | 0    | 5    | μΑ   |

| Tri-state Active Pull-up                  | PWMTRIPUP    | V(PWMx) while sourcing                                                                    |      |      |      |      |

|                                           |              | 100 μA to GND                                                                             | 0.5  | 1    | 1.2  | V    |

| Disable Comparator Threshold              | PWMDISTHR    |                                                                                           | 0.4  | 0.6  | 0.9  | V    |

| PWM High Voltage                          | PWMHIGH      | I(PWM) = -1mA,                                                                            |      |      |      |      |

| i www.riigii voitage                      | 1 WIVIIIIGII | measure VCC-PWM                                                                           | -    | -    | 1    | V    |

| PWM Low Voltage                           | PWMLOW       | I(PWM) = -1mA                                                                             | -    | -    | 1    | V    |

| Body Braking Comparator                   |              |                                                                                           |      |      |      |      |

| Threshold Voltage with EAIN<br>Decreasing | BBRTHRFALL   | Measure relative to floor voltage                                                         | -300 | -200 | -110 | mV   |

| Threshold Voltage with EAIN Increasing    | BBRTHRRISE   | Measure relative to floor voltage                                                         | -200 | -100 | -10  | mV   |

| Hysteresis                                | BBRTHRHYS    |                                                                                           | 70   | 105  | 130  | mV   |

| Propagation Delay                         | BBRDELAY     | VCC = 5V Measure time from EAIN < V(DACIN) (200mV overdrive) to GATEL transition to < 4V. | 30   | 65   | 90   | ns   |

| BBR1# Source Resistance                   | BBRSRCRES    | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                   | 20   | 40   | 75   | Ω    |

| PARAMETER                          | SYMBOL     | CONDITIONS                                                                            | MIN   | ТҮР  | MAX | UNIT |

|------------------------------------|------------|---------------------------------------------------------------------------------------|-------|------|-----|------|

| BBR1# Sink Resistance              | BBRSNKRES  |                                                                                       | 10    | 35   | 60  | Ω    |

| BBR1# High Voltage                 | BBRHIGH    | I(BBR1#) = -1mA, measure V(VCC)  – V(BBR1#)                                           | 0     | 0.4  | 0.8 | V    |

| BBR1# Low Voltage                  | BBRLOW     | I(BBR1#) = 1mA                                                                        | 0     | 0.35 | 0.8 | V    |

| Remote Sense Differential Amplifie | er         |                                                                                       |       |      |     |      |

| Unity Gain Bandwidth               | RSABW      | Note 1                                                                                | 1.5   | 3.2  | 4.5 | mV   |

| Input Outset Voltage               | RSAOFF     | 0.25V≤ V(VOSEN+) - V(VOSEN-)<br>≤ 1.52V,<br>0.25V≤ V(VOSEN1+) - V(VOSEN1-)<br>≤ 1.52V | -5    | 0    | 5   | mV   |

| Sink Current                       | RSASINK    | 0.5V≤ V(VOSEN+) - V(VOSEN-)<br>≤ 1.52V,<br>0.5V≤ V(VOSEN1+) - V(VOSEN1-)<br>≤ 1.52V   | 0.4   | 1    | 2   | mA   |

|                                    |            | V(VOSEN+) - V(VOSEN-) = 0.25V,<br>V(VOSEN1+) - V(VOSEN1-) =<br>0.25V                  | 0.225 | 0.5  | 0.8 |      |

| Source Current                     | RSASRC     | 0.25V≤ V(VOSEN+) - V(VOSEN-)<br>≤ 1.52V,<br>0.25V≤ V(VOSEN1+) - V(VOSEN1-)<br>≤ 1.52V | 3     | 9    | 20  | mA   |

| Slew Rate                          | RSASLEW    | 0.25V≤ V(VOSEN+) - V(VOSEN-)<br>≤ 1.52V,<br>0.25V≤ V(VOSEN1+) - V(VOSEN1-)<br>≤ 1.52V | 2     | 4    | 8   | V/μs |

| VOSEN+ Bias Current                | VOSNS-BIAS | 0.25 V < V(VOSEN+) < 1.52V,<br>0.25 V < V(VOSEN1+) < 1.52V                            | -     | 27   | 50  | μА   |

| VOSEN- Bias Current                | VOSNS+BIAS | -0.3V ≤ VOSEN- ≤ 0.3V, All VID<br>Codes,<br>-0.3V ≤ VOSEN1- ≤ 0.3V, All VID<br>Codes  | -     | 27   | 70  | μΑ   |

| High Voltage                       | VOHIGH     | V(VCC) – V(VO), V(VCC) – V(VO1)                                                       | 1.5   | 2    | 2.5 | V    |

| Low Voltage                        | VOLOW      | V(VCC) = 7V                                                                           | -     | 60   | 100 | mV   |

| VRHOT# Comparator                  |            |                                                                                       |       |      |     |      |

| Output Voltage                     | VRHTOUT    | I(VRHOT#) = 30mA                                                                      | -     | 150  | 400 | mV   |

| VRHOT# Leakage Current             | VRHTLEAK   | V(VRHOT#) = 5.5V                                                                      | -     | 0    | 10  | μΑ   |

| Platform Test Mode                 |            |                                                                                       |       |      |     |      |

| Comparator Threshold               | PTMTHR     | Raise ADDR voltage after VIN power-up                                                 | 2.2   | 2.6  | 3.1 | V    |

| Link States Reset Timer            | PTMTIME    |                                                                                       | 20    | -    | 24  | μs   |

| VR Settled                         |            |                                                                                       |       |      |     |      |

| Comparator Offset                  | VRSTLOFF   | Compare FB to VDAC reference                                                          | -     | 20   | -   | mV   |

| Delay to ALERT#                    | VRSTLDELAY | Delay after DAC settled to within 2 VID steps of final value                          | -     | 5    | -   | μs   |

| Current Inputs                     |            |                                                                                       |       |      |     |      |

| IINx to IINx Impedance             | IINRES     |                                                                                       | -     | 3000 | -   | Ω    |

| IINx to IINx Leakage Current       | IINLEAK    |                                                                                       | -1    | 0    | 1   | μΑ   |

| TRACK Inputs                       |            |                                                                                       |       |      |     |      |

| Input Leakage                      |            |                                                                                       | -1    | 0    | 1   | μΑ   |

IR3531

| PARAMETER                  | SYMBOL  | CONDITIONS                          | MIN   | TYP  | MAX   | UNIT |

|----------------------------|---------|-------------------------------------|-------|------|-------|------|

| TRACK to FB Offset         |         | Error amp in unity gain             | 15    | 36   | 65    | mV   |

| Release Error Voltage      |         | TRACK = VDAC+100mV, VDAC-FB         | -1    | 0    | 1     | mV   |

| VO Discharge Comparators   |         |                                     |       |      |       |      |

| Tri-state Enable Threshold |         | VO when PWM outputs enter tri-state | 200   | 250  | 300   | mV   |

| SCLK Synchronization Input |         |                                     |       |      |       |      |

| Rising Threshold           |         |                                     | 0.8   | 1.2  | 1.3   | V    |

| Falling Threshold          |         | Note 1                              | 0.625 | 0.85 | 1.025 | V    |

| Input Leakage              |         |                                     | -5    | 0    | 5     | μΑ   |

| Propagation Delay Rising   |         |                                     | -     | -    | 60    | ns   |

| Input Capacitance          |         | Note 1                              | -     | -    | 10    | рF   |

| General                    |         |                                     |       |      |       |      |

| VCC Supply Current         | VCCBIAS |                                     | 3     | 7    | 12    | mA   |

#### Notes:

- 1. Guaranteed by design but not tested in production

- 2. Error Amplifier input offset is trimmed to within ±1% for optimal system set point accuracy.

- 3. Final test VBOOT options of 0, 0.9, 1.35 and 1.5V are feasible. Contact International Rectifier Enterprise Power Business Unit for details.

- 4. Use of internal oscillator is not recommended, use SCLK input to set PWM frequency.

## THEORY OF OPERATION

#### SYSTEM DESCRIPTION

The IR3531 Multiphase Buck power system provides voltage regulation solutions for two individual supply outputs. The main output, RailO, controls up to four phases and produce up to 200A when paired with appropriate power stages. The secondary output, Rail1, is a single phase output capable of up to 50A, again with appropriate power stage. The IR3531 control IC is specialized to allow external clock synchronization and tracking capability for each rail. Features include a serial control and telemetry bus that can control output voltage settings and slew rates while allowing monitoring of the system thermals and load currents. The IR3531 control IC contains all necessary housekeeping, protection and control functions and communicates a three-level PWM signal to each power stage.

#### FREQUENCY AND PHASE TIMING CONTROL

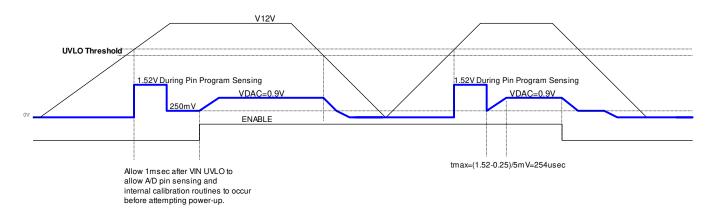

The IR3531 operates with external frequency synchronization which can be used to control input ripple from multiple paralleled power supply systems. Systems can be forced to operate out of phase thereby reducing instantaneous peak input currents and also controlling system noise signatures. The internal oscillator is used to calibrate the PWM ramp slopes and other functions at power up therefore it is desirable for the externally applied synchronization frequency to be very near the ROSC programmed internal frequency times the number of active phases. Calibration can take up to 1ms. This results in the PWM gain to be near the desired 50mV/% duty cycle. Furthermore, it is desired the SCLK input be stable prior to enabling the IR3531 voltage regulator.

The SCLK input frequency provided needs to equal the desired base switching frequency multiplied by the active number of phases. Phase shedding is available however SCLK needs to be adjusted accordingly to match the number of active phases.

Phase timing and interleave spacing is automatically optimized inside the controller and can accommodate changing phases on the fly (phase shedding). The PHSSHD pin can be used to dynamically drop from 1-3 phases while minimizing output voltage transients. Also, phases can be disabled by grounding the PWM outputs of the IR3531. Notice the driver ICs should be removed since a PWM low signal indicates a 0% duty cycle state which turns on the low-side MOSFETs and can potentially develop large negative inductor currents. The control IC detects which PWM pins are grounded during power up to determine the populated number of phases and automatically optimizes phase timing for minimal system ripple.

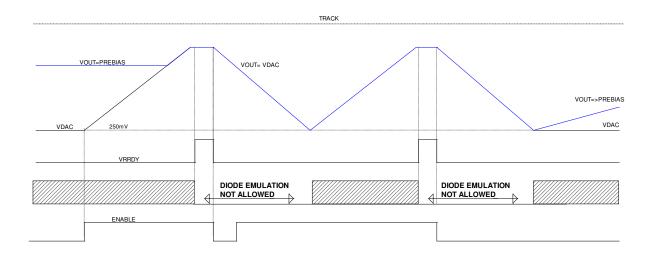

#### TRACK FUNCTIONALITY

Both Rail outputs of the IR3531 can be independently controlled through their respective TRACK inputs. TRACK pins override the internal VDAC reference inputs to the Error Amplifiers allowing users to control power up and power down VR output voltage characteristics. The IR3531 is fully soft-stop and pre-bias compatible. The control loop is full synchronous during soft stop events thereby preventing COUT capacitor discharge-induced inductive kicks. The control system allows non-synchronous buck operation once VO <=250mV — this allows outputs to return to their pre-biased operating points if available.

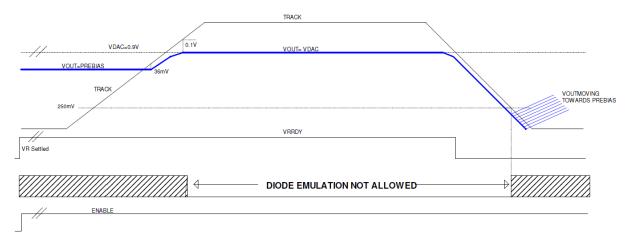

**Figure 6: TRACK Operation with Pre-Bias**

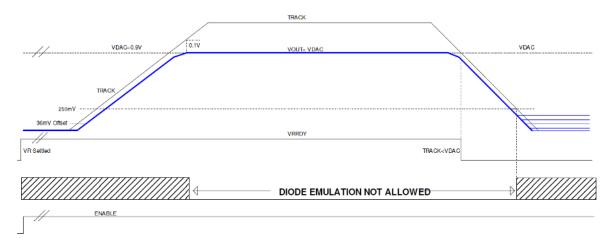

Figure 7: TRACK Operation without Pre-Bias

The TRACK inputs have a typical 36mV offset from the closed loop feedback operating point to ensure the error amplifier is in an off state when TRACK=0V. Furthermore, TRACK must exceed the respective VDAC by at least 100mV to ensure VDAC has complete control of the Error Amplifier as shown in Figures 6 and 7.

As a cautionary note the track input provides direct control of the output PWM duty cycle. The presence of excessive noise or glitches on TRACK when this input is active can cause sudden increases in the PWM duty cycle (up to 100%), potentially causing damage to the power converter.

#### **PWM CONTROL METHOD**

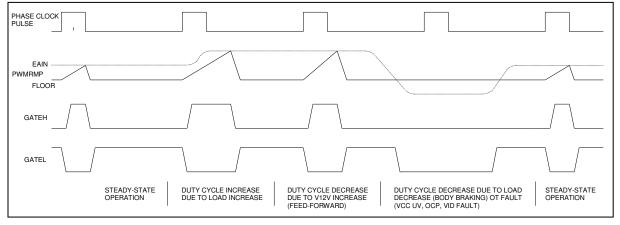

The steady state control architecture utilized in the IR3531 is feed-forward voltage mode control with trailing edge modulation. A high-gain wide-bandwidth voltage type error amplifier is used to achieve accurate voltage regulation and ultra-fast transient response. Feed-forward control is established by varying the PWM ramp slope proportionally to the input voltage resulting in the error amplifier operating point being independent of the input voltage. The input voltage can change due to variations in the silver box output voltage or due to the wire and PCB-trace voltage drop related to changes in load current. All PWM ramp slopes are calibrated at initial power-up. The PWM pulse is terminated once the PWM ramp exceeds the Error Amplifier output voltage.

Under dynamic load transitions, the IR3531 utilizes our patented Body Braking Malgorithm allows all low-side MOSFETs to be turned off during a load relaxation event allowing the MOSFET body diodes to conduct and dissipate some of the stored inductor energy and also speed up the inductor current slew rate by introducing a larger voltage

across the inductor. Body Braking<sup>™</sup> reduces the peak overshoot of the converter.

An error amplifier output voltage greater than the common mode input range of the PWM comparator results in 100% duty cycle regardless of the voltage of the PWM ramp. The resulting PWM control loop is capable of transitioning from 0% duty cycle to 100% duty cycle with overlapping phases within a few tens of nanoseconds in response to a load step decrease. Figure 8 on the next page depicts PWM operating waveforms under various conditions.

## **BODY BRAKING™**

In a conventional synchronous buck converter, the minimum time required to reduce the current in the inductor in response to a load-step decrease is:

$$T_{SLEW} = \frac{L*(I_{MAX} - I_{MIN})}{V_{O}}$$

The slew rate of the inductor current can be significantly increased by turning off the synchronous rectifier in response to a load-step decrease. The switch node voltage is then forced to decrease until conduction of the synchronous rectifier's body diode occurs. This increases the voltage across the inductor from Vout to Vout + V\_BODYDIODE. The minimum time required to reduce the current in the inductor in response to a load transient decrease is now:

$$T_{SLEW} = \frac{L*(I_{MAX} - I_{MIN})}{V_O + V_{BODYDIODE}}$$

Since the voltage drop in the body diode is often comparable to the output voltage, the inductor current

slew rate can be increased significantly. This patented

**Figure 8: PWM Operating Waveforms**

technique is referred to as "body braking" and is accomplished through the "body braking comparator." If the error amplifier's output voltage drops below VDAC, this comparator turns off the low-side gate driver, enabling the bottom FET body diode to take over. There is 100mV upslope and 200mV down slope hysteresis for the body braking comparator.

#### **BODY BRAKING™**

In a conventional synchronous buck converter, the minimum time required to reduce the current in the inductor in response to a load-step decrease is:

$$T_{SLEW} = \frac{L*(I_{MAX} - I_{MIN})}{V_O}$$

The slew rate of the inductor current can be significantly increased by turning off the synchronous rectifier in response to a load-step decrease. The switch node voltage is then forced to decrease until conduction of the synchronous rectifier's body diode occurs. This increases the voltage across the inductor from Vout to Vout +  $V_{\text{BODYDIODE}}$ . The minimum time required to reduce the current in the inductor in response to a load transient decrease is now:

$$T_{SLEW} = \frac{L * (I_{MAX} - I_{MIN})}{V_O + V_{RODYDIODE}}$$

Since the voltage drop in the body diode is often comparable to the output voltage, the inductor current

slew rate can be increased significantly. This patented technique is referred to as "body braking" and is accomplished through the "body braking comparator." If the error amplifier's output voltage drops below VDAC, this comparator turns off the low-side gate driver, enabling the bottom FET body diode to take over. There is 100mV upslope and 200mV down slope hysteresis for the body braking comparator.

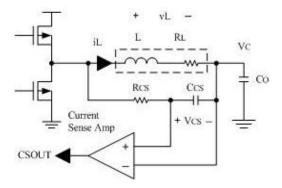

# LOSSLESS AVERAGE INDUCTOR CURRENT SENSING

Inductor current can be sensed by connecting a series resistor and a capacitor network in parallel with the inductor and measuring the voltage across the capacitor, as shown in Figure 8. The equation of the sensing network is:

$$v_C(s) = v_L(s) \frac{1}{1 + sR_{CS}C_{CS}} = i_L(s) \frac{R_L + sL}{1 + sR_{CS}C_{CS}}$$

Usually the resistor Rcs and capacitor Ccs are chosen, such that, the time constant of Rcs and Ccs equals the time constant of the inductor, which is the inductance L over the inductor DCR RL. If the two time constants match, the voltage across Ccs is proportional to the current through L, and the sense circuit can be treated as if only a sense resistor with the value of RL was used. The mismatch of the time constants does not affect the measurement of inductor DC current, but affects the AC component of the inductor current.

Figure 9: Inductor Current Sensing and Current Sense Amplifier

The advantage of sensing the inductor current versus high-side or low-side sensing is that actual output current being delivered to the load is obtained rather than peak or sampled information about the switch currents. The output voltage can be positioned to meet a load line based on real-time information. Except for a sense resistor in series with the inductor, this is the only sense method that can support a single cycle transient response. Other methods provide no information during either load increase (low-side sensing) or load decrease (high-side sensing).

An additional problem associated with peak or valley current mode control for voltage positioning is that they suffer from peak-to-average errors. These errors will appear in many ways but one example is the effect of frequency variation. If the frequency of a particular unit is 10% low, the peak-to-peak inductor current will be 10% larger and the output impedance of the converter will drop by about 10%. Variations in inductance, current sense amplifier bandwidth, PWM prop delay, any added slope compensation, input voltage, and output voltage are all additional sources of peak-to-average errors.

#### **CURRENT SENSE AMPLIFIER**

A high speed differential current sense amplifier is located in our driver ICs, as shown in Figure 9. Its gain is nominally 32.5 over the entire temperature operating range therefore the 3850 ppm/°C inductor DCR temperature coefficient should be compensated in the voltage loop feedback path. This can be accurately compensated by using a linearized Negative TC resistor network where the NTC can be located near the output inductors. The resulting temperature compensated current information is used by the control IC for voltage positioning and current reporting, and over current limit protection.

The input offset of this amplifier is calibrated to within +/-  $450\mu V$  (6 sigma limits) with a 200uV typical LSB calibration bit. This calibration routine is continuous and occurs at every 56 PWM cycles.

The current sense amplifier can accept positive differential input up to 50mV and negative up to -10mV before clipping. The output of the current sense amplifier is summed with the VDAC voltage and is returned to the control IC through the IIN pin. The IIN pins in the control IC are internally tied together through 3 KOhm resistors to produce a voltage representative of the average phase inductor current.

#### **AVERAGE CURRENT SHARE LOOP**

A current sharing loop is also incorporated in the IR3531 to ensure balance between the multiphase buck power stages. Poor current sharing can hamper transient response and degrade overall system efficiency. The current information of each phase is compared against the average phase current through a Share Adjust Amplifier which then manipulates the respective PWM ramp start voltage to add or subtract PWM output duty cycle. The current share amplifier is internally compensated such that the crossover frequency of the current share loop is much slower than that of the voltage loop and the two loops do not interact.

#### **INSTANTANEOUS CURRENT BALANCE**

A form of coarse current sharing is also incorporated into the IR3531 to protect against Synchronized High Load Repetition Rate transients which can saturate inductors and cause OVP conditions. The phase firing order of the multiphase system is continually being re-assessed and adjusted if required on a cycle-by-cycle basis to prevent instantaneous phase currents from deviating from each other. This also improves transient response by ensuring all phase currents track each other within a few switching cycles. Individual switch nodes will appear to be variable frequency however input and output ripple are unaffected by the varying phase firing order.

#### **SVID CONTROL**

The SVID bus allows the processor to communicate with the IR3531. The processor can program the voltage regulator output voltage and monitor telemetry data the IR3531 offers such as temperature and both rail currents. VCLK, VDIO and ALERT# communication lines are designed for external 50-75 ohm pull up resistors to 1.0-1.2V bias voltage and should not be floated. Note that ALERT# may assert twice for VID transitions of 2 VID steps or less. Addressing is programmed as a percentage of VDAC as shown by selecting the appropriate ADDR pin resistor divider combination and supports up to 14 addresses and 2 all call addresses (refer to Table 1). Table 2 provides a list of supported SVID commands. Table 3 provides a list of supported required SVID registers. The SVID communicates VID codes listed in Table 4a and 4b to program the VDAC set point.

The IR3531 can accept changes in the VID code and will vary the VDAC voltage accordingly. The slew rate of the voltage at the VDAC pin can be set by the appropriate command. The slew rate is internally programmed and no external pins or components are necessary. Digital VID transitions result in a smooth analog transition of the VDAC voltage and converter output voltage minimizing inrush currents, false over current conditions and overshoot of the output voltage.

The VID data from the SVID bus is stored in registers and is sent to the Digital-to-Analog Converter (DAC), whose output is sent to the VDAC buffer amplifier. The output of the buffer amplifier is the VDAC pin. To achieve optimal system setpoint voltage accuracy, first all contributing offsets of the IR3531 are independently trimmed and lastly the internal VDAC reference is trimmed to take into account all sum of all the offset components. Note that the resulting final VDAC voltage will have a slightly wider tolerance as it is compensating for the sum of all other offset components. This results in an overall 0.5% system set-point accuracy for VID range between 1V to 1.52V.

TABLE 1: ADDR/PSN A/D VOLTAGE PROGRAMMING (AS % OF VDAC)

| % of<br>VDAC | Binary<br>Code | Address<br>Name | Sync       | Turbo   |

|--------------|----------------|-----------------|------------|---------|

| 1.5%         | 00000          | A0/A1           | Ext. Sync  | Enable  |

| 4.7%         | 00001          | A0/A1           | Ext. Sync  | Disable |

| 7.8%         | 00010          | A0/A1           | Int. Clock | Enable  |

| 11%          | 00011          | A0/A1           | Int. Clock | Disable |

| 14%          | 00100          | A2/A3           | Ext. Sync  | Enable  |

| 17.2%        | 00101          | A2/A3           | Ext. Sync  | Disable |

| 20.3%        | 00110          | A2/A3           | Int. Clock | Enable  |

| 23.4%        | 00111          | A2/A3           | Int. Clock | Disable |

| 26.5%        | 01000          | A4/A5           | Ext. Sync  | Enable  |

| 29.7%        | 01001          | A4/A5           | Ext. Sync  | Disable |

| 32.8%        | 01010          | A4/A5           | Int. Clock | Enable  |

| 36%          | 01011          | A4/A5           | Int. Clock | Disable |

| 39%          | 01100          | A6/A7           | Ext. Sync  | Enable  |