## National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

### LP3882

# 1.5A Fast-Response Ultra Low Dropout Linear Regulators

### **General Description**

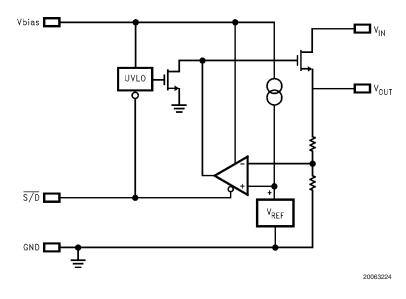

The LP3882 is a high current, fast response regulator which can maintain output voltage regulation with minimum input to output voltage drop. Fabricated on a CMOS process, the device operates from two input voltages: Vbias provides voltage to drive the gate of the N-MOS power transistor, while Vin is the input voltage which supplies power to the load. The use of an external bias rail allows the part to operate from ultra low Vin voltages. Unlike bipolar regulators, the CMOS architecture consumes extremely low quiescent current at any output load current. The use of an N-MOS power transistor results in wide bandwidth, yet minimum external capacitance is required to maintain loop stability.

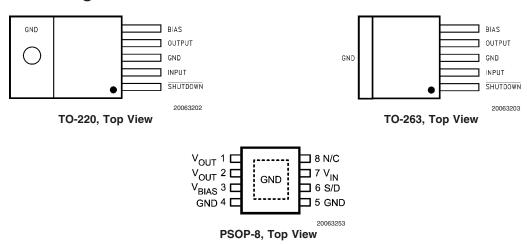

The fast transient response of these devices makes them suitable for use in powering DSP, Microcontroller Core voltages and Switch Mode Power Supply post regulators. The parts are available in TO-220, TO-263 and PSOP-8 packages.

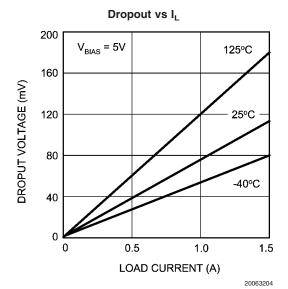

Dropout Voltage: 110 mV (typ) @ 1.5A load current.

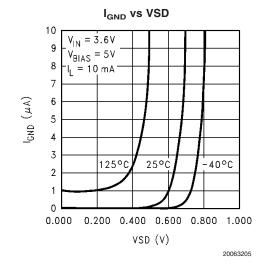

Ground Pin Current: 3 mA (typ) at full load.

Shutdown Current: 60 nA (typ) when S/D pin is low.

Precision Output Voltage: 1.5% room temperature accu-

racy.

#### **Features**

- Ultra low dropout voltage (110 mV @ 1.5A typ)

- Low ground pin current

- Load regulation of 0.04%/A

- 60 nA typical guiescent current in shutdown

- 1.5% output accuracy (25°C)

- TO-220, TO-263 and PSOP-8 packages

- Over temperature/over current protection

- -40°C to +125°C junction temperature range

## **Applications**

- DSP Power Supplies

- Server Core and I/O Supplies

- PC Add-in-Cards

- Local Regulators in Set-Top Boxes

- Microcontroller Power Supplies

- High Efficiency Power Supplies

- SMPS Post-Regulators

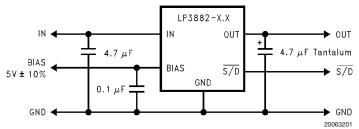

## **Typical Application Circuit**

At least 4.7  $\mu F$  of input and output capacitance is required for stability.

## **Connection Diagrams**

## **Ordering Information**

| Order Number   | Package Type | Package Drawing | Supplied As                 |

|----------------|--------------|-----------------|-----------------------------|

| LP3882ES-1.2   | TO263-5      | TS5B            | Rail                        |

| LP3882ESX-1.2  | TO263-5      | TS5B            | Tape and Reel               |

| LP3882ET-1.2   | TO220-5      | T05D            | Rail                        |

| LP3882ES-1.5   | TO263-5      | TS5B            | Rail                        |

| LP3882ESX-1.5  | TO263-5      | TS5B            | Tape and Reel               |

| LP3882ET-1.5   | TO220-5      | T05D            | Rail                        |

| LP3882ES-1.8   | TO263-5      | TS5B            | Rail                        |

| LP3882ESX-1.8  | TO263-5      | TS5B            | Tape and Reel               |

| LP3882ET-1.8   | TO220-5      | T05D            | Rail                        |

| LP3882EMR-1.2  | PSOP-8       | MRA08B          | Rail                        |

| LP3882EMRX-1.2 | PSOP-8       | MRA08B          | 2500 Units on Tape and Reel |

| LP3882EMR-1.5  | PSOP-8       | MRA08B          | Rail                        |

| LP3882EMRX-1.5 | PSOP-8       | MRA08B          | 2500 Units on Tape and Reel |

| LP3882EMR-1.8  | PSOP-8       | MRA08B          | Rail                        |

| LP3882EMRX-1.8 | PSOP-8       | MRA08B          | 2500 Units on Tape and Reel |

## **Block Diagram**

## **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

-65°C to +150°C Storage Temperature Range Lead Temp. (Soldering, 5 seconds) 260°C **ESD** Rating Human Body Model (Note 3) 2 kV Machine Model (Note 10) 200V Power Dissipation (Note 2) Internally Limited V<sub>IN</sub> Supply Voltage (Survival) -0.3V to +6VV<sub>BIAS</sub> Supply Voltage (Survival) -0.3V to +7V-0.3V to +7V Shutdown Input Voltage (Survival)

I<sub>OUT</sub> (Survival) Internally Limited Output Voltage (Survival) -0.3V to +6V Junction Temperature -40°C to +150°C

## **Operating Ratings**

V<sub>IN</sub> Supply Voltage  $(V_{OUT} + V_{DO})$  to 5.5V Shutdown Input Voltage 0 to +6V 1.5A  $I_{OUT}$ Operating Junction -40°C to +125°C Temperature Range

V<sub>BIAS</sub> Supply Voltage 4.5V to 6V

**Electrical Characteristics** Limits in standard typeface are for  $T_J = 25^{\circ}C$ , and limits in **boldface type** apply over the full operating temperature range. Unless otherwise specified:  $V_{IN} = V_{O}(NOM) + 1V$ ,  $V_{BIAS} = 4.5V$ ,  $I_{L} = 10$  mA,  $C_{IN} = 10$  mA, C $C_{OUT} = 4.7 \mu F$ ,  $V_{S/D} = V_{BIAS}$ .

| Symbol                                                                                | Parameter                               | Conditions                                                        | MIN<br>(Note 5) | Typical<br>(Note 4) | MAX<br>(Note 5) | Units |  |

|---------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------|-----------------|---------------------|-----------------|-------|--|

| \/                                                                                    | Output Voltage Tolerance                | 10 mA < I <sub>1</sub> < 1.5A                                     | 1.198           | (11016 4)           | 1.234           |       |  |

| V <sub>O</sub> Output Voltage Tolerance                                               | Output Voltage Tolerance                | $V_{O}(NOM) + 1V \le V_{IN} \le 5.5V$                             | 1.190           | 1.216               | 1.234           |       |  |

|                                                                                       |                                         | $ V_{O}(NOW) + V \le V_{IN} \le 3.3V$ $ 4.5V \le V_{BIAS} \le 6V$ | 1.186           | 1.210               | 1.246           |       |  |

|                                                                                       |                                         | BIAS = 01                                                         | 1.478           |                     | 1.522           | V     |  |

|                                                                                       |                                         |                                                                   | 1.470           | 1.5                 | 1.022           |       |  |

|                                                                                       |                                         |                                                                   | 1.455           |                     | 1.545           |       |  |

|                                                                                       |                                         |                                                                   | 1.773           |                     | 1.827           |       |  |

|                                                                                       |                                         |                                                                   |                 | 1.8                 |                 |       |  |

|                                                                                       |                                         |                                                                   | 1.746           |                     | 1.854           |       |  |

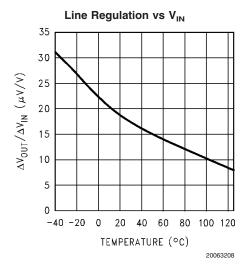

| $\Delta V_{O}/\Delta V_{IN}$                                                          | Output Voltage Line Regulation (Note 7) | $V_O(NOM) + 1V \le V_{IN} \le 5.5V$                               |                 | 0.01                |                 | %/V   |  |

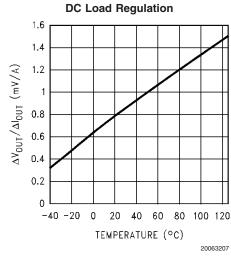

| · -   ·                                                                               | Output Voltage Load Regulation          | 10 mA < I <sub>L</sub> < 1.5A                                     |                 | 0.04                |                 | %/A   |  |

|                                                                                       | (Note 8)                                |                                                                   |                 | 0.06                |                 |       |  |

| V <sub>DO</sub> Dropout Voltage (Note 9)                                              | Dropout Voltage (Note 9)                | I <sub>L</sub> = 1.5A                                             |                 | 110                 | 170             | mV    |  |

|                                                                                       |                                         | (TO220 and TO263 only)                                            |                 | 110                 | 270             |       |  |

|                                                                                       |                                         | I <sub>L</sub> = 1.5A                                             |                 | 125                 | 190             |       |  |

|                                                                                       |                                         | (PSOP only)                                                       |                 | 120                 | 320             |       |  |

| I <sub>Q</sub> (V <sub>IN</sub> ) Quiescent Current Drawn fro                         | Quiescent Current Drawn from            | 10 mA < I <sub>L</sub> < 1.5A                                     |                 | 3                   | 7               | mA    |  |

|                                                                                       | V <sub>IN</sub> Supply                  |                                                                   |                 |                     | 8               |       |  |

|                                                                                       |                                         | V = 0.3V                                                          |                 | 0.03                | 1               | μΑ    |  |

|                                                                                       | <del> </del>                            |                                                                   |                 |                     | 30              | •     |  |

| I <sub>Q</sub> (V <sub>BIAS</sub> ) Quiescent Current Dra<br>V <sub>BIAS</sub> Supply | Quiescent Current Drawn from            | 10 mA < I <sub>L</sub> < 1.5A                                     |                 | 1                   | 2               | mA    |  |

|                                                                                       | V <sub>BIAS</sub> Supply                | V =                                                               |                 |                     | 3               |       |  |

|                                                                                       |                                         | $V   \overline{S/D} \le 0.3V$                                     |                 | 0.03                | 1<br><b>30</b>  | μΑ    |  |

| 1                                                                                     | Short-Circuit Current                   | V 0V                                                              |                 | 4.3                 | 30              | A     |  |

| I <sub>SC</sub><br>Shutdown Ir                                                        |                                         | V <sub>OUT</sub> = 0V                                             |                 | 4.3                 |                 | A     |  |

| V <sub>SDT</sub>                                                                      | Output Turn-off Threshold               | Output ON                                                         | 1.3             | 0.7                 |                 |       |  |

|                                                                                       | Output Turn-on Threshold                | Output = ON                                                       | 1.3             | _                   | 0.0             | V     |  |

| T-1 (OFF)                                                                             | Time OFF Delevi                         | Output = OFF                                                      |                 | 0.7                 | 0.3             |       |  |

| Td (OFF)                                                                              | Turn-OFF Delay                          | R <sub>LOAD</sub> X C <sub>OUT</sub> << Td (OFF)                  |                 | 20                  |                 | μs    |  |

| Td (ON)                                                                               | Turn-ON Delay                           | R <sub>LOAD</sub> X C <sub>OUT</sub> << Td (ON)                   |                 | 15                  |                 |       |  |

| I <sub>S/D</sub>                                                                      | S/D Input Current                       | V <u>S/D</u> =1.3V                                                |                 | 1                   |                 | μΑ    |  |

|                                                                                       |                                         | V = 0.3V                                                          |                 | -1                  |                 |       |  |

**Electrical Characteristics** Limits in standard typeface are for  $T_J = 25^{\circ}C$ , and limits in **boldface type** apply over the full operating temperature range. Unless otherwise specified:  $V_{IN} = V_O(NOM) + 1V$ ,  $V_{BIAS} = 4.5V$ ,  $I_L = 10$  mA,  $C_{IN} = C_{OUT} = 4.7 \ \mu\text{F}$ ,  $V_{S/D} = V_{BIAS}$ . (Continued)

| Symbol                                             | Parameter                                          | Conditions                                     | MIN<br>(Note 5) | Typical<br>(Note 4) | MAX<br>(Note 5) | Units      |  |  |  |

|----------------------------------------------------|----------------------------------------------------|------------------------------------------------|-----------------|---------------------|-----------------|------------|--|--|--|

| AC Parameters                                      |                                                    |                                                |                 |                     |                 |            |  |  |  |

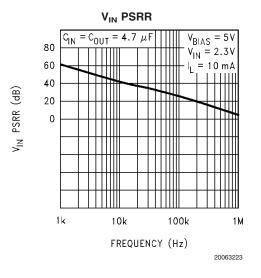

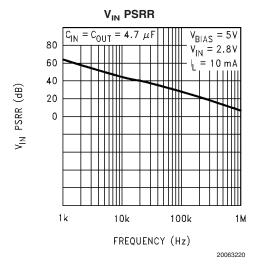

| PSRR (V <sub>IN</sub> )  PSRR (V <sub>BIAS</sub> ) | Ripple Rejection for V <sub>IN</sub> Input Voltage | $V_{IN} = V_{OUT} + 1V$ , $f = 120 \text{ Hz}$ |                 | 80                  |                 | dB         |  |  |  |

|                                                    |                                                    | $V_{IN} = V_{OUT} + 1V$ , $f = 1 \text{ kHz}$  |                 | 65                  |                 |            |  |  |  |

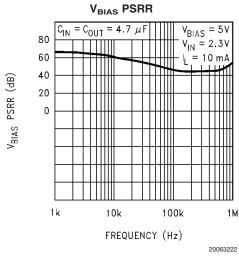

|                                                    | Ripple Rejection for V <sub>BIAS</sub><br>Voltage  | $V_{BIAS} = V_{OUT} + 3V$ , $f = 120 Hz$       |                 | 70                  |                 | ub         |  |  |  |

|                                                    |                                                    | $V_{BIAS} = V_{OUT} + 3V, f = 1 \text{ kHz}$   |                 | 65                  |                 |            |  |  |  |

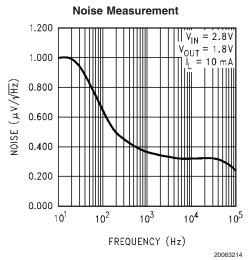

|                                                    | Output Noise Density                               | f = 120 Hz                                     |                 | 1                   |                 | μV/root–Hz |  |  |  |

| e <sub>n</sub>                                     | Output Noise Voltage                               | BW = 10 Hz - 100 kHz                           |                 | 150                 |                 | μV (rms)   |  |  |  |

|                                                    | V <sub>OUT</sub> = 1.8V                            | BW = 300 Hz - 300 kHz                          |                 | 90                  |                 |            |  |  |  |

**Note 1:** Absolute maximum ratings indicate limits beyond which damage to the component may occur. Operating ratings indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications, see Electrical Characteristics. Specifications do not apply when operating the device outside of its rated operating conditions.

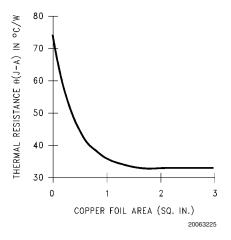

Note 2: At elevated temperatures, device power dissipation must be derated based on package thermal resistance and heatsink thermal values.  $\theta_{J-A}$  for TO-220 devices is 65°C/W if no heatsink is used. If the TO-220 device is attached to a heatsink, a  $\theta_{J-S}$  value of 4°C/W can be assumed.  $\theta_{J-A}$  for TO-263 devices is approximately 40°C/W if soldered down to a copper plane which is at least 1.5 square inches in area.  $\theta_{J-A}$  value for typical PSOP-8 PC board mounting is 166°C/W. If power dissipation causes the junction temperature to exceed specified limits, the device will go into thermal shutdown.

- Note 3: The human body model is a 100 pF capacitor discharged through a 1.5k resistor into each pin.

- Note 4: Typical numbers represent the most likely parametric norm for 25°C operation.

- Note 5: Limits are guaranteed through testing, statistical correlation, or design.

- Note 6: If used in a dual-supply system where the regulator load is returned to a negative supply, the output pin must be diode clamped to ground.

- Note 7: Output voltage line regulation is defined as the change in output voltage from nominal value resulting from a change in input voltage.

- Note 8: Output voltage load regulation is defined as the change in output voltage from nominal value as the load current increases from no load to full load.

- **Note 9:** Dropout voltage is defined as the minimum input to output differential required to maintain the output with 2% of nominal value. The PSOP-8 package devices have a slightly higher dropout voltage due to increased band wire resistance.

- Note 10: The machine model is a 220 pF capacitor discharged directly into each pin. The machine model ESD rating of pin 5 is 100V.

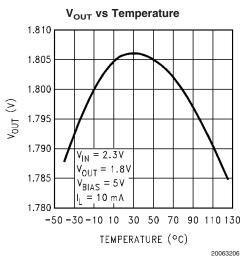

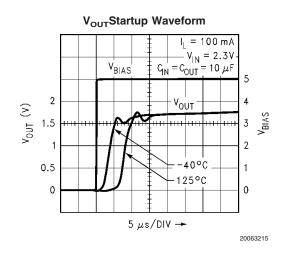

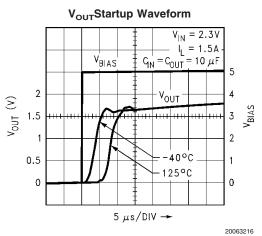

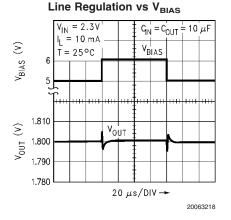

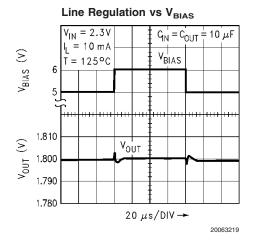

##

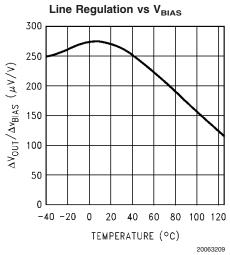

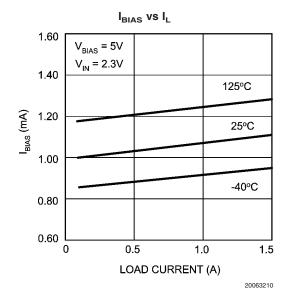

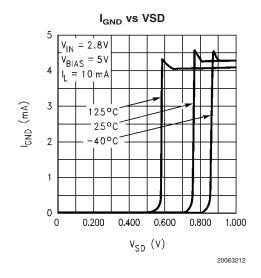

**Typical Performance Characteristics** Unless otherwise specified:  $T_A = 25^{\circ}C$ ,  $C_{OUT} = 4.7\mu F$ , Cin =  $4.7\mu F$ ,  $\overline{S/D}$  pin is tied to  $V_{BIAS}$ ,  $V_{IN} = 2.2V$ ,  $V_{OUT} = 1.8V$ . (Continued)

##

## **Application Hints**

#### **EXTERNAL CAPACITORS**

To assure regulator stability, input and output capacitors are required as shown in the Typical Application Circuit.

#### **OUTPUT CAPACITOR**

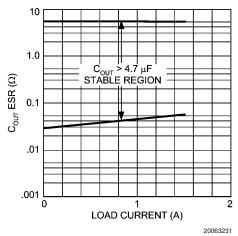

At least  $4.7\mu F$  of output capacitance is required for stability (the amount of capacitance can be increased without limit). The output capacitor must be located less than 1 cm from the output pin of the IC and returned to a clean analog ground. The ESR (equivalent series resistance) of the output capacitor must be within the "stable" range as shown in the graph below over the full operating temperature range for stable operation.

Minimum ESR vs Output Load Current

Tantalum capacitors are recommended for the output as their ESR is ideally suited to the part's requirements and the ESR is very stable over temperature. Aluminum electrolytics are not recommended because their ESR increases very rapidly at temperatures below 10C. Aluminum caps can only be used in applications where lower temperature operation is not required.

A second problem with Al caps is that many have ESR's which are only specified at low frequencies. The typical loop bandwidth of a linear regulator is a few hundred kHz to several MHz. If an Al cap is used for the output cap, it must be one whose ESR is specified at a frequency of 100 kHz or more.

Because the ESR of ceramic capacitors is only a few milli Ohms, they are not suitable for use as output capacitors on LP388X devices. The regulator output can tolerate ceramic capacitance totaling up to 15% of the amount of Tantalum capacitance connected from the output to ground.

#### **OUTPUT "BYPASS" CAPACITORS**

Many designers place small value "bypass" capacitors at various circuit points to reduce noise. Ceramic capacitors in the value range of about 1000pF to 0.1µF placed directly on the output of a PNP or P-FET LDO regulator can cause a loss of phase margin which can result in oscillations, even when a Tantalum output capacitor is in parallel with it. This is not unique to National Semiconductor LDO regulators, it is true of any P-type LDO regulator.

The reason for this is that PNP or P-FET regulators have a higher output impedance (compared to an NPN regulator), which results in a pole-zero pair being formed by every different capacitor connected to the output.

The zero frequency is approximately:

$$F_z = 1 / (2 X \pi X ESR X C)$$

Where ESR is the equivalent series resistance of the capacitor, and C is the value of capacitance.

The pole frequency is:

$$\mathsf{F}_\mathsf{p} = \mathsf{1} \; / \; (\mathsf{2} \; \mathsf{X} \; \pi \; \mathsf{X} \; \mathsf{R}_\mathsf{L} \; \mathsf{X} \; \mathsf{C})$$

Where  $R_L$  is the load resistance connected to the regulator output.

To understand why a small capacitor can reduce phase margin: assume a typical LDO with a bandwidth of 1MHz, which is delivering 0.5A of current from a 2.5V output (which means  $R_{\rm L}$  is 5 Ohms). We then place a .047  $\mu F$  capacitor on the output. This creates a pole whose frequency is:

$$F_p = 1 / (2 X \pi X 5 X .047 X 10E-6) = 677 kHz$$

This pole would add close to 60 degrees of phase lag at the crossover (unity gain) frequency of 1 MHz, which would almost certainly make this regulator oscillate. Depending on the load current, output voltage, and bandwidth, there are usually values of small capacitors which can seriously reduce phase margin. If the capacitors are ceramic, they tend to oscillate more easily because they have very little internal inductance to damp it out. If bypass capacitors are used, it is best to place them near the load and use trace inductance to "decouple" them from the regulator output.

#### **INPUT CAPACITOR**

The input capacitor must be at least 4.7  $\mu$ F, but can be increased without limit. It's purpose is to provide a low source impedance for the regulator input. Ceramic capacitors work best for this, but Tantalums are also very good. There is no ESR limitation on the input capacitor (the lower, the better). Aluminum electrolytics can be used, but their ESR increase very quickly at cold temperatures. They are not recommended for any application where temperatures go below about  $10^{\circ}\text{C}$ .

#### **BIAS CAPACITOR**

The  $0.1\mu F$  capacitor on the bias line can be any good quality capacitor (ceramic is recommended).

#### **BIAS VOLTAGE**

The bias voltage is an external voltage rail required to get gate drive for the N-FET pass transistor. Bias voltage must be in the range of 4.5 - 6V to assure proper operation of the part.

#### **UNDER VOLTAGE LOCKOUT**

The bias voltage is monitored by a circuit which prevents the regulator output from turning on if the bias voltage is below approximately 4V.

#### SHUTDOWN OPERATION

Pulling down the shutdown  $\overline{(S/D)}$  pin will turn-off the regulator. Pin  $\overline{S/D}$  must be actively terminated through a pull-up resistor (10 k $\Omega$  to 100 k $\Omega$ ) for a proper operation. If this pin is driven from a source that actively pulls high and low (such as a CMOS rail to rail comparator), the pull-up resistor is not required. This pin must be tied to Vin if not used.

## Application Hints (Continued)

#### POWER DISSIPATION/HEATSINKING

A heatsink may be required depending on the maximum power dissipation and maximum ambient temperature of the application. Under all possible conditions, the junction temperature must be within the range specified under operating conditions. The total power dissipation of the device is given by:

$$P_D = (V_{IN} - V_{OUT})I_{OUT} + (V_{IN})I_{GND}$$

where I<sub>GND</sub> is the operating ground current of the device.

The maximum allowable temperature rise  $(T_{Rmax})$  depends on the maximum ambient temperature  $(T_{Amax})$  of the application, and the maximum allowable junction temperature  $(T_{Jmax})$ :

$$T_{Rmax} = T_{Jmax} - T_{Amax}$$

The maximum allowable value for junction to ambient Thermal Resistance,  $\theta_{\text{JA}},$  can be calculated using the formula:

$$\theta_{JA} = T_{Rmax} / P_{D}$$

These parts are available in TO-220 and TO-263 packages. The thermal resistance depends on amount of copper area or heat sink, and on air flow. If the maximum allowable value of  $\theta_{JA}$  calculated above is  $\geq 60~^{\circ}\text{C/W}$  for TO-220 package and  $\geq 60~^{\circ}\text{C/W}$  for TO-263 package no heatsink is needed since the package can dissipate enough heat to satisfy these requirements. If the value for allowable  $\theta_{JA}$  falls below these limits, a heat sink is required.

#### **HEATSINKING TO-220 PACKAGE**

The thermal resistance of a TO220 package can be reduced by attaching it to a heat sink or a copper plane on a PC board. If a copper plane is to be used, the values of  $\theta_{\text{JA}}$  will be same as shown in next section for TO263 package.

The heatsink to be used in the application should have a heatsink to ambient thermal resistance,

$$\theta_{HA} \le \theta_{JA} - \theta_{CH} - \theta_{JC}$$

.

In this equation,  $\theta_{CH}$  is the thermal resistance from the case to the surface of the heat sink and  $\theta_{JC}$  is the thermal resistance from the junction to the surface of the case.  $\theta_{JC}$  is about 3°C/W for a TO220 package. The value for  $\theta_{CH}$  depends on method of attachment, insulator, etc.  $\theta_{CH}$  varies between 1.5°C/W to 2.5°C/W. If the exact value is unknown, 2°C/W can be assumed.

#### **HEATSINKING TO-263 PACKAGE**

The TO-263 package uses the copper plane on the PCB as a heatsink. The tab of these packages are soldered to the copper plane for heat sinking. The graph below shows a curve for the  $\theta_{\rm JA}$  of TO-263 package for different copper area sizes, using a typical PCB with 1 ounce copper and no solder mask over the copper area for heat sinking.

FIGURE 1.  $\theta_{JA}$  vs Copper (1 Ounce) Area for TO-263 package

## Application Hints (Continued)

As shown in the graph below, increasing the copper area beyond 1 square inch produces very little improvement. The minimum value for  $\theta_{JA}$  for the TO-263 package mounted to a PCB is 32°C/W.

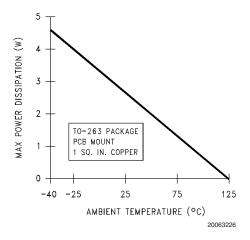

Figure 2 shows the maximum allowable power dissipation for TO-263 packages for different ambient temperatures, assuming  $\theta_{\rm JA}$  is 35°C/W and the maximum junction temperature is 125°C.

FIGURE 2. Maximum Power Dissipation vs Ambient Temperature For TO-263 Package

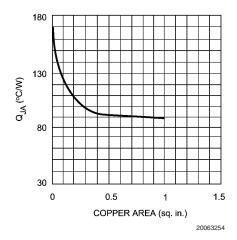

#### **HEATSINKING PSOP PACKAGE**

Heatsinking for the PSOP-8 package is accomplished by allowing heat to flow through the ground slug on the bottom of the package into the copper on the PC board. The heat

slug must be soldered down to a copper plane to get good heat transfer. It can also be connected through vias to internal copper planes. Since the heat slug is at ground potential, traces must not be routed under it which are not at ground potential. Under all possible conditions, the junction temperature must be within the range specified under operating conditions.

Figure 3 shows a curve for the  $\theta_{JA}$  of the PSOP package for different copper area sizes using a typical PCB with one ounce copper in still air.

FIGURE 3.  $\theta_{JA}$  vs. Copper (1 ounce) Area for PSOP Package

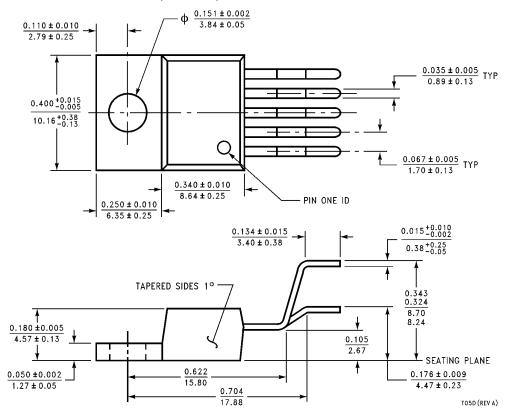

## Physical Dimensions inches (millimeters) unless otherwise noted

TO220 5-lead, Molded, Stagger Bend Package (TO220-5) NS Package Number T05D

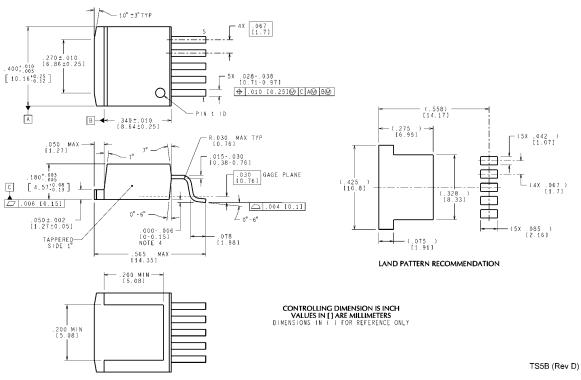

TO263 5-Lead, Molded, Surface Mount Package (TO263-5)

NS Package Number TS5B

11

### Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

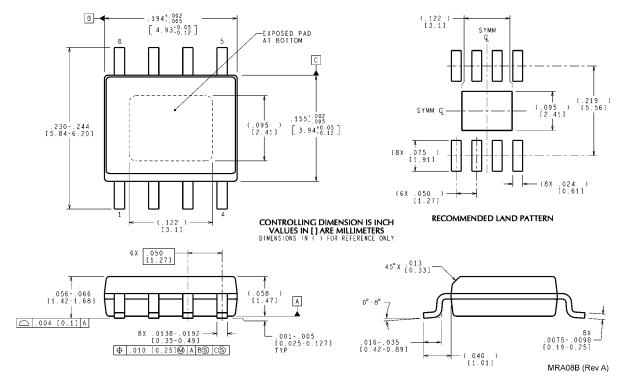

PSOP 8-Lead, Molded, PSOP-2 NS Package Number MRA08B

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.

For the most current product information visit us at www.national.com.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **BANNED SUBSTANCE COMPLIANCE**

National Semiconductor follows the provisions of the Product Stewardship Guide for Customers (CSP-9-111C2) and Banned Substances and Materials of Interest Specification (CSP-9-111S2) for regulatory environmental compliance. Details may be found at: www.national.com/quality/green.

Lead free products are RoHS compliant.

National Semiconductor Americas Customer Support Center

Email: new.feedback@nsc.com Tel: 1-800-272-9959

www.national.com

National Semiconductor Europe Customer Support Center Fax: +49 (0) 180-530 85 86

Email: europe.support@nsc.com

Deutsch Tel: +49 (0) 69 9508 6208

English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

National Semiconductor Asia Pacific Customer Support Center Email: ap.support@nsc.com National Semiconductor Japan Customer Support Center Fax: 81-3-5639-7507 Email: jpn.feedback@nsc.com Tel: 81-3-5639-7560