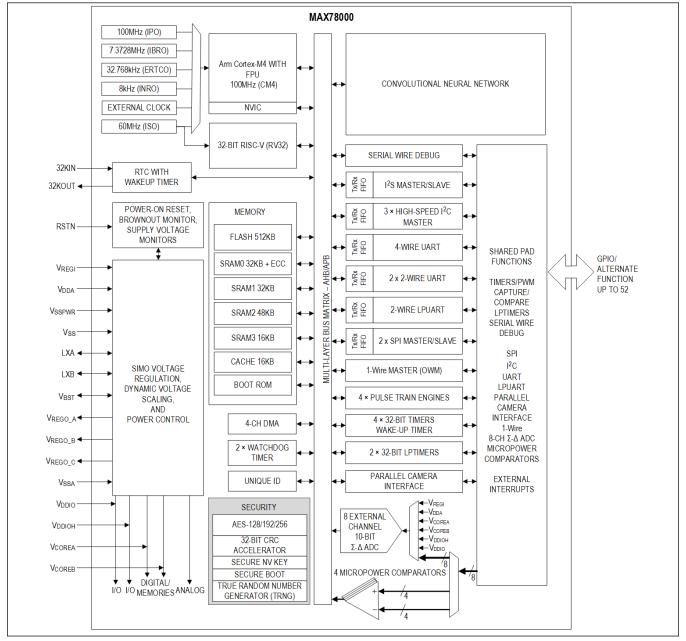

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

## **General Description**

Artificial intelligence (AI) requires extreme computational horsepower, but Maxim is cutting the power cord from AI insights. The MAX78000 is a new breed of AI microcontroller built to enable neural networks to execute at ultra-low power and live at the edge of the IoT. This product combines the most energy-efficient AI processing with Maxim's proven ultra-low power microcontrollers. Our hardware-based convolutional neural network (CNN) accelerator enables battery-powered applications to execute AI inferences while spending only microjoules of energy.

The MAX78000 is an advanced system-on-chip featuring an Arm<sup>®</sup> Cortex<sup>®</sup>-M4 with FPU CPU for efficient system control with an ultra-low-power deep neural network accelerator. The CNN engine has a weight storage memory of 442KB, and can support 1-, 2-, 4-, and 8-bit weights (supporting networks of up to 3.5 million weights). The CNN weight memory is SRAM-based, so AI network updates can be made on the fly. The CNN engine also has 512KB of data memory. The CNN architecture is highly flexible, allowing networks to be trained in conventional toolsets like PyTorch<sup>®</sup> and TensorFlow<sup>®</sup>, then converted for execution on the MAX78000 using tools provided by Maxim.

In addition to the memory in the CNN engine, the MAX78000 has large on-chip system memory for the microcontroller core, with 512KB flash and up to 128KB SRAM. Multiple high-speed and low-power communications interfaces are supported, including  $I^2S$  and a parallel camera interface (PCIF).

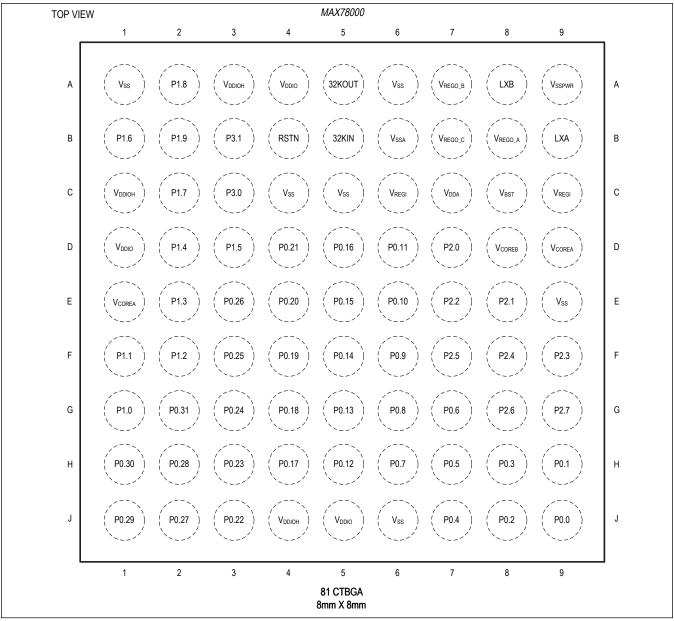

The device is available in a 81-pin CTBGA (8mm x 8mm, 0.8mm pitch) package.

### **Applications**

- Object Detection and Classification

- Audio Processing: Multi-Keyword Recognition, Sound Classification, Noise Cancellation

- Facial Recognition

- Time-Series Data Processing: Heart Rate/Health Signal Analysis, Multi-Sensor Analysis, Predictive Maintenance

### **Benefits and Features**

- Dual Core Ultra-Low-Power Microcontroller

- Arm Cortex-M4 Processor with FPU up to 100MHz

- 512KB Flash and 128KB SRAM

- Optimized Performance with 16KB Instruction Cache

- Optional Error Correction Code (ECC-SEC-DED)

for SRAM

- 32-Bit RISC-V Coprocessor up to 60MHz

- Up to 52 General-Purpose I/O Pins

- 12-Bit Parallel Camera Interface

- One I<sup>2</sup>S Master/Slave for Digital Audio Interface

- Neural Network Accelerator

- Highly Optimized for Deep Convolutional Neural Networks

- · 442k 8-Bit Weight Capacity with 1,2,4,8-Bit Weights

- Programmable Input Image Size up to 1024 x 1024

pixels

- Programmable Network Depth up to 64 Layers

- Programmable per Layer Network Channel Widths up to 1024 Channels

- 1 and 2 Dimensional Convolution Processing

- · Streaming Mode

- Flexibility to Support Other Network Types, Including MLP and Recurrent Neural Networks

- Power Management Maximizes Operating Time for Battery Applications

- Integrated Single-Inductor Multiple-Output (SIMO) Switch-Mode Power Supply (SMPS)

- 2.0V to 3.6V SIMO Supply Voltage Range

- Dynamic Voltage Scaling Minimizes Active Core

Power Consumption

- 22.2µA/MHz While Loop Execution at 3.0V from Cache (CM4 Only)

- Selectable SRAM Retention in Low-Power Modes with Real-Time Clock (RTC) Enabled

- Security and Integrity

- Available Secure Boot

- AES 128/192/256 Hardware Acceleration Engine

- True Random Number Generator (TRNG) Seed Generator

Ordering Information appears at end of data sheet.

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. CoreMark is a registered trademark of the Embedded Microprocessor Benchmark Consortium.

Motorola is a registered trademark of Motorola Trademark Holdings, LLC.

PyTorch is a trademark of Facebook, Inc.

TensorFlow is a trademark of Google, Inc.

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

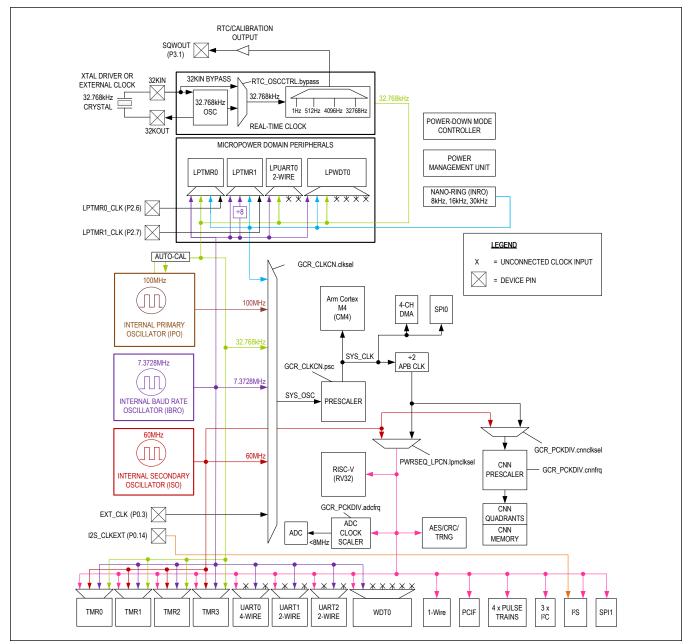

### Simplified Block Diagram

Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### TABLE OF CONTENTS

| General Description                                                  | 1  |

|----------------------------------------------------------------------|----|

| Applications                                                         | 1  |

| Benefits and Features                                                | 1  |

| Simplified Block Diagram                                             | 2  |

| Absolute Maximum Ratings                                             | 7  |

| Package Information                                                  | 7  |

| 81-CTBGA                                                             | 7  |

| Electrical Characteristics                                           | 7  |

| Electrical Characteristics—SPI                                       | 18 |

| Electrical Characteristics—I <sup>2</sup> C                          | 19 |

| Electrical Characteristics—I <sup>2</sup> S                          | 21 |

| Electrical Characteristics—PCIF                                      | 22 |

| Electrical Characteristics—1-Wire Master                             | 22 |

| Pin Configuration                                                    | 27 |

| 81 CTBGA                                                             | 27 |

| Pin Description                                                      | 28 |

| Detailed Description                                                 | 32 |

| Arm Cortex-M4 with FPU Processor and RISC-V RV32 Processor           | 32 |

| Convolutional Neural Network Accelerator (CNN)                       | 32 |

| Memory                                                               | 34 |

| Internal Flash Memory                                                | 34 |

| Internal SRAM                                                        | 34 |

| Comparators                                                          | 34 |

| Dynamic Voltage Scaling (DVS) Controller                             | 34 |

| Clocking Scheme                                                      | 34 |

| General-Purpose I/O and Special Function Pins                        | 35 |

| Parallel Camera Interface (PCIF)                                     | 36 |

| Analog-to-Digital Converter                                          | 36 |

| Single-Inductor Multiple-Output Switch-Mode Power Supply (SIMO SMPS) | 36 |

| Power Management                                                     | 37 |

| Power Management Unit                                                | 37 |

| ACTIVE Mode                                                          | 37 |

| SLEEP Mode                                                           | 37 |

| LOW POWER Mode (LPM).                                                | 37 |

| MICRO POWER Mode (µPM)                                               | 37 |

| STANDBY Mode                                                         | 38 |

| BACKUP Mode                                                          | 38 |

| POWER DOWN Mode (PDM)                                                | 39 |

Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

## TABLE OF CONTENTS (CONTINUED)

| Wakeup Sources                                                                     | . 39 |

|------------------------------------------------------------------------------------|------|

| Real-Time Clock                                                                    | . 39 |

| Programmable Timers                                                                | . 39 |

| 32-Bit Timer/Counter/PWM (TMR, LPTMR)                                              | . 40 |

| Watchdog Timer (WDT)                                                               | . 41 |

| Pulse Train Engine (PT)                                                            | . 41 |

| Serial Peripherals                                                                 | . 41 |

| I <sup>2</sup> C Interface (I2C)                                                   | . 41 |

| I <sup>2</sup> S Interface (I2S)                                                   | . 42 |

| Serial Peripheral Interface (SPI)                                                  | . 42 |

| UART (UART, LPUART)                                                                | . 43 |

| 1-Wire Master (OWM)                                                                | . 44 |

| Standard DMA Controller                                                            | . 44 |

| Security                                                                           | . 44 |

| AES                                                                                | . 44 |

| True Random Number Generator (TRNG) Non-Deterministic Random Bit Generator (NDRBG) | . 44 |

| CRC Module                                                                         | . 44 |

| Bootloader                                                                         | . 45 |

| Secure Boot.                                                                       | . 45 |

| Debug and Development Interface (SWD, JTAG)                                        | . 45 |

| Applications Information                                                           | . 46 |

| Bypass Capacitors                                                                  | . 46 |

| Ordering Information                                                               | . 46 |

| Revision History                                                                   | . 47 |

|                                                                                    |      |

Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### LIST OF FIGURES

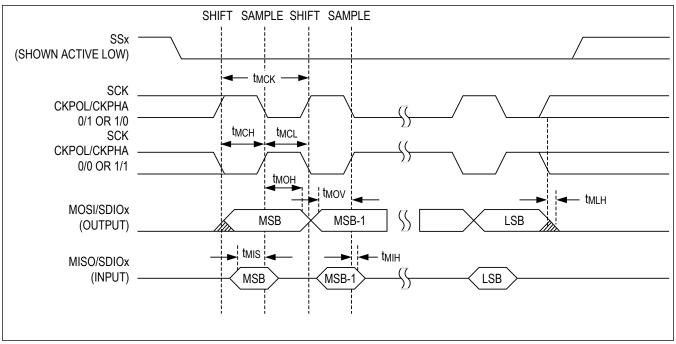

| Figure 1. SPI Master Mode Timing Diagram           | 23 |

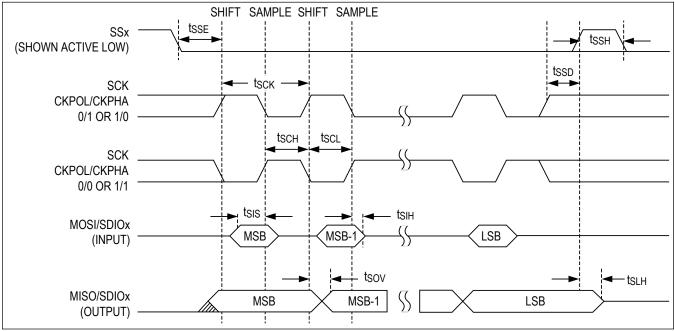

|----------------------------------------------------|----|

| Figure 2. SPI Slave Mode Timing Diagram            | 24 |

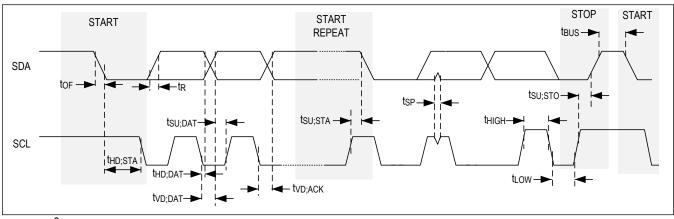

| Figure 3. I <sup>2</sup> C Timing Diagram          | 24 |

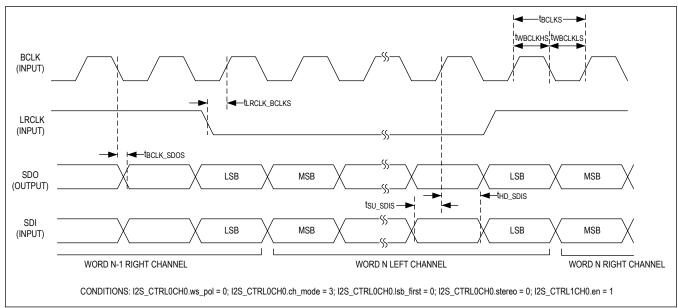

| Figure 4. I <sup>2</sup> S Timing Diagram          | 25 |

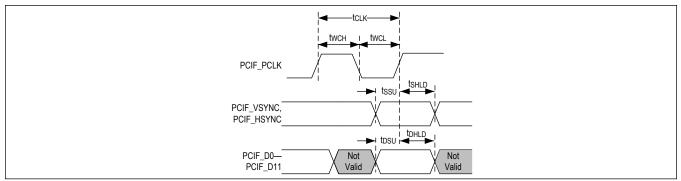

| Figure 5. Parallel Camera Interface Timing Diagram | 25 |

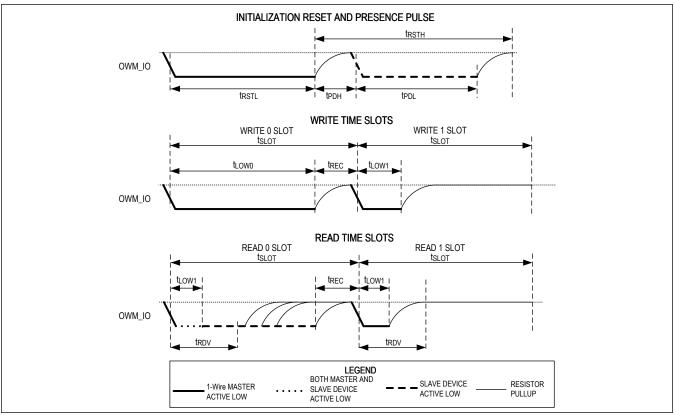

| Figure 6. 1-Wire Master Data Timing Diagram        | 26 |

| Figure 7. Clocking Scheme Diagram                  | 35 |

Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### LIST OF TABLES

| Table 1. BACKUP Mode SRAM Retention           | 38 |

|-----------------------------------------------|----|

| Table 2. Wakeup Sources                       | 39 |

| Table 3. Timer Configuration Options          | 40 |

| Table 4. Watchdog Timer Configuration Options | 41 |

| Table 5. SPI Configuration Options            | 43 |

| Table 6. UART Configuration Options           | 43 |

| Table 7. Common CRC Polynomials.              | 45 |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Absolute Maximum Ratings**

| V <sub>COREA</sub> , V <sub>COREB</sub> | 0.3V to +1.21V                    |

|-----------------------------------------|-----------------------------------|

| V <sub>DDIO</sub>                       | 0.3V to +3.6V                     |

| V <sub>DDIOH</sub>                      | 0.3V to +3.6V                     |

| V <sub>REGI</sub>                       | 0.3V to +3.6V                     |

| V <sub>DDA</sub>                        |                                   |

| GPIO (V <sub>DDIO</sub> )               | 0.3V to V <sub>DDIO</sub> + 0.5V  |

| RSTN, GPIO (V <sub>DDIOH</sub> )        | 0.3V to V <sub>DDIOH</sub> + 0.5V |

| 32KIN, 32KOUT                           | 0.3V to V <sub>DDA</sub> + 0.2V   |

| V <sub>DDIO</sub> Combined Pins (sink)  |                                   |

| V <sub>DDIOH</sub> Combined Pins (sink) |                                   |

| V <sub>SSA</sub>                        |                                   |

| V <sub>SS</sub><br>V <sub>SSPWR</sub><br>Output Current (sink) by any GPIO Pin<br>Output Current (source) by any GPIO Pin<br>Continuous Package Power Dissipation<br>board) $T_A = +70^{\circ}C$ (derate 2<br>+70°C)<br>Operating Temperature Range |                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Operating Temperature Range                                                                                                                                                                                                                         | 40°C to +105°C |

| Storage Temperature Range                                                                                                                                                                                                                           | 65°C to +150°C |

| Soldering Temperature                                                                                                                                                                                                                               | +260°C         |

|                                                                                                                                                                                                                                                     |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 81-CTBGA

| Package Code                           | X8188+3C       |

|----------------------------------------|----------------|

| Outline Number                         | <u>21-0735</u> |

| Land Pattern Number                    | <u>90-0460</u> |

| Thermal Resistance, Four-Layer Board   |                |

| Junction to Ambient (0 <sub>JA</sub> ) | 33.55°C/W      |

| Junction to Case $(\theta_{JC})$       | 6.73°C/W       |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <u>www.maximintegrated.com/</u> <u>thermal-tutorial</u>.

### **Electrical Characteristics**

| PARAMETER                      | SYMBOL             | CONDITIONS | MIN                                    | TYP | MAX  | UNITS |  |  |

|--------------------------------|--------------------|------------|----------------------------------------|-----|------|-------|--|--|

| POWER SUPPLIES                 |                    |            |                                        |     |      |       |  |  |

| Core Input Supply              | V <sub>COREA</sub> | Falling    | V <sub>COREA</sub><br>V <sub>RST</sub> | 1.1 | 1.21 | V     |  |  |

| Vollage A                      | Itage A VCOREA     | 4          | 0.9                                    | 1.1 | 1.21 |       |  |  |

| Core Input Supply<br>Voltage B | V <sub>COREB</sub> | Falling    | V <sub>COREB</sub><br>V <sub>RST</sub> | 1.1 | 1.21 | V     |  |  |

|                                |                    | Rising     | 0.9                                    | 1.1 | 1.21 |       |  |  |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

## **Electrical Characteristics (continued)**

| PARAMETER                            | SYMBOL             | CONDITIONS                  | MIN                                   | TYP  | MAX  | UNITS |

|--------------------------------------|--------------------|-----------------------------|---------------------------------------|------|------|-------|

| Input Supply Voltage,                | V <sub>REGI</sub>  | Falling                     | V <sub>REGI</sub><br>V <sub>RST</sub> | 3.0  | 3.6  | v     |

| Battery                              | _                  | Rising                      | 2.45                                  | 3.0  | 3.6  |       |

| Input Supply Voltage,<br>Analog      | V <sub>DDA</sub>   |                             | 1.71                                  | 1.8  | 1.89 | V     |

| Input Supply Voltage,<br>GPIO        | V <sub>DDIO</sub>  |                             | 1.71                                  | 1.8  | 1.89 | V     |

| Input Supply Voltage,<br>GPIO (High) | V <sub>DDIOH</sub> |                             | 1.71                                  | 3.0  | 3.6  | V     |

|                                      |                    | Monitors V <sub>COREA</sub> |                                       | 0.76 |      |       |

|                                      |                    | Monitors V <sub>COREB</sub> | 0.72                                  | 0.77 |      |       |

| Power-Fail Reset                     | N/                 | Monitors V <sub>DDA</sub>   | 1.58                                  | 1.64 | 1.69 | l v   |

| Voltage                              | V <sub>RST</sub>   | Monitors V <sub>DDIO</sub>  | 1.58                                  | 1.64 | 1.69 | V     |

|                                      |                    | Monitors V <sub>DDIOH</sub> | 1.58                                  | 1.64 | 1.69 | -     |

|                                      |                    | Monitors V <sub>REGI</sub>  | 1.91                                  | 1.98 | 2.08 |       |

| Power-On Reset                       |                    | Monitors V <sub>COREA</sub> |                                       | 0.63 |      | v     |

| Voltage                              | V <sub>POR</sub>   | Monitors V <sub>DDA</sub>   |                                       | 1.25 |      |       |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                 | SYMBOL     | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                            | MIN                                                                                                                                                                                                                                                                                                                                                                               | TYP  | MAX  | UNITS  |  |

|-------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|--|

| V <sub>REGI</sub> Current, ACTIVE<br>Mode |            | Dynamic, IPO enabled, $f_{SYS\_CLK(MAX)} =$<br>100MHz, total current into $V_{REGI}$ pin,<br>$V_{REGI} = 3.0V$ , $V_{COREA} = V_{COREB} =$<br>1.1V, CM4 in Active mode executing<br>CoreMark <sup>®</sup> , RV32 in ACTIVE mode<br>executing While(1), ECC disabled, all<br>CNN quadrants disabled, all CNN<br>memory disabled; inputs tied to $V_{SS}$ ,<br>$V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/sink<br>0mA |                                                                                                                                                                                                                                                                                                                                                                                   | 41.9 |      |        |  |

|                                           | IREGI_DACT | Dynamic, IPO enabled, $f_{SYS\_CLK(MAX)} =$<br>100MHz, total current into $V_{REGI}$ pin,<br>$V_{REGI} = 3.0V$ , $V_{COREA} = V_{COREB} =$<br>1.1V, CM4 and RV32 in ACTIVE mode<br>executing While(1), ECC disabled, all<br>CNN quadrants disabled, all CNN<br>memory disabled; inputs tied to $V_{SS}$ ,<br>$V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/sink<br>0mA                                                 |                                                                                                                                                                                                                                                                                                                                                                                   | 38   |      | μA/MHz |  |

|                                           |            |                                                                                                                                                                                                                                                                                                                                                                                                                       | Dynamic, IPO enabled, $f_{SYS\_CLK(MAX)} =$<br>100MHz, total current into $V_{REGI}$ pin,<br>$V_{REGI} = 3.0V$ , $V_{COREA} = V_{COREB} =$<br>1.1V, CM4 in ACTIVE mode executing<br>While(1), RV32 in SLEEP mode, ECC<br>disabled, all CNN quadrants disabled, all<br>CNN memory disabled; inputs tied to<br>$V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/<br>sink 0mA |      | 22.2 |        |  |

|                                           |            | Dynamic, total current into $V_{REGI}$ pin,<br>$V_{REGI} = 3.0V$ , $V_{COREA} = V_{COREB} =$<br>1.1V, CM4 in SLEEP mode, RV32 in<br>ACTIVE mode running from ISO, ECC<br>disabled, all CNN quadrants disabled, all<br>CNN memory disabled; inputs tied to<br>$V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/<br>sink 0mA                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                   | 22.9 |      |        |  |

|                                           | IREGI_FACT | Fixed, IPO enabled, ISO enabled, total current into $V_{REGI}$ , $V_{REGI}$ = 3.0V, $V_{COREA}$ = $V_{COREB}$ = 1.1V, CM4 in ACTIVE mode 0MHz, RV32 in ACTIVE mode 0MHz, all CNN quadrants disabled, all CNN memory disabled; inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/ sink 0mA                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                   | 744  |      | μΑ     |  |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                      | SYMBOL     | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                           | MIN | TYP  | MAX | UNITS  |

|------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| V <sub>REGI</sub> Current, SLEEP<br>Mode       | IREGI_DSLP | Dynamic, IPO enabled, $f_{SYS\_CLK(MAX)} =$<br>100MHz, ISO enabled, total current into<br>V <sub>REGI</sub> pins, V <sub>REGI</sub> = 3.0V, V <sub>COREA</sub> =<br>V <sub>COREB</sub> = 1.1V, CM4 in SLEEP mode,<br>RV32 in SLEEP mode, ECC disabled, all<br>CNN quadrants disabled, all CNN<br>memory disabled, standard DMA with 2<br>channels active; inputs tied to V <sub>SS</sub> ,<br>V <sub>DDIO</sub> , or V <sub>DDIOH</sub> ; outputs source/sink<br>0mA |     | 22.5 |     | µA/MHz |

|                                                | IREGI_FSLP | Fixed, IPO enabled, ISO enabled, total<br>current into $V_{REGI}$ pins, $V_{REGI}$ = 3.0V,<br>$V_{COREA}$ = $V_{COREB}$ = 1.1V, CM4 in<br>SLEEP mode, RV32 in SLEEP mode,<br>ECC disabled, all CNN quadrants<br>disabled, all CNN memory disabled;<br>inputs tied to $V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ;<br>outputs source/sink 0mA                                                                                                                             |     | 1.5  |     | mA     |

| V <sub>REGI</sub> Current, LOW                 | IREGI_DLP  | Dynamic, ISO enabled, total current into<br>$V_{REGI}$ pins, $V_{REGI}$ = 3.0V, $V_{COREA}$ =<br>$V_{COREB}$ = 1.1V, CM4 powered off, RV32<br>in ACTIVE mode, $f_{SYS}$ _CLK(MAX) =<br>60MHz, all CNN quadrants disabled, all<br>CNN memory disabled; inputs tied to<br>$V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/<br>sink 0mA                                                                                                                         |     | 18.3 |     | µA/MHz |

| POWER Mode                                     | IREGI_FLP  | Fixed, ISO enabled, total current into<br>$V_{REGI}$ pins, $V_{REGI}$ = 3.0V, $V_{COREA}$ =<br>$V_{COREB}$ = 1.1V, CM4 powered off, RV32<br>in ACTIVE mode 0MHz, all CNN<br>quadrants disabled, all CNN memory<br>disabled; inputs tied to $V_{SS}$ , $V_{DDIO}$ , or<br>$V_{DDIOH}$ ; outputs source/sink 0mA                                                                                                                                                       |     | 0.64 |     | mA     |

| V <sub>REGI</sub> Current, MICRO<br>POWER Mode | IREGI_DMP  | Dynamic, ERTCO enabled, IBRO<br>enabled, total current into $V_{REGI}$ pins,<br>$V_{REGI} = 3.0V$ , $V_{COREA} = V_{COREB} =$<br>1.1V, LPUART active, f <sub>LPUART</sub> =<br>32.768kHz, all CNN quadrants disabled,<br>all CNN memory disabled; inputs tied to<br>$V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/<br>sink 0mA                                                                                                                             |     | 230  |     | μΑ     |

| V <sub>REGI</sub> Current,<br>STANDBY Mode     | IREGI_STBY | Fixed, total current into $V_{REGI}$ pins,<br>$V_{REGI} = 3.0V$ , $V_{COREA} = V_{COREB} =$<br>1.1V, all CNN quadrants disabled, all<br>CNN memory disabled; inputs tied to<br>$V_{SS}$ , $V_{DDIO}$ , or $V_{DDIOH}$ ; outputs source/<br>sink 0mA                                                                                                                                                                                                                  |     | 11.3 |     | μΑ     |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                      | SYMBOL                                                                 | COND                                                                   | ITIONS                                                                                                              | MIN    | TYP  | MAX     | UNITS |  |

|------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--------|------|---------|-------|--|

|                                                |                                                                        | Total current into                                                     | All SRAM retained                                                                                                   |        | 11.1 |         |       |  |

|                                                |                                                                        | V <sub>REGI</sub> pins, V <sub>REGI</sub>                              | No SRAM retention                                                                                                   |        | 9    |         |       |  |

|                                                | = 3.0V, V <sub>COREA</sub> = V <sub>COREB</sub> = 1.1V, SRAM0 retained |                                                                        | 9.6                                                                                                                 |        |      |         |       |  |

| V <sub>REGI</sub> Current,                     | IREGI_BK                                                               | RTC disabled, all<br>CNN quadrants                                     | SRAM0 and<br>SRAM1 retained                                                                                         |        | 10.1 |         | μA    |  |

| BACKUP Mode                                    |                                                                        |                                                                        | SRAM0, SRAM1,<br>and SRAM2<br>retained                                                                              |        | 10.6 |         | ·     |  |

| V <sub>REGI</sub> Current, POWER<br>DOWN Mode  | IREGI_PDM                                                              |                                                                        | $V_{REGI} \text{ pins, } V_{REGI} = V_{COREB} = 1.1V; \text{ inputs} \\ 0, \text{ or } V_{DDIOH}; \text{ outputs} $ |        |      |         | μA    |  |

|                                                | V <sub>REGO_A_</sub> IOU<br>T                                          | V <sub>REGO_A</sub> output cur                                         | rent                                                                                                                |        | 5    | 50      |       |  |

| V <sub>REGO_X</sub> Output<br>Current          | V <sub>REGO_B_</sub> IOU<br>T                                          | V <sub>REGO_B</sub> output current                                     |                                                                                                                     |        | 5    | 50      | mA    |  |

|                                                | V <sub>REGO_C_</sub> IOU<br>T                                          | V <sub>REGO_C</sub> output cur                                         | rent                                                                                                                |        | 10   | 100     | ]     |  |

| V <sub>REGO_X</sub> Output<br>Current Combined | V <sub>REGO_X_IOU</sub><br>T_TOT                                       | All three $V_{REGO_X}$ outputs combined                                |                                                                                                                     |        | 20   | 100     | mA    |  |

| V <sub>REGO_X</sub> Output<br>Voltage Range    | V <sub>REGO_</sub> X_RA<br>NGE                                         | $V_{\text{REGI}} \ge V_{\text{REGO}_X} + 200 \text{mV}$                |                                                                                                                     | 0.5    | 1.0  | 1.85    | V     |  |

| V <sub>REGO_X</sub> Efficiency                 | V <sub>REGO_X_EFF</sub>                                                | V <sub>REGI</sub> = 2.7V, V <sub>REGO_X</sub> = 1.1 V, load =<br>30mA  |                                                                                                                     |        | 90   |         | %     |  |

| SLEEP Mode Resume<br>Time                      | t <sub>SLP_ON</sub>                                                    | Time from power mo of first user instructio                            |                                                                                                                     |        | 0.67 |         | μs    |  |

| LOW-POWER Mode<br>Resume Time                  | <sup>t</sup> LP_ON                                                     | Time from power mo<br>of first user instructio                         |                                                                                                                     |        | 9.5  |         | μs    |  |

| MICROPOWER Mode<br>Resume Time                 | t <sub>MP_ON</sub>                                                     | Time from power mo of first user instructio                            |                                                                                                                     |        | 31   |         | us    |  |

| STANDBY Mode<br>Resume Time                    | <sup>t</sup> STBY_ON                                                   | -                                                                      | Time from power mode exit to execution of first user instruction                                                    |        | 35   |         | μs    |  |

| BACKUP Mode Resume<br>Time                     | <sup>t</sup> вкu_on                                                    | Time from power mode exit to execution of first user instruction       |                                                                                                                     |        | 0.14 |         | ms    |  |

| POWER-DOWN Mode<br>Resume Time                 | <sup>t</sup> PDM_ON                                                    | Time from power mo<br>of first user instructio<br>bootloader execution |                                                                                                                     | 5      |      | ms      |       |  |

| CLOCKS                                         |                                                                        |                                                                        |                                                                                                                     |        |      |         |       |  |

| System Clock<br>Frequency                      | <sup>f</sup> sys_clk                                                   |                                                                        |                                                                                                                     | 0.0625 |      | 100,000 | kHz   |  |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

## **Electrical Characteristics (continued)**

| PARAMETER                                              | SYMBOL               | COND                                                                            | ITIONS                              | MIN | TYP                            | MAX | UNITS  |

|--------------------------------------------------------|----------------------|---------------------------------------------------------------------------------|-------------------------------------|-----|--------------------------------|-----|--------|

| System Clock Period                                    | <sup>t</sup> sys_clk |                                                                                 |                                     |     | 1/<br><sup>f</sup> sys_cl<br>K |     | ns     |

| Internal Primary<br>Oscillator (IPO)                   | fIPO                 |                                                                                 |                                     |     | 100                            |     | MHz    |

| Internal Secondary<br>Oscillator (ISO)                 | fiso                 |                                                                                 |                                     |     | 60                             |     | MHz    |

| Internal Baud Rate<br>Oscillator (IBRO)                | fibro                |                                                                                 |                                     |     | 7.3728                         |     | MHz    |

|                                                        |                      | 8kHz selected                                                                   |                                     |     | 8                              |     |        |

| Internal Nano-Ring<br>Oscillator (INRO)                | finro                | 16kHz selected                                                                  |                                     |     | 16                             |     | kHz    |

|                                                        |                      | 30kHz selected                                                                  |                                     | 32  |                                |     |        |

| External RTC Oscillator<br>(ERTCO)                     | <sup>f</sup> ERTCO   | 32kHz watch crystal, $C_L = 6pF$ , ESR <<br>90k $\Omega$ , $C_0 \le 2pF$ 32.768 |                                     |     | kHz                            |     |        |

| RTC Operating Current                                  | I <sub>RTC</sub>     | All power modes, RT                                                             | C enabled                           |     | 0.3                            |     | μA     |

| RTC Power-Up Time                                      | <sup>t</sup> RTC_ON  |                                                                                 |                                     |     | 250                            |     | ms     |

| External I <sup>2</sup> S Clock Input<br>Frequency     | fext_i2s_clk         | I2S_CLKEXT selecte                                                              | ed                                  |     |                                | 25  | MHz    |

| External System Clock<br>Input Frequency               | fext_clk             | EXT_CLK selected                                                                |                                     |     |                                | 80  | MHz    |

| External Low Power<br>Timer 1 Clock Input<br>Frequency | fEXT_LPTMR1_<br>CLK  | LPTMR1_CLK selec                                                                | ted                                 |     |                                | 8   | MHz    |

| External Low Power<br>Timer 2 Clock Input<br>Frequency | fext_lptmr2_<br>CLK  | LPTMR2_CLK selec                                                                | LPTMR2_CLK selected                 |     |                                | 8   | MHz    |

| CONVOLUTIONAL NEU                                      | RAL NETWORK          |                                                                                 |                                     |     |                                |     |        |

| CNN Active Energy                                      | E <sub>J_CNN</sub>   | Max power<br>network, random<br>data, and random<br>mask configuration          | x16 Quadrant 0, 1, 2, and 3 enabled |     | 4.02                           |     | pJ/MAC |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                          | SYMBOL                | COND                                                                   | ITIONS                                                                                                                                                                      | MIN | ТҮР   | MAX | UNITS |

|----------------------------------------------------|-----------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

|                                                    | ICOREA_CNN_<br>MNISTA | MNIST Standard<br>dataset, optimized<br>network                        | x16 Quadrant 0<br>enabled; x16<br>Quadrant 1, 2, and<br>3 powered down<br>and isolated                                                                                      |     | 10.1  |     |       |

|                                                    | ICOREA_CNN_<br>MNISTB |                                                                        | x16 Quadrant 0, 1,<br>2, and 3 enabled                                                                                                                                      |     | 29    |     |       |

|                                                    | ICOREA_CNNM<br>PRA    |                                                                        | x16 Quadrant 0<br>enabled; x16<br>Quadrant 1, 2, and<br>3 powered down<br>and isolated                                                                                      |     | 31.7  |     |       |

|                                                    | ICOREA_CNNM<br>PRB    | Max power<br>network, random<br>data, and random<br>mask configuration | x16 Quadrant 0, 1,<br>2, and 3 enabled.<br>External power<br>supply must be<br>used for V <sub>COREA</sub><br>since the on-board<br>SIMO will not<br>supply above<br>100mA. |     | 118   |     | mA    |

|                                                    | ICOREA_CNNM<br>PA     |                                                                        | x16 Quadrant 0<br>enabled; x16<br>Quadrant 1, 2, and<br>3 powered down<br>and isolated                                                                                      |     | 38.5  |     |       |

|                                                    | n                     | Max power<br>network, data,<br>mask configuration                      | x16 Quadrant 0, 1,<br>2, and 3 enabled.<br>External power<br>supply must be<br>used for VCOREA<br>since the on-board<br>SIMO will not<br>supply above<br>100mA.             |     | 146   |     |       |

| V <sub>REGI</sub> Mask Memory<br>Retention Current | IREGI_CNNMR           | V <sub>COREB</sub> = 1.0V                                              | x16 Quadrant 0<br>only; x16 Quadrant<br>1, 2, and 3<br>powered down and<br>isolated                                                                                         |     | 6.625 |     | μΑ    |

|                                                    |                       |                                                                        | x16 Quadrant 0, 1,<br>2, and 3 enabled                                                                                                                                      |     | 26.5  |     |       |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                                  | SYMBOL               | COND                                                                                                                   | ITIONS                                                                                 | MIN                         | TYP                         | MAX                         | UNITS |

|------------------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|-------|

| V <sub>REGI</sub> CNN Inactive<br>Current                  | IREGI_CNNIA          | CNN enabled/<br>inactive, clocks<br>disabled                                                                           | x16 Quadrant 0<br>enabled; x16<br>Quadrant 1, 2, and<br>3 powered down<br>and isolated |                             | 264                         |                             | μΑ    |

|                                                            |                      |                                                                                                                        | x16 Quadrant 0, 1,<br>2, and 3 enabled                                                 |                             | 790.4                       |                             |       |

| GENERAL-PURPOSE I/C                                        | )                    | •                                                                                                                      | •                                                                                      |                             |                             |                             |       |

| Input Low Voltage for All<br>GPIO Except P3.0 and<br>P3.1  | VIL_VDDIO            | P3.0 and P3.1 can<br>only use V <sub>DDIOH</sub><br>as I/O supply and<br>cannot use V <sub>DDIO</sub><br>as I/O supply | V <sub>DDIO</sub> selected as<br>I/O supply                                            |                             |                             | 0.3 ×<br>V <sub>DDIO</sub>  | V     |

| Input Low Voltage for All GPIO                             | VIL_VDDIOH           | V <sub>DDIOH</sub> selected as                                                                                         | I/O supply                                                                             |                             |                             | 0.3 ×<br>V <sub>DDIOH</sub> | V     |

| Input Low Voltage for<br>RSTN                              | V <sub>IL_RSTN</sub> |                                                                                                                        |                                                                                        |                             | 0.5 x<br>V <sub>DDIOH</sub> |                             | V     |

| Input High Voltage for<br>All GPIO Except P3.0<br>and P3.1 | VIH_VDDIO            | P3.0 and P3.1 can<br>only use V <sub>DDIOH</sub><br>as I/O supply and<br>cannot use V <sub>DDIO</sub><br>as I/O supply | V <sub>DDIO</sub> selected as<br>I/O supply                                            | 0.7 ×<br>V <sub>DDIO</sub>  |                             |                             | V     |

| Input High Voltage for<br>All GPIO                         | VIH_VDDIOH           | V <sub>DDIOH</sub> selected as                                                                                         | I/O supply                                                                             | 0.7 ×<br>V <sub>DDIOH</sub> |                             |                             | V     |

| Input High Voltage for RSTN                                | VIH_RSTN             |                                                                                                                        |                                                                                        |                             | 0.5 x<br>V <sub>DDIOH</sub> |                             | V     |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                                  | SYMBOL     | COND                                                                                                                       | ITIONS                                                                                                                                                                            | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------|------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| Output Low Voltage for<br>All GPIO Except P3.0<br>and P3.1 |            | /<br>=<br>0                                                                                                                | $V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 00, I_{OL} = 1\text{mA} \\ \end{cases}$                              |     | 0.2 | 0.4 |       |

|                                                            | No         | P3.0 and P3.1 can<br>only use V <sub>DDIOH</sub>                                                                           | $\label{eq:vdb} \begin{array}{l} V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 01, I_{OL} = 2\text{mA} \end{array}$ |     | 0.2 | 0.4 | - V   |

|                                                            |            | as I/O supply                                                                                                              | $V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 10, I_{OL} = 4\text{mA} \\ \end{array}$                              |     | 0.2 | 0.4 |       |

|                                                            |            |                                                                                                                            | $\label{eq:vdb} \begin{array}{l} V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 11, I_{OL} = 8\text{mA} \end{array}$ |     | 0.2 | 0.4 |       |

|                                                            |            | V <sub>DDIOH</sub> selected as<br>= 1.71V, GPIOn_DS<br>= 1mA                                                               |                                                                                                                                                                                   |     | 0.2 | 0.4 |       |

| Output Low Voltage for                                     |            | V <sub>DDIOH</sub> selected as<br>= 1.71V, GPIOn_DS<br>= 2mA                                                               | I/O supply, V <sub>DDIOH</sub><br>_SEL[1:0] = 01, I <sub>OL</sub>                                                                                                                 |     | 0.2 | 0.4 |       |

| Ali gpio                                                   | Vol_vddioh | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 10, I <sub>OL</sub><br>= 4mA |                                                                                                                                                                                   |     | 0.2 | 0.4 |       |

|                                                            |            | V <sub>DDIOH</sub> selected as<br>= 1.71V, GPIOn_DS<br>= 8mA                                                               |                                                                                                                                                                                   |     | 0.2 | 0.4 |       |

| Combined IOL, All GPIO                                     | IOL_TOTAL  |                                                                                                                            |                                                                                                                                                                                   |     |     | 48  | mA    |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                                                                  | SYMBOL                 | COND                                                                                                                                                                                 | ITIONS                                                                                                                                                                               | MIN                         | TYP | MAX  | UNITS |

|----------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|------|-------|

|                                                                            |                        |                                                                                                                                                                                      | $\label{eq:VDDIO} \begin{array}{l} V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 00, I_{OL} = -1\text{mA} \end{array}$ | V <sub>DDIO</sub> -<br>0.4  |     |      |       |

| Output High Voltage for<br>All GPIO Except P3.0 V <sub>C</sub><br>and P3.1 | Manager                | P3.0 and P3.1 can<br>only use V <sub>DDIOH</sub>                                                                                                                                     | $\label{eq:VDDIO} \begin{array}{l} V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 01, I_{OL} = -2\text{mA} \end{array}$ | V <sub>DDIO</sub> -<br>0.4  |     |      | - V   |

|                                                                            | Voh_vddio              | as I/O supply and<br>cannot use V <sub>DDIO</sub><br>as I/O supply                                                                                                                   | $V_{DDIO} \text{ selected as} $ I/O supply, V_DDIO<br>= 1.71V,<br>GPIOn_DS_SEL[1:<br>0] = 10, I_{OL} = -4mA                                                                          | V <sub>DDIO</sub> -<br>0.4  |     |      |       |

|                                                                            |                        | $\label{eq:VDDIO} \begin{array}{l} V_{DDIO} \text{ selected as} \\ I/O \text{ supply, } V_{DDIO} \\ = 1.71V, \\ \text{GPIOn_DS_SEL[1:} \\ 0] = 11, I_{OL} = -8\text{mA} \end{array}$ | V <sub>DDIO</sub> -<br>0.4                                                                                                                                                           |                             |     |      |       |

|                                                                            |                        | V <sub>DDIOH</sub> selected as<br>= 1.71V, GPIOn_DS<br>= -1mA                                                                                                                        | I/O supply, V <sub>DDIOH</sub><br>_SEL[1:0] = 00, I <sub>OL</sub>                                                                                                                    | V <sub>DDIOH</sub><br>- 0.4 |     |      |       |

| Output High Voltage for<br>All GPIO Except P3.0                            |                        | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 01, I <sub>OL</sub><br>= -2mA                                                          |                                                                                                                                                                                      | V <sub>DDIOH</sub><br>- 0.4 |     |      | v     |

| and P3.1                                                                   | VOH_VDDIOH             | V <sub>DDIOH</sub> selected as I/O supply, V <sub>DDIOH</sub><br>= 1.71V, GPIOn_DS_SEL[1:0] = 10, I <sub>OL</sub><br>= -4mA                                                          |                                                                                                                                                                                      | V <sub>DDIOH</sub><br>- 0.4 |     |      | v     |

|                                                                            |                        | V <sub>DDIOH</sub> selected as<br>= 1.71V, GPIOn_DS<br>= -8mA                                                                                                                        | I/O supply, V <sub>DDIOH</sub><br>_SEL[1:0] = 11, I <sub>OL</sub>                                                                                                                    | V <sub>DDIOH</sub><br>- 0.4 |     |      |       |

| Output High Voltage for P3.0 and P3.1                                      | V <sub>OH_VDDIOH</sub> | V <sub>DDIOH</sub> = 1.71V, GF<br>fixed at 00, I <sub>OL</sub> = -1r                                                                                                                 |                                                                                                                                                                                      | V <sub>DDIOH</sub><br>- 0.4 |     |      | V     |

| Combined I <sub>OH</sub> , All GPIO                                        | IOH_TOTAL              |                                                                                                                                                                                      |                                                                                                                                                                                      |                             |     | -48  | mA    |

| Input Hysteresis<br>(Schmitt)                                              | V <sub>IHYS</sub>      |                                                                                                                                                                                      |                                                                                                                                                                                      |                             | 300 |      | mV    |

| Input Leakage Current<br>Low                                               | IIL                    |                                                                                                                                                                                      | <sub>DIOH</sub> = 3.6V, V <sub>DDIOH</sub><br>Iy, V <sub>IN</sub> = 0V, internal                                                                                                     | -100                        |     | +100 | nA    |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

| PARAMETER                     | SYMBOL                                                      | CONE                                                                                        | DITIONS                                                                                | MIN                        | TYP                 | MAX                 | UNITS |

|-------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------|---------------------|---------------------|-------|

|                               | IIН                                                         | V <sub>DDIO</sub> = 1.89V, V <sub>DI</sub><br>selected as I/O supp<br>internal pulldown dis | DIOH = 3.6V, V <sub>DDIOH</sub><br>Dly, V <sub>IN</sub> = 3.6V,<br>sabled              | -800                       |                     | +800                | nA    |

| Input Leakage Current<br>High | I <sub>OFF</sub>                                            | V <sub>DDIO</sub> = 0V, V <sub>DDIO</sub><br>selected as I/O supp                           | <sub>H</sub> = 0V, V <sub>DDIO</sub><br>bly, V <sub>IN</sub> < 1.89V                   | -1                         |                     | +1                  |       |

|                               | I <sub>IH3V</sub>                                           | V <sub>DDIO</sub> = V <sub>DDIOH</sub> =<br>selected as I/O supp                            | 1.71V, V <sub>DDIO</sub><br>bly, V <sub>IN</sub> = 3.6V                                | -2                         |                     | +2                  | μA    |

| Input Pullup Resistor<br>RSTN | R <sub>PU_R</sub>                                           | Pullup to V <sub>DDIOH</sub>                                                                |                                                                                        |                            | 25                  |                     | kΩ    |

| Input Pullup/Pulldown         | R <sub>PU1</sub>                                            | Normal resistance,                                                                          | P1M = 0                                                                                |                            | 25                  |                     | kΩ    |

| Resistor for All GPIO         | R <sub>PU2</sub>                                            | Highest resistance,                                                                         | P1M = 1                                                                                |                            | 1                   |                     | MΩ    |

| ADC (SIGMA-DELTA)             |                                                             |                                                                                             |                                                                                        |                            |                     |                     |       |

| Resolution                    |                                                             |                                                                                             |                                                                                        |                            | 10                  |                     | Bits  |

| ADC Clock Rate                | <b>f</b> ACLK                                               |                                                                                             |                                                                                        | 0.1                        |                     | 8                   | MHz   |

| ADC Clock Period              | t <sub>ACLK</sub>                                           |                                                                                             |                                                                                        |                            | 1/f <sub>ACLK</sub> |                     | μs    |

|                               |                                                             | AIN[7:0],<br>ADC_DIVSEL =<br>[00],<br>ADC_CH_SEL =<br>[7:0]                                 | REF_SEL = 0,<br>INPUT_SCALE = 0                                                        | V <sub>SSA</sub> +<br>0.05 |                     | V <sub>BG</sub>     |       |

| Input Voltage Range           | Maria                                                       | AIN[7:0],<br>ADC_DIVSEL =<br>[01],<br>ADC_CH_SEL =<br>[7:0]                                 | REF_SCALE = 0,<br>INPUT_SCALE = 0                                                      | V <sub>SSA</sub> +<br>0.05 |                     | 2 x V <sub>BG</sub> | V     |

| input voltage Kange           | Vain                                                        | AIN[7:0],<br>ADC_DIVSEL =<br>[10],<br>ADC_CH_SEL =<br>[7:0]                                 | REF_SCALE = 0,<br>INPUT_SCALE =<br>0, V <sub>DDIOH</sub> selected<br>as the I/O supply | V <sub>SSA</sub> +<br>0.05 |                     | V <sub>DDIOH</sub>  | v     |

|                               | AIN[7:0],<br>ADC_DIVSEL =<br>[11],<br>ADC_CH_SEL =<br>[7:0] | REF_SEL = 0,<br>INPUT_SCALE =<br>0, V <sub>DDIOH</sub> selected<br>as the I/O supply        | V <sub>SSA</sub> +<br>0.05                                                             |                            | V <sub>DDIOH</sub>  |                     |       |

| Input Impedance               | R <sub>AIN</sub>                                            |                                                                                             |                                                                                        |                            | 30                  |                     | kΩ    |

| Analog Input                  |                                                             | Fixed capacitance to                                                                        | o V <sub>SSA</sub>                                                                     |                            | 1                   |                     | pF    |

| Capacitance                   | C <sub>AIN</sub>                                            | Dynamically switched capacitance 250                                                        |                                                                                        |                            | fF                  |                     |       |

| Integral Nonlinearity         | INL                                                         | Measured at +25°C                                                                           |                                                                                        |                            |                     | ±2                  | LSb   |

| Differential Nonlinearity     | DNL                                                         | Measured at +25°C                                                                           |                                                                                        |                            |                     | ±1                  | LSb   |

| Offset Error                  | V <sub>OS</sub>                                             |                                                                                             |                                                                                        |                            | ±1                  |                     | LSb   |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics (continued)**

(Limits are 100% tested at  $T_A = +25^{\circ}$ C and  $T_A = +105^{\circ}$ C. TYP specifications are provided for  $T_A = +25^{\circ}$ C. Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested. Specifications to the minimum operating temperature are guaranteed by design and are not production tested. GPIO are only tested at  $T_A = +105^{\circ}$ C.)

| PARAMETER                          | SYMBOL               | CONDITIONS                                                  | MIN | TYP  | MAX  | UNITS             |

|------------------------------------|----------------------|-------------------------------------------------------------|-----|------|------|-------------------|

| ADC Active Current                 | I <sub>ADC</sub>     | ADC active, reference buffer enabled, input buffer disabled |     | 102  |      | μΑ                |

| ADC Setup Time                     | tADC_SU              | Any power-up of ADC clock or ADC bias to CpuAdcStart        |     |      | 10   | μs                |

| ADC Output Latency                 | t <sub>ADC</sub>     |                                                             |     | 1067 |      | t <sub>ACLK</sub> |

| ADC Sample Rate                    | f <sub>ADC</sub>     |                                                             |     |      | 7.8  | ksps              |

| ADC Input Leakage                  | IADC_LEAK            | ADC inactive or channel not selected                        |     | 10   |      | nA                |

| Full-Scale Voltage                 | V <sub>FS</sub>      | ADC code = 0x3FF                                            |     | 1.2  |      | V                 |

| Bandgap Temperature<br>Coefficient | V <sub>TEMPCO</sub>  | Box method                                                  |     | 30   |      | ppm               |

| COMPARATORS                        |                      |                                                             |     |      |      |                   |

| Input Offset Voltage               | VOFFSET              |                                                             |     | ±1   |      | mV                |

|                                    | V <sub>HYST</sub>    | AINCOMPHYST[1:0] = 00                                       |     | ±23  |      |                   |

| land the stars at                  |                      | AINCOMPHYST[1:0] = 01                                       |     | ±50  |      |                   |

| Input Hysteresis                   |                      | AINCOMPHYST[1:0] = 10                                       |     | ±2   |      | - mV              |

|                                    |                      | AINCOMPHYST[1:0] = 11                                       |     | ±7   |      | 1                 |

| Input Voltage Range                | VIN_CMP              | Common-mode range                                           | 0.6 |      | 1.35 | V                 |

| FLASH MEMORY                       | •                    |                                                             |     |      |      |                   |

| Floop Frond Time                   | t <sub>M_ERASE</sub> | Mass erase                                                  |     | 20   |      |                   |

| Flash Erase Time                   | <sup>t</sup> P_ERASE | Page erase                                                  |     | 20   |      | ms                |

| Flash Programming<br>Time per Word | t <sub>PROG</sub>    | 32-bit programming mode, f <sub>FLC_CLK</sub> = 1MHz        |     | 42   |      | μs                |

| Flash Endurance                    |                      |                                                             | 10  |      |      | kcycles           |

| Data Retention                     | t <sub>RET</sub>     | T <sub>A</sub> = +105°C                                     | 10  |      |      | years             |

### **Electrical Characteristics—SPI**

| PARAMETER                                      | SYMBOL                              | CONDITIONS                                                                         | MIN                  | TYP                 | MAX | UNITS |

|------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------|----------------------|---------------------|-----|-------|

| MASTER MODE                                    |                                     |                                                                                    |                      |                     |     |       |

| SPI Master Operating<br>Frequency for SPI0     | <sup>f</sup> MCK0                   | f <sub>SYS_CLK</sub> = 100MHz, f <sub>MCK0(MAX)</sub> =<br>f <sub>SYS_CLK</sub> /2 |                      |                     | 50  | MHz   |

| SPI Master Operating<br>Frequency for SPI1     | fMCK1                               | f <sub>SYS_CLK</sub> = 100MHz, f <sub>MCK1(MAX)</sub> =<br>f <sub>SYS_CLK</sub> /4 |                      |                     | 25  | MHz   |

| SPI Master SCK Period                          | t <sub>MCKX</sub>                   |                                                                                    |                      | 1/f <sub>MCKX</sub> |     | ns    |

| SCK Output Pulse-<br>Width High/Low            | t <sub>MCH</sub> , t <sub>MCL</sub> |                                                                                    | t <sub>MCKX</sub> /2 |                     |     | ns    |

| MOSI Output Hold Time<br>After SCK Sample Edge | <sup>t</sup> мон                    |                                                                                    | t <sub>MCX</sub> /2  |                     |     | ns    |

# Artificial Intelligence Microcontroller with Ultra-Low-Power Convolutional Neural Network Accelerator

### **Electrical Characteristics—SPI (continued)**

(Timing specifications are guaranteed by design and not production tested.)

| PARAMETER                                                | SYMBOL           | CONDITIONS | MIN TYP              | MAX | UNITS |

|----------------------------------------------------------|------------------|------------|----------------------|-----|-------|

| MOSI Output Valid to<br>Sample Edge                      | t <sub>MOV</sub> |            | t <sub>MCKX</sub> /2 |     | ns    |

| MOSI Output Hold Time<br>After SCK Low Idle              | t <sub>MLH</sub> |            | t <sub>MCKX</sub> /2 |     | ns    |

| MISO Input Valid to<br>SCK Sample Edge<br>Setup          | t <sub>MIS</sub> |            | 5                    |     | ns    |

| MISO Input to SCK<br>Sample Edge Hold                    | t <sub>MIH</sub> |            | t <sub>MCKX</sub> /2 |     | ns    |

| SLAVE MODE                                               |                  |            |                      |     |       |

| SPI Slave Operating<br>Frequency                         | fsck             |            |                      | 50  | MHz   |

| SPI Slave SCK Period                                     | t <sub>SCK</sub> |            | 1/f <sub>SCK</sub>   |     | ns    |