# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

### FEATURES AND BENEFITS

- AEC-Q100 Grade 0 qualified

- Internal buck pre-regulator followed by LDO outputs

- 5.5 to 36 V VIN operating range (50 V maximum); for start/stop, cold crank, and load dump requirements

- 2.2 MHz constant on-time buck regulator

- Valley current sensing achieves shortest buck on-times

- 50 V absolute maximum input voltage for surges

- 5.5 to 46 V input voltage range

- -40°C to 150°C junction temperature range

- Power-on reset (NPOR pin) with adjustable rising delay

- 5 V (V5P pin) internal low dropout tracking linear regulator with both overcurrent foldback and short-to-battery protection

- 5 V (V5 pin) internal low dropout linear regulator with overcurrent foldback protection

### Continued on the next page...

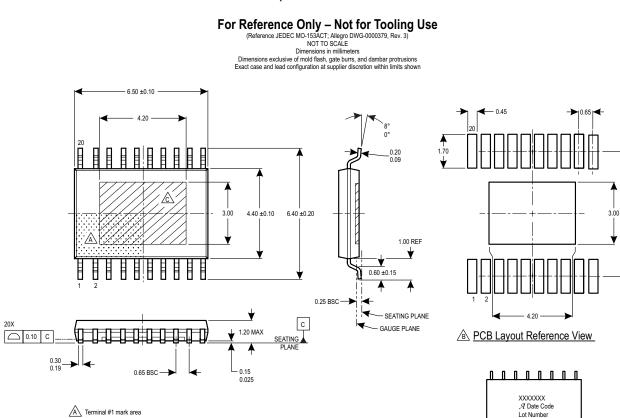

## PACKAGE: 20-pin TSSOP with exposed thermal pad (suffix LP)

### DESCRIPTION

The A4405 is an automotive power management IC that uses a high frequency constant on-time 5.45 V pre-regulator to supply two internal 5 V linear regulators and a 3.3 V linear DMOS driver. Designed to supply CAN and microprocessor power supplies in high temperature environments, the A4405 is ideal for under hood applications. Efficient operation is achieved by using a buck pre-regulator to efficiently drop the input voltage before supplying the linear regulators; this reduces power dissipation and increases overall regulator efficiency.

The switching regulator is capable of operating at a nominal switching frequency of 2.2 MHz. The high switching frequency enables the customer to select low value inductors and ceramic capacitors while avoiding EMI in the AM frequency band.

Protection features include undervoltage lockout and thermal shutdown. The V5P output is protected from short-to-battery events. In case of a shorted load, all regulators feature overcurrent protection. The A4405 also features power-on-reset with *Continued on the next page*...

### **APPLICATIONS:**

- Automotive Control Modules, such as:

- Electronic power steering (EPS)

- Transmission control (TCU)

- Antilock braking (ABS)

- Emissions control

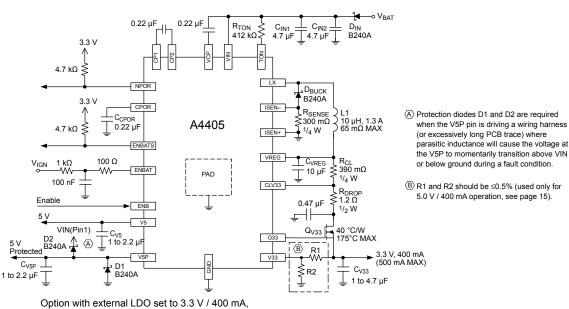

## Typical Application Circuit

(Add R1 and R2 and remove R<sub>DROP</sub> to set external LDO to 5.0 V / 400 mA)

A4405-DS, Rev. 4 MCO-0000658

### FEATURES AND BENEFITS (CONTINUED)

- 3.3 V (V33 pin) external linear regulator DMOS driver with a programmable current limit (up to 500 mA) and overcurrent foldback protection

- Logic enable input (ENB pin)

- Ignition enable input (ENBAT pin)

- Ignition status indicator (ENBATS pin)

- Buck pulse-by-pulse overcurrent protection

- Buck LX short circuit protection (latched)

ABSOLUTE MAXIMUM RATINGS [1]

- Missing asynchronous diode protection (latched)

- Switcher (VREG pin), 3.3 V (V33 pin), and charge pump (VCP pin) undervoltage lockout protection (UVLO)

- Thermal shutdown protection (TSD)

## DESCRIPTION (CONTINUED)

adjustable delay for the microprocessor output.

The A4405 is supplied in a low profile (1.2 mm max) 20-pin TSSOP package with exposed thermal pad (suffix LP). The package is lead (Pb) free with 100% matte-tin leadframe plating

### **SELECTION GUIDE**

| Part Number  | Packing                     |  |

|--------------|-----------------------------|--|

| A4405KLPTR-T | 4000 pieces per 13-in. reel |  |

| Characteristic                | Symbol                                | Notes      | Rating                       | Unit |

|-------------------------------|---------------------------------------|------------|------------------------------|------|

| VIN Pin                       | V <sub>IN</sub>                       |            | -0.3 to 50                   | V    |

| LX Pin                        | N/                                    |            | -0.3 to 50                   | V    |

|                               | V <sub>LX</sub>                       | t < 250 ns | -1.5                         | V    |

| VCP, CP1, and CP2 Pins        | V <sub>VCP</sub> , V <sub>CPx</sub>   |            | –0.3 to 60                   | V    |

| ISEN– Pin                     | V <sub>ISEN-</sub>                    |            | –0.5 to 1                    | V    |

| ISEN+ Pin                     | V <sub>ISEN+</sub>                    |            | -0.5 to 0.5                  | V    |

| ENBAT Pin <sup>[2]</sup>      | V <sub>ENBAT</sub>                    |            | -0.3                         | V    |

| ENBAT Pin Current             | I <sub>ENBAT</sub>                    |            | -50 to 50                    | mA   |

| VREG Pin                      | V <sub>VREG</sub>                     |            | –0.3 to 8                    | V    |

| V33 Pin                       | V <sub>V33</sub>                      |            | –0.3 to 7                    | V    |

| G33 Pin <sup>[3]</sup>        | V <sub>G33</sub>                      |            | -0.3                         | V    |

| CLV33 Pin                     | V <sub>CLV33</sub>                    |            | –0.3 to 10                   | V    |

| V5P Pin                       | V <sub>V5P</sub>                      |            | –0.3 to V <sub>IN</sub> +0.5 | V    |

| V5 Pin                        | V <sub>V5</sub>                       |            | –0.3 to 7                    | V    |

| TON Pin                       | V <sub>TON</sub>                      |            | –0.3 to 50                   | V    |

| NPOR and CPOR Pins            | V <sub>xPOR</sub>                     |            | –0.3 to 7                    | V    |

| ENB and ENBATS Pins           | V <sub>EN</sub> , V <sub>ENBATS</sub> |            | –0.3 to 7                    | V    |

| Operating Ambient Temperature | T <sub>A</sub>                        | Range K    | -40 to 135                   | °C   |

| Junction Temperature          | T <sub>J</sub> (max)                  |            | -40 to 150                   | °C   |

| Storage Temperature Range     | T <sub>stg</sub>                      |            | -40 to 150                   | °C   |

<sup>[1]</sup>Absolute maximum ratings are limiting values that should not be exceeded under worst case operating conditions or damage may occur.

<sup>[2]</sup> The ENBAT pin is internally clamped to approximately 8.5 V due to an ESD protection device.

<sup>[3]</sup> The G33 pin is internally clamped by an ESD protection device. Clamp voltages range from 10 V (min) to 15 V (max).

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions*                                 | Value | Unit |

|----------------------------|-----------------|--------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{\theta JA}$ | Estimated on 4-layer PCB based on JEDEC standard | 32    | °C/W |

\*Additional thermal information available on the Allegro website.

# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

### **Table of Contents**

| Specifications                                 | 2 |

|------------------------------------------------|---|

| Functional Block Diagram                       |   |

| Pin-out Diagram and Terminal List              |   |

| Electrical Characteristics                     |   |

| Characteristic Performance                     |   |

| Functional Description1                        |   |

| Basic Operation1                               |   |

| Overcurrent Protection1                        |   |

| Dropout Mode1                                  | 1 |

| Soft Start1                                    | 1 |

| Buck Pulse Width (t <sub>ON</sub> )1           |   |

| ISEN+ and ISEN                                 |   |

| Switcher Overcurrent Protection1               | 2 |

| LX Short Circuit Protection1                   | 2 |

| Missing Asynchronous Diode Protection          |   |

| Thermal Shutdown1                              | 3 |

| Power-On Reset (NPOR)1                         | 3 |

| V5 Regulator                                   | 4 |

| V5P Tracking Regulator1                        | 4 |

| 3.3 V Linear Regulator1                        | 5 |

| Charge Pump                                    |   |

| ENBAT1                                         | 5 |

| ENBATS1                                        | 5 |

| ENB1                                           | 5 |

| Timing Diagrams1                               | 6 |

| Application Information1                       | 8 |

| Switcher On-Time and Switching Frequency 1     |   |

| Low Voltage Operation1                         |   |

| Inductor Selection1                            | 8 |

| Output Capacitor1                              | 9 |

| Input Capacitor1                               |   |

| Rectification Diode1                           |   |

| External MOSFET Selection1                     | 9 |

| 3.3 V Dropping Resistor (R <sub>DROP</sub> ) 2 | 0 |

| PCB Layout2                                    |   |

| Application Circuit Performance2               | 3 |

| Package Outline Drawing2                       | 6 |

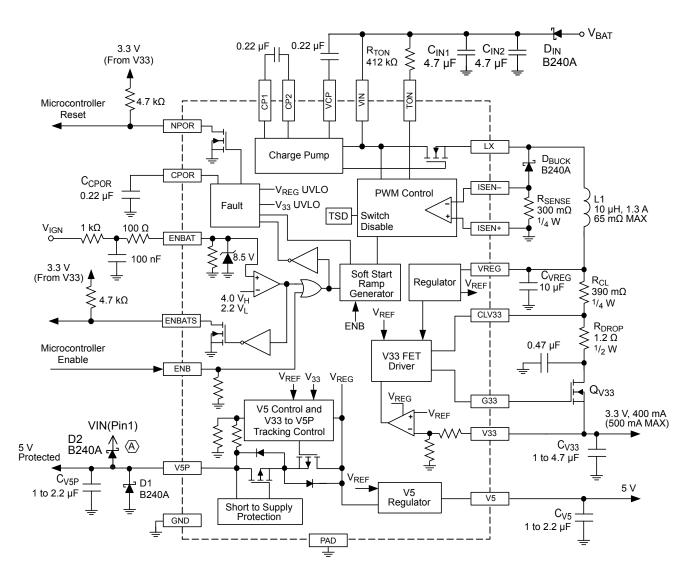

FUNCTIONAL BLOCK DIAGRAM

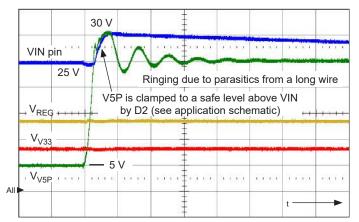

Protection diodes D1 and D2 are required when the V5P pin is driving a wiring harness (or excessively long PCB trace) where parasitic inductance will cause the voltage at the V5P to momentarily transition above VIN or below ground during a fault condition.

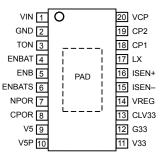

### **Pinout Diagram**

#### **Terminal List Table**

| Name   | Number | Function                                                                |

|--------|--------|-------------------------------------------------------------------------|

| CLV33  | 13     | 3.3 V current sense and limit input                                     |

| CP1    | 18     | Charge pump capacitor terminal 1                                        |

| CP2    | 19     | Charge pump capacitor terminal 2                                        |

| CPOR   | 8      | NPOR delay programming pin                                              |

| ENB    | 5      | Logic enable input from the microcontroller                             |

| ENBAT  | 4      | Ignition enable input from the key or switch via a 1 $k\Omega$ resistor |

| ENBATS | 6      | Open drain ignition status output                                       |

| G33    | 12     | Gate driver to the external MOSFET for 3.3 V regulation                 |

| GND    | 2      | Ground terminal                                                         |

| ISEN-  | 15     | Buck negative current sense pin, sense resistor and diode node          |

| ISEN+  | 16     | Buck positive current sense pin, sense resistor and ground node         |

| LX     | 17     | Buck regulator switching node                                           |

| NPOR   | 7      | Active low, open-drain fault indication output                          |

| PAD    | _      | Exposed pad for enhanced thermal dissipation                            |

| TON    | 3      | Buck regulator on-time programming pin                                  |

| V33    | 11     | 3.3 V regulator output                                                  |

| V5     | 9      | 5 V regulator output                                                    |

| V5P    | 10     | 5 V tracking, protected regulator output                                |

| VCP    | 20     | Charge pump reservoir capacitor terminal                                |

| VIN    | 1      | Input voltage                                                           |

| VREG   | 14     | Buck regulator DC output, and input to the 3.3 V external regulator     |

### **ELECTRICAL CHARACTERISTICS:** Valid at $-40^{\circ}C \le T_J \le 150^{\circ}C$ , 5.5 V $\le V_{IN} \le 36$ V, unless otherwise specified

| Characteristic                             | Symbol                   | Test Conditions                                                                                                                                                                                                                    | Min. | Тур. | Max. | Unit |

|--------------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| GENERAL                                    | ·                        |                                                                                                                                                                                                                                    |      |      |      |      |

| Function Input Voltage                     | V <sub>IN(f)</sub>       | Device functional, parameters not guaranteed                                                                                                                                                                                       | 5.5  | -    | 46   | V    |

| Operating Input Voltage                    | V <sub>IN(op)</sub>      |                                                                                                                                                                                                                                    | 5.5  | 13.5 | 36   | V    |

| Supply Quiescent Current [1]               | Ι <sub>Q</sub>           | $V_{\rm IN}$ = 13.5 V, $V_{\rm IGN}$ > $V_{\rm IGN(H)}$ or $V_{\rm ENB}$ > $V_{\rm ENB(H)},$ no load on VREG                                                                                                                       | -    | 10   | _    | mA   |

| Supply Quiescent Current <sup>[1]</sup>    | I <sub>Q(SLEEP)</sub>    | $\rm V_{IN}$ = 13.5 V, $\rm V_{IGN}$ < $\rm V_{IGN(L)}, ~V_{ENB}$ < $\rm V_{ENB(L)}, ~no$ load on VREG                                                                                                                             | -    | _    | 10   | μA   |

| BUCK REGULATOR                             | ·                        |                                                                                                                                                                                                                                    |      |      |      |      |

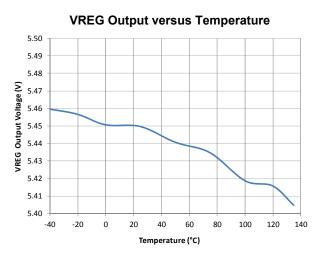

|                                            |                          | ENB = high, $V_{INSW(L)} < V_{IN} < 27 V$ ,<br>25 mA < I <sub>VREG</sub> < 600 mA                                                                                                                                                  | 5.25 | 5.45 | 5.60 | V    |

| Switcher Output                            | V <sub>VREG</sub>        | $\label{eq:entropy} \begin{split} \text{ENB} &= \text{high} \text{, } \text{V}_{\text{INSW}(\text{NOM})} \leq \text{V}_{\text{IN}} \leq 27 \text{ V}, \\ \text{25 mA} \leq \text{I}_{\text{VREG}} \leq 750 \text{ mA} \end{split}$ | 5.30 | 5.45 | 5.60 | V    |

|                                            |                          | ENB = high , 5.5 V < V <sub>IN</sub> < 6.5 V, LX 100% on, 100 mA < I <sub>VREG</sub> < 600 mA                                                                                                                                      | 5.15 | -    | 6.46 | V    |

|                                            | t <sub>SW(L)</sub>       | $V_{INSW(L)} < V_{IN} < V_{INSW(NOM)}$ , $R_{TON} = 412 \text{ k}\Omega$                                                                                                                                                           | _    | 1.6  | _    | μs   |

| Switcher Period <sup>[2]</sup>             | t <sub>SW(NOM)</sub>     | $V_{INSW(NOM)} < V_{IN} < V_{INSW(H)}$ , $R_{TON} = 412 \text{ k}\Omega$                                                                                                                                                           | _    | 450  | _    | ns   |

|                                            | t <sub>SW(H)</sub>       | $V_{\rm INSW(H)}$ < $V_{\rm IN}$ < 36 V, $R_{\rm TON}$ = 412 k $\Omega$                                                                                                                                                            | _    | 1.6  | _    | μs   |

| Switcher On-Time                           |                          | $V_{IN}$ = 7 V, $R_{TON}$ = 412 k $\Omega$                                                                                                                                                                                         | 1070 | 1335 | 1600 | ns   |

|                                            | +                        | V <sub>IN</sub> = 13.5 V, R <sub>TON</sub> = 412 kΩ                                                                                                                                                                                | 160  | 200  | 240  | ns   |

|                                            | t <sub>ON</sub>          | V <sub>IN</sub> = 27 V, R <sub>TON</sub> = 412 kΩ                                                                                                                                                                                  | 80   | 118  | 135  | ns   |

|                                            |                          | $V_{IN}$ = 35 V, $R_{TON}$ = 412 k $\Omega$                                                                                                                                                                                        | 220  | 275  | 330  | ns   |

|                                            | V <sub>INSW(L)</sub>     | $V_{\text{IN}}$ falling, $t_{\text{SW}}$ changes from $t_{\text{SW(L)}}$ to 100% duty cycle                                                                                                                                        | 5.9  | 6.2  | 6.5  | V    |

| Switcher Period V <sub>IN</sub> Threshold  | V <sub>INSW(NOM)</sub>   | $V_{\text{IN}}$ falling, $t_{\text{SW}}$ changes from $t_{\text{SW}(\text{NOM})}$ to $t_{\text{SW}(\text{L})}$                                                                                                                     | 7.7  | 8.3  | 8.9  | V    |

|                                            | V <sub>INSW(H)</sub>     | $V_{\text{IN}}$ rising, $t_{\text{SW}}$ changes from $t_{\text{SW}(\text{NOM})}$ to $t_{\text{SW}(\text{H})}$                                                                                                                      | 28   | 31   | 34   | V    |

| Switcher Deried V Hystoresia               |                          | $V_{\text{INSW}(L)}$ and $V_{\text{INSW}(NOM)}$ comparators, relative to the $V_{\text{IN}}$ voltage that initially caused the switcher period to change                                                                           | -    | 250  | _    | mV   |

| Switcher Period V <sub>IN</sub> Hysteresis | V <sub>INSW(HYS)</sub>   | $V_{\text{INSW}(\text{H})}$ comparator, relative to the $V_{\text{IN}}$ voltage that initially caused the switcher period to change                                                                                                | -    | 700  | _    | mV   |

| Ruck Switch On Registeres                  | Б                        | T <sub>J</sub> = 25°C, I <sub>DS</sub> = 0.1 A                                                                                                                                                                                     | _    | 275  | 300  | mΩ   |

| Buck Switch On-Resistance                  | R <sub>DS(on)</sub>      | T <sub>J</sub> = 150°C, I <sub>DS</sub> = 0.1 A                                                                                                                                                                                    | _    | 400  | 470  | mΩ   |

| Minimum On-Time                            | t <sub>on(min)</sub>     | V <sub>IN</sub> = 13.5 V, R <sub>TON</sub> = 49.9 kΩ                                                                                                                                                                               | _    | 65   | 90   | ns   |

| Minimum Off-Time                           | t <sub>off(min)</sub>    | V <sub>IN</sub> = 13.5 V                                                                                                                                                                                                           | 85   | 110  | 140  | ns   |

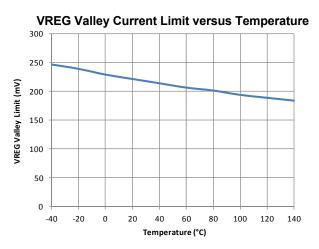

| ISEN Voltage Threshold                     | V <sub>ISEN</sub>        | V <sub>ISEN+</sub> – V <sub>ISEN-</sub>                                                                                                                                                                                            | 175  | 220  | 265  | mV   |

| VREG Valley Current Limit                  | I <sub>LIM(VALLEY)</sub> | $R_{SENSE}$ = 300 m $\Omega$ , $V_{IN}$ > $V_{INSW(L)}$                                                                                                                                                                            | _    | 733  | _    | mA   |

| VREG Peak Current Limit                    | I <sub>LIM(PEAK)</sub>   |                                                                                                                                                                                                                                    | 2.5  | 5.0  | _    | A    |

Continued on the next page ...

| ELECTRICAL CHARACTERISTICS (continued): Valid at -40°C | $S \leq T_J \leq 150^{\circ}C$ , 5.5 V $\leq V_{IN} \leq 36$ V, unless otherwise specified |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------|

|--------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Characteristic                         | Symbol                  | Symbol Test Conditions                                                                               |       | Тур.        | Max.  | Unit |

|----------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------|-------|-------------|-------|------|

| 5 V LINEAR REGULATORS                  |                         | ·                                                                                                    |       |             |       |      |

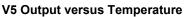

| V5 Accuracy and Load Regulation        | V <sub>V5</sub>         | 10 mA < I <sub>V5</sub> < 215 mA, V <sub>VREG</sub> ≥ 5.25 V                                         | 4.9   | 5.0         | 5.1   | V    |

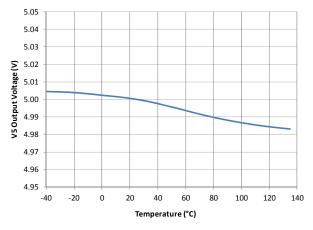

| V5P Accuracy and Load Regulation       | V <sub>V5P</sub>        | 10 mA < I <sub>V5P</sub> < 270 mA, V <sub>VREG</sub> ≥ 5.25 V                                        | 4.9   | 5.0         | 5.1   | V    |

| V5P/V33 Tracking Ratio                 | V5P <sub>track</sub>    | V <sub>V5P</sub> / V <sub>V33</sub>                                                                  | 1.507 | 1.515       | 1.523 | _    |

| V5P/V33 Tracking Accuracy              | Err <sub>V5Ptrack</sub> | 2.69 V < V <sub>V33</sub> < 3.37 V, I <sub>V5P</sub> = 75 mA,<br>5.5 V < V <sub>IN</sub> < 27 V      | -0.5  | -           | +0.5  | %    |

| LINEAR REGULATOR AND FET D             | RIVER                   |                                                                                                      |       | · · · · · · |       |      |

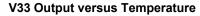

| V33 Accuracy                           | Err <sub>V33</sub>      | 10 mA < I <sub>V33</sub> < 500 mA                                                                    | 3.23  | 3.30        | 3.37  | V    |

| G33 Source Current <sup>[1]</sup>      | I <sub>G33(SRC)</sub>   | V <sub>V33</sub> = 3.0 V, V <sub>G33</sub> = V <sub>G33(MAX)</sub> – 1 V                             | -175  | -250        | -400  | μA   |

| G33 Sink Current <sup>[1]</sup>        | I <sub>G33(SINK)</sub>  | V <sub>V33</sub> = 3.6 V, V <sub>G33</sub> = 6 V                                                     | 0.5   | 3           | _     | mA   |

| G33 Maximum Voltage                    | V <sub>G33(MAX)</sub>   | V <sub>V33</sub> = 3.0 V                                                                             | 9     | _           | 15    | V    |

| G33 Minimum Voltage                    | V <sub>G33(MIN)</sub>   | V <sub>V33</sub> = 3.6 V                                                                             | _     | 0.7         | 1.0   | V    |

| G33 Output Impedance <sup>[2]</sup>    | R <sub>OUT</sub>        |                                                                                                      | _     | 175         | _     | Ω    |

| External FET Gate Capacitance [2]      | C <sub>ISS</sub>        |                                                                                                      | 250   | _           | 5200  | pF   |

| CHARGE PUMP (VCP PIN)                  |                         |                                                                                                      |       |             |       |      |

| Output Voltage                         | ΔV <sub>VCP</sub>       | V <sub>VCP</sub> - V <sub>IN</sub>                                                                   | 4.1   | 6.6         | _     | V    |

| Switching Frequency                    | f <sub>SW(CP)</sub>     |                                                                                                      | _     | 100         | _     | kHz  |

| LOGIC ENABLE INPUT (ENB PIN)           |                         |                                                                                                      |       |             |       |      |

|                                        | V <sub>ENB(H)</sub>     | V <sub>ENB</sub> rising                                                                              | _     | _           | 2.0   | V    |

| ENB Logic Input Threshold              | V <sub>ENB(L)</sub>     | V <sub>ENB</sub> falling                                                                             | 0.8   | -           | _     | V    |

| ENB Logic Input Current <sup>[1]</sup> | I <sub>ENB(IN)</sub>    | V <sub>ENB</sub> = 3.3 V                                                                             | _     | -           | 100   | μA   |

| ENB Pull-Down Resistance               | R <sub>ENB</sub>        |                                                                                                      | _     | 60          | _     | kΩ   |

| IGNITION ENABLE INPUT (ENBA            |                         | TS PINS)                                                                                             |       |             |       |      |

| ENBAT and ENBATS Thresholds            | V <sub>IGN(H)</sub>     | $V_{IGN}$ rising via a 1 k $\Omega$ series resistance, measure $V_{IGN}$ when $I_Q$ occurs           | -     | _           | 4.0   | V    |

| ENDAT and ENDATS THRESHOLDS            | V <sub>IGN(L)</sub>     | $V_{IGN}$ falling via a 1 k $\Omega$ series resistance, measure $V_{IGN}$ when $I_{Q(SLEEP)}$ occurs | 2.2   | -           | _     | V    |

|                                        |                         | $V_{IGN}$ = 5.5 V via a 1 k $\Omega$ series resistance                                               | -     | 50          | 100   | μA   |

| ENBAT Input Current <sup>[1]</sup>     | I <sub>ENBAT(IN)</sub>  | $V_{IGN}$ = 0.8 V via a 1 k $\Omega$ series resistance                                               | 0.5   | -           | 5     | μA   |

| ENBAT Input Resistance                 | R <sub>ENBAT</sub>      |                                                                                                      | -     | 650         | _     | kΩ   |

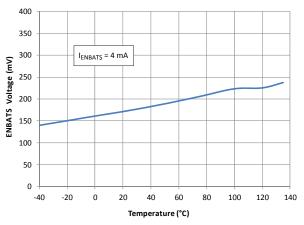

| IGNITION STATUS OUTPUT (ENB            |                         |                                                                                                      |       |             |       |      |

| ENBATS Output Voltage                  | V <sub>ENBATS(L)</sub>  | I <sub>ENBATS</sub> = 4 mA                                                                           | -     | _           | 400   | mV   |

| ENBATS Leakage Current <sup>[1]</sup>  | IENBATS                 | V <sub>ENBATS</sub> = 3.3 V                                                                          | _     | _           | 1     | μA   |

| ENBATS Turn-On Delay                   | t <sub>ENBATS</sub>     | Sleep mode to V <sub>ENBATS</sub> = 3.3 V                                                            | _     | 11          | _     | ms   |

Continued on the next page ...

### **ELECTRICAL CHARACTERISTICS** (continued) Valid at $-40^{\circ}C \le T_J \le 150^{\circ}C$ , 5.5 V $\le V_{IN} \le 36$ V; unless otherwise specified

| Characteristic                          | Symbol                  | Test Conditions                                                                                                                                                                                                   | Min. | Тур. | Max. | Unit |

|-----------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| NPOR PIN OUTPUT AND TIMING              |                         |                                                                                                                                                                                                                   | · ·  |      | ·    |      |

| NPOR Power-Up Delay                     | t <sub>NPOR</sub>       | C <sub>POR</sub> = 0.22 μF                                                                                                                                                                                        | -    | 20   | _    | ms   |

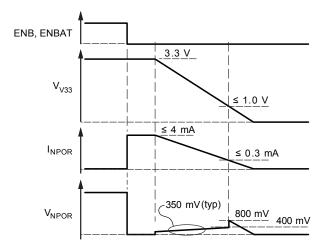

|                                         |                         | $\label{eq:stars} \begin{array}{l} ENB = high \; or \; ENBAT = high, \\ V_{VREG} < V_{REGNPOR(L)} \; or \; V_{V33} < V_{33NPOR(L)}, \\ I_{NPOR} \leq 4 \; mA \end{array}$                                         | _    | _    | 400  | mV   |

| NPOR Output Voltage                     | V <sub>NPOR(L)</sub>    | ENBAT = low, ENB transitioning to low,<br>$V_{VREG} = 5.45 \text{ V}, I_{NPOR} \le 0.3 \text{ mA},$<br>$0.8 \text{ V} < V_{V33} < \text{Err}_{V33}, 0^{\circ}\text{C} \le \text{T}_{J} \le 150^{\circ}\text{C}$   | _    | 350  | 800  | mV   |

|                                         |                         | ENBAT = low, ENB transitioning to low,<br>$V_{VREG} = 5.45 \text{ V}, I_{NPOR} \le 0.3 \text{ mA},$<br>$1.0 \text{ V} < V_{V33} < \text{Err}_{V33}, -40^{\circ}\text{C} \le \text{T}_{J} \le 150^{\circ}\text{C}$ | _    | _    | 800  | mV   |

| NPOR Leakage Current <sup>[1]</sup>     | I <sub>NPOR(LEAK)</sub> | $V_{NPOR} = 3.3 V$                                                                                                                                                                                                | -    | -    | 1    | μA   |

| CPOR PIN CHARACTERISTICS                |                         |                                                                                                                                                                                                                   |      |      |      |      |

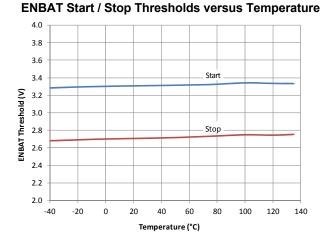

| CPOR Charge Current <sup>[1]</sup>      | I <sub>CPOR(SRC)</sub>  |                                                                                                                                                                                                                   | -    | -13  | _    | μA   |

| CPOR Threshold                          | V <sub>CPOR(H)</sub>    | V <sub>CPOR</sub> rising                                                                                                                                                                                          | 1.0  | 1.2  | 1.4  | V    |

| VREG PIN SOFT START TIMING              |                         |                                                                                                                                                                                                                   |      |      |      |      |

| Soft Start                              | t <sub>SS</sub>         |                                                                                                                                                                                                                   | -    | 10   | -    | ms   |

| PROTECTION CIRCUITRY                    |                         |                                                                                                                                                                                                                   |      |      |      |      |

| VREG Pin NPOR Thresholds                | V <sub>REGNPOR(H)</sub> | V <sub>VREG</sub> rising, NPOR transitioning to high                                                                                                                                                              | 4.80 | 5.00 | 5.20 | V    |

| VREG PIN NPOR Thresholds                | V <sub>REGNPOR(L)</sub> | V <sub>VREG</sub> falling, NPOR transitioning to low                                                                                                                                                              | 4.75 | 4.94 | 5.14 | V    |

| VREG Pin NPOR Hysteresis                | V <sub>REG(HYS)</sub>   |                                                                                                                                                                                                                   | -    | 60   | -    | mV   |

| V33 Regulator NPOR Thresholds           | V <sub>33NPOR(H)</sub>  | $V_{V33}$ rising, NPOR transitioning to high                                                                                                                                                                      | 2.80 | 2.95 | 3.10 | V    |

| V55 Regulator NFOR Thresholds           | V <sub>33NPOR(L)</sub>  | $V_{V33}$ falling, NPOR transitioning to low                                                                                                                                                                      | 2.69 | 2.83 | 2.97 | V    |

| V33 Regulator NPOR Hysteresis           | V <sub>33(HYS)</sub>    |                                                                                                                                                                                                                   | -    | 125  | _    | mV   |

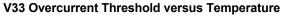

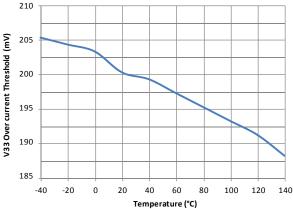

| V33 Regulator Overcurrent Threshold     | V <sub>33OCP</sub>      | V <sub>VREG</sub> – V <sub>CLV33</sub>                                                                                                                                                                            | 175  | 200  | 245  | mV   |

| V33 Regulator Current Limit             | I <sub>V33ILIM</sub>    | R <sub>CL</sub> = 620 mΩ                                                                                                                                                                                          | -    | 323  | -    | mA   |

| V33 Regulator Foldback Threshold        | V <sub>33IFB</sub>      | $V_{V33} = 0 V, V_{VREG} - V_{CLV33}$                                                                                                                                                                             | 35   | 55   | 75   | mV   |

| V33 Regulator Foldback<br>Current Limit | I <sub>V33IFB</sub>     | R <sub>CL</sub> = 620 mΩ                                                                                                                                                                                          | -    | 89   | _    | mA   |

| V5P Pin Current Limit <sup>[1]</sup>    | I <sub>V5PILIM</sub>    | $V_{V5P} = 5 V$                                                                                                                                                                                                   | -300 | -405 | _    | mA   |

| V5P Pin Foldback Current <sup>[1]</sup> | I <sub>V5PIFB</sub>     | $V_{V5P} = 0 V$                                                                                                                                                                                                   | -70  | -110 | -150 | mA   |

| V5 Pin Current Limit <sup>[1]</sup>     | I <sub>V5ILIM</sub>     | V <sub>V5</sub> = 5 V                                                                                                                                                                                             | -230 | -315 | _    | mA   |

| V5 Pin Foldback Current <sup>[1]</sup>  | I <sub>V5IFB</sub>      | V <sub>V5</sub> = 0 V                                                                                                                                                                                             | -84  | -105 | -163 | mA   |

| Thermal Shutdown Threshold              | T <sub>JTSD</sub>       | T <sub>J</sub> rising                                                                                                                                                                                             | 155  | 170  | _    | °C   |

| Thermal Shutdown Hysteresis             | T <sub>JTSD(HYS)</sub>  |                                                                                                                                                                                                                   | _    | 20   | _    | °C   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of (sourcing) the specified pin.

<sup>[2]</sup> Determined by design and systems characterization. Not production tested.

### CHARACTERISTIC PERFORMANCE

1,400 1,300

1,200

1,100

1,100 1,000 1,100 1,100 1,100 1,100 1,100 1,100 1,100 1,100 1,100 1,100 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,0000 1,0000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,000 1,00

ton

400

300

200

100

0

-40

-20

0

20

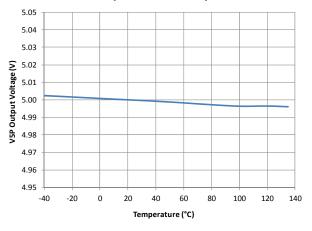

V5P Output versus Temperature

40

Temperature (°C)

60

ton versus Temperature

V<sub>IN</sub> = 7.5 V

V<sub>IN</sub> = 35 V

V<sub>IN</sub> = 13.5 V

V<sub>IN</sub> = 27 V

120

140

80

100

# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

### **CPOR Charging Current versus Temperature**

ENB Start / Stop Thresholds versus Temperature

ENBATS (Low) Voltage versus Temperature

## FUNCTIONAL DESCRIPTION

### **Basic Operation**

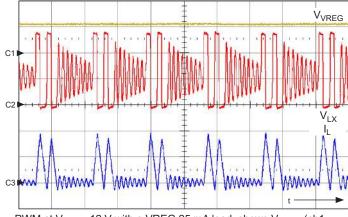

The A4405 contains a fixed on-time, buck switching pre-regulator with valley sensing current mode control, two integrated 5 V linear regulators, and an N-channel FET driver for a 3.3 V linear regulator. The constant on-time (COT) converter maintains a constant output frequency because the on-time is inversely proportional to the supply voltage. As the input voltage decreases the on-time is increased, which maintains a relatively constant period. Valley mode current control allows the converter to achieve very short on-times because current is measured during the off-time.

With very low input voltages the buck switch maintains a 100% duty cycle. This turns the buck switch on 100% of the time (no switching) and allows the regulator to operate in dropout mode.

The device is enabled via logic level ENB or high voltage ignition ENBAT input. When the device is enabled the converter starts up under the control of an internal soft start routine. The two enable inputs are logically ORed together internally so either of the inputs can be used to enable the device.

Under light load conditions the switch enters pulse-skipping mode to ensure regulation is maintained. In order to maintain a wide input voltage range the switcher period is extended when the minimum on- or off-time is reached, or when the input supply is at either end of its range.

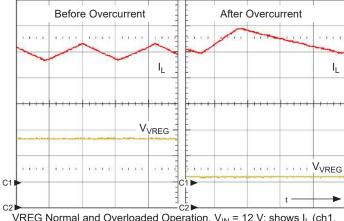

### **Overcurrent Protection**

The A4405 features overcurrent protection on all regulators including the VREG pre-regulator. The buck switch current limit is determined by the selection of the sense resistor at the ISENx pins. Output current is also monitored on the 5VP and 5V linear regulators, and if shorted the outputs fold back. The external FET driver has a current limit tap that can be used with a sense resistor to trigger a current limit based on an external resistor and trip voltage.

### **Dropout Mode**

The topology of a COT timer is ideal for systems that have high input voltages. Because current is measured during the off-time, very short on-times can be achieved. With low input voltages the switcher must maintain very short off-times. To prevent the switcher from reaching its minimum off-time, the switcher is designed to enter a 100% duty cycle mode. This causes the switcher to stop acting as a buck switch. The voltage at VREG then becomes the simply the supply voltage minus the drop across the buck switch and inductor. In this mode the maximum available current may be lower, depending on ambient temperature and supply voltage, while in dropout mode.

### Soft Start

An internal ramp generator and counter allow the output voltage to ramp-up. This limits the maximum demand on the external power supply by controlling the inrush current required to charge the external capacitor and any DC load at startup. Internally, the ramp is set to 10 ms nominal.

The following conditions are required to trigger a soft start:

- ENBAT or ENB transition to high, and

- There is no thermal shutdown, and

- V33 voltage is below its UVLO threshold, and

- VREG voltage is below its UVLO threshold.

### Buck Pulse Width (ton)

A resistor from the TON input to VIN sets the on-time of the converter for a given input voltage. When the supply voltage is between 8.3 and 31 V, the switcher period remains constant based on the selected value of  $R_{TON}$ . At voltages lower than 6.5 V the switch is in dropout mode. For reasonable input voltage ranges the period of the converter is held constant resulting in a constant operating frequency over the input supply range. More information on how to choose  $R_{TON}$  can be found in the Application Information section.

The formula to calculate the value for the on-time resistor is:

$$t_{\rm on} = (R_{\rm TON} / V_{\rm IN}) \times 6.36 \times 10^{-12} + 5 \times 10^{-9}$$

(ns). (1)

### **ISEN+** and **ISEN**-

The sense inputs are used to sense the current in the buck, freewheeling diode during the off-time cycle. The value for  $R_{SENSE}$  is obtained by the formula:

$$R_{\rm SENSE} = 220 \,(\rm mV) \,/ \, I_{\rm VALLEY} \quad , \tag{2}$$

where  $I_{VALLEY}$  is the lowest current measured through the inductor during the off-time cycle. It is recommended that the current sense resistor be sized so that, at peak output current, the voltage

at the ISEN– pin does not exceed -0.75 V during PWM operation (that is, a transient condition). Because the diode current is measured when the inductor current is at the valley, the average output current is greater than the I<sub>VALLEY</sub> value. The value for I<sub>VALLEY</sub> should be:

$$I_{\text{VALLEY}} = I_{\text{OUT}(\text{AVG})} - 0.5 \times I_{\text{RIPPLE}} + \text{K}$$

,

where:

$I_{OUT(AVG)}$  is the average of the output currents of all the regulators,

I<sub>RIPPLE</sub> is the inductor ripple current, and

K is a design margin allowing for component tolerances.

The peak current in the switch is simply:

$$I_{\rm PEAK} = I_{\rm VALLEY} + I_{\rm RIPPLE} \ . \tag{4}$$

Information on how to calculate the ripple current is included in the Application Information section.

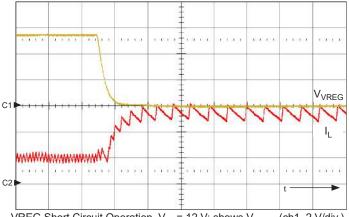

### **Switcher Overcurrent Protection**

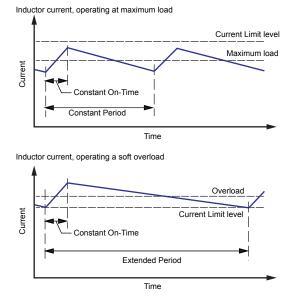

The converter utilizes pulse-by-pulse valley current limiting, which is activated when the current through the sense resistor (that is, the buck output current) is high enough to create 220 mV between the ISEN pins. During an overload condition, the switch is turned on for a period determined by the constant on-time circuitry. The switch off-time is extended until the current decays to the current limit value set by the selection of the sense resistor, at which point the switch is allowed to turn on again. Because no slope compensation is required in this control scheme, the current limit is maintained at a reasonably constant level across the input voltage range.

Figure 1 illustrates how the current is limited during an overload condition. The current decay (period with switch off) is proportional to the output voltage. As the overload is increased, the output voltage tends to decrease and the switching period increases.

### LX Short Circuit Protection

If the LX node is shorted to ground there will be a relatively high peak current in the buck MOSFET within a very short time. The A4405 protects itself by detecting the unusually high current, turning off the buck MOSFET, and latching itself off. To avoid false tripping, the current required to activate the peak current protection ( $I_{LIM(PEAK)}$ , nominally 5 A) is set well above the normal range of currents. When the peak current limit is activated the A4405 is latched off until either  $V_{IN}$  is cycled below its UVLO threshold or the A4405 is disabled (both ENBAT and ENB must be brought low) and re-enabled. NPOR is not directly activated (pulled low) by the peak current protection circuitry. However, NPOR will certainly be in the correct state depending on VREG and V33.

(3)

Figure 1. Current limiting during overload conditions

### **Missing Asynchronous Diode Protection**

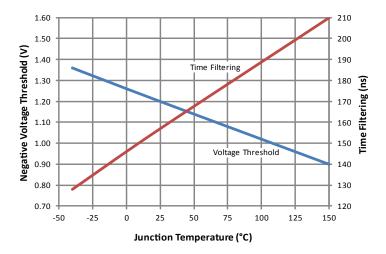

In most high voltage asynchronous buck regulators, if the asynchronous diode is missing or damaged the LX pin will transition to a very high negative voltage when the upper MOSFET turns off, resulting in damage to the regulator. The A4405 includes protection circuitry to detect when the asynchronous diode is missing or damaged. If the LX pin becomes more negative than 1.2 V at 25°C for more than 157 ns, the A4405 will latch itself in the off state to prevent damage. After a missing diode fault occurs, the latch must be reset by either cycling VIN or ENBAT or ENB. See figure 2 for the missing diode voltage threshold and time filtering versus temperature.

### **Thermal Shutdown**

If the A4405 junction temperature becomes too high, a thermal shutdown circuit disables the VREG output, thus protecting the A4405 from damage. When a thermal shutdown occurs, the buck regulator stops switching and the VREG voltage will decay. When  $V_{VREG}$  crosses its UVLO threshold, the NPOR signal is pulled low. Thermal shutdown is not a latched condition so, when the junction temperature cools to an acceptable level, the A4405 will automatically restart.

### Power-On Reset (NPOR)

The NPOR output is an open drain pin that can be used to signal a reset event to a DSP or microcontroller. The NPOR function actively monitors ENBAT, ENB, V33, and VREG. During powerup, NPOR is held low for a programmable amount of time, t<sub>NPOR</sub>,

Figure 2. Missing diode protection versus device junction temperature

after both VREG and V33 transition above their upper UVLO thresholds. The rising edge delay allows time for the regulators to be within specification when the DSP or microcontroller begins processing. The amount of the rising edge delay is determined by the value of the external capacitor from the CPOR pin to ground.

The rising delay can be calculated from the following formula:

$$t_{\rm NPOR} = 92.3 \times 10^3 \times C_{\rm CPOR} \quad (\text{seconds}). \tag{5}$$

Any of the following conditions will force NPOR to transition to low immediately (within a few microseconds):

- V33 voltage falls below its UVLO threshold, or

- VREG voltage falls below its UVLO threshold, or

- ENBAT and ENB are both low, or

- Charge pump voltage is too low. or

- Internal IC regulation (V<sub>RAIL</sub>) is too low.

If thermal shutdown occurs, PWM switching will terminate,  $V_{VREG}$  and/or  $V_{V33}$  will decay below the UVLO threshold, and NPOR will transition to low. Thus, a thermal shutdown event indirectly causes NPOR to transition to low.

When the A4405 is disabled (either both ENB and ENBAT are low, or V<sub>IN</sub> is removed) the NPOR output is held low until the voltage from the 3.3 V regulator (V<sub>V33</sub>) falls below 1.0 V. This assumes maximum initial current (4 mA) in the NPOR open drain DMOS. The NPOR voltages would be somewhat lower for lower values of I<sub>NPOR</sub>. See figure 3.

Figure 3. NPOR and V33 characteristics when the A4405 is disabled

# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

### V5 Regulator

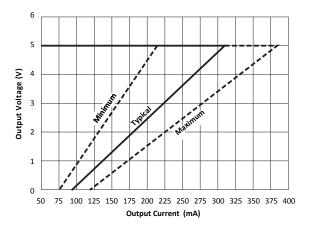

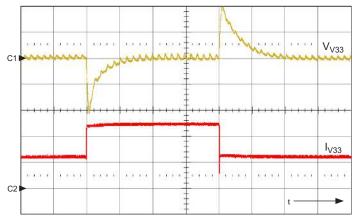

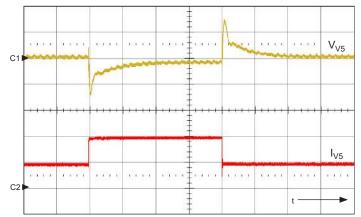

The 5 V linear regulator is provided to supply local circuitry. This regulator can deliver 300 mA (typ), 215 mA (min). When a direct short is applied to this regulator the output the current folds back to 0 V at approximately 100 mA (typ) (figure 4).

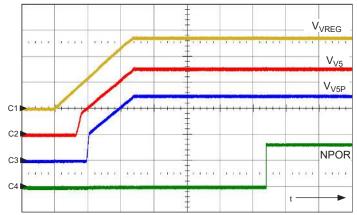

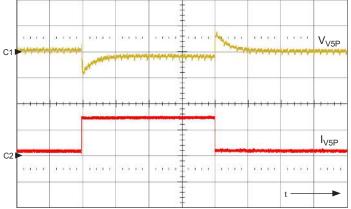

### **V5P Tracking Regulator**

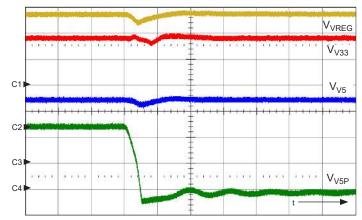

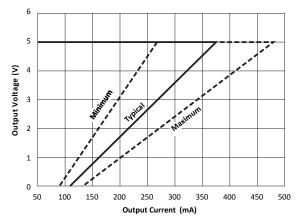

The 5VP linear tracking regulator is provided to supply remote circuitry such as off-board sensors. The V5P pin is monitored and if a short to ground or a short to battery occurs the V5P output is disabled and/or disconnected and the other outputs (VREG, V5, and V33) remain active until the short is removed. The regulator can deliver 375 mA (typ), 270 mA (min). When a direct short is applied to this regulator the output the current folds back to 0 V

Figure 4. Foldback current limit of the 5V regulator

Figure 6. V5P is shorted to ground in 5  $\mu$ s (D<sub>V5P</sub> is populated); shows V<sub>VREG</sub> (ch1, 2 V/div.), V<sub>V33</sub> (ch2, 1 V/div.), V<sub>V5</sub> (ch3, 2 V/div.), V<sub>V5P</sub> (ch4, 2 V/div.), t = 10  $\mu$ s/div.

at approximately 112 mA (typ) (figure 5).

The V5P regulator is designed to track the V33 output during power-up and when the device is completing a soft start ramp. The V5P regulator tracks the 3.3 V output to within  $\pm 0.5\%$  under normal steady state operating conditions. If the V33 regulator is decreasing, the V5P regulator accurately tracks the V33 output down to the point at which a V33 undervoltage fault (2.825 V nominally: 2.95 V – 125 mV) results in the NPOR output going active.

The figures 6 and 7 show A4405 operation when the V5P pin is shorted to ground and VIN (battery). In both cases, the V5P output is disabled and/or disconnected while the other outputs (VREG, V5, and V33) remain active.

Figure 5. Foldback current limit of the 5VP regulator

Figure 7. V5P is shorted to a 25 V battery; shows V<sub>VREG</sub> (ch1, 2 V/div.), V<sub>V33</sub> (ch2, 2 V/div.), VIN pin (ch3, 5 V/div.), V<sub>V5P</sub> (ch4, 5 V/div.), t = 10  $\mu$ s/div.

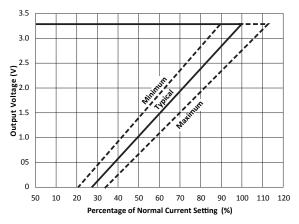

### 3.3 V Linear Regulator

An additional 3.3V linear regulator can be implemented using an external MOSFET. In the event the 3.3V regulator output is shorted to ground, the A4405 protects the external MOSFET by folding back when the programmed current limit,  $I_{CL}$ , is exceeded. The current limit is determined by the voltage developed across the external sense resistor,  $R_{CL}$ , shown in the Typical Application Circuit schematic. The 3.3V current limit can be calculated using the following formula:

$$I_{\rm CL} = V_{\rm CLV33} / R_{\rm CL} \quad , \tag{6}$$

where  $V_{CLV33}$  is as documented in the Electrical Characteristics table, nominally 200 mV. Typically  $R_{CL}$  will be a fairly low value so it will not dissipate significant power, 1/4 W should be adequate, but the tolerance should be 1% or less.

When  $I_{CL}$  is exceeded, the maximum load current through the external MOSFET is typically folded back to 48% of  $I_{CL}$  as shown in figure 8.

Some applications require 5.0 V instead of 3.3 V. The external LDO controller will produce 5.0 V if a resistor divider is inserted between the controller output (that is, the source of the external MOSFET) and the V33 pin, as shown on page 1 of this datasheet. In this case, the 1.2  $\Omega/0.5$  W power dropping resistor in series with the drain of the external MOSFET must be removed from the design.

Allegro recommends using resistors with  $\leq 0.5\%$  tolerance for two reasons: (1) the 5.0 V output will have the best accuracy, and (2) to maintain a low tracking error between the V5P and the 5.0 V output. A comparison of two sets of resistor values at 0.1% and 0.5% tolerance are shown in the following table.

| R1 and R2 Values             | 5V Output Range (V) |       |       | V5P/V5                   |

|------------------------------|---------------------|-------|-------|--------------------------|

| and Tolerances               | Min.                | Тур.  | Max.  | Tracking<br>Accuracy (%) |

| 100 Ω and 196 Ω<br>±0.1%     | 4.887               | 4.999 | 5.112 | ±0.6                     |

| 100 Ω and 196 Ω<br>±0.5%     | 4.874               | 4.999 | 5.125 | ±0.9                     |

| 1.02 kΩ and 2.18 kΩ<br>±0.1% | 4.867               | 5.002 | 5.141 | -1.1, +1.2               |

| 1.02 kΩ and 2.18 kΩ<br>±0.5% | 4.855               | 5.002 | 5.154 | -1.4, +1.5               |

### **Charge Pump**

The charge pump is used to generate a supply above  $V_{IN}$ . A 0.22 µF ceramic monolithic capacitor should be connected between VCP and VIN to act as a reservoir to run the DMOS switch. The VCP voltage is internally monitored to ensure that the charge pump is disabled in the case of a fault condition. A 0.22  $\mu F$  ceramic monolithic capacitor should be connected between CP1 and CP2.

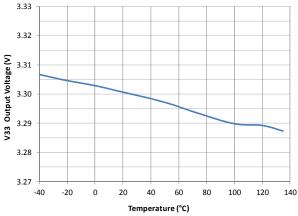

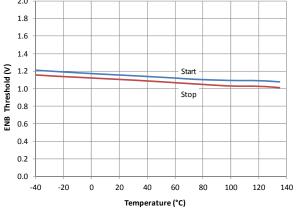

### ENBAT

This is a level-triggered enable input, use for enabling the device based on a high voltage ignition or battery switch (via a 1 k $\Omega$  resistor). The ENBAT comparator thresholds are  $V_{IGN(L)} = 2.2 V(min)$ and  $V_{IGN(H)} = 4.0 V(max)$ . ENBAT is used only as a momentary switch to enable or wake up the A4405. After ENBAT is removed, ENB must be high to keep the A4405 enabled. The ENB and ENBAT signals are logically ORed together internally so either one may wake up the A4405 and both must be low to disable the A4405. Only one of the two inputs must be pulled high in order to enable the part. If there is no requirement for an ignition switch, then ENBAT can be pulled low, which makes ENB a single reset control.

If an external resistor and capacitor are used to form a low-pass filter to the ENBAT pin, then a 100  $\Omega$  resistor must be used to prevent the external capacitor from discharging into and damaging the ENBAT pin. See the Typical Application Circuit schematic for connection of these 3 components.

### ENBATS

When a logic high is sensed on the ENBAT input, the ENBATS output will go high, signaling to the user that the ignition input is high. When a logic low is sensed on the ENBAT input, then ENBATS will also transition to low. The ENBATS input logic levels are identical to the ENBAT input logic levels.

### ENB

This pin can be used as an enable input from either a DSP or from a microcontroller. This input has an internal pull-down resistor so it may be left unconnected if not used.

Figure 8. Foldback current limit of the V33 regulator

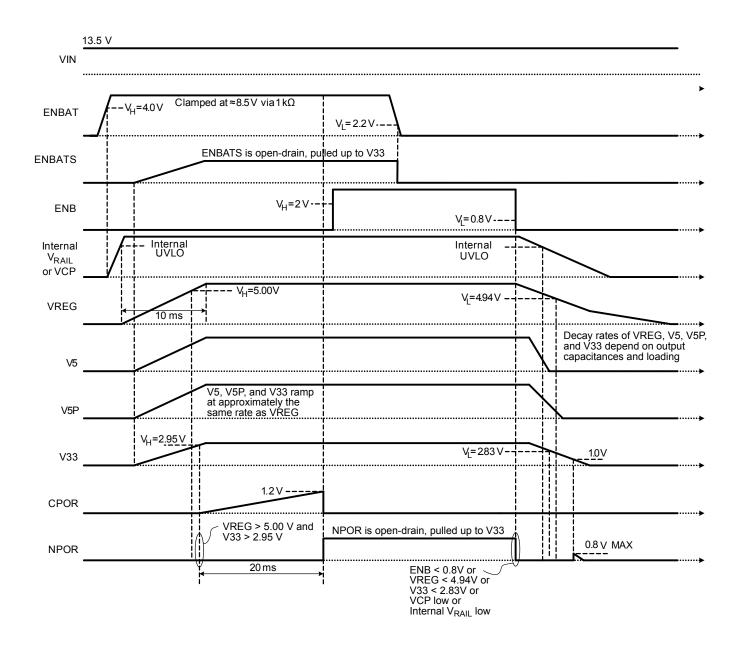

## TIMING DIAGRAMS

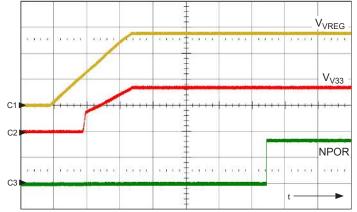

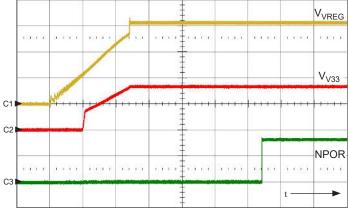

Typical power-up and power-down by ENBAT and ENB with V<sub>IN</sub> = 13.5 V; ENBATS is assumed to be connected to V33 via a pull-up resistor

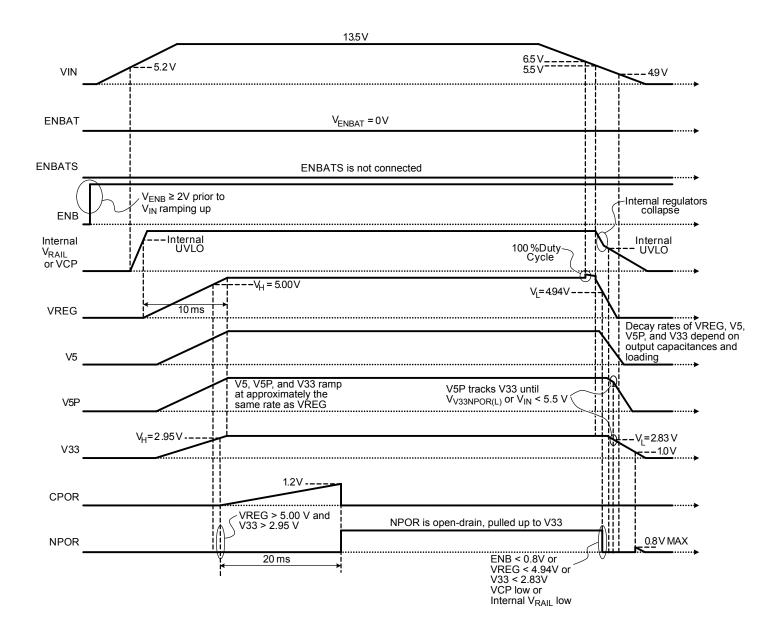

Typical power-up and power-down via VIN with ENB always logic high; ENBAT and ENBATS are not used

### **APPLICATION INFORMATION**

#### Switcher On-Time and Switching Frequency

In order for the switcher to maintain regulation, the energy that is transferred to the inductor during the on-time must be transferred to the capacitor during the off-time. Because of this relationship, the load current and IR drops, as well as input and output voltages, affect the on-time of the converter. The formula that governs switcher on-time is shown below:

$$t_{\rm ON} = \frac{T_{\rm SW} \times \{V_{\rm VREG} + [(R_{\rm L} + R_{\rm SENSE}) \times I_{\rm PEAK}] + V_{\rm f}\}}{V_{\rm IN} - R_{\rm DS(on)} \times I_{\rm PEAK} + V_{\rm f}} \quad (7)$$

where  $V_{\rm f}$  is the forward voltage on the diode  $D_{\rm BUCK}$  in the Typical Application Circuit schematic.

The effects of the voltage drop on the inductor and trace resistance will affect the switching frequency. However, the frequency variation due to these factors is small and is covered in the variation of the switcher period, which is  $\pm 25\%$  of the target. Removing these current dependent terms simplifies the formula:

$$t_{\rm ON} = \frac{(1/f_{\rm SW}) \times (V_{\rm VREG} + R_{\rm SENSE} \times I_{\rm PEAK}) + V_{\rm f}}{V_{\rm IN} - R_{\rm DS(on)} \times I_{\rm PEAK} + V_{\rm f}} \quad . \tag{8}$$

Be sure to use the worst-case sense voltage and forward voltage of the diode  $D_{BUCK}$ , including any effects due to temperature. For an example: assume a 1 A converter with a supply voltage of 13.5 V. The output voltage is 5.45 V,  $V_f$  is 0.45 V,  $R_{SENSE} \times I_{PEAK}$  is 0.20 V,  $R_{DS(ON)} \times I_{PEAK}$  is 0.15 V, and the required frequency is 2.2 MHz. Substituting into equation 8, we can solve for  $t_{ON}$ :

$$t_{ON} = 1 / 2.2 \text{ (MHz)} \times \\ [(5.45+0.20+0.45) / (13.5-0.15+0.45)] \\ = 201 \text{ (ns)} .$$

The formulas above describe how  $t_{ON}$  changes based on input and load conditions. Because load changes are minimal and the output voltage is fixed, the only factor that will affect the on-time is the input voltage. The converter is able to maintain a constant period over a varying supply voltage because the on-time changes based on the input voltage. The current into the TON terminal is derived from a resistor tied to VIN, which sets the on-time proportional to the supply voltage. Selecting the resistor value based on the t<sub>ON</sub> calculated above is done using the following formula:

$$R_{\rm TON} = \left[ V_{\rm IN} \times (t_{\rm ON} - 5 \,(\rm ns)) \right] / 6.36 \times 10^{-12} \quad . \tag{9}$$

After the resistor is selected and a suitable  $t_{ON}$  is found, it must be demonstrated that  $t_{ON}$  does not, under worst-case conditions, exceed the minimum on-time or minimum off-time of the converter. The minimum on-time occurs at maximum input voltage and minimum load. The maximum off-time occurs at minimum supply voltage and maximum load. For supply voltages below 8.3 V and above 6.5 V, refer to the Low Voltage Operation section.

### Low Voltage Operation

The converter can run at very low input voltages; with a 5.25 V output the minimum input supply can be as low as 5.5 V. When operating at high frequencies the on-time of the converter must be very short because the available period is short. At high input voltages the converter should not violate the minimum on-time,  $t_{ON}(min)$ , while at low input voltages the converter should not violate the minimum off-time,  $t_{OFF}(min)$ . Rather than limit the supply voltage range, the converter solves this problem by automatically increasing the period. With the period extended the converter will not violate the minimum on-time or off-time specifications. If the input voltage is between 8.3 and 31 V, the converter maintains a constant period. When calculating worst case on-times and off-times, make sure to use the highest switching frequency if the supply voltage is in that range.

When operating at voltages below 8.3 V, additional care must be taken when selecting the inductor and diode. At low voltages the maximum current may be limited due to the IR drops in the current path. When selecting external components for low voltage operation, the IR drops must be considered for determining on-time, so the complete equation (formula 8) should be used to make sure the converter does not violate the timing specification.

### **Inductor Selection**

Choosing the right inductor is critical to the correct operation of the switcher. The converter is capable of running at frequencies above 2 MHz, this makes it possible to use small inductor values, which reduces cost and board area.

The inductor value is what determines the ripple current. It is important to size the inductor so that under worst-case conditions  $I_{TRIP}$  equals  $I_{AVG}$ , minus half of the ripple current, plus a reasonable margin. If the ripple current is too large, the converter will activate the current limit function. Typically peak-to-peak

ripple current should be limited to a range of 20% to 25% of the maximum average load current.

Worst-case ripple current occurs at maximum supply voltage.

After calculating the duty cycle for this condition, the ripple current can be calculated:

$$D = \frac{V_{\text{VREG}} + (R_{\text{SENSE}} \times I_{\text{PEAK}}) + V_{\text{f}}}{V_{\text{IN}}(\text{max}) - R_{\text{DS}(\text{on})} \times I_{\text{PEAK}} + V_{\text{f}}} \quad (10)$$

Using the duty cycle, a ripple current can be calculated using the formula below:

$$L = \frac{V_{\rm IN} - V_{\rm VREG}}{I_{\rm RIPPLE}} \times D \times \frac{1}{f_{\rm SW}(\rm min)} \quad , \tag{11}$$

where  $I_{RIPPLE}$  is 25% of the maximum load current, and  $f_{SW}(min)$  is the minimum switching frequency, nominal frequency minus 25%. For the example used above, a 1 A converter with a supply voltage of 13.5 V was the design objective. The supply voltage can vary by  $\pm 10\%$ . The output voltage is 5.45 V,  $V_f$  is 0.5 V,  $V_{SENSE}$  is 0.20 V and the required frequency is 2.2 MHz. The duty cycle is calculated to be 36.45%. The worst-case frequency is 1.76 MHz, 2.2 MHz minus 20%. Using these numbers in formula 11 shows that the minimum inductance for this converter is 9.6  $\mu$ H.

### **Output Capacitor**

The converter is designed to operate with a low value ceramic output capacitor on VREG (C<sub>VREG</sub>). When choosing a ceramic capacitor make sure the rated voltage is at least 3 times the maximum output voltage of the converter. This is because the capacitance of a ceramic decreases as it operates closer to the capacitor rated voltage. It is recommended that the VREG output be decoupled with a 10  $\mu$ F X7R ceramic capacitor. Greater capacitance may be required on the output if load surges dramatically influence the output voltage.

Output ripple is determined by the output capacitance and the effects of ESR and ESL can be ignored assuming recommended layout techniques are followed. The output voltage ripple is approximated by:

$$V_{\text{RIPPLE}} = I_{\text{RIPPLE}} / \left(8 \times f_{\text{SW}} \times C_{\text{VREG}}\right)$$

(12)

#### **Input Capacitor**

The value of the input capacitance affects the amount of current ripple on the input. This current ripple is usually the source of supply-side EMI. The amount of interference will depend on the impedance from the input capacitor and the bulk capacitance located on the supply bus. Placing a 0.1  $\mu$ F ceramic capacitor very close to the input supply pin will help reduce EMI effects. The small capacitor will help reduce high frequency transient currents on the supply line. If further filtering is needed it is recommended that two ceramic capacitors be used in parallel to further reduce emissions.

### **Rectification Diode**

The diode conducts the current during the off cycle. A Schottky diode is required to minimize the forward drop and switching losses. In order to size the diode correctly it is necessary to find the average diode conduction current using the formula below :

$$I_{\text{diode(avg)}} = I_{\text{load}} \times (1 - D(\min))$$

(13)

where D(min) is the minimum duty cycle, defined as:

$$D(\min) = (V_{VREG} + V_f) / (V_{IN} + V_f)$$

(14)

where  $V_{\rm IN}$  is the maximum input voltage and  $V_{\rm f}$  is the maximum forward voltage of the diode.

The average power dissipation in the diode is:

$$P_{Ddiode(avg)} = I_{avg} \times D(\min) \times V_{f}$$

(15)

The power dissipation in the sense resistor must also be considered using  $I^2R$  and the minimum duty cycle.

#### **External MOSFET Selection**

To choose an external MOSFET for the 3.3 V linear regulator consider the maximum of: drain-to-source voltage ( $V_{DS}$ ), continuous drain current ( $I_D$ ), threshold voltage ( $V_{GSTH}$ ), on-resistance ( $R_{DS(on)}$ ), and thermal resistance ( $R_{\theta JC}$ ).

The buck switcher pre-regulates the voltage to the external MOS-FET, so even under worst case conditions, the MOSFET will not have to support more than 7 V from drain to source. Also, the 3.3 V current limit will usually be set from 200 to 500 mA using the external current setting resistor,  $R_{CL}$ . Numerous MOSFETs are available with  $V_{DS}$  ratings of at least 20 V that can support much more than 1 A. These two goals should not be difficult to achieve.

The A4405 gate drive circuitry is guaranteed to pull the G33 voltage down to 1 V, maximum. Therefore, Allegro recommends using a MOSFET with a  $V_{GS}$  threshold ( $V_{GSTH}$ ) higher than 1 V. Do not use a MOSFET that will conduct significant current when  $V_{GS}$  is at 1 V and the system is at the highest expected ambient temperature.

One of the more critical specifications is the MOSFET onresistance,  $R_{DS(on)}$ . If the on-resistance is too high, then the 3.3 V regulator will not be able to maintain 3.3 V at the maximum required load current,  $I_{LIM(V33)}$ . Calculate the typical  $R_{DS(on)}$  (at 25°C) using the following formula:

$$R_{\rm DS(on)25^{\circ}C} < 0.6 \times 1.56 \,({\rm V}) \,/ \,(I_{\rm LIM(V33)} - R_{\rm DROP}) \tag{16}$$

where  $I_{LIM(V33)}$  is the maximum required 3.3 V output current, and  $R_{DROP}$  is the value of the resistor connected from the CLV33 pin to the drain of the MOSFET.

The multiplier of 0.6 in the following formula allows a 66% increase in  $R_{DS(on)}$  when the MOSFET is very hot:

$$R_{\rm DS(on)25^{\circ}C} < 0.6 \times \left(\frac{1.56 \,({\rm V})}{I_{\rm LIM(V33)}} - R_{\rm DROP}\right)$$

(17)

where  $I_{LIM(V33)}$  is the maximum required 3.3 V output current.

The necessity and value of  $R_{DROP}$  is closely related to the thermal resistance ( $R_{\theta JC}$ ) of the MOSFET. For a medium size MOS-FET (such as an SOT-223) including  $R_{DROP}$  in the PCB layout is highly recommended. For a large size MOSFET with a very low thermal resistance (such as a DPAK)  $R_{DROP}$  is probably not necessary.

MOSFET thermal resistance is a function of die size, package size, and cost. So, choosing  $R_{DROP}$  and  $R_{\theta JC}$  together should result in optimal performance, minimal component sizes, and lowest system cost. Determining the value and power dissipated by the series dropping resistor and MOSFET thermal resistance are addressed in detail in the 3.3 V Dropping Resistor section.

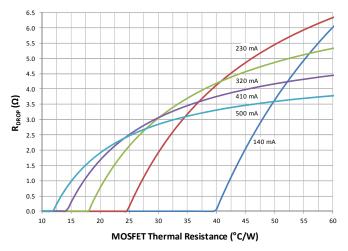

### 3.3 V Dropping Resistor (R<sub>DROP</sub>)

In the Typical Application Circuit schematic, there are two resistors,  $R_{CL}$  and  $R_{DROP}$ , from the output of the buck regulator to

the drain of the external MOSFET.  $R_{CL}$  must always be present because it sets the 3.3 V regulator current limit threshold. However,  $R_{DROP}$ , if used, prevents the external MOSFET from dissipating too much power during certain conditions. In particular, when the battery voltage is extremely low ( $V_{BAT} \le 6.5$  V) and the buck regulator transitions to dropout mode (100% duty cycle) then  $V_{VREG}$  will be approximately 1 V higher than normal. In this situation, without  $R_{DROP}$ , the MOSFET could dissipate too much power.

The value of  $R_{DROP}$  depends on the maximum PCB temperature, the maximum current load on the 3.3 V regulator,  $I_{LIM(V33)}$ , the maximum allowable junction temperature of the MOSFET, and the thermal resistance of the MOSFET. As the thermal resistance of the MOSFET decreases, the required value of  $R_{DROP}$  will also decrease. If the MOSFET is relatively large and has a very low thermal resistance, then  $R_{DROP}$  is not required (0  $\Omega$ ).

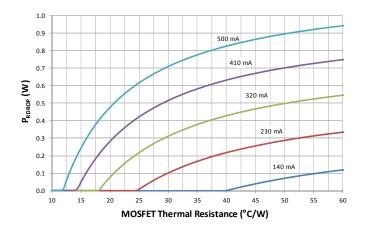

Figure 9 shows recommended values of  $R_{DROP}$  versus MOSFET thermal resistance at various 3.3 V regulator maximum current settings ( $I_{LIM(V33)}$ ). This graph assumes a PCB temperature of 135°C, a maximum MOSFET junction temperature of 145°C,  $V_{BAT}$  of 6.5 V, and 3.23 V from the linear regulator. This graph takes into account the voltage drop across the 3.3 V current limit resistor,  $R_{CL}$ .

Figure 9. Value of  $R_{DROP}$  versus MOSFET thermal resistance at various V33 regulator maximum current settings,  $I_{LIM(V33)}$

# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

After a value for  $R_{DROP}$  is determined, the designer should calculate its maximum power dissipation (I<sup>2</sup> × R) and select an appropriate component, allowing adequate design margin. Assuming the  $R_{DROP}$  value was chosen referencing figure 9, then figure 10 can be used to determine the power dissipated by  $R_{DROP}$  versus MOSFET thermal resistance at various 3.3V regulator current settings. The exact value of  $R_{DROP}$  is not critical, so a component with 1% or 5% tolerance could be used.

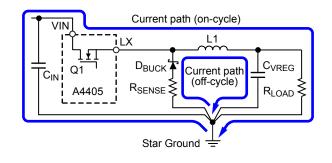

### **PCB** Layout

The board layout will have a large impact on the performance of the device. It is important to isolate high current ground returns to minimize ground bounce that could produce reference errors in the device. The method used to isolate power ground from noise sensitive circuitry is to use a star ground. This approach ensures that the high current components such as the input capacitor, output capacitor, and diode have very low impedance paths to each other. Figure 11 illustrates the technique.

The ground connections from each of the components should be very close to each other and be connected on the same surface as the components. Internal ground planes should not be used for the star ground connection, because vias add impedance to the current path.

In order to further reduce noise effects on the PCB, noise sensitive traces should not be connected to internal ground planes. The feedback network from the switcher output should have an independent ground trace that goes directly to the exposed pad underneath the device. The exposed pad should be connected to internal ground plans and any exposed copper used for heat dissipation. If the ground connections from the device are also connected directly to the exposed pad, the ground reference from the feedback network will be less susceptible to noise injection or ground bounce.

Figure 10.  $R_{DROP}$  Dissipation versus MOSFET thermal resistance at various V33 regulator maximum current settings,  $I_{V33\Pi,IM}$

Figure 11. Illustration of star ground connection

# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

To reduce radiated emissions from the high frequency switching nodes, it is important to have an internal ground plane directly under the LX node. The plane should not be broken directly under the node because the lowest impedance path back to the star ground would then be directly under the signal trace. If another trace does break the return path, the energy will have to find another path, which is through radiated emissions.

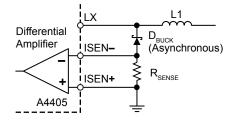

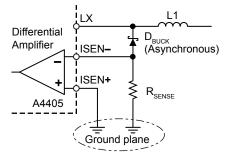

For accurate current sensing, the current sense pins, ISEN+ and ISEN–, and the internal differential amplifier comprise a differential signal receiver, and a balanced pair of traces should be routed from the pins of the buck current sense resistor,  $R_{\rm SENSE}$ , as shown in figure 12 (upper panel). The ISEN+ pin and the sense resistor ground should not be separated by simply using local via connections to the ground plane (figure 12 lower panel). Incorrect routing of the ISEN+ pin would likely add an offset error to the buck current sense signal.

Correct routing of ISEN+ and ISEN– traces (direct on same plane)

Incorrect routing of ISEN+ and ISEN– traces (using vias to a ground plane)

Figure 12. Comparison of routing paths for the traces between the A4405 ISEN+ and ISEN– traces and the sense resistor,  ${\sf R}_{\sf SENSE}$

### APPLICATION CIRCUIT PERFORMANCE

(Refer to Typical Application Circuit diagram.)

#### **Bill of Materials for Critical Components**

This design is capable of full load,  $135^{\circ}$ C ambient, and  $5.5 V_{BAT}$  indefinitely with an adequate thermal solution

| Component                                              | Description                                                         | Package      | Manufacturer   | Part Number        |

|--------------------------------------------------------|---------------------------------------------------------------------|--------------|----------------|--------------------|

| Q <sub>V33</sub>                                       | MOSFET, 40 V, 90 A, 4.3 mΩ, T <sub>J</sub> 175°C                    | DPAK         | Infineon       | IPD90N04S3-04      |

| R <sub>SENSE</sub>                                     | Resistor, 0.300 $\Omega$ , $^{1}/_{4}$ W, 1%                        | 1206         |                |                    |

| R <sub>CL</sub>                                        | Resistor, 0.390 $\Omega$ , $^{1}/_{4}$ W, 1%                        | 1206         |                |                    |

| R <sub>DROP</sub>                                      | Resistor, 1.2 $\Omega$ total, $1/2$ W, 1%                           | 1210         |                |                    |

| C <sub>IN1</sub> , C <sub>IN2</sub>                    | Capacitor, Ceramic, 4.7 µF, 50 V, 10%, X7R                          | 1210         | Murata         | GCM32ER71H475KA55L |

| C <sub>VREG</sub>                                      | Capacitor, Ceramic, 10 µF, 16 V, 10%, X7R                           | 1206         | Kemet          | C1206C106K4RACTU   |

| C <sub>V33</sub> , C <sub>V5</sub> , C <sub>V5P</sub>  | Capacitor, Ceramic, 2.2 µF, 16 V, 10%, X7R                          | 1206         | Murata         | GRM31MR71C225KA35L |

| D <sub>BUCK</sub> , D <sub>IN</sub> , D <sub>V5P</sub> | Diode, Schottky, 2 A, 40 V                                          | SMA          | Diodes, Inc.   | B240A-13-F         |

| L1                                                     | Inductor, 10 $\mu$ H, 64 m $\Omega$ , 2.39 A <sub>sat</sub> , 165°C | 7.6 x 7.6 mm | Cooper/Bussman | DRA73-100-R        |

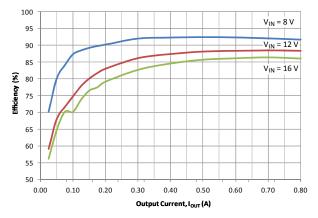

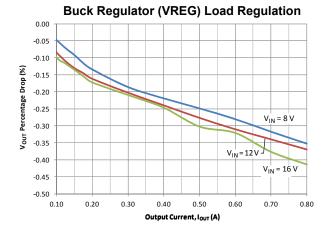

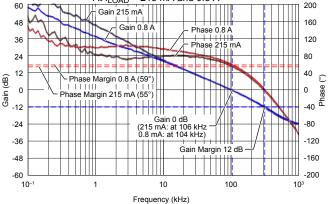

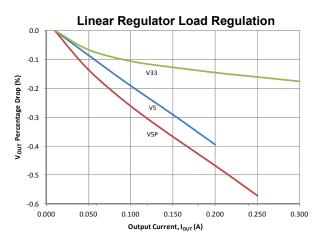

#### **Buck Regulator (VREG) Efficiency**

# Constant On-Time Buck Regulator with Single External and Dual Internal Linear Regulators

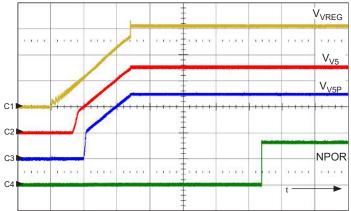

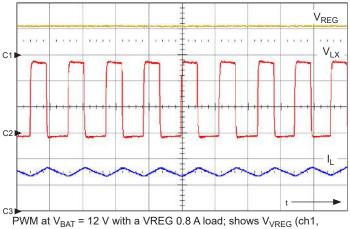

Startup at V<sub>IN</sub> = 13.5 V; shows V<sub>VREG</sub> (ch1, 2 V/div.), V<sub>V33</sub> (ch2, 2 V/div.), NPOR (ch3, 2 V/div.), t = 5 ms/div.