on Kit L ible Re

Resources and Mode

Click here to ask an associate for production status of specific part numbers.

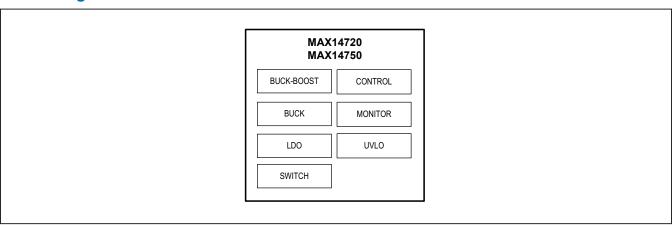

#### **Power-Management Solution**

#### MAX14720/MAX14750

#### **General Description**

The MAX14720/MAX14750 are compact power-management solutions for space-constrained, battery-powered applications where size and efficiency are critical. Both devices integrate a power switch, a linear regulator, a buck regulator, and a buck-boost regulator.

The MAX14720 is designed to be the primary powermanagement device and is ideal for either non-rechargeable battery (coin-cell, dual alkaline) applications or for rechargeable solutions where the battery is removable and charged separately. The device includes a button monitor and sequencer.

The MAX14750 works well as a companion to a charger or PMIC in rechargeable applications. It provides direct pin control of each function and allows greater flexibility for controlling sequencing.

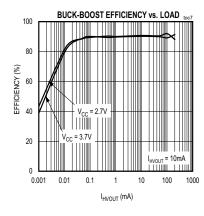

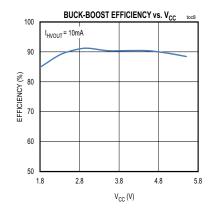

The devices include two programmable micro- $I_Q$ , high-efficiency switching converters: a buck-boost regulator and a synchronous buck regulator. These regulators feature a burst mode for increased efficiency during light-load operation.

The low-dropout linear regulator has a programmable output. It can also operate as a power switch that can disconnect the guiescent load of system peripherals.

The devices also include a power switch with batterymonitoring capability. The switch can isolate the battery from all system loads to maximize battery life when not operating. It is also used to isolate the battery-impedance measurements. This switch can operate as a generalpurpose load switch as well.

The MAX14720 includes a programmable power controller that allows the device to be configured either for use in applications that require a true off state or for always-on applications. This controller provides a delayed reset signal, voltage sequencing, and customized button timing for on/off control and recovery hard reset.

Both devices also include a multiplexer for monitoring the power inputs and outputs of each function.

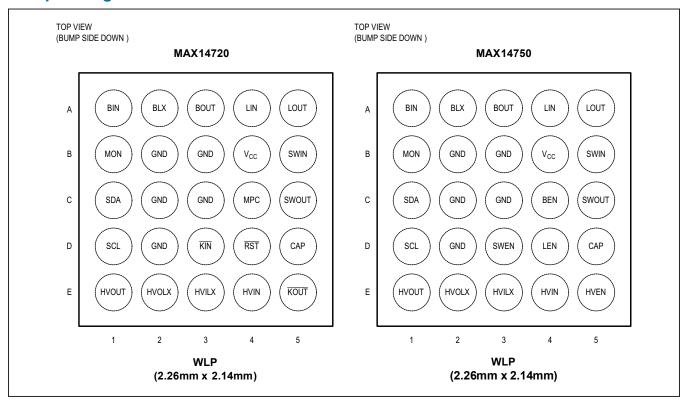

These devices are available in a 25-bump, 0.4mm pitch, 2.26mm x 2.14mm wafer-level package (WLP) and operate over the -40°C to +85°C extended temperature range.

#### **Benefits and Features**

- Extended System Battery Use Time

- Micro-I<sub>O</sub> 250mW Buck-Boost Regulator

- Input Voltage from 1.8V to 5.5V

- Output Voltage Programmable from 2.5V to 5V

- 1.1µA Quiescent Current

- Programmable Current Limit

- Micro-I<sub>Q</sub> 200mA Buck Regulator

- Input Voltage from 1.8V to 5.5V

- Output Voltage Programmable from 1.0V to 2.0V

- 0.9µA Quiescent Current

- Micro-I<sub>Q</sub> 100mA LDO

- Input Voltage From 1.71V to 5.5V

- Output Programmable From 0.9V to 4.0V

- 0. 9µA Quiescent Current

- Configurable as Load Switch

- Extend Product Shelf-Life

- Battery Seal Mode (MAX14720)

- 120nA Battery Current

- · Power Switch On-Resistance

- 250mΩ (max) at 2.7V

- 500mΩ (max) at 1.8V

- · Battery Impedance Detector

- Easy-to-Implement System Control

- Configurable Power Mode and Reset Behavior (MAX14720)

- Push-Button Monitoring to Enable Ultra-Low Power Shipping Mode

- Disconnects All Loads From Battery and Reduces Leakage to Less than 1µA

- Power-On Reset (POR) Delay and Voltage Sequencing

- Individual Enable Pins (MAX14750)

- · Voltage Monitor Multiplexer

- I<sup>2</sup>C Control Interface

#### **Applications**

- Wearable Medical Devices

- Wearable Fitness Devices

- Portable Medical Devices

Ordering Information appears at end of data sheet.

#### **Absolute Maximum Ratings**

| (Voltages Referenced to GND.) BIN, LIN, SDA, SCL, SWIN, BEN, SWOUT, SWE LEN, HVEN, HVIN, HVOUT, MON, CAP, $V_{\rm CC}$ , | N,                       |

|--------------------------------------------------------------------------------------------------------------------------|--------------------------|

| MPC, KIN, RST, KOUT                                                                                                      | -0.3V to +6.0\           |

| HVILX0.3V to                                                                                                             | V <sub>HVIN</sub> + 0.3V |

| HVOLX0.3V to V <sub>F</sub>                                                                                              | 1VOUT + 0.3V             |

| BLX, BOUT0.3V to                                                                                                         | $(V_{BIN} + 0.3V)$       |

| LOUT0.3V to                                                                                                              | $(V_{LIN} + 0.3V)$       |

| GND                                                                                                                      | -0.3V to +0.3V           |

| Continuous-Current into HVIN, BIN, SWIN±1000mA            |

|-----------------------------------------------------------|

| Continuous-Current into Any Other Terminal±100mA          |

| Continuous Power Dissipation (multilayer board at +70°C): |

| 5x5 Array 25-Ball 2.26mm x 2.14mm 0.4mm Pitch WLP         |

| (derate 19.07mW/°C)1.525W                                 |

| Operating Temperature Range40°C to +85°C                  |

| Junction Temperature+150°C                                |

| Storage Temperature Range65°C to +150°C                   |

| Lead Temperature (soldering 10s)+300°C                    |

| Soldering Temperature (reflow)+260°C                      |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

| PACKAGE TYPE: 25 WLP                   |                                |  |  |  |

|----------------------------------------|--------------------------------|--|--|--|

| Package Code                           | W252M2+1                       |  |  |  |

| Outline Number                         | 21-0788                        |  |  |  |

| Land Pattern Number                    | Refer to Application Note 1891 |  |  |  |

| THERMAL RESISTANCE, FOUR-LAYER BOARD   |                                |  |  |  |

| Junction to Ambient (θ <sub>JA</sub> ) | 52.43°C/W                      |  |  |  |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                   | SYMBOL            | CONDITIONS                                                                                                                                                      | MIN  | TYP  | MAX  | UNITS |

|-----------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| SUPPLY CURRENT              |                   |                                                                                                                                                                 |      |      |      |       |

| Seal Input Current          | I <sub>SEAL</sub> | Seal mode, all functions disabled                                                                                                                               |      | 0.12 | 1    | μA    |

| Off Input Current           | l <sub>OFF</sub>  | No blocks enabled, no battery measurement active                                                                                                                |      | 1.2  | 2.8  | μА    |

| MON Input Current           | I <sub>MON</sub>  | No blocks enabled, no battery measurement active, MON enabled, MONCtr[2:0] = 000.                                                                               |      | 4    | 7.2  | μА    |

| Switch Input Current        | I <sub>SW</sub>   | Switch enabled, I <sub>SWOUT</sub> = 0A                                                                                                                         |      | 1.2  | 2.8  | μA    |

|                             |                   | LDO enabled, I <sub>LOUT</sub> = 0A                                                                                                                             |      | 2.1  | 4.4  |       |

| LDO Input Current           | I <sub>LDO</sub>  | LDO enabled, LIN UVLO enabled, ILOUT = 0A                                                                                                                       |      | 2.4  | 4.8  | μA    |

|                             |                   | LDO enabled, switch mode, I <sub>LOUT</sub> = 0A                                                                                                                |      | 1.5  | 3.2  |       |

|                             |                   | Buck enabled, I <sub>BOUT</sub> = 0A                                                                                                                            |      | 2    | 4.1  |       |

| Buck Input Current          | I <sub>BUCK</sub> | Buck enabled, BIN UVLO enabled, IBOUT = 0A                                                                                                                      |      | 2.2  | 4.5  | μA    |

| D. I. D. III.               |                   | Buck-Boost enabled, I <sub>HVOUT</sub> = 0A,<br>V <sub>HVOUT</sub> = 4V                                                                                         |      | 2    | 4.7  |       |

| Buck-Boost Input<br>Current | ost Input IBCKBST | Buck-Boost enabled, BIN UVLO<br>enabled, I <sub>HVOUT</sub> = 0A,<br>V <sub>HVOUT</sub> = 4V                                                                    |      | 2.3  | 5    | μA    |

| On Input Current            | I <sub>ON</sub>   | LDO, buck, and buck-boost<br>enabled; BIN UVLO and LIN UVLO<br>enabled; I <sub>SWOUT</sub> = I <sub>LOUT</sub> = I <sub>BOUT</sub><br>= I <sub>HVOUT</sub> = 0A |      | 4.4  | 8.3  | μА    |

| POWER SEQUENCE              |                   |                                                                                                                                                                 |      |      |      | •     |

| Poot Time                   | t                 | MAX14720                                                                                                                                                        | 9.9  | 11   | 12.1 | ms    |

| Boot Time                   | <sup>t</sup> воот | MAX14750                                                                                                                                                        | 21.6 | 24   | 26.4 |       |

| Reset Time                  | t <sub>RST</sub>  | MAX14720                                                                                                                                                        | 72   | 80   | 88   | ms    |

## **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                        | SYMBOL                           | CONDITIONS                                                                                                           | MIN | TYP  | MAX  | UNITS |

|----------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| POWER SWITCH                     |                                  |                                                                                                                      |     |      |      |       |

| Input Voltage Range              | V <sub>SWIN</sub>                | V <sub>SWIN</sub> ≤ V <sub>CC</sub>                                                                                  | 1.8 |      | 5.5  | V     |

| Quiescent Supply<br>Current      | I <sub>Q_SW</sub>                | I <sub>SWOUT</sub> = 0A                                                                                              |     | 0.05 | 0.09 | μА    |

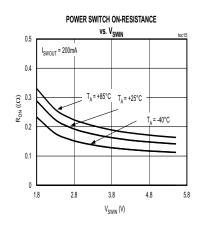

| Switch On-Resistance             | P                                | I <sub>SWOUT</sub> = 200mA                                                                                           |     | 0.16 | 0.25 | 0     |

| Switch On-Resistance             | R <sub>ON_</sub> sw              | V <sub>SWIN</sub> = 1.8V, I <sub>SWOUT</sub> = 200mA                                                                 |     | 0.27 | 0.5  | Ω     |

| Maximum Output<br>Current        | ISWOUT_MAX                       |                                                                                                                      | 200 |      |      | mA    |

| Turn On Time                     |                                  | $I_{SWOUT}$ = 0mA, $C_{SWOUT}$ = 100 $\mu$ F, time from 10% to 90% of $V_{SWIN}$ , SWSoftStart = 0                   |     | 0.65 |      | ms    |

| Turn-On Time                     | t <sub>ON_SW</sub>               | I <sub>SWOUT</sub> = 0mA, C <sub>SWOUT</sub> = 100μF, time from 10% to 90% of V <sub>SWIN</sub> , SWSoftStart = 1    |     | 13.8 |      | ms    |

| Short-Circuit Current<br>Limit   | I <sub>SHRT_SW</sub>             | V <sub>SWOUT</sub> = GND, SWSoftStart = 0                                                                            | 200 | 460  | 700  | mA    |

| Soft-Start Current Limit         | I <sub>SSTR_SW</sub>             | V <sub>SWOUT</sub> = GND, SWSoftStart = 1                                                                            | 9   | 25   | 54   | mA    |

| Thermal-Shutdown<br>Threshold    | T <sub>SHDN_SW</sub>             | T <sub>J</sub> rising                                                                                                |     | 150  |      | °C    |

| Thermal-Shutdown<br>Hysteresis   | T <sub>SHDN_HYST_SW</sub>        |                                                                                                                      |     | 20   |      | °C    |

| BUCK BOOST CONVER                | RTER (C <sub>OUT</sub> = 10MF, I | = 4.7MF, unless otherwise noted.)                                                                                    |     |      |      |       |

| Input Voltage Range              | V <sub>HVIN</sub>                |                                                                                                                      | 1.8 |      | 5.5  | V     |

| Quiescent Supply                 | 1                                | V <sub>HVOUT</sub> = 4V, I <sub>HVOUT</sub> = 0A,<br>BIN UVLO disabled                                               |     | 1.1  | 2.6  |       |

| Current                          |                                  | V <sub>HVOUT</sub> = 4V, I <sub>HVOUT</sub> = 0A,<br>BIN UVLO enabled                                                |     | 1.3  | 3    | - μΑ  |

| Minimum Input Voltage<br>Startup | V <sub>HVIN_</sub> STUP          | I <sub>LOAD</sub> = 1mA, minimum input<br>voltage for correct startup of the<br>buck-boost                           | 1.9 |      |      | V     |

| Maximum Output Operating Power   | Рмахнуоит                        | V <sub>HVIN</sub> = 3V                                                                                               | 250 |      |      | mW    |

| Output Voltage                   | V <sub>HVOUT</sub>               | 100mV step                                                                                                           | 2.5 |      | 5    | V     |

| Output Accuracy                  | ACC <sub>HVOUT</sub>             | I <sub>HVOUT</sub> = 1mA, average output<br>C <sub>OUT</sub> ≥ 10µF                                                  | -3  |      | +3   | %     |

| Line Regulation Error            | V <sub>H</sub> VINREG_BOOST      | V <sub>HVIN</sub> = 1.8V to 5.5V,<br>I <sub>HVOUT</sub> = 10uA, V <sub>HVOUT</sub> = 4V,<br>I <sub>SET</sub> = 100mA | -1  | 0.1  | +1   | %/V   |

## **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                | SYMBOL                          | CONDITIONS                                                                                                  | MIN  | TYP  | MAX  | UNITS  |

|------------------------------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|------|------|------|--------|

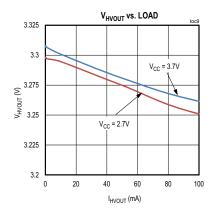

| Load Regulation Error                    | egulation Error V. OADDEO DOCCE | V <sub>HVOUT</sub> = 4V, I <sub>HVOUT</sub> = 10μA to 50mA, I <sub>SET</sub> = 100mA                        |      | 100  |      | mV/A   |

| Load Negulation Error                    | VLOADREG_BOOST                  | V <sub>HVOUT</sub> = 4V, I <sub>HVOUT</sub> = 10μA to 100mA, I <sub>SET</sub> = 100mA                       |      | 310  |      | IIIV/A |

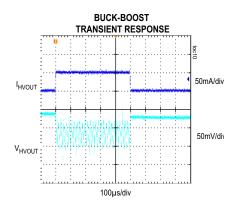

| Line Transient                           | VLINETRAN_BST                   | $V_{HVOUT}$ = 4V, $I_{SET}$ = 100mA,<br>$V_{HVIN}$ = $V_{CC}$ = 2.5V to 5V,<br>0.2µs rise time              |      | 15   |      | mV     |

|                                          |                                 | I <sub>HVOUT</sub> = 0mA to 10mA, 200ns rise time, V <sub>HVOUT</sub> = 4V, I <sub>SET</sub> = 100mA        |      | 9    |      |        |

| Load Transient                           | VLOADTRAN_BST                   | I <sub>HVOUT</sub> = 0mA to 100mA,<br>200ns rise time, V <sub>HVOUT</sub> = 4V,<br>I <sub>SET</sub> = 100mA |      | 31   | mV   | mV     |

| Oscillator Frequency                     | fosc_bst                        |                                                                                                             | 1.78 | 2    | 2.25 | MHz    |

| Passive Discharge<br>Pulldown Resistance | R <sub>PDL_BST</sub>            |                                                                                                             | 5    | 10   | 16   | kΩ     |

| Active Discharge<br>Current              | I <sub>ACTDL_BST</sub>          | V <sub>HVIN</sub> = 3V                                                                                      | 6    | 19   | 38   | mA     |

| Turn-On Time                             | ton_boost                       | Time from enable to full current capability                                                                 |      | 100  |      | ms     |

| UVLO on HVOUT                            | V <sub>H</sub> VOUT_UVLO        | UVLO voltage on HVOUT rising                                                                                | 1.6  | 1.75 | 1.9  | V      |

| UVLO Threshold<br>Hysteresis             | V <sub>UVLO_HYS</sub>           |                                                                                                             |      | 150  |      | mV     |

| Precharge Current                        | I <sub>PC_BOOST</sub>           | Precharge current. V <sub>HVIN</sub> = 1.8V,<br>V <sub>HVOUT</sub> = 1.65V                                  | 4    | 6.5  | 9    | mA     |

| Startup Input Current                    | I <sub>INSTUP_BST</sub>         | Input startup current. V <sub>HVIN</sub> = 1.8V,<br>V <sub>HVOUT</sub> = 1.6V                               |      | 11   |      | mA     |

| Startup Output Current                   | I <sub>OSTUP_BST</sub>          | Output startup current.<br>V <sub>HVIN</sub> = 1.8V, V <sub>HVOUT</sub> = 5V                                |      | 6.5  |      | mA     |

| Pulse Mode Input<br>Current Limit        | I <sub>PLS_IN</sub>             | $V_{HVOUT}$ = 4V, $V_{HVIN}$ < $V_{HVOUT}$ - 0.5V, $f_{SW}$ = $f_{OSC}/10$ , $I_{SET}$ = 100mA              |      | 6.6  |      | mA     |

| Pulse Mode Switching<br>Period Ratio     | T <sub>RATIO</sub>              | f <sub>OSC</sub> /f <sub>SW</sub> , 128 steps                                                               | 10   |      | 138  |        |

| Short-Circuit Peak<br>Current Limit      | ISHRT_BOOST                     | V <sub>HVOUT</sub> = GND.                                                                                   | 0.4  | 1.1  | 1.9  | А      |

| Thermal-Shutdown<br>Threshold            | T <sub>SHDN_BST</sub>           | T <sub>J</sub> rising                                                                                       |      | 150  |      | °C     |

| Thermal-Shutdown<br>Hysteresis           | T <sub>SHDN_HYST_BST</sub>      |                                                                                                             |      | 21   |      | °C     |

## **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                 | SYMBOL                     | CONDITIONS                                                                                          | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------|------|------|------|-------|

| BUCK CONVERTER (C                         | OUT = 10MF, L = 2.2MI      | H, unless otherwise noted.)                                                                         |      |      |      |       |

| Input Voltage Range                       | V <sub>BIN</sub>           |                                                                                                     | 1.8  |      | 5.5  | V     |

|                                           |                            | I <sub>BOUT</sub> = 0A                                                                              |      | 0.8  | 1.6  |       |

| Quiescent Supply<br>Current               | I <sub>Q_BUCK</sub>        | I <sub>BOUT</sub> = 0A, BIN UVLO enabled                                                            |      | 1    | 2    | μA    |

| Carron                                    |                            | I <sub>BOUT</sub> = 0A, BuckMd[1:0] = 01                                                            |      |      | 4.8  | mA    |

| Maximum Operative Output Current          | I <sub>MAXBOUT</sub>       |                                                                                                     | 250  |      |      | mA    |

| Output Voltage                            | V <sub>BOUT</sub>          | 25mV step                                                                                           | 1    |      | 2    | V     |

| Output Accuracy                           | A <sub>CC_BOUT</sub>       | V <sub>BIN</sub> = (V <sub>BOUT</sub> + 0.1V) or higher,<br>I <sub>BOUT</sub> = 1mA; average output | -3   |      | +3   | %     |

| Dropout Voltage                           | V <sub>DROP_BUCK</sub>     | I <sub>BOUT</sub> = 0A                                                                              |      | 95   | 120  | mV    |

| Line Regulation Error                     | V <sub>LINEREG_BUCK</sub>  | V <sub>BIN</sub> = from 2V to 5V,<br>V <sub>BOUT</sub> = 1.2V                                       |      | 0.65 |      | %/V   |

| Load Regulation Error                     | VLOADREG_BUCK              | BuckInteg = 1, I <sub>BOUT</sub> = 200mA                                                            |      | 23   |      | mV    |

| Line Transient                            | V <sub>LINETRAN_BUCK</sub> | $V_{BOUT}$ = 1.2V, $V_{BIN}$ = $V_{CC}$ : 2.0V to 5V, 1 $\mu$ s rise time                           |      | 50   |      | mV    |

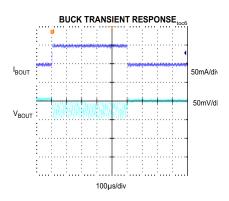

| Load Transient                            | V <sub>LOADTRAN_BUCK</sub> | I <sub>BOUT</sub> = 0mA to 200mA, 200ns rise time                                                   |      | 70   |      | mV    |

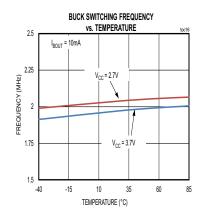

| Oscillator Frequency                      | fosc_bk                    |                                                                                                     | 1.78 | 2    | 2.25 | MHz   |

| Passive Discharge<br>Pull-Down Resistance | R <sub>PDL_BK</sub>        |                                                                                                     | 5    | 10   | 16   | kΩ    |

| Active Discharge<br>Current               | I <sub>ACTDL_BK</sub>      |                                                                                                     | 5.5  | 17   | 33   | mA    |

| T 0 T                                     |                            | Time from enable to full current capability; BuckFst = 0                                            |      | 60   |      |       |

| Turn-On Time                              | ton_Buck                   | Time from enable to full current capability; BuckFst = 1                                            |      | 30   |      | ms    |

| Startup Output Current                    | I <sub>STUP_BK</sub>       | BuckFst = 0                                                                                         |      | 18   |      | mA    |

| Startup Output Current                    | I <sub>STUP_BK</sub>       | BuckFst = 1                                                                                         |      | 42   |      | mA    |

| Short-Circuit Peak<br>Current Limit       | I <sub>SHRT_BUCK</sub>     | V <sub>BOUT</sub> = GND.                                                                            | 0.54 | 0.8  | 2.19 | А     |

| Thermal-Shutdown<br>Threshold             | T <sub>SHDN_BUCK</sub>     | T <sub>J</sub> rising                                                                               |      | 150  |      | °C    |

| Thermal-Shutdown<br>Hysteresis            | TSHDN_HYST_BUCK            |                                                                                                     |      | 21   |      | °C    |

|                                           |                            |                                                                                                     |      |      |      |       |

#### **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                | SYMBOL                    | CONDITIONS                                                                       | MIN                     | TYP   | MAX   | UNITS |  |

|------------------------------------------|---------------------------|----------------------------------------------------------------------------------|-------------------------|-------|-------|-------|--|

| LDO (C <sub>LOUT</sub> = 1µF, uni        | ess otherwise noted.      | Typical values are with I <sub>LOUT</sub> = 10m                                  | ıA, V <sub>LOUT</sub> = | = 2V) |       |       |  |

| Innut Valta na Danna                     |                           | LDO mode                                                                         | 1.71                    |       | 5.5   |       |  |

| Input Voltage Range                      | V <sub>LIN</sub>          | Switch mode                                                                      | 1.2                     |       | 5.5   | V     |  |

|                                          |                           | I <sub>LOUT</sub> = 0A                                                           |                         | 0.9   | 1.9   |       |  |

| Quiescent Supply<br>Current              | I <sub>Q_LDO</sub>        | I <sub>LOUT</sub> = 0A, LIN UVLO enabled                                         |                         | 1.1   | 2.2   | μΑ    |  |

| CuCi.ii                                  |                           | I <sub>LOUT</sub> = 0A, switch mode                                              |                         | 0.3   | 0.5   |       |  |

| Quiescent Supply<br>Current in dropout   | I <sub>Q_LDO_DRP</sub>    | I <sub>LOUT</sub> = 0A, V <sub>SET</sub> = 2.8V                                  |                         | 2.1   | 4.6   | μA    |  |

| Maximum Output                           | 1                         | V <sub>LIN</sub> > 1.8V                                                          | 100                     |       |       | m Λ   |  |

| Current                                  | ILOUT_MAX                 | V <sub>LIN</sub> = 1.8V or lower                                                 | 50                      |       |       | mA    |  |

| Output Voltage                           | V <sub>LOUT</sub>         | 100mV step                                                                       | 0.9                     |       | 4     | V     |  |

| Output Accuracy                          | ACC <sub>LDO</sub>        | $V_{LIN}$ = ( $V_{LOUT}$ + 0.5V) or higher,<br>$I_{LOUT}$ = 1mA                  | -3.1                    |       | +3.1  | %     |  |

| Dropout Voltage                          | V <sub>DROP_LDO</sub>     | V <sub>LIN</sub> = V <sub>SET</sub> = 2.7V,<br>I <sub>LOUT</sub> = 100mA         |                         | -     | 100   | mV    |  |

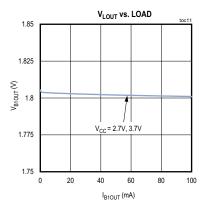

| Line Regulation Error                    | V <sub>LINEREG_LDO</sub>  | V <sub>LIN</sub> = (V <sub>LOUT</sub> + 0.5 V) to 5.5V                           | -0.5                    |       | +0.5  | %/V   |  |

| Load Regulation Error                    | V <sub>LOADREG_LDO</sub>  | V <sub>LIN</sub> = 1.8V or higher,<br>I <sub>LOUT</sub> = 100μA to 100mA         |                         | 0.001 | 0.005 | %/mA  |  |

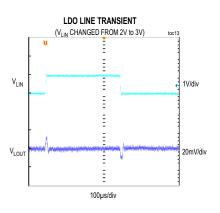

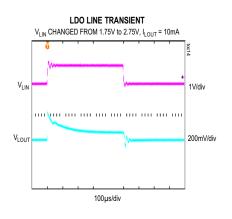

| Line Transient                           | V <sub>LINETRAN_LDO</sub> | V <sub>LIN</sub> = 4V to 5V, 200ns rise time                                     |                         | ±35   |       | \/    |  |

| Line Transient                           |                           | V <sub>LIN</sub> = 4V to 5V,1µs rise time                                        |                         | ±25   |       | mV    |  |

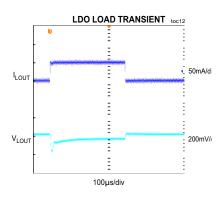

| Load Transient                           | V <sub>LOADTRAN_LDO</sub> | I <sub>LOUT</sub> = 0mA to 10mA,<br>200ns rise time                              |                         | 100   |       | m)/   |  |

| Load Transient                           |                           | I <sub>LOUT</sub> = 0mA to 100mA,<br>200ns rise time                             |                         | 200   |       | – mV  |  |

| Passive Discharge<br>Pulldown Resistance | R <sub>PDL_LDO</sub>      |                                                                                  | 4                       | 10    | 18    | kΩ    |  |

| Active Discharge<br>Current              | I <sub>ACTDL_LDO</sub>    |                                                                                  | 5                       | 20    | 40    | mA    |  |

| Switch Mode                              | D                         | V <sub>LIN</sub> = 1.8V, I <sub>LOUT</sub> = 50mA                                |                         |       | 1     | Ω     |  |

| Resistance                               | R <sub>ON_LDO</sub>       | V <sub>LIN</sub> = 1.2V, I <sub>LOUT</sub> = 5mA                                 |                         |       | 3     | 12    |  |

| Turn-On Time                             | ta                        | I <sub>LOUT</sub> = 0mA , time from 10% to 90% of final regulation value         |                         | 0.95  |       | me    |  |

|                                          | ton_ldo                   | I <sub>LOUT</sub> = 0mA , time from 10% to 90% of V <sub>LIN</sub> , Switch mode |                         | 1.8   |       | - ms  |  |

| Short-Circuit Current                    | I <sub>SHRT_LDO</sub>     | V <sub>LOUT</sub> = GND                                                          |                         | 380   |       |       |  |

| Limit                                    | _                         | V <sub>LOUT</sub> = GND, Switch mode                                             |                         | 370   |       | mA    |  |

#### **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                          | SYMBOL                   | CONDITIONS                                                                            | MIN TY | P MAX | UNITS             |

|----------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------|--------|-------|-------------------|

| Thermal-Shutdown Threshold                         | <sup>t</sup> SHDN_LDO    | T <sub>J</sub> rising                                                                 | 15     | 0     | °C                |

| Thermal-Shutdown<br>Hysteresis                     | tshdn_hyst_ldo           |                                                                                       | 21     |       | °C                |

|                                                    |                          | 10Hz to 100kHz, V <sub>LIN</sub> = 5V,<br>V <sub>LOUT</sub> = 3.3V                    | 15     | 0     |                   |

| Outset Naiss                                       | OUT                      | 10Hz to 100kHz, V <sub>LIN</sub> = 5V,<br>V <sub>LOUT</sub> = 2.5V                    | 12     | 5     |                   |

| Output Noise                                       | OUT <sub>NOISE_LDO</sub> | 10Hz to 100kHz, V <sub>LIN</sub> = 5V,<br>V <sub>LOUT</sub> = 1.2V                    | 90     | )     | μV <sub>RMS</sub> |

|                                                    |                          | 10Hz to 100kHz, V <sub>LIN</sub> = 5V,<br>V <sub>LOUT</sub> = 0.9V                    | 80     | )     |                   |

| BATTERY IMPEDANCE                                  | MEASUREMENT              |                                                                                       |        |       |                   |

| SWOUT Allowed<br>Supply Range                      | V <sub>SWOUT</sub>       |                                                                                       | 2      | 5.5   | V                 |

| SWOUT UVLO                                         | U <sub>VLOSWOUT</sub>    | Falling edge                                                                          | 1.92   | 2     | V                 |

| SWOUT UVLO<br>Hysteresis                           | U <sub>VLOHYST</sub>     | Hysteresis                                                                            | 30     | )     | mV                |

| V <sub>CC</sub> Impedance Test<br>Current Range    | I <sub>BIM_CUR</sub>     | Programmable current source with step change of 2x                                    | 250    | 8000  | μА                |

| V <sub>CC</sub> Impedance Test<br>Current Accuracy | I <sub>BIM_ACC</sub>     | V <sub>CC</sub> > 1.2V                                                                | -10    | 10    | %                 |

| V <sub>CC</sub> Input Divider<br>Resistance        | R <sub>VCC</sub>         | V <sub>CC</sub> measure enabled                                                       | 1.5    | 5     | МΩ                |

| Measurable V <sub>CC</sub><br>Voltage Range        | V <sub>CC_FS</sub>       | Allowed V <sub>CC</sub> voltages range for SAR ADC operation                          | 1.2    | 3.6   | V                 |

| V <sub>CC</sub> Voltage Resolution LSB             | V <sub>CC_LSB</sub>      |                                                                                       | 10.    | 2     | mV                |

| Worst-Case Accuracy                                | .,                       | V <sub>CC</sub> = 1.2V                                                                | -72    | +72   | .,                |

| of Single V <sub>CC</sub><br>Measurement           | V <sub>CC_ACC</sub>      | V <sub>CC</sub> = 3.6V                                                                | -100   | +100  | – mV              |

| Worst-Case Accuracy                                | .,                       | V <sub>CC1</sub> – V <sub>CC2</sub> = 100mV                                           | -22    | +22   | 0/                |

| of Differential V <sub>CC</sub><br>Measurement     | VCC_ACC_DIFF             | V <sub>CC1</sub> - V <sub>CC2</sub> = 1.0V                                            | -3.5   | +3.5  | - %               |

| V <sub>CC</sub> Voltage Wait Time<br>Accuracy      | twait_acc                | 10ms, 100ms, 1s programmable twait                                                    | -10    | +10   | %                 |

| SAR ADC V <sub>CC</sub> Voltage<br>Conversion Time | t <sub>CONV</sub>        | Actual full V <sub>CC</sub> measurement time is t <sub>WAIT</sub> + t <sub>CONV</sub> | 12     | 0     | μs                |

## **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                                    | SYMBOL                      | CONDITIONS                                              | MIN                     | TYP    | MAX  | UNITS |

|--------------------------------------------------------------|-----------------------------|---------------------------------------------------------|-------------------------|--------|------|-------|

| MONITOR MULTIPLEXE                                           | R                           |                                                         |                         |        |      |       |

| SWIN To MON Switch<br>Resistance                             | R <sub>MON_SWIN</sub>       | V <sub>SWIN</sub> > 1.8V, I <sub>LOAD</sub> = 2mA       |                         | 80     | 120  | Ω     |

| SWOUT/BIN/HVIN/<br>HVOUT/LIN To MON<br>Switch Resistance     | R <sub>MON_HV</sub>         | Sensed pin voltage > 1.8V,<br>I <sub>LOAD</sub> = 500μA |                         |        | 400  | Ω     |

| LOUT/BOUT To MON<br>Switch Resistance                        | R <sub>MON_LV</sub>         | Sensed pin voltage > 0.9V,<br>I <sub>LOAD</sub> = 500µA |                         |        | 500  | Ω     |

| BBM Time                                                     | t <sub>BBM</sub>            | Anytime MONCtr[2:0] changed                             |                         | 80     |      | μs    |

| Pulldown Resistance                                          | R <sub>MON_PD</sub>         | MONHiZ = 0                                              |                         | 100    |      | kΩ    |

| UVLO/POR                                                     |                             |                                                         |                         |        |      |       |

| Input Voltage Range                                          | V <sub>VCC</sub>            |                                                         | 1.8                     |        | 5.5  | V     |

| BIN UVLO Threshold<br>Rising                                 | V <sub>TH_BIN_RISE</sub>    |                                                         | 1.68                    | 1.73   | 1.77 | V     |

| BIN UVLO Threshold Falling                                   | V <sub>TH_BIN_FALLING</sub> |                                                         | 1.66                    | 1.71   | 1.75 | V     |

| LIN UVLO Threshold Rising                                    | V <sub>TH_LIN_RISE</sub>    |                                                         | 1.64                    | 1.68   | 1.72 | V     |

| LIN UVLO Threshold Falling                                   | V <sub>TH_LIN_FALLING</sub> |                                                         | 1.62                    | 1.66   | 1.7  | V     |

| DOD E III                                                    | .,                          | Seal mode                                               | 0.76                    | 1.21   |      |       |

| POR Falling                                                  | VTH_POR_FALLING             | No seal mode                                            | 1.55                    | 1.66   | 1.77 | V     |

| DOD Dining                                                   |                             | Seal mode                                               |                         | 1.27   | 1.71 | \ \/  |

| POR Rising                                                   | VTH_POR_RISING              | No seal mode                                            | 1.58                    | 1.69   | 1.8  | V     |

| DIGITAL SIGNALS (V <sub>CC</sub>                             | = 1.8V to 5.5V, unles       | s otherwise noted. Typical values a                     | re at V <sub>CC</sub> = | 2.7V.) |      |       |

| Input Logic-High (SDA,<br>SCL,SWEN,KIN,<br>BEN,MPC,LEN,HVEN) | V <sub>IH</sub>             | No seal mode                                            | 1.4                     |        |      | V     |

| Input Logic-Low (SDA, SCL,SWEN,KIN,                          | V <sub>IL</sub>             | No seal mode                                            |                         |        | 0.45 |       |

| BEN,MP,LEN,HVEN)                                             | VIL                         | No seal mode, V <sub>CC</sub> ≥ 2.7V                    |                         |        | 0.5  | V     |

| Input Logic-High, Seal                                       | V                           | Seal mode                                               | 4.1                     |        |      | V     |

| Mode (SDA, SCL, $\overline{\text{KIN}}$ , MPC)               | VIH_SEAL                    | Seal mode, V <sub>CC</sub> ≥ 2.7V                       | 2.2                     |        |      | V     |

#### **Electrical Characteristics (continued)**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = -40^{\circ}C$  to +85°C, all registers in their default state, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                              | SYMBOL               | CONDITIONS            | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------|----------------------|-----------------------|-----|-----|-----|-------|

| Input Logic-Low,<br>Seal Mode (SDA, SCL,<br>KIN, MPC)  | V <sub>IL_SEAL</sub> | Seal mode             |     |     | 0.5 | V     |

| Output Logic-Low (SDA, RST, KOUT)                      | V <sub>OL</sub>      | I <sub>OL</sub> = 4mA |     |     | 0.4 | V     |

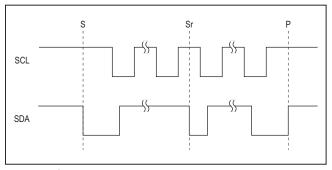

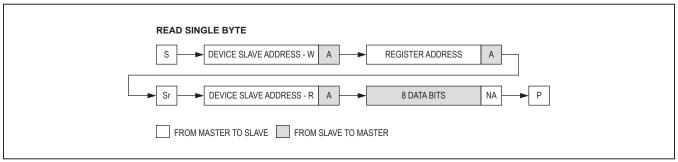

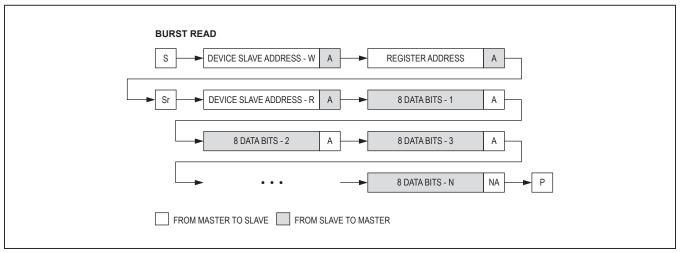

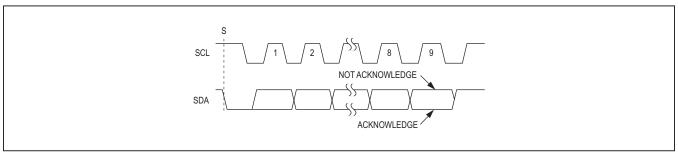

| SCL Clock Frequency                                    | f <sub>SCL</sub>     |                       | 0   |     | 400 | kHz   |

| KIN Pullup Resistance                                  | R <sub>KIN</sub>     |                       |     | 210 |     | kΩ    |

| Bus Free Time Between<br>a Stop and Start<br>Condition | <sup>t</sup> BUF     |                       | 1.3 |     |     | μs    |

| Start Condition<br>(Repeated) Hold Time                | <sup>t</sup> HD:STA  | (Note 2)              | 0.6 |     |     | μs    |

| Low Period of SCL<br>Clock                             | t <sub>LOW</sub>     |                       | 1.3 |     |     | μs    |

| High Period of SCL<br>Clock                            | <sup>t</sup> HIGH    |                       | 0.6 |     |     | μs    |

| Setup Time for a<br>Repeated Start<br>Condition        | <sup>t</sup> su:sta  |                       | 0.6 |     |     | μs    |

| Data Hold Time                                         | t <sub>HD:DAT</sub>  | (Note 3)              | 0   |     | 0.9 | μs    |

| Data Setup Time                                        | <sup>t</sup> su:dat  |                       | 100 |     |     | ns    |

| Setup Time for Stop<br>Condition                       | tsu:sto              |                       | 0.6 |     |     | μs    |

| Spike Pulse Widths<br>Suppressed by Input<br>Filter    | t <sub>SP</sub>      |                       | 50  |     |     | ns    |

Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Limits over the operating temperature range are guaranteed by design.

Note 2:  $f_{SCL}$  must meet the minimum clock low time plus the rise/fall times.

Note 3: The maximum t<sub>HD:DAT</sub> has to be met only if the device does not stretch the low period (t<sub>LOW</sub>) of the SCL signal.

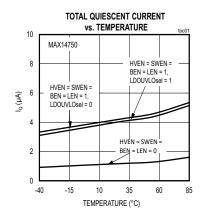

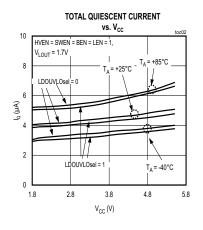

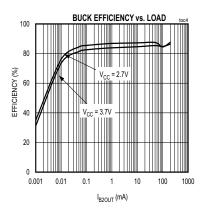

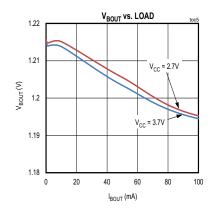

#### **Typical Operating Characteristics**

$(V_{CC} = V_{BIN} = V_{LIN} = V_{HVIN} = V_{SWIN} = 2.7V$ ,  $T_A = +25$ °C, all registers in their default state, unless otherwise noted.)

#### **Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = V<sub>BIN</sub> = V<sub>LIN</sub> = V<sub>HVIN</sub> = V<sub>SWIN</sub> = 2.7V, T<sub>A</sub> = +25°C, all registers in their default state, unless otherwise noted.)

#### **Bump Configurations**

#### **Bump Description**

| BU                    | BUMP                  |                                                             | BUMP                                                                                               |  | FUNCTION |

|-----------------------|-----------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|----------|

| MAX14720              | MAX14750              | NAME                                                        | FUNCTION                                                                                           |  |          |

| A1                    | A1                    | BIN                                                         | Buck Regulator Input (must be connected to HVIN on the board). Bypass with a 1µF capacitor to GND. |  |          |

| A2                    | A2                    | BLX                                                         | Buck Regulator Switch                                                                              |  |          |

| A3                    | A3                    | BOUT                                                        | Buck Regulator Output. Bypass with a 10µF capacitor to GND.                                        |  |          |

| A4                    | A4 LIN                |                                                             | LDO Input. Bypass with a 1µF capacitor to GND.                                                     |  |          |

| A5                    | A5                    | LOUT                                                        | LDO Output. Bypass with a 1µF capacitor to GND.                                                    |  |          |

| B1                    | B1                    | MON                                                         | Monitor Multiplexer Output                                                                         |  |          |

| B2, B3, C2,<br>C3, D2 | B2, B3, C2,<br>C3, D2 | GND                                                         | Ground                                                                                             |  |          |

| B4                    | B4                    | V <sub>CC</sub>                                             | Power Supply Input                                                                                 |  |          |

| B5                    | B5                    | SWIN                                                        | Power Switch Input. SWIN ≤ V <sub>CC</sub>                                                         |  |          |

| C1                    | C1                    | C1 SDA Open-Drain I <sup>2</sup> C Serial Data Input/Output |                                                                                                    |  |          |

| C4                    | _                     | MPC                                                         | Multipurpose Control Input                                                                         |  |          |

| _                     | C4                    | BEN                                                         | Active-High Buck Regulator Enable Input                                                            |  |          |

#### **Bump Description (continued)**

| BU       | MP       | NAME  | FUNCTION                                                                                                |

|----------|----------|-------|---------------------------------------------------------------------------------------------------------|

| MAX14720 | MAX14750 | NAME  | FUNCTION                                                                                                |

| C5       | C5       | SWOUT | Power Switch Output. Bypass with a 100µF capacitor to GND for battery impedance measurement.            |

| D1       | D1       | SCL   | I <sup>2</sup> C Serial Clock                                                                           |

| D3       | _        | KIN   | KEY Input. Active-low button monitor with internal 210kΩ pullup.                                        |

| _        | D3       | SWEN  | Active-High Power Switch Enable Input                                                                   |

| D4       | _        | RST   | Active-Low, Open-Drain Reset Output                                                                     |

| _        | D4       | LEN   | Active-High Linear Regulator Enable Input                                                               |

| D5       | D5       | CAP   | Internal Power Decoupling. Bypass with a 0.1µF capacitor to GND.                                        |

| E1       | E1       | HVOUT | Buck-Boost Regulator Output. Bypass with a 10µF capacitor to GND.                                       |

| E2       | E2       | HVOLX | Buck-Boost Regulator Boost Switch                                                                       |

| E3       | E3       | HVILX | Buck-Boost Regulator Buck Switch                                                                        |

| E4       | E4       | HVIN  | Buck-Boost Regulator Input (Must be Connected to BIN on the Board). Bypass with a 1μF capacitor to GND. |

| E5       | _        | KOUT  | KEY Output. Active-low, open-drain buffered copy of KIN.                                                |

| _        | E5       | HVEN  | Active-High Buck-Boost Regulator Enable Input                                                           |

**Note:** All capacitance values listed in this document refer to effective capacitance. Be sure to specify capacitors that will meet these requirements under typical system operating conditions taking into consideration the effects of voltage and temperature.

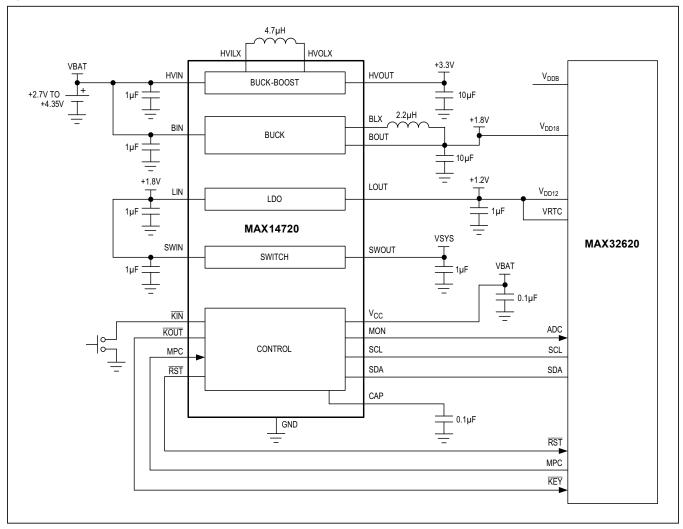

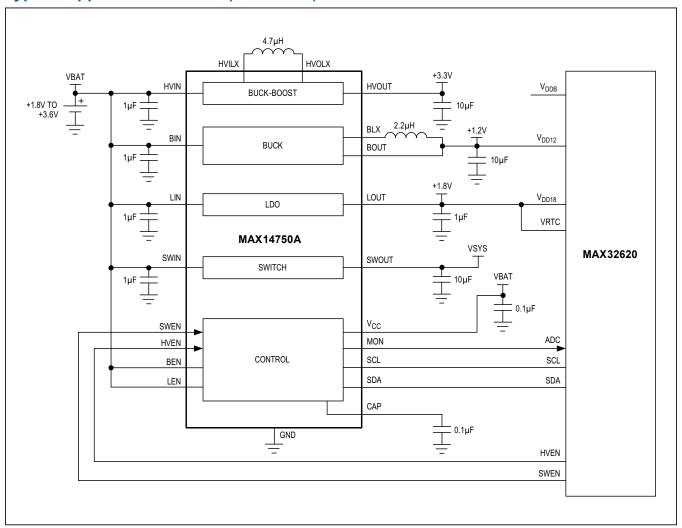

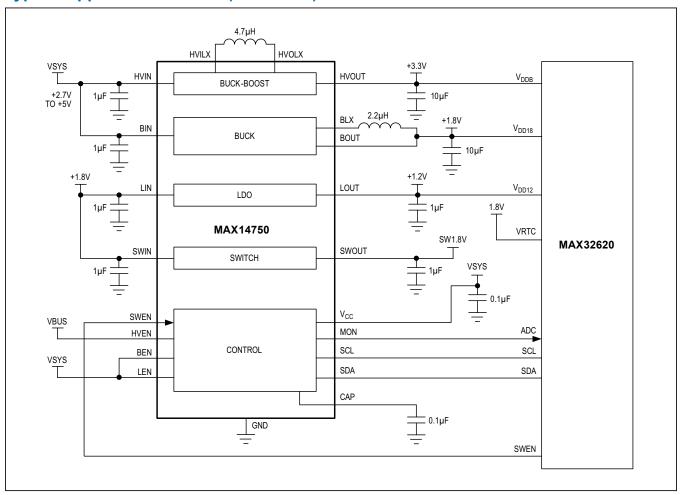

#### **Block Diagram**

#### **Detailed Description**

#### **Power Regulation**

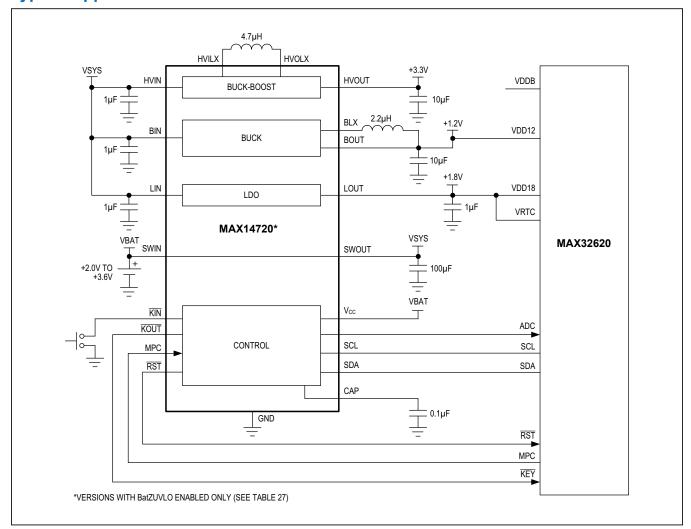

The MAX14720/MAX14750 include a buck-boost regulator, a synchronous buck regulator, a low quiescent current linear regulator, and a power switch with integrated battery monitoring. Burst mode operation of the switching regulators provides excellent light-load efficiency and allows the switching regulators to run continuously without significant energy cost.

The buck-boost regulator in the devices is suitable for applications (such as low-power display biasing) that need the voltage present continuously while running from a battery. The buck-boost regulator can also operate in a current-limited mode to reduce current surges to the supply. The current-limiting is implemented by dividing down the frequency of the switching and is dependent on the ratio of the input-to-output voltage. Step-down operation is not allowed when current-limiting is active.

#### **UVLO**

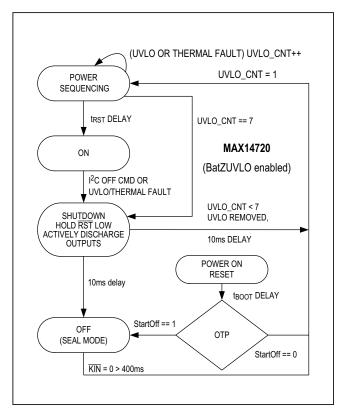

In addition to the internal power-on-reset (POR) circuit, the devices also have two UVLO circuits that monitor the voltages on BIN and LIN pin to ensure that input voltages are sufficient for proper operation. It is required that the boost and buck-boost are powered from the same voltage so they share a UVLO on the BIN pin. The LDO has its own UVLO on the LIN pin. The UVLO circuits are disabled when the blocks are not enabled to reduce the quiescent current. The devices provide the ability to select which of the two UVLOs are used so that applications with BIN and LIN tied to the

same supply can share a single UVLO to reduce quiescent current. The selection is made in the UVLOCfg register and the effects of the different settings are shown in the Table 1. In the MAX14720, if there is a fault in a block that is enabled by the sequencer (every \_Seq[2:0] option except 000, 110 or 111) the part will transition to the shutdown state. The device then waits for the fault to clear before beginning the power on sequence. A fault is any condition that causes the block to turn off when it should be enabled, such as a UVLO condition or thermal shutdown. On MAX14720 versions with BatZUVLO enabled and SWSeq = 001 (always on), the load switch is kept on even in the event of a fault. This allows the device to recover from UVLO fault conditions when it is connected as shown in Figure 11. On devices with these options, in the case of a fault during the power sequencing, a retry counter is incremented. If seven failures in a row occur, retries are aborted and the device returns to OFF mode.

#### **Output Discharge**

The regulators include circuitry to discharge their outputs. Active discharge applies a current sink, while passive discharge applies a load resistor. The active discharge is enabled during hard reset, or for 10ms as the part enters the off/seal mode. It can also be activated in the on state by a register bit when the regulator is disabled. Passive discharge is applied in the off/seal mode if the GlbPasDsc bit is set and can also be applied in the on state by a register bit when the regulator is disabled.

**Table 1. UVLO Configuration**

| UVLOCfg | BBBUVLOsel | LDOUVLOsel | BIN UVLO | LIN UVLO |

|---------|------------|------------|----------|----------|

| 0x00    | LIN        | LIN        | Disabled | Enabled  |

| 0x01    | LIN        | BIN        | Enabled  | Enabled  |

| 0x02    | BIN        | LIN        | Enabled  | Enabled  |

| 0x03    | BIN        | BIN        | Enabled  | Disabled |

#### Power On/Off and Reset Control

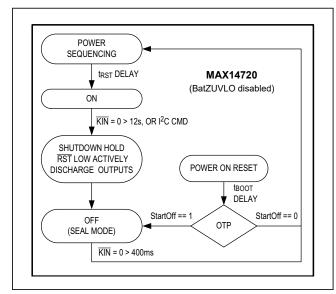

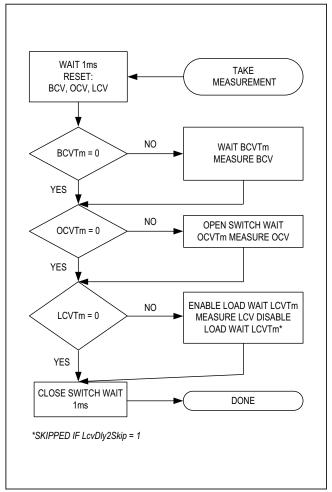

The MAX14750 provides individual enable pins for each of the primary functions, while the MAX14720 includes a push-button monitor and sequencing controller. Figure 1 shows the basic flow diagram for the power-management control inside the MAX14720. Each primary function of the MAX14720 can be automatically enabled by the sequencing controller. The functions can default to be controlled by the I<sup>2</sup>C configuration registers. The default state is determined by the factory configuration. See I<sup>2</sup>C Register Descriptions section for more information.

When the device begins the shutdown process, reset is driven low, all functions are disabled and outputs are actively discharged. Then, 10ms later, the device will be in the off state (seal mode) where all functions are disabled except for the power button monitor.

#### **Power Sequencing**

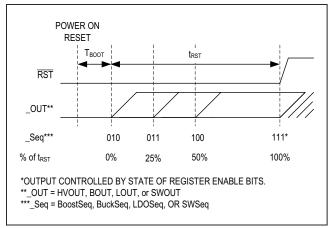

The sequencing of the voltage regulators during power-on is configurable. Each regulator can be configured to be turned on at one of four points during the power-on process. The four points are:  $t_{\rm BOOT}$  after the power-on event, after the  $\overline{\rm RST}$  signal is released, or at two points in between. The two points in between are fixed proportionally to the duration of the POR process, but the overall time of the reset delay is configurable at 80ms, 120ms, 220ms, and 420ms. (Note that the actual turn-on time of some converters may be limited by the soft-starting of the output.) Figure 3 shows the timing relationship. Additionally, the

Figure 1. Power State Diagram for MAX14720

regulators can be preselected to default off and can be turned on with an I<sup>2</sup>C command after reset is released.

## Battery Impedance Measurement (MAX14720, BatZUVLO Enabled Only)

The MAX14720 contains circuitry to measure the impedance of the power supply. To perform this measurement, SWIN must be connected to  $V_{CC}$ , with no capacitor present on the battery-side; all loads draw their power from the power-switch output (see <u>Typical Application Circuits</u>).

By default, the power switch is configured with a soft-start current limit that prevents potential high current drawn from the battery. This soft-start lasts 60ms after the power switch is turned on.

During battery measurement, the impedance measurement circuitry will open the power switch and record the voltage at the input to the switch before and after a current load is applied. During the measurement, the system must rely on the energy stored in the capacitor attached to the output of the switch for operation. If the SWOUT voltage falls below SWOUT UVLO threshold, the battery measurement is immediately aborted and the power switch closes.

Figure 2. BatZUVLO enabled for MAX14720

The parameters of the current load and the timing of the pulse are specified in registers BatTime(0x0D) and BatCfg(0x0E) when the measurement is requested and the results are presented in registers BatV(0x0F), BatOCV(0x10), and BatLCV(0x11) (see Figure 4). Battery impedance measurement is only available on devices with BatZUVLO enabled (see Table 27).

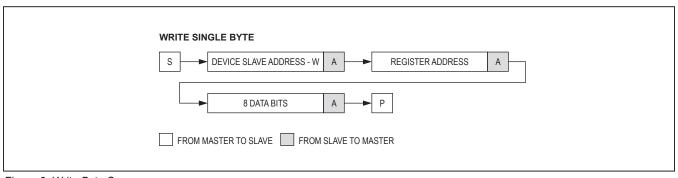

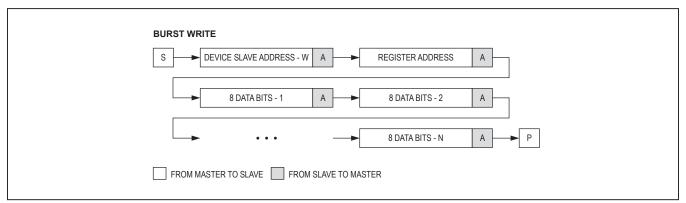

#### I<sup>2</sup>C Interface

The devices use the two-wire I<sup>2</sup>C interface to communicate with the host microcontroller. The configuration settings and status information provided through this interface are detailed in the register descriptions.

#### I<sup>2</sup>C Addresses

The registers of the devices are accessed through the slave address of 010101Ax (A is configurable by OTP).

Figure 3. Reset Sequence Programming (MAX14720)

Figure 4. Battery Impedance Measurement

# 12C Register Map

| )                   | •                |                 |                 |                 |               |                               |                |                |                |

|---------------------|------------------|-----------------|-----------------|-----------------|---------------|-------------------------------|----------------|----------------|----------------|

| REGISTER<br>ADDRESS | REGISTER<br>NAME | B7              | B6              | B5              | B4            | B3                            | B2             | B1             | B0             |

| 00×0                | Chipld           |                 |                 |                 | S             | ChipId[7:0]*                  |                |                |                |

| 0x01                | ChipRev          |                 |                 |                 | Chip          | ChipRev[7:0]*                 |                |                |                |

| 0x02                | Reserved         |                 |                 |                 | Ř             | Reserved                      |                |                |                |

| 0×03                | BoostCDiv        | CIkDivEn        |                 |                 |               | CIkDivSet[6:0]                | 3:0]           |                |                |

| 0x04                | BoostlSet        | ı               | I               | 1               |               |                               |                | BoostlSet[2:0] |                |

| 0x05                | BoostVSet        | 1               | 1               | 1               |               |                               | BoostVSet[4:0] | [6             |                |

| 90×0                | BoostCfg         |                 | BoostSeq[2:0]*  |                 | Boost         | BoostEn[1:0]                  | ı              | BoostEMI       | BoostInd       |

| 0x07                | BuckVSet         | ı               | 1               |                 |               | Buc                           | BuckVSet[5:0]  |                |                |

| 0x08                | BuckCfg          |                 | BuckSeq[2:0]*   |                 | Buck          | BuckEn[1:0]                   | Buck∿          | BuckMd[1:0]    | BuckFst        |

| 60×0                | BucklSet         |                 | BucklSet[2:0]   |                 | BuckCfg       | BuckInd                       | BuckHysOff     | BuckMinOT      | BuckInteg      |

| 0x0A                | LDOVSet          | ı               | ı               | I               |               |                               | LDOVSet[4:0]   |                |                |

| 0x0B                | LDOCfg           |                 | LDOSeq[2:0]*    |                 | LDO<br>PasDSC | LDO<br>ActDSC                 | Грое           | LDOEn[1:0]     | LDOМоdе        |

| 0x0C                | SwitchCfg        |                 | SWSeq[2:0]*     |                 | l             | 1                             | SWE            | SWEn[1:0]      | SWSoftStart    |

| 0x0D                | BatTime          |                 |                 | BCVT            | BCVTm[1:0]    | OCV                           | OCVTm[1:0]     | LCVTm[1:0]     | [1:0]          |

| 0x0E                | BatCfg           | BIA**           | BIMAbort**      |                 | 1             | LcvDly2Skip                   |                | BatlmpCur[2:0] |                |

| 0x0F                | BatBCV           |                 |                 |                 | Ã             | BCV[7:0]*                     |                |                |                |

| 0x10                | BatOCV           |                 |                 |                 | Ó             | OCV[7:0]*                     |                |                |                |

| 0x11                | BatLCV           |                 |                 |                 | ľ             | LCV[7:0]*                     |                |                |                |

| 0x12-0x18           | Reserved         |                 |                 |                 | ı Æ           | Reserved                      |                |                |                |

| 0x19                | MONCfg           | MONEn           | 1               | 1               | 1             | MONHIZ                        |                | MONCtr[2:0]    |                |

| 0x1A                | BootCfg          |                 | PwrRstCfg[3:0]* | [3:0]*          |               | SftRstCfg*                    | PFNPUDCfg*     | BootDly[1:0]*  | [1:0]*         |

| 0x1B                | PinStat          | I               | I               | ı               | I             | KIN/SWEN                      | KOUT/HVEN      | MPC/BEN        | RST/LEN        |

| 0x1C                | BBBExtra         | Boost<br>HysOff | BoostPasDsc     | Boost<br>ActDsc | 1             | I                             | BuckPasDsc     | BuckActDsc     | BuckFScl       |

| 0x1D                | HandShk          | StartOff*       | GlbPasDsc*      | 1               | 1             | ı                             |                | 1              | StayOn         |

| 0x1E                | UVLOCfg          | I               | l               | I               | I             | I                             | I              | BBBUVLOsel*    | LDO<br>UVLOsel |

| 0x1F                | PWROFF           |                 |                 |                 | PWRC          | PWROFFCMD[7:0]                |                |                |                |

| 0x20<br>0x2B        | ОТРМар           |                 |                 |                 | Programmed    | Programmed Default OTP Values | ılues          |                |                |

|                     |                  |                 |                 |                 |               |                               |                |                |                |

Note:

All registers reset to default value on hard and soft reset.

Reserved Bits: Must not be modified from their default states to ensure proper operation.

Bolded Names: Bits default value can be factory configured by OTP. Bolded bits with asterisk are set by OTP only.

\*Read-only \*\*Bits autoreset at the end of impedance measurement (either completed or aborted).

#### I<sup>2</sup>C Register Descriptions

#### Table 2. Chipld Register (0x00)

| ADDRESS:     | 0x00 (Read-  | Only)          |                |                 |             |            |   |   |

|--------------|--------------|----------------|----------------|-----------------|-------------|------------|---|---|

| BIT          | 7            | 6              | 5              | 4               | 3           | 2          | 1 | 0 |

| NAME         |              |                |                | Chipl           | d[7:0]      |            |   |   |

| Chip_ld[7:0] | Chip_Id[7:0] | bits show info | mation about t | he version of t | he MAX14720 | /MAX14750. |   |   |

#### Table 3. ChipRev Register (0x01)

| ADDRESS:     | 0x01 (Read-  | Only)          |               |                 |             |              |          |   |

|--------------|--------------|----------------|---------------|-----------------|-------------|--------------|----------|---|

| BIT          | 7            | 6              | 5             | 4               | 3           | 2            | 1        | 0 |

| NAME         |              |                |               | ChipR           | ev[7:0]     |              |          |   |

| ChipRev[7:0] | ChipRev[7:0] | bits show info | rmation about | the revision of | the MAX1472 | 0/MAX14750 s | silicon. |   |

#### Table 4. BoostCDiv Register (0x03)

| ADDRESS:       | 0x03                                                                                           |                                                                                                                 |                                                                                          |                                                                               |                                                                                                 |                                   |                                   |              |

|----------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|--------------|

| BIT            | 7                                                                                              | 6                                                                                                               | 5                                                                                        | 4                                                                             | 3                                                                                               | 2                                 | 1                                 | 0            |

| NAME           | ClkDivEn                                                                                       |                                                                                                                 |                                                                                          |                                                                               | ClkDivSet[6:0                                                                                   | ]                                 |                                   |              |

| ClkDivEn       | This allows the 0: Normal Of 1: Divided Combined When the closed frequency. The ClkDivSet[6:0] | peration, Full (<br>lock Current L<br>cck divider is en<br>ne peak curren<br>o]. The regulat<br>s below the out | ator to be oper Dutput Current mited Mode nabled, the bo t is set by Boo or will stop sw | rated in a curre Capability ost is operatee ostISet[2:0] and itching when the | ent limited outp<br>d with a fixed p<br>d the switching<br>he voltage is all<br>only be enabled | eak current lim<br>frequency is d | determined by<br>pint and will or | nly run when |

| ClkDivSet[6:0] | When the cui                                                                                   |                                                                                                                 | ode is enabled                                                                           | I, the frequenc                                                               | cy of the boost<br>0 + ClkDivSet[                                                               | •                                 |                                   |              |

## Table 5. BoostlSet Register (0x04)

| ADDRESS:       | 0x04 |   |   |   |   |   |                |   |

|----------------|------|---|---|---|---|---|----------------|---|

| BIT            | 7    | 6 | 5 | 4 | 3 | 2 | 1              | 0 |

| NAME           | _    | _ | _ | _ | _ |   | BoostISet[2:0] |   |

| BoostlSet[2:0] |      |   |   |   |   |   |                |   |

## Table 6. BoostVSet Register (0x05)

| ADDRESS:       | 0x05                                                                                                    |                           |   |   |               |               |                 |          |

|----------------|---------------------------------------------------------------------------------------------------------|---------------------------|---|---|---------------|---------------|-----------------|----------|

| BIT            | 7                                                                                                       | 6                         | 5 | 4 | 3             | 2             | 1               | 0        |

| NAME           | _                                                                                                       | _                         | _ |   |               | BoostVSet[4:0 | ]               |          |

| BoostVSet[4:0] | Boost Output<br>2.5V to 5.0V, I<br>000000 = 2.5V<br>000001 = 2.6V<br><br>011001 = 5.0V<br>> 011001 = 5. | linear scale, 1<br>V<br>V |   | • | tched and can | change only w | /hen boost is d | isabled. |

#### Table 7. BoostCfg Register (0x06)

| ADDRESS:      | 0x06                                                                                                              |                                                             |                |                                |                                             |                |           |          |

|---------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|--------------------------------|---------------------------------------------|----------------|-----------|----------|

| BIT           | 7                                                                                                                 | 6                                                           | 5              | 4                              | 3                                           | 2              | 1         | 0        |

| NAME          | Boost                                                                                                             | Seq[2:0] (Rea                                               | d-only)        | Boos                           | tEn[1:0]                                    | _              | BoostEMI  | BoostInd |

| BoostSeq[2:0] | 000 = Disabl<br>001 = Reserved<br>010 = Enable<br>011 = Enable<br>100 = Enable<br>101 = Reserved<br>110 = Control | ed ved ed at 0% of Bo ed at 25% of B ed at 50% of B ved ved |                | ess Delay Cor<br>ess Delay Cor | ntrol                                       | elay Control ( | MAX14720) |          |

| BoostEn[1:0]  | 00 = Disable<br>01 = Enabled                                                                                      | d. Active disch<br>d<br>d when MPC is                       | narge behavior |                                | Seq[2:0] == 11 <sup>o</sup><br>BoostActDsc. | 1)             |           |          |

| BoostEMI      | 0 = EMI dam                                                                                                       | ping active (in                                             |                |                                | when in discon                              | tinuous mode   |           |          |

| BoostInd      | Boost Induct<br>1 = Inductan<br>0 = Inductan                                                                      | ce is 3.3µH                                                 |                |                                |                                             |                |           |          |

## Table 8. BuckVSet Register (0x07)

| ADDRESS:      | 0x07 |                                 |   |   |                |                |                 |        |

|---------------|------|---------------------------------|---|---|----------------|----------------|-----------------|--------|

| BIT           | 7    | 6                               | 5 | 4 | 3              | 2              | 1               | 0      |

| NAME          | _    | _                               |   |   | BuckV          | Set[5:0]       |                 |        |

| BuckVSet[5:0] |      | linear scale, 2<br>000V<br>025V |   |   | ched and can o | change only wh | nen buck is dis | abled. |

## Table 9. BuckCfg Register (0x08)

| ADDRESS:     | 0x08                                                                                     |                                                                                                                                                                                                  |                                                                                                                          |                                                      |                    |                 |         |         |  |  |