16V, 500mA, Low Quiescent Current Linear Regulator

#### The Future of Analog IC Technology

### DESCRIPTION

The MP2018 is a low-power linear regulator that supplies power to systems with highvoltage batteries. The MP2018 includes a wide 3V to 16V input voltage range, low dropout voltage, and low quiescent supply current. The low quiescent current and low dropout voltage allow the MP2018 to operate at extremely low power levels. Therefore, the MP2018 is ideal for low-power microcontrollers and batterypowered equipment.

The MP2018 provides two fixed output voltage options: 3.3V and 5.0V.

The regulator output current is limited internally, and the device is protected against short-circuit, overload, and over-temperature conditions. The MP2018 also includes thermal shutdown and current-limiting fault protection.

The MP2018 is available in a TO252-5 package.

### FEATURES

- 3V to 16V Input Range

- 10µA Quiescent Supply Current

- Stable with Low-Value Output Ceramic Capacitor (>0.47µF)

- 500mA Specified Current

- Fixed Output Voltage

- Output ±2% Accuracy

- Specified Current Limit

- Power Good

- Programmable Power Good Delay

- Thermal Shutdown and Short-Circuit Protection (SCP)

- -40°C to +150°C Specified Junction Temperature Range

- Available in a TO252-5 Package

### **APPLICATIONS**

- Portable/Battery-Powered Equipment

- Ultra-Low Power Microcontrollers

- Cellular Handsets

- Medical Imaging

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

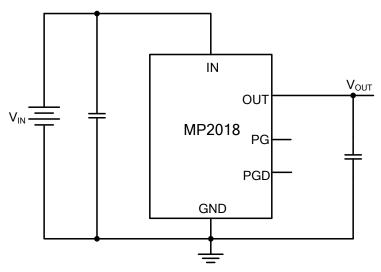

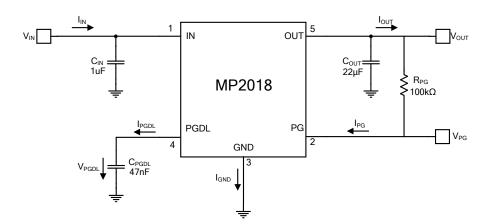

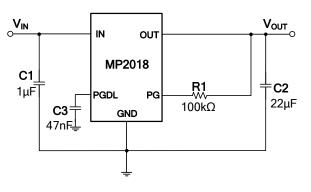

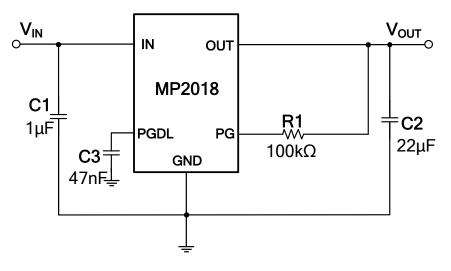

### **TYPICAL APPLICATION**

#

| Part Number* |              | Package | Top Marking |  |  |

|--------------|--------------|---------|-------------|--|--|

|              | MP2018GZD-33 | TO252-5 | See Below   |  |  |

|              | MP2018GZD-5  | TO252-5 | See Below   |  |  |

\* For Tape & Reel, add suffix –Z (e.g.: MP2018GZD-5–Z).

### **TOP MARKING (MP2018GZD-33)**

MPS YYWW MP2018-33 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP2018-33: Part number LLLLLLLL: Lot number

### **TOP MARKING (MP2018GZD-5)**

MPS YYWW MP2018-5 LLLLLLLL

MPS: MPS prefix YY: Year code WW: Week code MP2018-5: Part number LLLLLLLL: Lot number

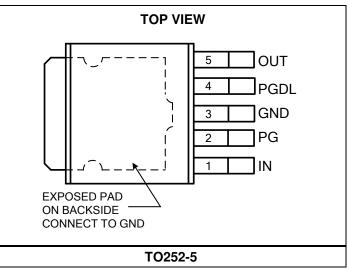

### PACKAGE REFERENCE

### ABSOLUTE MAXIMUM RATINGS <sup>(1)</sup>

| IN                          |                                            |

|-----------------------------|--------------------------------------------|

| OUT                         |                                            |

| PG                          |                                            |

| PGDL                        |                                            |

| Lead temperature            | 260°C                                      |

| Storage temperature         |                                            |

| Continuous power dissipatio | on (T <sub>A</sub> = +25°C) <sup>(2)</sup> |

| TO252-5                     | 2.27W                                      |

|                             |                                            |

### ESD Susceptibility <sup>(3)</sup>

| Human body mode (HBM)4kV |      |  |

|--------------------------|------|--|

| Machine mode (MM)        | 200V |  |

### Recommended Operating Conditions (4)

| Supply voltage (V <sub>IN</sub> ) | 3V to 16V                       |

|-----------------------------------|---------------------------------|

| Operating temperature             |                                 |

|                                   | $T_A \le T_J \le +150^{\circ}C$ |

# *Thermal Resistance* <sup>(5)</sup> *θ<sub>JA</sub> θ<sub>JC</sub>* TO252-5.......55.......3...°C/W

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) Devices are ESD-sensitive. Handling precaution is recommended.

- The device is not guaranteed to function outside of its operating conditions.

- 5) Measured on JESD51-7, 4-layer PCB.

### **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 13.5V,  $T_J$  = +25°C, unless otherwise noted.

| Parameter                       | Symbol          | Condition                                                                                                                               | Min   | Тур  | Max    | Units            |

|---------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|------|--------|------------------|

|                                 |                 | 0 < Iout < 1mA                                                                                                                          |       | 12   | 17     |                  |

| GND pin current                 |                 | 1mA < I <sub>OUT</sub> < 30mA                                                                                                           |       | 16   | 22     | μA               |

|                                 |                 | 30mA < Iоит < 500mA                                                                                                                     |       | 105  | 150    |                  |

| Load current limit              | ILIMIT          | V <sub>OUT</sub> = 0V                                                                                                                   | 550   | 900  | 1450   | mA               |

| Output voltage accuracy         |                 | $\label{eq:mp2018GZD-5} \begin{array}{l} MP2018GZD\text{-}5,  V_{\text{IN}} = 6V \text{ to } 16V, \\ I_{\text{LOAD}} = 5mA \end{array}$ | 4.9   | 5    | 5.1    | v                |

| Output voltage accuracy         |                 | $\label{eq:mp2018GZD-33} \begin{split} MP2018GZD-33, \ V_{IN} = 4.3V \ to \ 16V, \\ I_{LOAD} = 5mA \end{split}$                         | 3.234 | 3.3  | 3.366  |                  |

|                                 | Vdropout        | $\label{eq:mp2018GZD-5, I_{LOAD} = 300mA, \\ V_{DROPOUT} = V_{IN} - V_{O}$                                                              |       | 400  | 650    | - mV             |

| Dropout voltage (6)             |                 | $\label{eq:mp2018GZD-33, I_{LOAD} = 300mA, \\ V_{DROPOUT} = V_{IN} - V_O$                                                               |       | 500  | 700    |                  |

| Diopoul voltage (9)             |                 | $\label{eq:mp2018GZD-5, I_{LOAD} = 500mA, \\ V_{DROPOUT} = V_{IN} - V_{O}$                                                              |       | 750  | 1000   |                  |

|                                 |                 | $\label{eq:mp2018GZD-33} \begin{array}{l} H_{LOAD} = 500 \text{mA}, \\ V_{DROPOUT} = V_{IN} - V_{O} \end{array}$                        |       | 1000 | 1300   |                  |

| Line regulation                 |                 | $V_{IN} = 8V$ to 16V, $I_{LOAD} = 5mA$                                                                                                  | -10   | 1    | 10     | mV               |

| Load regulation                 |                 | $I_{LOAD} = 5mA$ to 500mA                                                                                                               |       | 1    | 15     | mV               |

|                                 |                 | $100Hz, C_{OUT} = 10\mu F, I_{LOAD} = 10mA$                                                                                             |       | 57   |        | dB               |

| Output voltage PSRR (7)         |                 | 1kHz, Cout = 10µF, Iload = 10mA                                                                                                         |       | 45   |        | dB               |

|                                 |                 | $100$ kHz, C <sub>OUT</sub> = $10\mu$ F, I <sub>LOAD</sub> = $10$ mA                                                                    |       | 51   |        | dB               |

| Startup response time           |                 | $\begin{array}{l} MP2018GZD\text{-}5,\ I_{\text{LOAD}}=10mA,\\ C_{\text{OUT}}=22\mu F \end{array}$                                      |       | 1    | 2      |                  |

| Startup response time           |                 | $\begin{array}{l} MP2018GZD33,\ I_{LOAD}=10mA,\\ C_{OUT}=22\mu F \end{array}$                                                           |       | 0.6  | 1.5 ms |                  |

| PG rising threshold             |                 |                                                                                                                                         | 90%   | 93%  | 96%    | Vout             |

| PG rising threshold hysteresis  |                 |                                                                                                                                         |       | 5%   |        | V <sub>OUT</sub> |

| PG low voltage                  |                 | Sink 1mA current                                                                                                                        |       | 0.1  | 0.4    | V                |

| PG leakage current              |                 | $V_{PG} = 5V$                                                                                                                           |       |      | 1      | μΑ               |

| PGDL charging current           |                 | $V_{PGDL} = 1V$                                                                                                                         | 3     | 5.5  | 9      | μΑ               |

| PGDL rising threshold           |                 |                                                                                                                                         | 1.5   | 1.65 | 2      | V                |

| PGDL falling threshold          |                 |                                                                                                                                         | 0.2   | 0.4  | 0.7    | V                |

| PG delay time                   | <b>t</b> PGDL   | C <sub>PGDL</sub> = 47nF, 10% to 90% PGDL rising threshold                                                                              | 6     | 11   | 14     | ms               |

| PG reaction time                |                 | $C_{PGDL} = 47 nF$                                                                                                                      |       | 0.5  | 2      | μs               |

| Thermal shutdown (7)            | T <sub>SD</sub> |                                                                                                                                         |       | 165  |        | °C               |

| Thermal shutdown hysteresis (7) | ΔTSD            |                                                                                                                                         |       | 30   |        | °C               |

#### NOTES:

6) Dropout voltage: Measured when the output voltage (V<sub>OUT</sub>) has dropped 100mV from the nominal value obtained at V<sub>IN</sub> = 13.5V.

1) Derived from bench characterization. Not tested in production.

### **PIN FUNCTIONS**

| Pin #                                      | Name | Description                                                                                                                        |

|--------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------|

| 1                                          | IN   | Input voltage. Connect a 3V to 16V supply to IN.                                                                                   |

| 2                                          | PG   | Power good.                                                                                                                        |

| 3                                          | GND  | <b>Ground.</b> GND is connected to the exposed pad internally. GND and the exposed pad must be connected to the same ground plane. |

| 4 PGDL Programmable power good delay time. |      | Programmable power good delay time.                                                                                                |

| 5                                          | OUT  | <b>Regulated output voltage.</b> Connect a low-value ceramic capacitor (≥0.47µF) to the output for stability.                      |

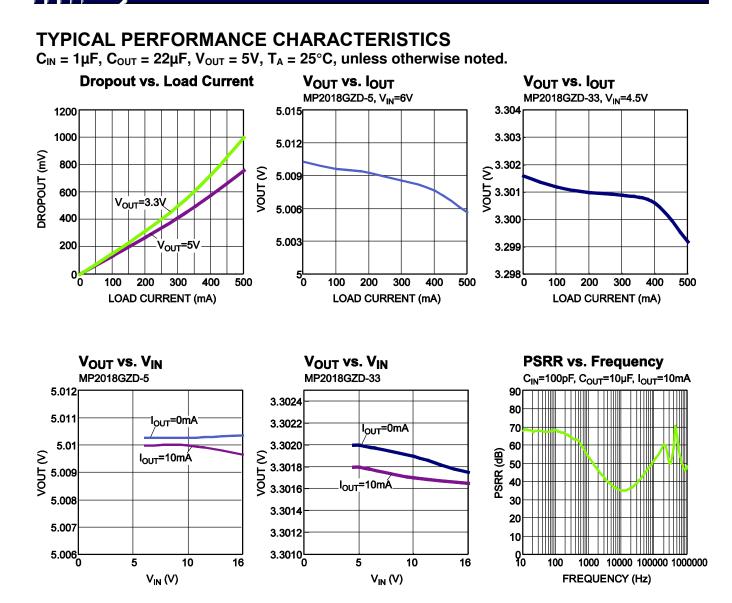

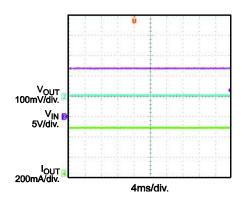

#### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued) $C_{IN} = 1\mu F$ , $C_{OUT} = 22\mu F$ , $V_{OUT} = 5V$ , $T_A = 25^{\circ}C$ , unless otherwise noted. Start-Up through VIN **Load Transient Line Transient** V<sub>IN</sub>=12V, I<sub>OUT</sub>=250mA-500mA V<sub>IN</sub>=12V, I<sub>OUT</sub>=500mA V<sub>IN</sub>=6V-7V, I<sub>OUT</sub>=500mA V<sub>OUT</sub>/AC 100mV/div. V<sub>IN</sub> 5V/div. V<sub>IN</sub> 2V/div. V<sub>OUT</sub> 2V/div. V<sub>OUT</sub>/AC 10mV/div. I<sub>OUT</sub> 200mA/div. lout 200mA/div 2ms/div. 40ms/div. 400µs/div. Shutdown through VIN **Short-Circuit Entry Short-Circuit Recovery** V<sub>IN</sub>=12V, I<sub>OUT</sub>=500mA IOUT=0mA to Short Circuit Short Circuit to IOUT=0mA V<sub>OUT</sub> 2V/div. V<sub>IN</sub> 5V/div. VOUT 2V/div. V<sub>OUT</sub> 2V/div. I<sub>OUT</sub> 200mA/div. IOUT 1A/div. I<sub>OUT</sub> 200mA/div.

20ms/div.

## Short-Circuit Steady State

10ms/div.

1ms/div.

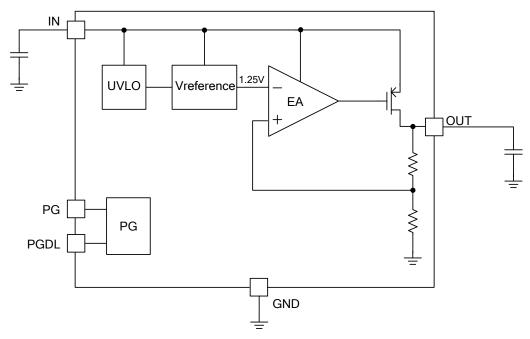

### **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

### **OPERATION**

The MP2018 is a linear regulator that supplies power to systems with high-voltage batteries. The MP2018 includes a wide 3V to 16V input range, low dropout voltage, and low quiescent supply current.

#### **Short-Circuit Protection (SCP)**

The regulator output current is limited internally, and the device is protected against short-circuit and overload conditions. The peak output current is limited to around 900mA, which exceeds the 500mA recommended continuous output current.

#### **Thermal Shutdown**

When the junction temperature exceeds the upper threshold (165°C), the thermal sensor sends a signal to the control logic to shut down the IC. The IC restarts when the temperature has cooled sufficiently (135°C).

The maximum power output current is a function of the package's maximum power dissipation for a given temperature.

The maximum power dissipation depends on the thermal resistance of the case and the circuit board, the temperature difference between the die junction and the ambient air, and the rate of the air flow. GND and the exposed pad must be connected to the ground plane for proper dissipation.

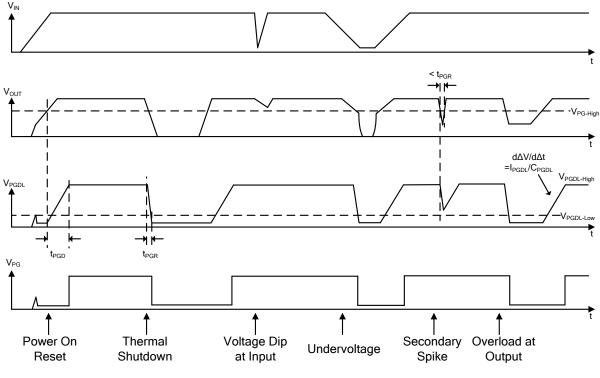

#### Power Good (PG) Output

The MP2018 has a power good pin (PG). PG is the open drain of an internal MOSFET and should be connected to the output voltage ( $V_{OUT}$ ) or an external voltage source (<15V) through a resistor (i.e.: 100k $\Omega$ ). If  $V_{OUT}$  reaches 93% of the nominal value, the MOSFET turns off, and PG is pulled high by  $V_{OUT}$  or an external voltage source. When  $V_{OUT}$  drops to 88% of the nominal value, the PG voltage is pulled to GND.

There is a delay time when PG asserts high. The delay time can be programmed by adding a capacitor on PGDL. Select a capacitor for PGDL using Equation (1):

$$C_{PGDL}(nF) = \frac{t_{PGDL}(ms) \times I_{PGDL}(\mu A)}{V_{th_PGDL}(V)}$$

(1)

Where  $t_{PGDL}$  is the desired delay time when PG asserts high,  $I_{PGDL}$  is the PGDL charging current, and  $V_{th_{PGDL}}$  is 1.65V.

Figure 2 shows the power good timing.

Figure 2: Power Good Timing

### **APPLICATION INFORMATION**

#### Selecting the Input Capacitor

For proper operation, place a dielectric type X5R or X7R ceramic capacitor between 1 -  $10\mu$ F (C1) between the input pin and ground. Larger values in this range help improve line transient response.

#### **Selecting the Output Capacitor**

For stable operation, use a dielectric type X5R or X7R ceramic capacitor (C2) between 1 -  $22\mu$ F. Larger values in this range help improve load transient response and reduce noise. Output capacitors of other dielectric types may be used but are not recommended since their capacitance can deviate greatly from their rated value over temperature.

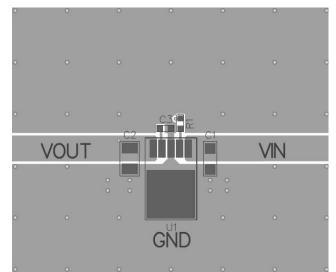

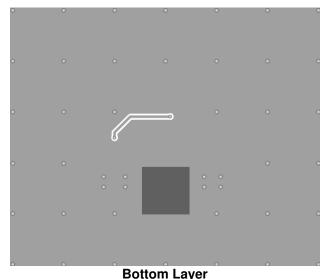

#### **PCB Layout Guidelines**

Efficient PCB layout is critical for good regulation, ripple rejection, transient response, and thermal performance. It is highly recommended to duplicate the EVB layout for optimal performance. For best results, refer to Figure 3, Figure 4, and follow the guidelines below.

- 1. Place the input and output bypass ceramic capacitors close to IN and OUT respectively.

- 2. Connect IN, OUT, and especially GND to a large copper area to cool the chip and improve thermal performance and long-term reliability.

Figure 3: MP2018 Schematic

**Top Layer**

Figure 4: Recommended Layout

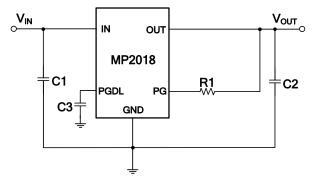

#### Design Example

Figure 5 shows a design example following the application guidelines.

Figure 5: Design Example

### **TYPICAL APPLICATION CIRCUIT**

Figure 6: Typical Application Circuit

0.136(3.45) REF

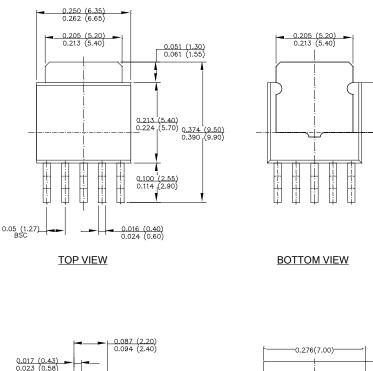

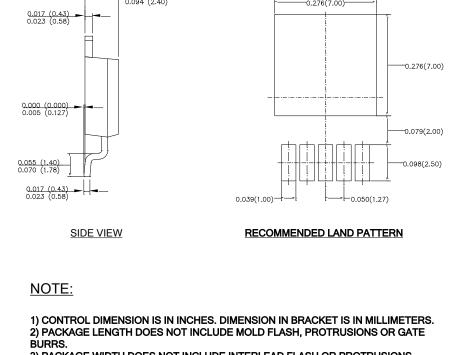

### PACKAGE INFORMATION

TO252-5

a) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

4) DRAWING CONFORMS TO JEDEC TO-252.

5) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.