# SANYO Semiconductors DATA SHEET

An ON Semiconductor Company

# LV5803M — Step-down Switching Regulator

#### Overview

LV5803M is a 1ch step-down switching regulator.  $0.2\Omega$  FET is incorporated on the upper side to achieve high-efficiency operation for large output current. Low-heat resistance and compact-package MFP8 employed. Current mode control type, with superior load current response and easy phase compensation ON/OFF pin, allowing the standby mode with the current drain of  $80\mu$ A or less Pulse-by-pulse over-current protection and overheat protection available for protection of load devices Soft start pin to be provided with a capacitance for soft start.

#### **Functions**

- 2A 1ch step-down switching regulator

- Wide input dynamic range (4.5 to 18V)

- High efficiency (90%  $I_{OUT} = 1A$ ,  $V_{IN} = 12V$ ,  $V_{O} = 5V$ )

- Standby mode

- Over-current protection

• Thermal shutdown

Reference voltage: 0.8VFixed frequency: 330kHz

• Soft start

• Compact package: MFP8 (225mil)

#### **Specifications**

**Maximum Ratings** at Ta = 25°C

| _                                     |                        |                            |                     |      |

|---------------------------------------|------------------------|----------------------------|---------------------|------|

| Parameter                             | Symbol                 | Conditions                 | Ratings             | Unit |

| Maximum input V <sub>IN</sub> voltage | V <sub>IN</sub> max    |                            | 20                  | V    |

| BOOT pin maximum voltage              | V <sub>BT</sub> max    |                            | 25                  | V    |

| SW pin maximum voltage                | V <sub>SW</sub> max    |                            | V <sub>IN</sub> max | V    |

| BOOT pin-SW pin maximum voltage       | V <sub>BS-SW</sub> max |                            | 7                   | V    |

| EN pin maximum voltage                | V <sub>EN max</sub>    |                            | 20                  | V    |

| FB, COMP, SS pin maximum voltage      | Vfs max                |                            | 7                   | V    |

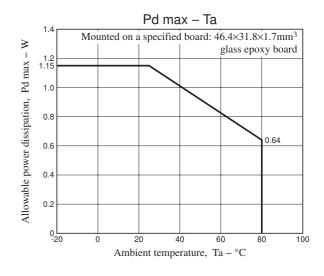

| Allowable power dissipation           | Pd max                 | With specified substrate * | 1.15                | W    |

| Junction temperature                  | Tj max                 |                            | 150                 | °C   |

| Operating temperature                 | Topr                   |                            | -20 to 80           | °C   |

| Storage temperature                   | Tstg                   |                            | -40 to 150          | °C   |

<sup>\*</sup> Specified substrate:  $46.4 \text{mm} \times 31.8 \text{mm} \times 1.7 \text{mm}$ , glass epoxy substrate

Note: Plan the maximum voltage while including coil and surge voltages, so that the maximum voltage is not exceeded even for an instant.

- Any and all SANYO Semiconductor Co.,Ltd. products described or contained herein are, with regard to "standard application", intended for the use as general electronics equipment (home appliances, AV equipment, communication device, office equipment, industrial equipment etc.). The products mentioned herein shall not be intended for use for any "special application" (medical equipment whose purpose is to sustain life, aerospace instrument, nuclear control device, burning appliances, transportation machine, traffic signal system, safety equipment etc.) that shall require extremely high level of reliability and can directly threaten human lives in case of failure or malfunction of the product or may cause harm to human bodies, nor shall they grant any guarantee thereof. If you should intend to use our products for applications outside the standard applications of our customer who is considering such use and/or outside the scope of our intended standard applications, please consult with us prior to the intended use. If there is no consultation or inquiry before the intended use, our customer shall be solely responsible for the use.

- Specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

## LV5803M

## **Recommended Operating Conditions** at Ta = 25°C

| Parameter                       | Symbol             | Conditions | Ratings                 | Unit |

|---------------------------------|--------------------|------------|-------------------------|------|

| V <sub>IN</sub> pin voltage     | V <sub>IN</sub>    |            | 4.5 to 18               | V    |

| BOOT pin voltage                | V <sub>BT</sub>    |            | -0.3 to 23              | V    |

| SW pin voltage                  | V <sub>SW</sub>    |            | -0.4 to V <sub>IN</sub> | V    |

| BOOT pin-SW pin maximum voltage | V <sub>BS-SW</sub> |            | 6.5                     | V    |

| EN pin maximum voltage          | V <sub>EN</sub>    |            | 18                      | V    |

| FB, COMP, SS pin voltage        | V <sub>FSO</sub>   |            | 6                       | V    |

## **Electrical Characteristics** at Ta = 25 °C, $V_{\mbox{IN}} = 12 \mbox{V}$ , unless otherwise specified.

| Parameter                                             | Cumbal            | Conditions                                                          |      | Ratings |      | Unit |

|-------------------------------------------------------|-------------------|---------------------------------------------------------------------|------|---------|------|------|

|                                                       | Symbol            | Symbol Conditions                                                   | min  | typ     | max  | Unit |

| IC current drain at standby                           | I <sub>CC</sub> 1 | EN=0V                                                               |      | 80      |      | μА   |

| IC current drain in operation                         | I <sub>CC</sub> 2 | EN=open                                                             |      | 2       |      | mA   |

| Efficiency                                            | Effcy             | V <sub>IN</sub> =12V, I <sub>OUT</sub> =1A, Vo=5V, Design target *1 |      | 90      |      | %    |

| Reference voltage                                     | Vref              | V <sub>IN</sub> =4.5V to 18V (±2%)                                  | -2%  | 0.8     | +2%  | V    |

| FB pin bias current                                   | Iref              | FB=0.8V application                                                 |      | 10      | 100  | nA   |

| High-side ON resistance                               | RonH              | BOOT=5V                                                             |      | 0.20    |      | Ω    |

| Oscillation frequency                                 | fosc              |                                                                     | 265  | 330     | 395  | kHz  |

| Oscillation frequency during short-circuit protection | foscs             |                                                                     | 26   | 33      | 40   | kHz  |

| EN high-threshold voltage                             | Venh              |                                                                     | 1.25 | 1.55    | 1.85 | V    |

| EN low-threshold voltage                              | Venl              |                                                                     | 0.95 | 1.25    | 1.55 | V    |

| EN pull-up current                                    | len               | EN=0V                                                               |      | 45      |      | μА   |

| Maximum ON DUTY                                       | D max             |                                                                     |      | 86      |      | %    |

| Current limit peak value 1                            | Ic1               | V <sub>IN</sub> =12V, V <sub>OUT</sub> =5V, L=10μH                  | 2.5  |         | 5.3  | Α    |

| Current limit peak value 2                            | lc2               | V <sub>IN</sub> =12V, V <sub>OUT</sub> =3.3V, L=10μH                | 2.8  |         | 5.6  | Α    |

| Current limit peak value 3                            | Ic3               | V <sub>IN</sub> =12V, V <sub>OUT</sub> =1.2V, L=10μH                | 3.1  |         | 5.9  | Α    |

| Thermal shutdown temperature                          | Ttsd              | *Design guarantee *2                                                |      | 160     |      | °C   |

| Thermal shutdown temperature hysteresis               | Dtsd              | *Design guarantee *2                                                |      | 40      |      | °C   |

| Soft start current                                    | I <sub>SS</sub>   | SS=0V                                                               | 6    | 10      | 14   | μА   |

<sup>\*1:</sup> Reference value (not tested before shipment)

<sup>\*2:</sup> Design guarantee (value guaranteed by design and not tested before shipment)

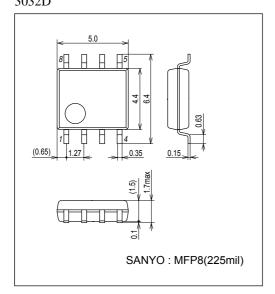

### **Package Dimensions**

unit : mm (typ) 3032D

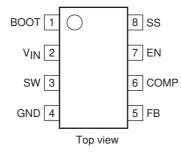

## **Pin Assignment**

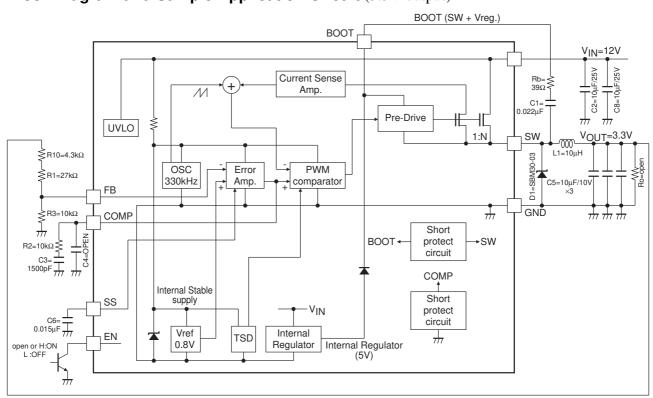

## **Block Diagram and Sample Application Circuit** (3.3V output)

- C1, C8, C5 = ceramic capacitor used.

- L1 = CDRH105RPN-100NC (sumida made)

# LV5803M

#### **Pin Function**

| PIN FU  | unction         |                                                                                                                                                                                                                                                                                                                                                                                                    |                                |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Pin No. | Pin name        | Function                                                                                                                                                                                                                                                                                                                                                                                           | Equivalent circuit             |

| 1       | воот            | Upper MOS transistor boot strap capacitance connection pin. Connect the boot capacitance of about $0.022\mu F$ between SW pins. To protect the SW pin's absolute maximum rating, to ensure stable operation, and to eliminate noise, the boot capacitance serial resistance (about $100\Omega$ ) Rb proves                                                                                         | Short protection circuit  BOOT |

| 2       | V <sub>IN</sub> | Input voltage pin.  Connect substantially large (10µF 2 parameters or more) capacitance between this pin and GND.                                                                                                                                                                                                                                                                                  | Output MOS                     |

| 3       | SW              | Power switch pin. Connect the output LC filter. Connect the above capacitance between this pin and BOOT pin.                                                                                                                                                                                                                                                                                       | sw                             |

| 4       | GND             | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                        |                                |

| 5       | FB              | Feedback pin. Sets the output voltage by means of split resistor in the section of the output voltage $V_{OUT}$ - FB - GND. $V_{OUT}$ setting is made as calculated below: $V_{OUT} = Vref \times \{1 + \frac{(R1 + R10)}{R3}\}$ $Vref = 0.8V$ Example: 3.3V output voltage (See Block Diagram and Sample Application Circuit) $V_{OUT} = Vref \times \{1 + \frac{(27k + 4.3k)}{10k}\}$ = 3.304V   | VIN Internal regulation line   |

| 8       | SS              | Soft start pin. Sets the soft start time by means of the built-in $10\mu A$ source voltage and external soft start capacity. The soft start capacity C6 can be set as follows: $C6 = 10\mu A \times \frac{Tss}{Vref}$ Where, Tss is the soft start time and Vref is the reference voltage. $Example: 1.2ms \ soft \ start \ time \ achieved$ $C6 = 10\mu A \times \frac{1.2ms}{0.8V} = 0.015\mu F$ | SS WHO FB                      |

| 6       | COMP            | Phase compensation pin. Connects with the phase compensation external capacitance and resistance of DC/DC converter close loop.                                                                                                                                                                                                                                                                    | Short protection circuit  COMP |

| 7       | EN              | Enable pin. Converter enabled when set to the HIGH voltage or OPEN state and disabled when connected to GND.                                                                                                                                                                                                                                                                                       | VIN                            |

#### LV5803M

#### Considerations for the design

- During use with  $V_{IN}$  = 12V or less, the boot strap voltage may become deficient due to intermittent operation at no load, resulting in failure of normal operation. In this case, insert a resistance of about 500 $\Omega$  between  $V_{OUT}$  and GND and avoid the intermittent operation mode during use.

- Insertion of serial beads in the Schottky diode for removal of noise may cause generation of the negative voltage deviating from the absolute maximum rating at the SW pin, resulting in failure of normal operation. In such an event, do not insert beads as above described and, instead, remove noise by means of the BOOT resistance Rb.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of January, 2008. Specifications and information herein are subject to change without notice.