# KSZ8342Q

# **Data Sheet**

Version 1.0 / February 5, 2014

Micrel, Inc. 2013, 2014 All rights reserved

Micrel is a registered trademark of Micrel and 'ts subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective own vrs

The information furnis new by Micrel in this document is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its, se. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer. N icrel Products are not designed or authorized for use as components in life support appliances, devices or systems where manufaction of a product can reasonably be expected to result in personal injury. Life support devices or systems are a vices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose fai up to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel process for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

# **Table of Contents**

| 1  | Ge   | eneral Description                   | 8    |

|----|------|--------------------------------------|------|

| 2  | Fea  | atures                               | 9    |

| 3  | Ар   | plications                           | .1(  |

| 4  | Par  | rt Ordering Information              | 12   |

| 5  |      | ickage Pinout                        |      |

| 6  | Pin  | n Descriptions and Strapping Options | . 14 |

| 7  |      | stem Memory Map                      |      |

| 8  | MIF  | PS Processor Core                    | .21  |

| 8  | .1   | Execution Units                      | .22  |

| 8  | .2   | Multiply/Divide Unit (MDU)           | . 22 |

| 8  | .3   | System Coprocessor                   |      |

| 8  | .4   | Memory Management Unit               | .23  |

| 8  | .5   | Translation Lookaside Buffer         | . 23 |

|    | 8.5  |                                      | .23  |

|    | 8.5  | 5.2 Instruction TLB                  | .23  |

| 8  | .6   | Cache Controller                     |      |

| 8  | .7   | Enhanced JTAG (EJTAG)                | .24  |

| 8  | .8   | Power Management                     | .24  |

| 9  | ZS   | P Voice Module Processor             | .26  |

| 9  | .1   | ZSP Architecture                     |      |

| 9  | .2   | 8.2 ZSP Functional Units             |      |

|    | 9.2  |                                      |      |

|    | 9.2  |                                      |      |

|    | 9.2  |                                      |      |

|    | 9.2  |                                      |      |

|    | 9.2  |                                      |      |

|    |      | 2.6 Device Emulation Unit            |      |

|    | 3    | ZSP Boot Process                     |      |

| 10 | 3-17 | Port Switch                          |      |

| 1  | 0.1  | Media Access Controller (MAC)        |      |

|    | 10.  | .1.1 Address Lookup                  | . 30 |

| 10.1.2     | Learning                                   |    |

|------------|--------------------------------------------|----|

| 10.1.3     | Migration                                  |    |

| 10.1.4     | Aging                                      | 31 |

| 10.1.5     | Forwarding                                 | 31 |

| 10.1.6     | MAC Operation                              |    |

| 10.2 Phys  | sical Layer (PHY)                          |    |

| 10.2.1     | 100BASE-T Transmit                         | 37 |

| 10.2.2     | 100BASE-T Receive                          |    |

| 10.2.3     | 10BASE-T Transmit                          |    |

| 10.2.4     | 10BASE-T Receive                           |    |

| 10.2.5     | MDI/MDI-X Auto Crossover                   |    |

| 10.2.6     | Auto-Negotiation                           |    |

| 10.2.7     | PHY Power Management                       | 40 |

| 10.3 Adva  | anced Switch Functions                     | 42 |

| 10.3.1     | Bypass Mode                                | 42 |

| 10.3.2     | IEEE 802.1Q VLAN Support                   | 42 |

| 10.4 3-Po  | Sit Switch QUS Fhonty Support              | 43 |

| 10.4.1     | Port-Based Priority                        | 43 |

| 10.4.2     | 802.1p-Based Priority                      | 43 |

| 10.4.3     | DiffServ-Based Priority                    | 44 |

| 10.4.4     | Spanning Tree Support                      |    |

| 10.4.5     | Rapid Spanning Tree Support                |    |

| 10.4.6     | Tail Tagging Mode                          | 47 |

| 10.4.7     | IGMP Support                               |    |

| 10.4.8     | Port Mirroring Support                     | 47 |

| 10.4.9     | Rate Limiting Shipport                     | 48 |

| 10.4.10    | Unicast NAC Address Filtering              | 49 |

| 10.4.11    | Loopt ack Support                          | 49 |

| 10.4.12    | Static MAC Address Table                   | 51 |

| 10.4. '3   | VLAN Table                                 | 53 |

| 16.4.14    | Dynamic MAC Address Table                  | 53 |

| 10.4.15    | MIB (Management Information Base) Counters | 54 |

| 1 Ethernet | DMA Controller                             | 58 |

|            |                                            |    |

| 11.1 Descriptor Lists and Data Buffers59      |

|-----------------------------------------------|

| 11.2 Receive Descriptors (RDES0-RDES3)        |

| 11.3 Transmit Descriptors (TDES0-TDES3)       |

| 12 Memory Interfaces                          |

| 12.1 SDRAM Interface                          |

| 12.2 Flash Interface                          |

| 12.2.1 Indirect Accesses                      |

| 12.2.2 Direct Accesses                        |

| 12.2.3 SPI Frequency                          |

| 12.2.4 Flash Configurations                   |

| 13 PCM Interface                              |

| 14 SPI SLIC Interface                         |

| 15 UART                                       |

| 16 Interrupt Control                          |

| 17 GPIO                                       |

| 18 Timers                                     |

|                                               |

| 20 Power Management                           |

| 20.1       PHY Power Management               |

| 20.1.1 Normal Operating Mode                  |

| 20.1.2 Energy Detect Mode77                   |

| 20.1.3 Port based Power Down Mode             |

| 20.1.4 Power Saving Mode                      |

| 20.1.5 Port based Power Down Mode             |

| 20.1.6 Energy Efficie t Lthernet              |

| 20.2 MIPS Processor                           |

| 21 Electrical Specifications                  |

| 21.1 Absolute Maximum Ratings                 |

| 21.2 Openting Ratings                         |

| 21.3 CDרלא Memory Interface80                 |

| 21.4 Flash Memory Interface                   |

| 21.5 3-Port Switch Electrical Characteristics |

| 22 Timing Specifications                      |

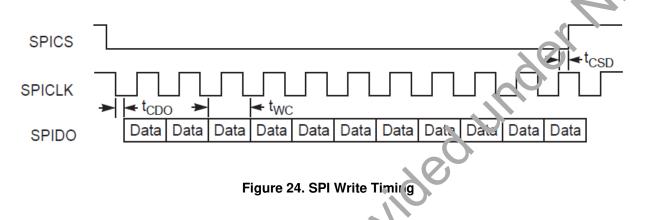

| 2  | 22.1 | SPI Interface Timing              |  |

|----|------|-----------------------------------|--|

|    | 22.7 | 1.1 SPI Write Timing              |  |

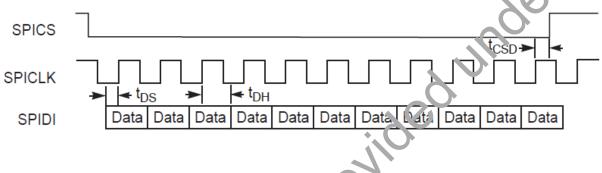

|    | 22.1 | 1.2 SPI Read Timing               |  |

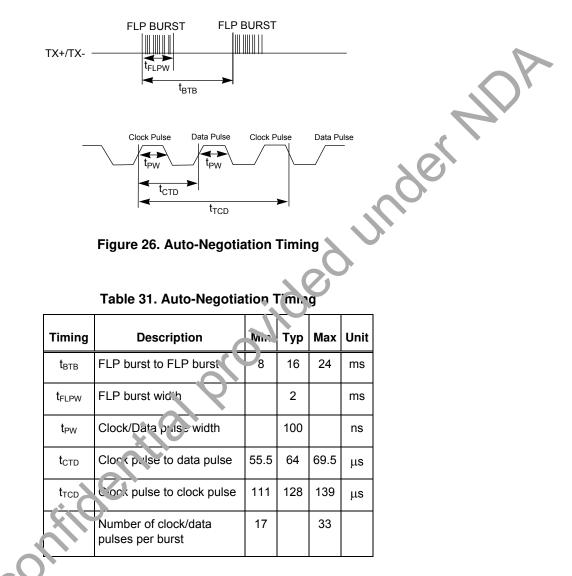

| 2  | 22.2 | Auto-Negotiation Timing           |  |

| 2  | 22.3 | Reset Circuit Guidelines          |  |

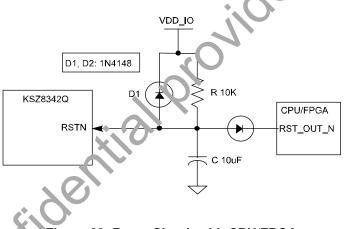

| 2  | 22.4 | Reset and Power Sequencing Timing |  |

| 2  | 22.5 | Reference Clock                   |  |

| 2  | 22.6 | Transformer Selection             |  |

| 23 | The  | ermal Specifications              |  |

| 24 | Мес  | chanical Specifications           |  |

| 25 |      | vision History                    |  |

|    |      |                                   |  |

| List of Figures                                                             |    |

|-----------------------------------------------------------------------------|----|

|                                                                             |    |

|                                                                             |    |

| Figure 1. KSZ8342 Block Diagram                                             | 8  |

| Figure 2 Typical KS78342 VoIP System Application                            | 11 |

| Figure 3. System Memory Map                                                 | 20 |

| Figure 3. System Memory Map<br>Figure 4. MIPS 4KEc Processor Block Diagram  | 21 |

| Figure 5. ZSP Internal Block Diagram<br>Figure 6. 3-Port Switch Connections |    |

| Figure 6. 3-Port Switch Connections                                         |    |

| Figure 7. Destination Address Lookup Flow Chart, Stage 1                    |    |

| Figure 8. Destination Address Resolution Flow Chart, Stage 2                |    |

| Figure 9. Auto Negotiation Process                                          |    |

| Figure 10. 802.1p Priority Field Format                                     |    |

| Figure 11. Tail Tag Frame Format                                            | 47 |

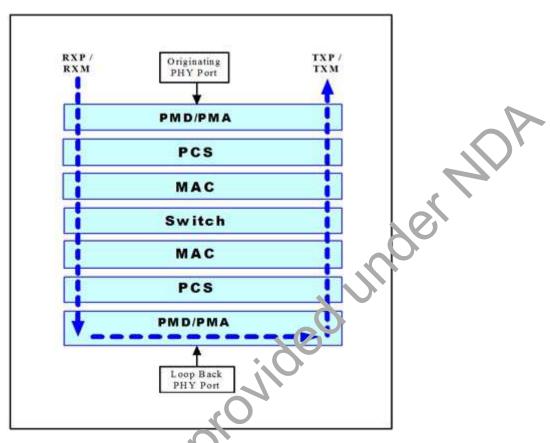

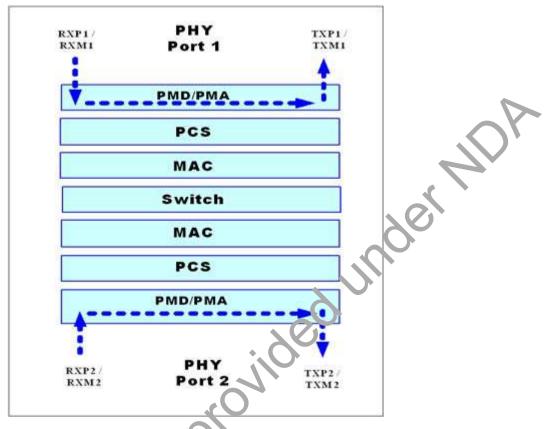

| Figure 12. Far-End Loopback Path                                            |    |

| Figure 13. Near-End Loopback Path                                           | 51 |

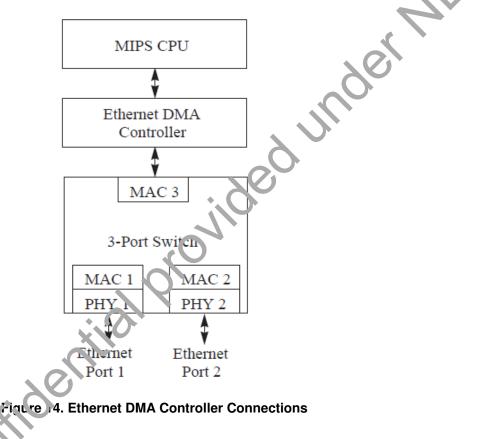

| Figure 14. Eincinet DMA Controller Connections                              | 58 |

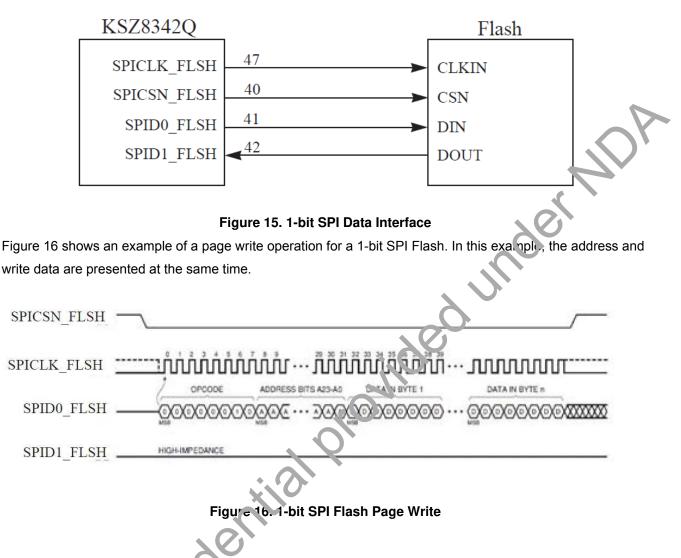

| Figure 15 bit SPI Data Interface                                            |    |

| Figure 10. I-bit SPI Flash Page Write                                       | 67 |

| Sigure 17. 1-bit SPI Flash Page Read                                        |    |

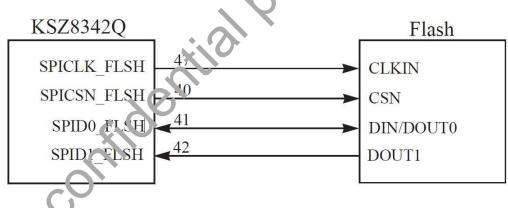

| Figure 18. 2-bit SPI Data Interface                                         |    |

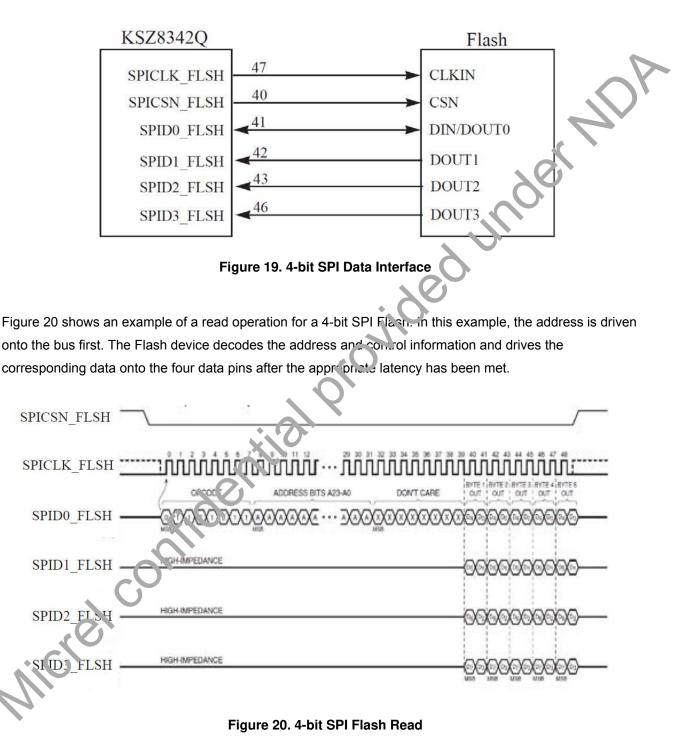

| Figure 19. 4-bit SPI Data Interface                           | 69  |

|---------------------------------------------------------------|-----|

| Figure 20. 4-bit SPI Flash Read                               | 69  |

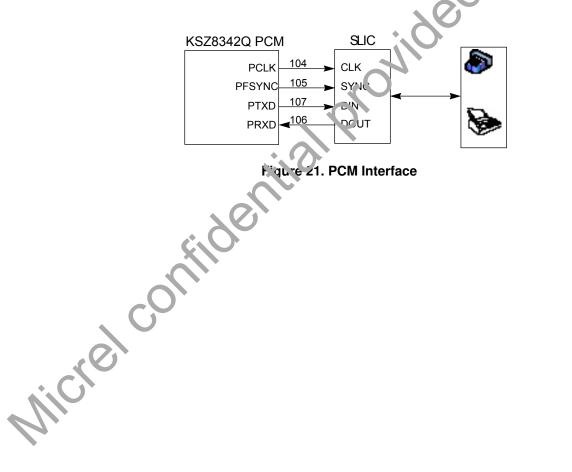

| Figure 21. PCM Interface                                      | 70  |

| Figure 22. SPI SLIC Interface                                 | 71  |

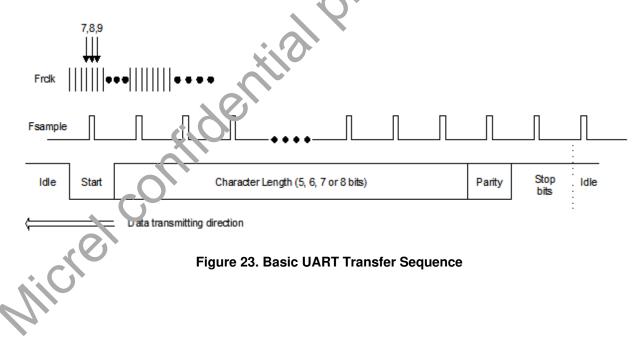

| Figure 23. Basic UART Transfer Sequence                       | 72  |

| Figure 24. SPI Write Timing                                   | 8.3 |

| Figure 25. SPI Read Timing                                    |     |

| Figure 26. Auto-Negotiation Timing                            | 85  |

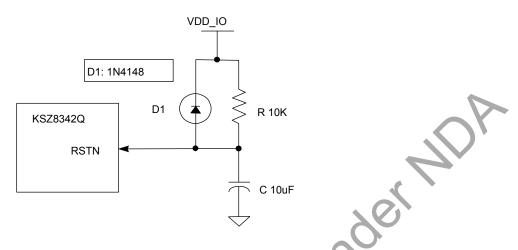

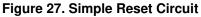

| Figure 27. Simple Reset Circuit                               | 86  |

| Figure 28. Reset Circuit with CPU/FPGA                        | 86  |

| Figure 29. Reset and Power Sequence Timing                    | 87  |

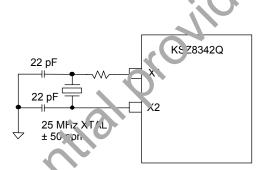

| Figure 30. Crystal Clock Connection Using X1 and X2           | 88  |

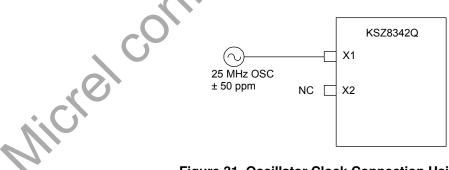

| Figure 31. Oscillator Clock Connection Using X1               | 88  |

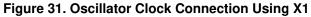

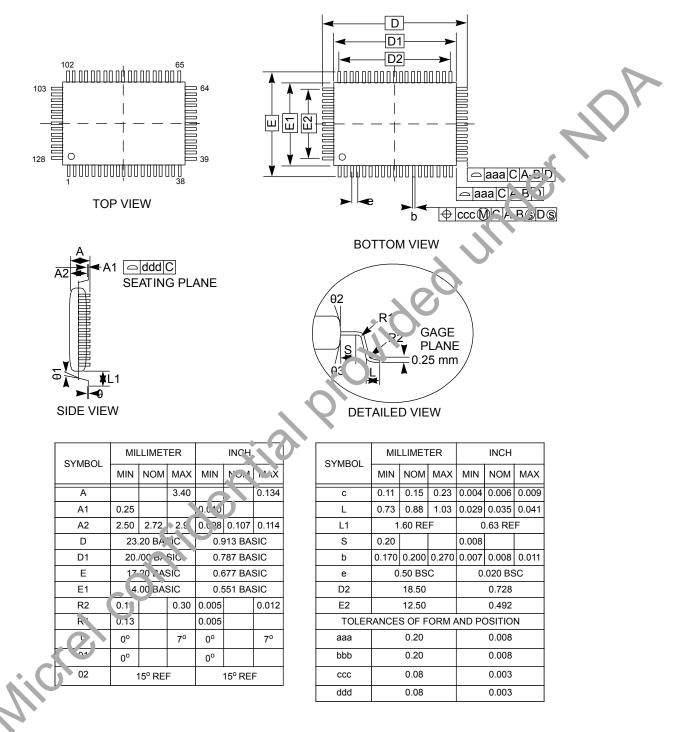

| Figure 32. KSZ8342Q 128-Pin Package Mechanical Specifications | 92  |

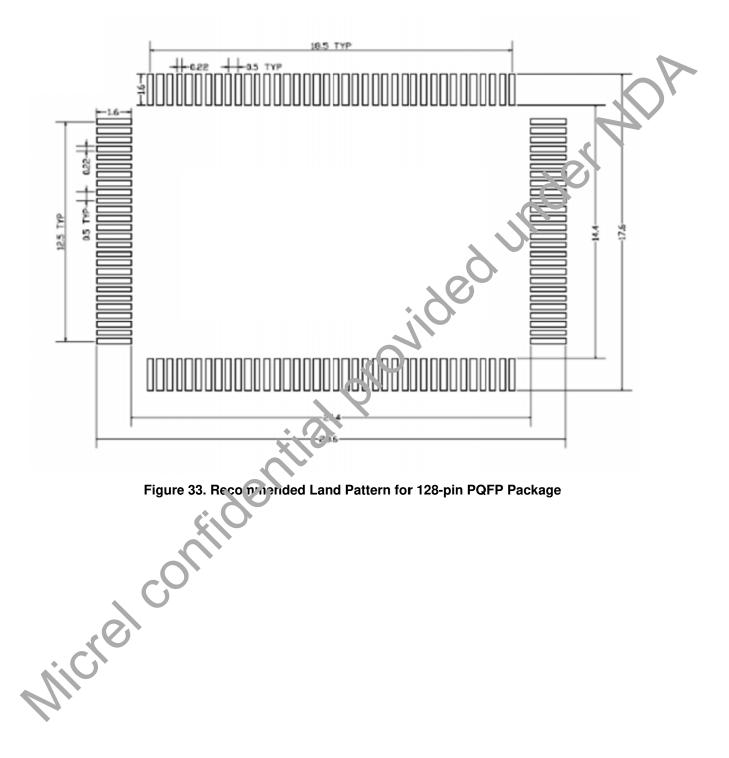

| Figure 33. Recommended Land Pattern for 128-pin PQFP Package. | 93  |

# List of Tabies

| Table | e 1. KSZ8342 External Interfaces                                        | 10 |

|-------|-------------------------------------------------------------------------|----|

| Table | e 2. KSZ8342Q Pin Descriptions                                          | 14 |

| Table | e 3. KSZ8342 Functional Block State per Power Management Operating Mode | 41 |

| Table | e 4. FID+ Destination Address Lookup in VLAN Mode                       | 42 |

| Table | e 5. Spanning Tree State :                                              | 44 |

| Table | e 6. Static MAC Addr. ss Table Bit Assignment                           | 52 |

| Table | e 7. Static VLAN Table Bit Assignment                                   | 52 |

| Table | e 8. Dynamic V. AN Table Bit Assignment                                 | 53 |

| Table | e 9. Format of Per-Port MIB Counters                                    | 55 |

| Table | e 10. Port i Per-Port MIB Counters Indirect Memory Offsets              | 55 |

| Table | e 11. Format of "All-Port Dropped Packet" MIB Counter                   | 57 |

| ⊤ab'e | e 12. "All Port Dropped Packet" MIB Counters Indirect Memory Offsets    | 57 |

| Table | e 13. RDES0 Receive Descriptor Fields                                   | 59 |

|       |                                                                         |    |

| Table 14. RDES1 Receive Descriptor Fields          | 61  |

|----------------------------------------------------|-----|

| Table 15. RDES2 Receive Descriptor Fields          | 61  |

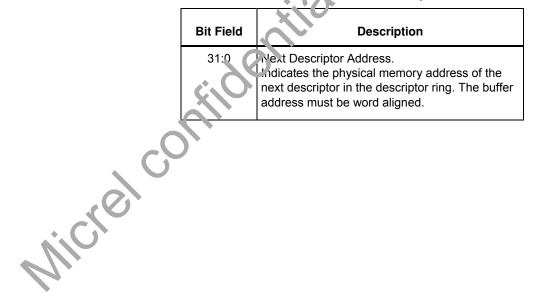

| Table 16. RDES3 Receive Descriptor Fields          | 62  |

| Table 17. TDES0 Receive Descriptor Fields          | 62  |

| Table 18. TDES1 Receive Descriptor Fields          |     |

| Table 19. TDES2 Receive Descriptor Fields          | 6 1 |

| Table 20. TDES3 Receive Descriptor Fields          |     |

| Table 21. Main Memory Parameters                   | 65  |

| Table 22. KSZ8342 GPIO Options                     |     |

| Table 23. KSZ8342 Power Signals                    | 76  |

| Table 24. Absolute Maximum Ratings – Device        | 80  |

| Table 25. Operating Ratings                        | 80  |

| Table 26. Supported SDR Memory Devices             | 81  |

| Table 27. Supported Flash memory Modules           | 81  |

| Table 28. 3-Port Switch Electrical Specifications  | 81  |

| Table 29 SPI Flash and SLIC Write Timing           | 83  |

| Table 30. SPI Flash and SLIC Read Timing           | 84  |

| Table 31. Auto-Negotiation Timing                  | 85  |

| Table 32. Reset and Power Sequence Timing          | 87  |

| Table 33. Typical Reference Crystal Characteristic | 89  |

| Table 34. Transformer Characteristics              | 89  |

| Table 35. Qualified Single-Port Magnetics          | 90  |

| Table 36. KSZ8342 Thermal Specifications           | 91  |

| Nicrel confide                                     |     |

### **General Description** 1

The Micrel KSZ8342Q supplies a complete solution for converting analog signals from a traditional telephone of fax machine for transmission over IP. By incorporating an advanced DSP, the KSZ8342Q provides all logic necessary for performing analog to digital telephone. The KSZ8342Q device is available in a RoHS-compliant 128-lead QFP package.

The KSZ8342Q device leverages Micrel's core technology competencies including:

- IPv6 •

- Low Power •

- Energy Efficient Ethernet (EEE) •

- High degree of integration and compact design •

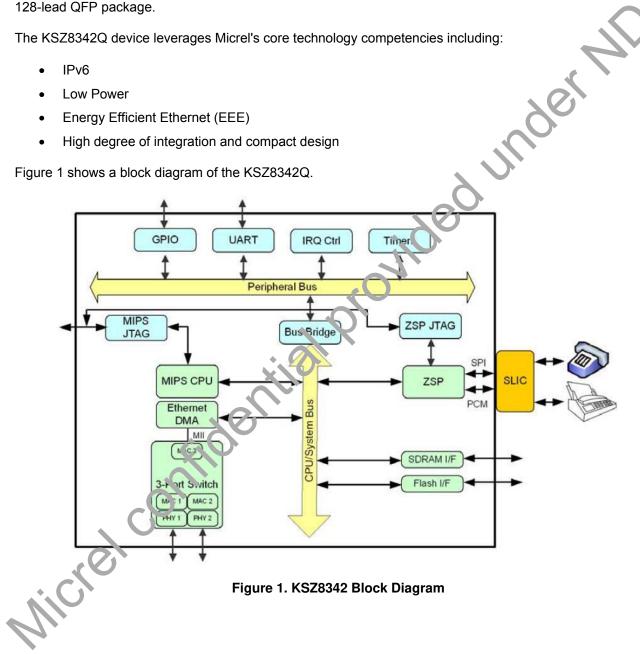

Figure 1 shows a block diagram of the KSZ8342Q.

# 2 Features

Features of the KSZ8342 VoIP processor include:

### MIPS™ Core Processor

The KSZ8342 integrates a MIPS32 M4KEc as the central processing unit for the VoIP SoC. This includes optimized MIPS32 M4KEc configuration options for VoIP including cache size, cache organization, Ci U register size, and memory BIST.

### ZSP400 Digital Signal Processor

Voice over IP applications require numerous speech codec technologies to convey voice signals over the TCP/IP networks. The major speech codecs implemented in the ZSP firmware include  $<7.1 \mu$ /A, G.722, G.722.1, G.722.2, G.723.1, G726, G.729A/B and G.167 Acoustic Echo Cancellation. The ZSP firmware is available in binary format.

### Switch Engine

A 3-port switch engine contains a 10BASE-T/100BASE-TX MAC that supports full-duplex flow control and half-duplex back pressure collision flow control. The switch engine facilitates non-blocking packet switching at 1 Gbps, and programmable rate limiting from 0 - 100 Mbps on 1 oth input and output. The device contains broadcast storm protections and snooping support for Municast packet filtering. Two ports are used to communicate with the external Ethernet interface. The third port is used for internal communication between the switch and the Ethernet DMA block as shown in Figure 1.

### 10/100 Mbps Ethernet PHY

The KSZ8342 contains two Ethernet P<sup>1</sup>Y devices, one per port. Each 10/100 TX/RX PHY supports adaptive equalization and baseline warde correction. For maximum power savings, the PHY supports IEEE 802.3az MAC/PCS Energy Efficient Eurer, et (EEE) functions. The PHY is IEEE 802.3az compliant and contains loopback functions, on-chi<sub>N</sub> termination, an on-chip LDO and enhanced PLL for low EMI transmission. Note that the internal third communication port does not contain a PHY.

### SDRAM Memory Support

The KSZ8 42 Or support SDR memory up to 64 MB. A 16-bit data width is implemented for the SDR.

# U/RTand GPIO

The KSZ8342 contains a single industry-standard UART port. The KSZ8342Q 128-pin package contains 18 shared GPIO pins. There are no dedicated GPIO pins on the KSZ8342Q.

### Interrupt Controller

An integrated central interrupt controller facilitates low-latency interrupt service.

### Technology

The KSZ8342Q is fabricated using a 0.11 m process with a 1.2V core voltage and a 3.3V I/O voltage. The -NDr KSZ8342Q is available in a 128-pin PQFP package.

Table 1 lists the external interface for both the KSZ8342Q VoIP devices.

|    | Interface             | Usage                                                           |

|----|-----------------------|-----------------------------------------------------------------|

|    | SDRAM Memory          | Single data rate                                                |

|    | Flash                 | 4-bit wide serial NOR hoot ROM                                  |

|    | PCM                   | Analog telephone cornections — data                             |

|    | SPI SLIC              | Analog (e), onone connections —<br>configuration and debug only |

|    | Ethernet Ports        | Transmit/receive converted analog telephone signals — two ports |

|    | UART                  | Terminal connection                                             |

|    | MIPS EJTAG / ZSP JTAG | Shared debug and test port for<br>MIPS core and ZSP core        |

| ic | elconfident           |                                                                 |

### Table 1. KSZ8342 External Interfaces

### **Applications** 3

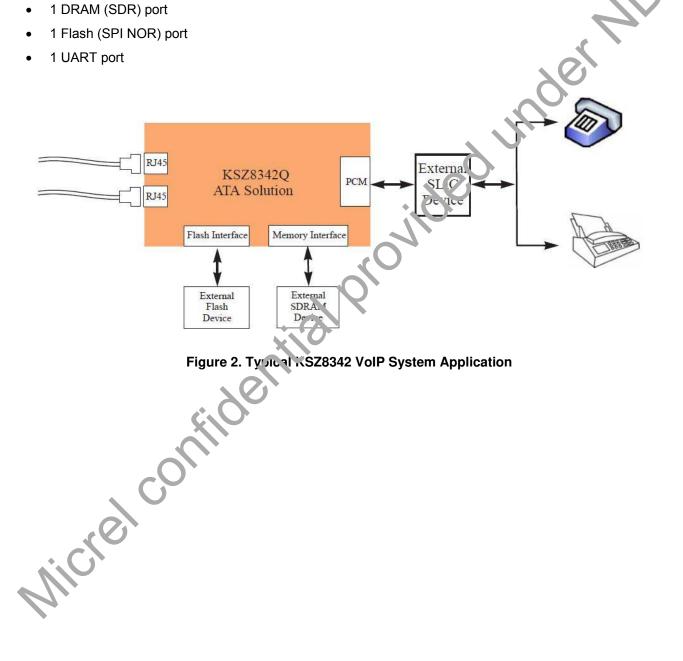

The KSZ8342Q provides the following external interfaces to support connection to one or more of the following peripherals shown in Figure 2.

- 2 Ethernet 802.3 transceiver interfaces •

- 1 PCM interface for connection to analog telephone .

- 1 DRAM (SDR) port •

- 1 Flash (SPI NOR) port

- •

### **Part Ordering Information** 4

|                                                 | -pin PQFP<br>-pin PQFP | Pb-free<br>Pb-free | Commercial tempera<br>solution.<br>Industrial tempera | $\neg \bigcirc$ |

|-------------------------------------------------|------------------------|--------------------|-------------------------------------------------------|-----------------|

| Kideniik                                        |                        |                    |                                                       | ature so utinn  |

|                                                 |                        | sided              | Junder                                                |                 |

| •                                               |                        |                    |                                                       |                 |

| Micrel Inc. • 2180 Fortune Drive • San Jose, CA |                        |                    |                                                       |                 |

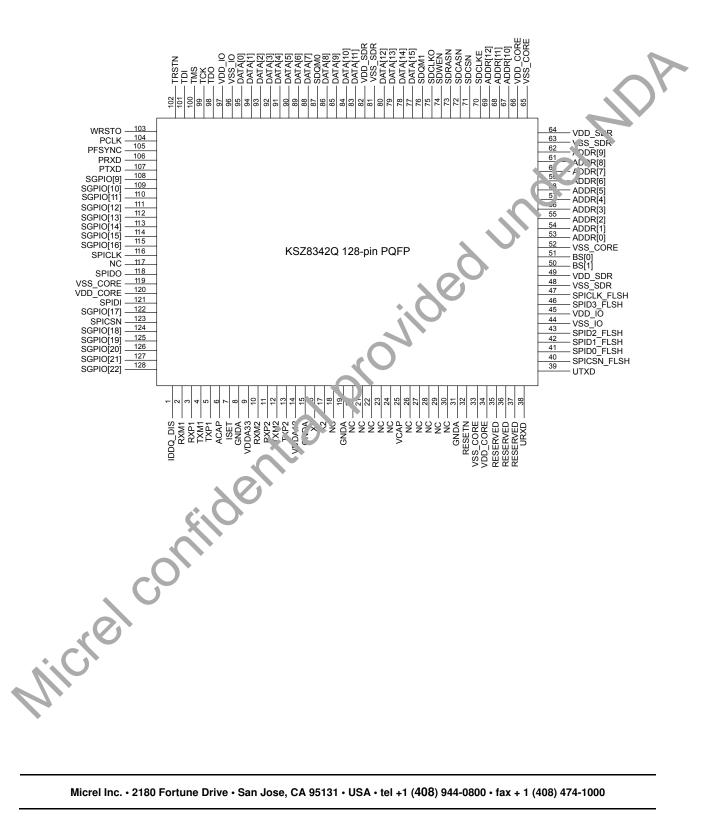

### **Package Pinout** 5

# 6 Pin Descriptions and Strapping Options

Table 2 lists the pin descriptions for the KSZ8342Q device. In this table, there are dedicated GPIO pins referred to by the name GPIO, and also multiplexed GPIO pin referred to by the name SGPIO.

| KSZ8342Q Pin<br>Number | Pin Name | Туре                          | Description                                                                                                                                       |

|------------------------|----------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                      | IDDQ_DIS | I                             | This pin contains an internal pull-up and is used during device manufacturing and test. It must not be connected during normal operation.         |

| 2                      | RXM1     | I/O                           | Physical receive or transmit signal (- differential).                                                                                             |

| 3                      | RXP1     | I/O                           | Physical receive or transmit signal ( - c'fferential).                                                                                            |

| 4                      | TXM1     | I/O                           | Physical transmit or receive signal (- differential).                                                                                             |

| 5                      | TXP1     | I/O                           | Physical transmit or receive signal (+ differential).                                                                                             |

| 6                      | ACAP     | PWR                           | Connect to Pin 1-, and a >1uF capacitor.                                                                                                          |

| 7                      | ISET     | I                             | Set PHY transmit output current.<br>Concect to ground through a 6.49 k Ohm 1% resistor.                                                           |

| 8                      | GNDA     | GND                           | Analog GND.                                                                                                                                       |

| 9                      | VDDA33   | PWR                           | 3.3V analog VDD.                                                                                                                                  |

| 10                     | RXM2     | 0                             | Physical receive or transmit signal (- differential).                                                                                             |

| 11                     | RXP2     | <i>.</i> /o                   | Physical receive or transmit signal (+ differential).                                                                                             |

| 12                     | TXM2     | 1/0                           | Physical transmit or receive signal (- differential).                                                                                             |

| 13                     | TXP2     | I/O                           | Physical transmit or receive signal (+ differential).                                                                                             |

| 14                     | VL DA 2  | PWR                           | Connect to Pin 6 (ACAP)                                                                                                                           |

| 15                     | GNDA     | GND                           | Analog GND.                                                                                                                                       |

| 16                     | X1       | l<br>LVTTL,<br>3.3-V tolerant | Crystal or oscillator clock connection.<br>This signal is the source clock of the internal PLL. The clock frequency<br>should be 25 MHz ± 50 ppm. |

### Table 2. KSZ8342Q Pin Descriptions

| KSZ8342Q Pin<br>Number | Pin Name    | Туре                     | Description                                                                                                                                              |

|------------------------|-------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17                     | X2          | 0                        | Crystal clock pin.<br>Pins (X1, X2) connect to a crystal. If an oscillator is used, X1 connects<br>to a 3.3V tolerant oscillator and X2 is a no connect. |

| 18                     | NC          |                          | This pin is not connected and should be left open.                                                                                                       |

| 19                     | GNDA        | GND                      | Analog GND.                                                                                                                                              |

| 20 - 24                | NC          |                          | This pin is not connected and should be left open.                                                                                                       |

| 25                     | VCAP        | 0                        | Decoupling cap for internal biasing voltage                                                                                                              |

| 26                     | NC          |                          | This pin is not connected and should be 'en open.                                                                                                        |

| 27                     | NC          |                          | This pin is not connected and should be left open.                                                                                                       |

| 28                     | NC          |                          | This pin is not connected and should be left open.                                                                                                       |

| 29                     | NC          |                          | This pin is not connected and should be left open.                                                                                                       |

| 30                     | NC          |                          | This pin is not connected and should be left open.                                                                                                       |

| 31                     | GNDA        | GND                      | Analog CI 'D.                                                                                                                                            |

| 32                     | RESETN      | I                        | Hai twa e reset pin (active low).                                                                                                                        |

| 33                     | VSS_CORE    | GND                      | Digital core GND.                                                                                                                                        |

| 34                     | VDD_CORE    | PWR                      | 1.2V digital core VDD.                                                                                                                                   |

| 35 - 37                | Reserved    | V TI. Schmitt<br>Trigger | This pin is used during manufacturing test and must be tied to ground during normal operation.                                                           |

| 38                     | URXD        | I<br>LVTTL               | UART receive data.                                                                                                                                       |

| 39                     | LTXD        | O<br>8mA, LVTTL          | UART transmit data.                                                                                                                                      |

| 40                     | SFICSN_FLSH | O<br>8mA, LVTTL          | Serial NOR Flash memory chip select, asserted low. This output signal is connected to the chip select input of the NOR Flash.                            |

| 41                     | SPIDO_FLSH  | I/O<br>8mA, LVTTL        | Serial NOR Flash data pin bit 0. This bidirectional signal is connected to the lowest-order data bit for 1-, 2- and 4-bit Flash devices.                 |

| KSZ8342Q Pin<br>Number | Pin Name     | Туре                  | Description                                                                                                                                   |

|------------------------|--------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 42                     | SPID1_FLSH   | I/O<br>8mA, LVTTL     | Serial NOR Flash data pin bit 1. This bidirectional signal is connected to the high-order bit in a 2-bit Flash, or to bit 1 in a 4-bit Flash. |

| 43                     | SPID2_FLSH   | I/O<br>8mA, LVTTL     | Serial NOR Flash data pin 2. This bidirectional signal is used on youner connecting to a 4-bit Flash.                                         |

| 44                     | VSS_IO       | GND                   | Digital I/O GND.                                                                                                                              |

| 45                     | VDDIO        | PWR                   | 3.3V digital I/O VDD.                                                                                                                         |

| 46                     | SPID3_FLSH   | I/O<br>8mA, LVTTL     | Serial NOR Flash data pin bit 3. This bidiry ct. na signal is used only when connecting to a 4-bit Flash.                                     |

| 47                     | SPICLK_FLSH  | O<br>8mA, LVTTL       | Serial NOR Flash clock pin output. This signal connects to the clock input of the Flash device.                                               |

| 48                     | VSS_SDR      | GND                   | GND for internal SDRAM n em ry controller.                                                                                                    |

| 49                     | VDD_SDR      | PWR                   | 3.3V for internal SDLAN, memory controller.                                                                                                   |

| 50-51                  | BS[1:0]      | I/O<br>8mA, LVTTL     | SDRAM bank st lect [1:0].<br>For DRAM devicts, these pins are used as SDRAM Bank Select pins<br>BS[1:0].                                      |

| 52                     | VSS_CORE     | GND                   | Digiral core GND.                                                                                                                             |

| 53-62                  | ADDR[0:9]    | O<br>SSTL18<br>LVT1.  | SPRAM memory address pins [0:9].                                                                                                              |

| 63                     | VSS_SDR      | Gi 'D                 | GND for internal SDRAM memory controller.                                                                                                     |

| 64                     | VDD_SDR      | PWR                   | 3.3V for internal SDRAM memory controller.                                                                                                    |

| 65                     | VSS_CORE     | GND                   | Digital core GND.                                                                                                                             |

| 66                     | VDD_CORL     | PWR                   | 1.2V digital core VDD.                                                                                                                        |

| 67-69                  | ADDr.[10:12] | O<br>SSTL18,<br>LVTTL | SDRAM memory address pins [10:12].                                                                                                            |

| 70                     | SDCLKE       | O<br>SSTL18,<br>LVTTL | SDRAM clock enable.<br>Clock Enable output for SDRAM interface.<br>Can be used for power down mode.                                           |

| KSZ8342Q Pin |             |                         |                                                                                                                              |

|--------------|-------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Number       | Pin Name    | Туре                    | Description                                                                                                                  |

| 71           | SDCSN       | O<br>SSTL18,<br>LVTTL   | SDRAM chip select, asserted low.                                                                                             |

| 72           | SDCASN      | O<br>SSTL18,<br>LVTTL   | SDRAM column address Select, asserted low.                                                                                   |

| 73           | SDRASN      | O<br>SSTL18,<br>LVTTL   | SDRAM row address Select, asserted low.                                                                                      |

| 74           | SDWEN       | O<br>SSTL18,<br>LVTTL   | SDRAM write enable, asserted low.                                                                                            |

| 75           | SDCLKO      | O<br>SSTL18             | SDRAM clock output.<br>Clock output for SDRAM in terface.<br>Single ended clock for COF, differential clock for SDRAM.       |

| 76           | SDQM1       | O<br>SSTL18,<br>LVTTL   | SDRAM data mas                                                                                                               |

| 77-80        | DATA[15:12] | I/O<br>SSTL18,<br>LVTTL | Mernory data bus[15:12]<br>Bidirectional bus for 16-bit data input and output. The data bus is for<br>CORAM memory accesses. |

| 81           | VSS_SDR     | GN₽                     | GND for internal SDRAM memory controller.                                                                                    |

| 82           | VDD_SDR     | P.VR                    | 3.3V for internal SDRAM memory controller.                                                                                   |

| 83-86        | DATA[11:8]  | I/O<br>SSTL18,<br>LVTTL | Memory data bus [11:8]<br>Bidirectional bus for 16-bit data input and output. The data bus is for<br>SDRAM memory accesses.  |

| 87           | SDQM        | O<br>SSTL18,<br>LVTTL   | SDRAM data mask.                                                                                                             |

| 88-95        | DATA[7:0]   | I/O<br>SSTL18,<br>LVTTL | Memory data bus [7:0]<br>Bidirectional bus for 16-bit data input and output. The data bus is for<br>SDRAM memory accesses.   |

| 96           | VSS_IO      | GND                     | Digital I/O GND.                                                                                                             |

| 97           | VDD_IO      | PWR                     | 3.3V Digital I/O VDD.                                                                                                        |

| []                     |            |                               |                                                                                                                        |

|------------------------|------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------|

| KSZ8342Q Pin<br>Number | Pin Name   | Туре                          | Description                                                                                                            |

| 98                     | TDO        | O<br>4mA,<br>LVTTL            | JTAG test data output.                                                                                                 |

| 99                     | тск        | I<br>LVTTL                    | JTAG test clock.                                                                                                       |

| 100                    | TMS        | I<br>LVTTL                    | JTAG test mode select.                                                                                                 |

| 101                    | TDI        | I<br>LVTTL                    | JTAG test data input.                                                                                                  |

| 102                    | TRSTN      | l<br>LVTTL Schmitt<br>Trigger | JTAG test reset.<br>Reset signal for JTAG controller:                                                                  |

| 103                    | WRSTO      | O<br>8mA,<br>LVTTL            | Watchdog timer reset cutrut<br>When the Watchdog Timer expires, this signal will be asserted for at<br>least 200 msec. |

| 104                    | PCLK       | I/O<br>8mA,<br>LVTTL          | PCM bus clock. Used for PCM bus timing.                                                                                |

| 105                    | PFSYNC     | I/O<br>8mA,<br>LVTT⊵          | PCM frame sync.<br>I rame synchronization signal for the PCM bus. This signal is<br>ynchronous to PCLK.                |

| 106                    | PRXD       | I VTTL                        | PCM receive data. Input data from PCM bus.                                                                             |

| 107                    | PTXD       | O<br>8mA,<br>LVTTL            | PCM transmit data. Output data to PCM bus. The signal is synchronous to PCLK.                                          |

| 108 - 115              | GPIC[9.16] | I/O<br>8mA,<br>LVTTL          | Shared GPIO pins 9 - 16.                                                                                               |

| 116                    | SPICK      | I/O<br>8mA,<br>LVTTL          | SLIC SPI clock output. This signal is used only for configuration and debug of the external SLIC device.               |

| 117                    | NC         |                               | This pin is not connected and should be left open.                                                                     |

| Number  | Pin Name    | Туре                 | Description                                                                                                    |

|---------|-------------|----------------------|----------------------------------------------------------------------------------------------------------------|

| 118     | SPIDO       | O<br>8mA,<br>LVTTL   | SLIC SPI data output. This signal is used only for configuration and debug of the external SLIC device.        |

| 119     | VSS_CORE    | GND                  | Digital Core GND.                                                                                              |

| 120     | VDD_CORE    | PWR                  | 1.2V Digital Core VDD.                                                                                         |

| 121     | SPIDI       | l<br>8mA,<br>LVTTL   | SLIC SPI data input. This signal is used only for configuration and debug of the external SLIC device.         |

| 122     | SGPIO[17]   | I/O<br>8mA,<br>LVTTL | Shared GPIO pin 17.                                                                                            |

| 123     | SPICSN      | O<br>8mA,<br>LVTTL   | SLIC SPI chip select output. This signal is used only for configuration and debug of the external SLIC device. |

| 124-128 | GPIO[18:22] | I/O<br>8mA,<br>LVTTL | Shared GPIO p. 1s 18 - 22.                                                                                     |

|         |             | ż                    | 2                                                                                                              |

| Mic     | sel conti   | dent                 |                                                                                                                |

|         | sel cor     |                      | A 95131 · USA · tel +1 (408) 944-0800 · fax + 1 (408) 474-1000                                                 |

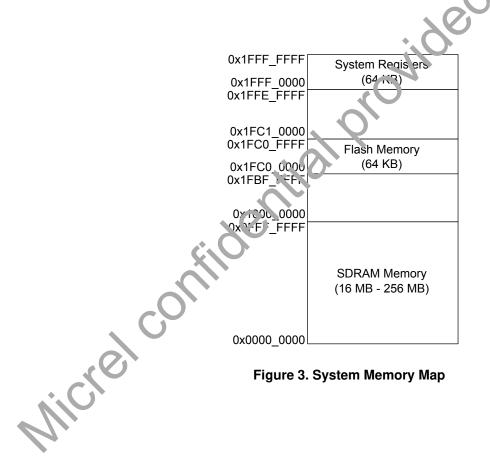

# 7 System Memory Map

As noted earlier, the KSZ8342 supports up to 64MB of SDR memory. It supports up to 64MB of Serial Flash memory.

The system memory map is 512MB in size and is organized as shown in Figure 3. It consists of

- System Registers: 64KB located at the top of the memory map.

- Flash memory: is remapped at boot time by software. The KSZ8342 supports serial NOT. Fla. h devices of 64MB in size. For NAND Flash devices, the memory is accessed indirectly. As such, NAND Flash is accessed via a 64KB space in the memory map.

- **ZSP Memory**: For the ZSP memory, bits 31:19 of the *ZSP External Memory* register nocated at offset address 0x0014 determines where the 512KB block of ZSP memory resident in physical address space.

- **SDR memory**: located at the bottom of the memory map.

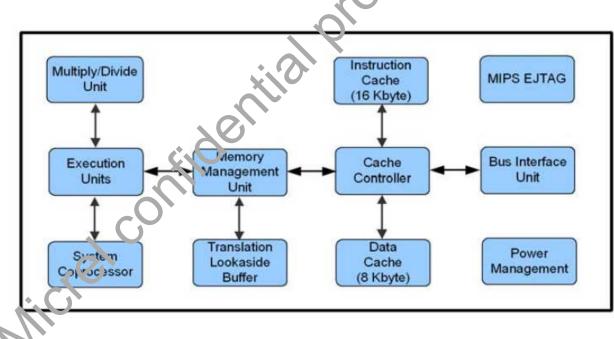

# 8 MIPS Processor Core

The KSZ8342 integrates a MIPS32 M4KEc as the central processing unit for the VoIP SoC. This includes optimized MIPS32 M4KEc configuration options for VoIP, including cache size, cache organization, CPU register size, and memory BIST. This section provides an overview of the MIPS Processor. For further details see the section "MIPS32® 4KEc® Processor Core Datasheet, Revision 02.03, March 4, 2008."

under

The KSZ8342 implements the M4KEc with the following characteristics:

- 5 pipeline stages

- Clock speeds of 25/62.5/125/166 MHz

- 2 way set associative 16 KB I-Cache

- 2 way set associative 8 KB D-Cache

- 2 register file sets

- EJTAG TAP controller

- 4/2 Instruction/Data hardware breakpoints

The MIPS CPU clock rate is set via bits 2:0 of the *System Clock an* 1 B<sub>c</sub> s *Control* register located at offset 0x000C.

### Figure 4. MIPS 4KEc Processor Block Diagram

# 8.1 Execution Units

The 4KEc core execution unit in the KSZ8342 VoIP solution implements a load/store architecture with singlecycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The 4KEc™ core contains thirty-two 32-bit general-purpose registers used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline. Herny

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Branch determination and branch target calculation

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data • producing instructions are followed closely by consumers of their results.

- Zero/One detect unit for implementing the CLZ and CLC in tructions •

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

# 8.2 Multiply/Divide Unit (MDU)

The 4KEc core in the KSZ8342 VoIP solution contains a multiply/divide unit (MDU) that includes a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the integer unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows long-running MDU operations, such as a divide, to be partially masked by system stalls and/or other integer unit instructions.

The MDU supports execution of a 16:35 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every click cycle. Appropriate interlocks are implemented to stall the issue of back-to-back 32x32 multiply be alons. Multiply operand size is automatically determined by logic built into the MDU.

Divide operations are includemented with a simple 1 bit per clock iterative algorithm. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

# System Coprocessor

The MPS 4KEc system coprocessor (CP0) in the KSZ8342 VoIP solution is responsible for the virtual-tophysical address translation and cache protocols, the exception control system, the processor's diagnostics

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000

capability, and the operating modes (kernel, user, and debug), interrupts enabled or disabled. Configuration information such as cache size and set associativity is available by accessing the CP0 registers.

# 8.4 Memory Management Unit

The MIPS 4KEc core in the KSZ8342 VoIP solution contains a fully functional MMU that interfaces between the execution unit and the cache controller. The TLB consists of two address translation buffers; a 16 duan entry fully associative Joint TLB (JTLB) and a two-entry fully associative Instruction TLB (ITLB).

When an instruction address is calculated, the virtual address is compared to the contents of the two-entry ITLB. If the address is not found in the ITLB, the JTLB is accessed. If the entry is found in the JTLB, that entry is then written into the ITLB. If the entry is not found in the JTLB, a TLB refill exception is taken.

ded

# 8.5 Translation Lookaside Buffer

The TLB consists of two address translation buffers;

- 16 dual-entry fully associative Joint TLB (JTLB)

- 2-entry fully associative Instruction TLB (ITLB)

## 8.5.1 Joint TLB

The MIPS 4KEc in the KSZ8342 VoIP solution implements a no dual-entry, fully associative Joint TLB (JTLB). The purpose of the TLB is to translate virtual addresses and their corresponding address space identifier (ASID) into a physical memory address. The JTLB is organized in page pairs to minimize the overall size. Each *tag* entry corresponds to 2-data entries, and ven page entry and an odd page entry. The highest order virtual address bit not participating in the tag comparison is used to determine which of the data entries is used. Since page size can vary on a page-pair basis, the determination of which address bits participate in the comparison and which bit is used to make the even-odd determination is decided dynamically during the TLB lookup.

# 8.5.2 Instruction T.B

The Instruction TLB (IT\_B) is a small 2-entry, fully associative TLB dedicated to performing translations for the instruction stream. The ITLB only maps 4-Kbyte pages/sub-pages. The ITLB is managed by hardware and is transparent to software. The larger JTLB is used for load/store address translations and as a backing store for the ITLB. If a fetch address cannot be translated by the ITLB, the JTLB is used to attempt to translate it in the following clock cycle. If successful, the translation information is copied into the ITLB for further use.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000

# 8.6 Cache Controller

The MIPS 4KEc core cache controller in the KSZ8342 VoIP solution is used to control accesses to the instruction and data cache. The KSZ8342 implements a 16 KB instruction cache and an 8 KB data cache. Each cache can each be accessed in a single processor cycle. In addition, each cache has its own 32-bit data path and both caches can be accessed in the same pipeline clock cycle. Bus Interface (BIU) The MIPS 4KEc Bus Interface Unit (BIU) in the KSZ8342 VoIP solution controls the external interface signals. Additionally, it contains the implementation of the 32-byte collapsing write buffer. The purpose of this punct is to store and combine write transactions before issuing them at the external interface. Since the 4KEc core caches follow a write-through cache policy, the write buffer significantly reduces the number of writes transactions on the external interface as well as reducing the amount of stalling in the constant to issuance of multiple writes in a short period of time.

# 8.7 Enhanced JTAG (EJTAG)

The MIPS 4KEc core in the KSZ8342 VoIP solution includes an Enhanced VTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to star 1a, duser mode and kernel modes of operation, the 4KEc core provides a Debug mode which is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a debug exception return (DERET) instruction is executed. During this time the processor executes the debug exception handler routine. The EJTAG interface operates through the Trist a ccess Port, a serial communication used for transferring test data in and out of the 4KEc core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define what registers are selected and how they are used. In the KSZ8342, the five external JTAG ping are multiplexed internally between the MIPS JTAG unit and the ZSP JTAG unit. Similarly, the TDO or using bit 8 of the ZSP Control register located at offset address 0x0018. If this bit is cleared, the result from the MIPS JTAG unit is driven onto TDO. If this bit is set, the result from the ZSP JTAG unit is driven onto TDO.

# 8.8 Power Management

The MIPS 4KEc core in the KSZ8342 VoIP solution offers a number of power management features, including low-power design, active power management and power-down modes of operation. The 4KEc core is a static clasing that supports a WAIT instruction designed to signal the rest of the device that execution and clocking should be halted, reducing system power consumption during idle periods.

The 4KEc<sup>™</sup> core provides two mechanisms for system level low power support:

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000

- Register controlled power management •

- Instruction controlled power management ٠

# 9 ZSP Voice Module Processor

The ZSP is to process audio data between the PCM controller and the MIPS CPU. Its main function includes voice data compression, decompression, PLC, dial tone generation, and miscellaneous speech CODEC functions. It contains an internal DMA for direct data transfer, between the ZSP and system DRAM/PCM (or A/D D/A). A special reset signal is controlled via a system register is used to enable the DMA (channel °) to self-start voice codec firmware transfer onto I-MEM for the ZSP core.

Note that the ZSP processor does not include any programmable function that can be controlled by the user. All ZSP programming is done through the MIPS processor. The initial clock rate for the ZSP module is determined as shown in **Error! Reference source not found.**. This section provides an overview of the ZSP Voice Module Processor. For further details see the section "ZSP400 Digital Signal Processor Architecture, December 2001."

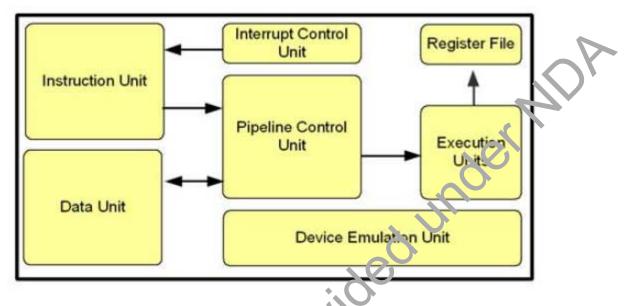

# 9.1 ZSP Architecture

The ZSP core is a 16-bit fixed point four-way superscalar digital signal processor (DSP) core. The five-stage pipeline processes up to 20 instructions at a time. The ZSP includes two multiply-accumulate execution unit (MACs) and two arithmetic logic units (ALUs).

The ZSP supports contains a dual 5-stage pipeline that supports single cycle add-compare-select, bit manipulation, and 32-bit arithmetic and logic operations. The ZSP core generates separate 16-bit addresses for instruction fetches and data memory transactions.

# 9.2 8.2 ZSP Functional Units

The ZSP core consists of seven functional units:

- Data Unit

- Instruction Unit (3∠ KW)

- Pipeline Control Unit (32 KW)

- Arithmetic Legic Unit

- Multiply Accumulate Unit

- Orerand Register File Unit

- Device Emulation Unit

A block diagram of the core illustrating how the functional units are interconnected is shown in Figure 5. Each of these blocks is described briefly in the following subsections.

Figure 5. ZSP Internal Block Diagram

### 9.2.1 Instruction Unit

The instruction unit is comprised of the instruct or mache, prefetch unit, program counter control, and instruction dispatcher. The instruction cache is direct-mapped and holds eight lines of four words each. Four instructions are prefetched each clock c, cle and forwarded to the pipeline control unit for grouping. The prefetch unit utilizes static branch are are in and prefetch techniques to minimize cache miss penalties and reduce pipeline stalls.

## 9.2.2 Data Unit

The data unit is comprised of the data cache, data prefetch unit, circular buffers, and load/store arbitration unit. Each cycle the data unit can prefetch and cache four data words. The write logic can perform one single or double words store per cycle. The data unit also provides hardware for the implementation of two circular buffers and three data linking registers.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000

## 9.2.3 Pipeline Control Unit

The pipeline control unit groups instructions for parallel execution and synchronizes the execution of these instructions through the pipeline. To perform instruction grouping, the pipeline control unit resolves data and resource dependencies in the program sequence. This allows the hardware to schedule instructions for execution by the functional units, removing this task from the programmer or compiler. The pipeline control unit handles branch mispredictions, interrupts, and stalls from external memory accesses.

## 9.2.4 Execution Units

The ZSP contains two identical 16-bit ALUs which can work independently or together to form a single 32-bit ALU. In addition to traditional ALU functionality, the ALUs also provide bit manipulation and no malization capability.

In addition to the ALU's, the ZSP integrates two MAC units that can work together condependently. Independently, they can each perform a 16-bit by 16-bit multiply with a single 40-bit accumulation in a single cycle. Together, they work to perform a 32-bit by 32-bit multiply with 40-bit accumulation in a single cycle. The MACs also contain hardware support for complex multiplies and the functionality to perform a single-cycle add-compare select for Viterbi decoding.

### 9.2.5 Register Files

The ZSP has two register files: the operand register file and the control register file. The operand register file consists of 16 general purpose registers, half of which are shadowed. The control register file maintains registers which control the state and operation of the core. All registers are user visible (read and write).

# 9.2.6 Device Emulation Unit

The ZSP contains dedicated logic to support sophisticated emulation and debugging functions.

# 9.3 ZSP Boot Process

The ZSP processor in he CSZ8342 VoIP solution does not boot automatically on reset, but rather remains in the reset state. To Loot the ZSP processor, software must set bit 0 of the *ZSP Control* register located at offset address 0x0018.

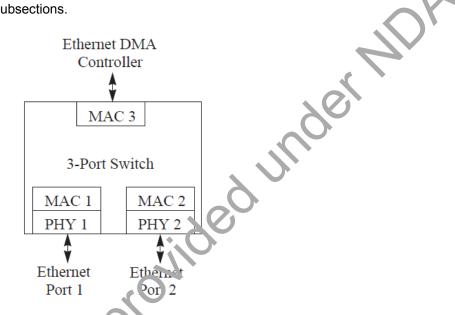

# 10 3-Port Switch

The KSZ8342 contains a 3-port switch. Two ports are used for external Ethernet communication and facilitate power efficient switching in 10/100 Mbps Ethernet applications. The third port is used internally to communicate with the Ethernet DMA controller. This concept is shown in Figure 6. Each of the blocks in this figure is described in the following subsections.

Figure 6. 3-Port Switch Connections

The switch contains advanced power management and sophisticated QoS features, including IPv6 priority classification support. Advanced power management features of the 3-port switch include hardware power down, software power down, per port so ver down, and the energy detect mode that shuts downs the transceiver when a port is id'e.

The KSZ8342 VoIP SoC 3 pc.+ switch contains the following main features:

- Low Power (32 bit data width @ 31.25MHz)

- Non-bicking packet switching throughput at wire speed

- 2x 8 12.3 FHYs + 1x MII for internal EDMA

- IEEE 802.1Q VLAN support for up to 16 groups full-range of VLANID)

- VLAN ID tag/un-tag options, per-port basis

- > IEEE 802.1p/q tag insertion or removal on a per port basis (egress)

- Programmable rate limiting from 0 to 100 Mbps at the ingress and egress ports

- Broadcast storm protection •

- IEEE 802.1D Spanning Tree Protocol support ٠

- Special Tagging Mode to inform the processor which ingress port

- IGMP v1/v2 Snooping support for multicast packet filtering •

- Double Tagging support ٠

# 10.1 Media Access Controller (MAC)

The KSZ8342 contains a dedicated Media Access Controller (MAC) for each Ethernet port. The MAC processes data moving between the 3-port switch and the PHY as shown in Figure 1. The MAC performs the following functions: dedur

- Address Lookup

- Learning

- Migration

- Aging

- Forwarding

### 10.1.1 Address Lookup

An internal lookup table stores MAC addresses and their associated information. It contains a 1K Unicast address table plus switching information.

### 10.1.2 Learning

The KSZ8342 is guaranteed to learn 1K and esses and distinguishes itself from hash-based lookup tables, which depending on the operating environment and probabilities, may not guarantee the absolute number of addresses it can learn. The interration updates its table with a new entry if the following conditions are met:

- 1. The received packet's Source Address (SA) does not exist in the lookup table.

- 2. The received packet is good; the packet has no receiving errors, and is of legal length. The lookup engine inserts the rualified SA into the table, along with the port number and time stamp. If the table is full, the last entry of the table is deleted to make room for the new entry.

### Migration 10.1

The internal lookup engine also monitors whether a station has moved. If a station has moved, it will update the table accordingly. Migration happens when the following conditions are met:

1. The received packet's source address is in the table but the associated source port information is different.

2. The received packet is good; the packet has no receiving errors, and is of legal length.

The lookup engine will update the existing record in the table with the new source port information.

### 10.1.4 Aging

The lookup engine updates the time stamp information of a record whenever the corresponding SA appears. The time stamp is used in the aging process. If a record is not updated for a period of time, the lockup angine removes the record from the table. The lookup engine constantly performs the aging process and will continuously remove aging records. The aging period is about 300 seconds. This feature can be enabled or disabled through register 3 (0x03) bit [2].

### 10.1.5 Forwarding

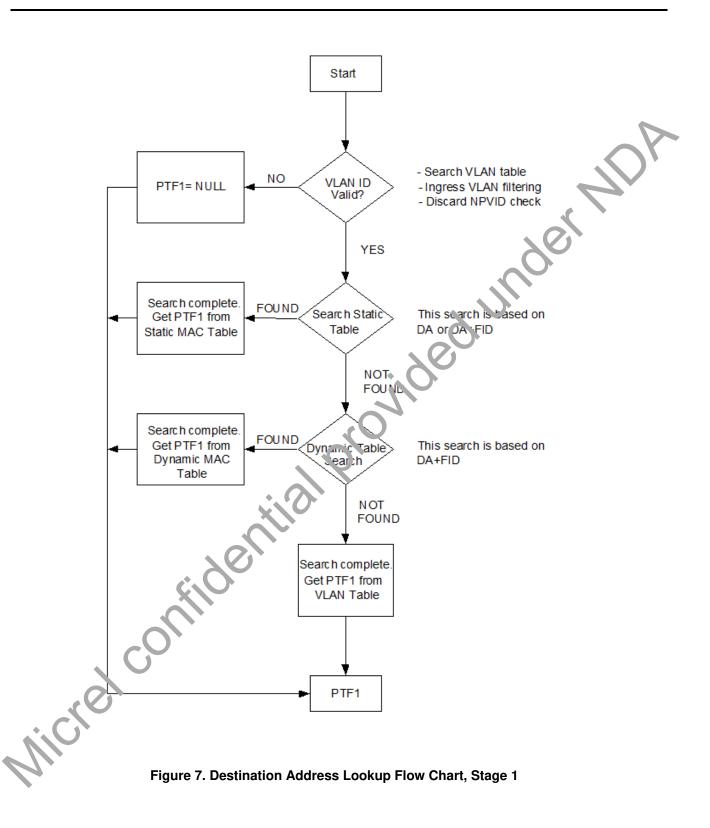

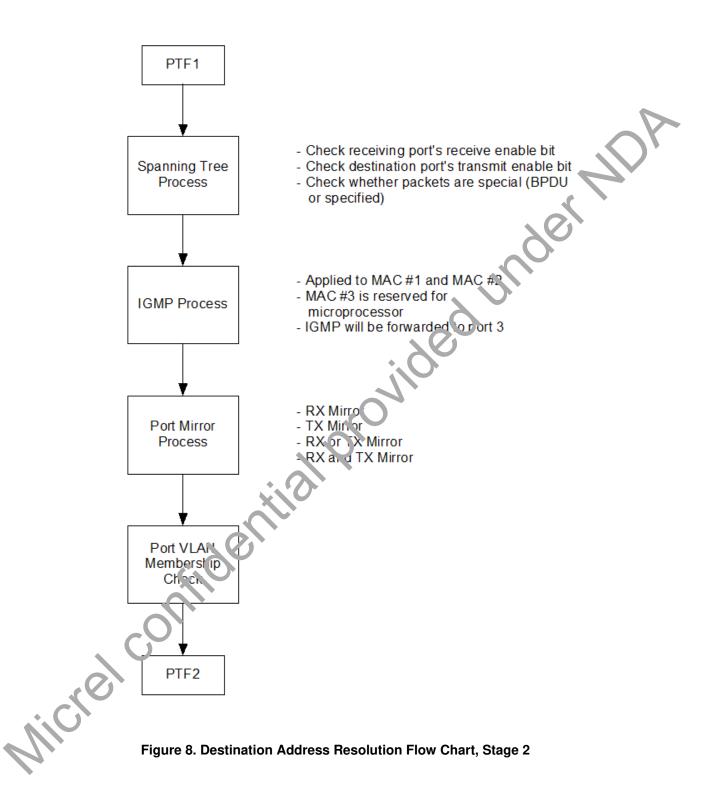

The KSZ8342 forwards packets using the algorithm that is depicted in the following flowcharts. Figure 7 shows stage one of the forwarding algorithm where the search engine Iro's up the VLAN ID, static table, and dynamic table for the destination address, and comes up with "port to forward 1" (PTF1). PTF1 is then further modified by spanning tree, IGMP snooping, port mirroring, and port VLAN processes to come up with "port to forward 2" (PTF2), as shown in Figure 8. The packet is sent to PTr2.

ri. .ket is s itano itan

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000

The switch will not forward the following types of packets:

- Error packets: These include framing errors, Frame Check Sequence (FCS) errors, alignment errors, and illegal size packet errors.

- IEEE802.3x PAUSE frames: The switch intercepts these packets and performs full duplex flow control

accordingly.

- Local packets based on destination address (DA) lookup: If the destination port from the lookup to ble matches the port from which the packet originated, the packet is defined as "local."

### 10.1.6 MAC Operation

The KSZ8342 MAC strictly abides by IEEE 802.3 standards to maximize compatibility.

### Inter Packet Gap (IPG)

If a frame is successfully transmitted, the 96 bits time IPG is measured between the two consecutive MTXEN. If the current packet is experiencing collision, the 96 bits time IPG is measured from MCRS and the next MTXEN.

### Back-Off Algorithm

The KSZ8342 implements the IEEE 802.3 standard for the binary exponential back-off algorithm, and optional "aggressive mode" back-off. After 16 collisions, the packet is optionally dropped depending on the switch configuration for register 4 (0x04) bit [3].

### Late Collision

If a transmit packet experiences collisions ofter 512 bit times of the transmission, the packet is dropped.

### Illegal Frames

The KSZ8342 discards frames up to 1518 bytes, 1536 bytes or 1916 bytes. These maximum frame size settings are programmed in register 4 (0x04). Since the KSZ8342 supports VLAN tags, the maximum sizing is adjusted when these tags are present.

### Full Duplex Flow Control

The KSZ8342 st pports standard IEEE 802.3x flow control frames on both transmit and receive sides. On the receive side, if the KSZ8342 receives a pause control frame, the KSZ8342 will not transmit the next normal frame crucin the timer, specified in the pause control frame, expires. If another pause frame is received before the current timer expires, the timer will be updated with the new value in the second pause frame. During this period (while it is flow controlled), only flow control packets from the KSZ8342 are transmitted.

On the transmit side, the KSZ8342 has intelligent and efficient ways to determine when to invoke flow control. The flow control is based on availability of the system resources, including available buffers, available transmit queues and available receive queues.

The KSZ8342 will flow control a port that has just received a packet if the destination port resource is busy. The KSZ8342 issues a flow control frame (XOFF), containing the maximum pause time defined by the IEEE 802.3x standard. Once the resource is freed up, the KSZ8342 sends out the other flow control frame (XON) with zero pause time to turn off the flow control (turn on transmission to the port). A hysteresis feature is provided to prevent the flow control mechanism from being constantly activated and deactivated.

The KSZ8342 flow controls all ports if the receive queue becomes full.

### Half-Duplex Backpressure

A half-duplex backpressure option (not in IEEE 802.3 standards) is also provided. The activation and deactivation conditions are the same as full duplex flow control. If backpress are is required, the KSZ8342 sends preambles to defer the other stations' transmission (carrier sense depiction).

To avoid jabber and excessive deference (as defined in the 802.3 s and ard), after a certain time, the KSZ8342 discontinues the carrier sense and then raises it again huckly. This short silent time (no carrier sense) prevents other stations from sending out packets this keeping other stations in a carrier sense deferred state. If the port has packets to send during a backpressure situation, the carrier sense type backpressure is interrupted and those packets are transmitted instead. If there are no additional packets to send, carrier sense type backpressure is reactively again until switch resources free up. If a collision occurs, the binary exponential back-off algorithm is skipped and carrier sense is generated immediately, thus reducing the chance of further collisions and carrier sense is maintained to prevent packet reception. To ensure no packet loss in 10 BASE-T or 100 BASE-TX half duplex modes, the user must enable the following:

- Aggressive back-off (reg ster 2 (Jx03), bit [0])

- No excessive collision drup (register 4 (0x04), bit [3])

Note: These bits are not set as defaults, as this is not the IEEE standard.

### Broadcast Storm Protection

The KSZ8542 bas an intelligent option to protect the switch system from receiving too many broadcast packets. As the broadcast packets are forwarded to all ports except the source port, an excessive number of switch resources (bandwidth and available space in transmit queues) may be utilized. The KSZ8342 has the option to include "multicast packets" for storm control. The broadcast storm rate parameters are programmed globally, and can be enabled or disabled on a per port basis. The rate is based on a 67ms interval for 100BT

and a 500ms interval for 10BT. At the beginning of each interval, the counter is cleared to zero, and the rate limit mechanism starts to count the number of bytes during the interval. The rate definition is described in register 6 (0x06) and 7 (0x07). The default setting is 0x63 (99 decimal).

This is equal to a rate of 1%, calculated as follows:

148,800 frames/sec \* 67ms/interval \* 1% = 99 frames/interval (approx.) = 0x63

Note: The number 148,800 frames/sec is based on 64-byte block of packets in 100BASE-TX with 12 bytes of IPG and 8 bytes of preamble between two packets.

### Port Individual MAC Address and Source Port Filtering

The KSZ8342 provide individual MAC address for port 1 and port 2 respectively. They (an be set at register 142-147 and 148-153. With this feature, the CPU connected to the port 3 can receive the packets from two internet subnets which have their own MAC address.

The packet will be filtered if its source address matches the MAC address of port 1 or port 2 when the register 21 and 37 bit 6 is set to 1 respectively. For example, the packet will be 'or ped after it completes the loop of a ring network.

# 10.2 Physical Layer (PHY)

The KSZ8342 implements a 2-port 10/100 Mbps PHY interface that contains the following main features.

- On-chip LDO

- Loopback PHY BIST test

- IEEE 802.3az MAC/PCS EEE function

- Enhanced PLL for low EMI transmusion

- Intelligent power saving mod as

- On-chip termination

Each Ethernet port in the KSZ8342 VoIP solution supports the following transfer protocols.

- 100BASE-T Transmit

- 100BASE-1 Receive

- 10BASE Transmit

- 10F ASE-T Receive

Fach of these functions is described in the following subsections.

## 10.2.1 100BASE-T Transmit

The transmit function of the 100BASE-TX performs:

- Parallel-to-serial conversion

- 4B/5B coding

- scrambling

- NRZ-to-NRZI conversion

- MLT3 encoding and transmission

The data flow through the transmit circuit is as follows:

- 1. Parallel-to-serial conversion translates the MII data from the MAC into a 125MH2 sector bit stream.

- 2. The data and control stream are converted into 4B/5B coding, followed by a scrampler.

- 3. The serialized data is converted from NRZ-to-NRZI format, and then transmixed in MLT3 current output.

- 4. The output current is set by an external 1% 11.8k Ohm resistor for 'be 1:1 transformer ratio.

The output signal has a typical rise/fall time of 4ns and complies with the ANSI TP-PMD standard regarding amplitude balance, overshoot, and timing jitter. The wave-shaped 10BASE-T output is also incorporated into the 100BASE-TX transmitter.

The 100BASE-T transmit logic also contains a scramble. The purpose of the scrambler is to spread the power spectrum of the signal to reduce electromagnetic interference (EMI) and baseline wander. Transmitted data is scrambled through the use of an 11-bit with linear feedback shift register (LFSR). The scrambler generates a 2047-bit non-repetitive sequence, and the receiver then de-scrambles the incoming data stream using the same sequence as at the transmitter.

# 10.2.2 100BASE-T Receive

The 100BASE-TX receiver function performs:

- Adaptive e qualization

- DC res ora ion

- ML13-to-NRZI conversion

- Lata and clock recovery

- NRZI-to-NRZ conversion

- De-scrambling

- 4B/5B decoding

- Serial-to-parallel conversion

Incoming data passes through an equalization filter to compensate for inter-symbol interference (ISI) over the twisted pair cable. Since the amplitude loss and phase distortion is a function of the cable length, the equalizer must adjust its characteristics to optimize performance.

The variable equalizer makes an initial estimation based on comparisons of incoming signal strength against some known cable characteristics, and then tunes itself for optimization. This is an ongoing process and seladjusts against environmental changes such as temperature variations.

The equalized signal goes through a DC restoration and data conversion block. The DC restoration will be used to compensate for the effect of baseline wander and to improve the dynamic range.

The differential data conversion circuit converts the MLT3 format back to NRZI. The slicing threshold is also adaptive.

The clock recovery circuit extracts the 125MHz clock from the edges of the NRZI signal. This recovered clock is then used to convert the NRZI signal into the NRZ format. This signal is sont through the de-scrambler followed by the 4B/5B decoder. Finally, the NRZ serial data is converted to the MII format and provided as the input data to the MAC.

## 10.2.3 10BASE-T Transmit

The 10BASE-T driver is incorporated with the 100BASE-<sup>-</sup>X driver to allow for transmission using the same magnetic. They are internally wave-shaped and pre-e npr asized into outputs with typical 2.3V amplitude. The harmonic contents are at least 27dB below the fundamental frequency when driven by an all-ones Manchester-encoded signal.

## 10.2.4 10BASE-T Receive

On the receive side, input buffers and lovel detecting squelch circuits are employed. A differential input receiver circuit and a phase-received loop (PLL) perform the decoding function. The Manchester-encoded data stream is separated into clock signal and NRZ data. A squelch circuit rejects signals with levels less than 400mV or with short pulse widths to prevent noise at the RXP-or-RXM input from falsely triggering the decoder.

When the inrup exceeds the squelch limit, the PLL locks onto the incoming signal and the KSZ8342 decodes a data frame. The receiver clock is maintained active during idle periods in between data reception.

## 10.2.5 MDI/MDI-X Auto Crossover

To eliminate the need for crossover cables between similar devices, the KSZ8342 VoIP solution supports HP Auto MDI/MDI-X and IEEE 802.3u standard MDI/MDI-X auto crossover. HP Auto MDI/MDI-X is the default. The auto-sense function detects remote transmit and receive pairs and correctly assigns transmit and receive pairs for the KSZ8342 device. This feature is extremely useful when end users are unaware of cable types, and also, saves on an additional uplink configuration connection. The auto-crossover feature can be disable of through the port control registers, or MIIM PHY registers.

## 10.2.6 Auto-Negotiation

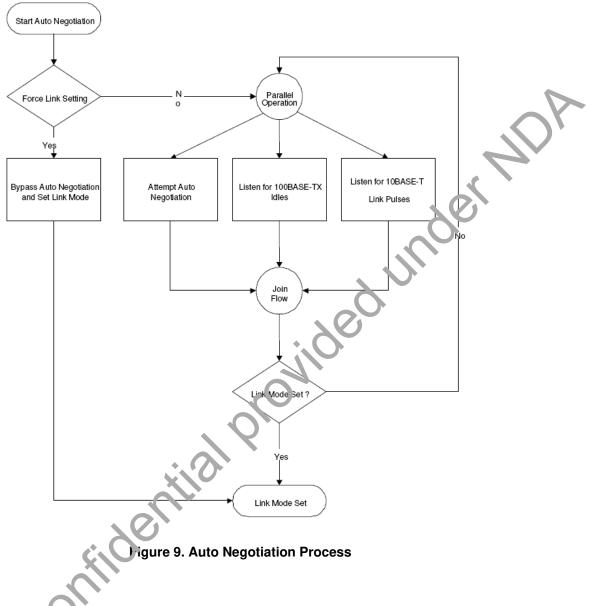

The KSZ8342 conforms to the auto-negotiation protocol, defined in Clause 28 of the IEEE 223u specification. Auto-negotiation allows unshielded twisted pair (UTP) link partners to specification mode of operation. In auto negotiation, link partners advertise their capabilities across the link to each other. If auto-negotiation is not supported or the KSZ8342 link partner is forced to bypass auto-negotiation, the KSZ8342 sets its operating mode by observing the signal at its receiver. This is known as parallel detection. and allows the KSZ8342 to establish link by listening for a fixed signal protocol in the absence of autonegotiation advertisement protocol. Figure 9 shows a flow diagram of the auto-negotiation process. s wiccel

# 10.2.7 PHY Power Management

The KSZ8342 supports enhanced power management feature in low power state with energy detection to ensure low-power dissipation during device idle periods. There are three operating modes under the power management function

#### · · ·ormal Operation Mode

Energy Detect Mode

Port Based Power Down Mode

Table 3 indicates all internal function blocks status under four different power management operation modes. For more information, please refer to Section 10, "Energy Efficient Ethernet."

#### Normal Operating Mode

This is the default setting bit[1:0] = 00 in register 195 after the chip power-up or hardware reset. When the KSZ8342 is in this mode, all PLL clocks are running. The PHY and MAC are on and the host interface is ready for a CPU read or write.

During the normal operation mode, the host CPU can set the bit[1:0] in register 195 to transit the current normal operation mode to any one of the other three power management operation

#### Energy Detect Mode

The energy detect mode provides a mechanism to save more power than in the normal operation mode when the KSZ8342 is not connected to an active link partner.

This mode can result in a power savings of up to 50% relative to normal mode. If the cable is unplugged, the KSZ8342 can automatically enter to a low power state (energy detect node). In this mode the KSZ8342 transmits 120ns width pulses at a 1 pulse/s rate. Once activity resulties due to plugging a cable or attempting by the far end to establish link, the KSZ8342 can automatically power up to normal power state from the energy detect mode.

Energy detect mode consists of two states, normal pc ver state and low power state. While in low power state, the KSZ8342 reduces power consumption by disabling all circuitry except the energy detect circuitry of the receiver. The energy detect mode is entered by setting bit[1:0] = 01 in register 195. When the KSZ8342 is in this mode, it monitors the cable energy . If there is no energy on the cable for a time longer than the programmed value in bits 7:0 (Go-Sloep time) in register 196, the KSZ8342 will go into a low power state.

#### Port based Power Down Mode

The KSZ8342 features a per-port power down mode. To save power, a PHY port that is not in use can be powered down via port co. trol register 29 or 45 bit 3, or MIIM PHY register. It will saves about 15 mA per port.

|                          | Power Management Operating Mode |                     |  |  |  |

|--------------------------|---------------------------------|---------------------|--|--|--|

| KSZ8342 Functional Block | Normal                          | Energy Detect       |  |  |  |

| Internal PLL clocks      | Enabled                         | Disabled            |  |  |  |

| Transmit/Receive PHY     | Enabled                         | Energy detect at Rx |  |  |  |

Troje 3. KSZ8342 Functional Block State per Power Management Operating Mode

| MAC            | Enabled | Disabled |

|----------------|---------|----------|

| Host Interface | Enabled | Disabled |

## 10.3 Advanced Switch Functions

## 10.3.1 Bypass Mode

The KSZ8342 also offer a by-pass mode which enables system- level power saving. When the Croc (connected to Port 3) enters a power saving mode of power down or sleeping mode, the KSZ8342 switches to the by-pass mode in which the switch function between Port1 and Port2 is sustained. In the Py pass mode, the packets with DA to port 3 will be dropped and by pass the internal buffer memory, reak, the buffer memory more efficiency for the data transfer between port 1 and port 2. Specially, the power saving get more in energy detect mode with the by-pass to be used.

## 10.3.2 IEEE 802.1Q VLAN Support

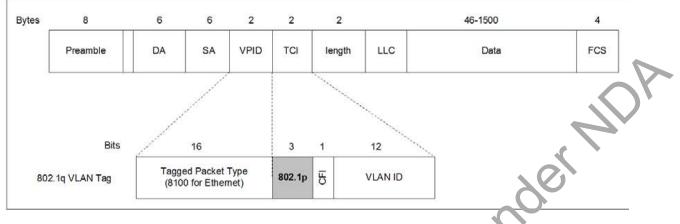

The KSZ8342 supports 16 active VLANs out of the 4096 possible V Ar's specified in the IEEE 802.1Q specification. KSZ8342 provides a 16-entry VLAN Table, which converts the 12-bits VLAN ID (VID) to the 4-bits Filter ID (FID) for address lookup. If a non-tagged or nu r-v'D-tagged packet is received, the ingress port default VID is used for lookup. In VLAN mode, the lookup process starts with VLAN table lookup to determine whether the VID is valid. If the VID is not valid, the packet is dropped and its address is not learned. If the VID is valid, the FID is retrieved for further lookup. Time F'D + Destination Address (FID+DA) are used to determine the destination port. The FID + Course Address (FID+SA) are used for address learning.

| Destination<br>Address Found in<br>Static MAC Table? | Use FID Fing? | FID Match  | DA + FID Found<br>in Dynamic<br>MAC Table? | Action Taken                                                                          |

|------------------------------------------------------|---------------|------------|--------------------------------------------|---------------------------------------------------------------------------------------|

| No                                                   | Don't Cara    | Don't Care | No                                         | Broadcast to the membership ports defined in the VLAN table bits [18:16]              |

| No                                                   | Dor." Care    | Don't Care | Yes                                        | Send to the destination port defined in the Dynamic MAC address table bits [53:52].   |