#### **PRELIMINARY**

March 1994

# DS3875 Futurebus + Arbitration Controller MIL-STD-883 General Description

(For a complete description of operation, please refer to the commercial datasheet.)

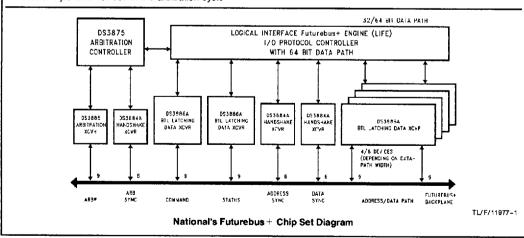

The DS3875 Futurebus + Arbitration Controller is a member of National Semiconductor's Futurebus + chip set designed specifically for the IEEE 896.1 Futurebus + standard. The DS3875 implements Distributed Arbitration and Distributed Arbitration messages in a single chip.

The DS3875 interfaces with Futurebus+ through the DS3885 BTL Arbitration Transceiver and the DS3884A BTL Handshake Transceiver. The DS3885 BTL Arbitration Transceiver incorporates the competition logic needed for the Arbitration Number signal lines. The DS3884A BTL Handshake Transceiver has selectable Wired-OR receiver glitch filtering. The DS3884A is used for the Arbitration Sequencing and Arbitration Condition signal lines.

Additional transceiver included in the military Futurebus + chip set is the DS3886A BTL 9-bit Latching Data Transceiver. The DS3886A transceiver features edge-triggered latches in the driver which may be bypassed during a fall-through mode and a transparent latch in the receiver.

The Logical Interface Futurebus + Engine (LIFE) I/O Protocol Controller with 64-bit Data Path incorporates the Compelled Mode Futurebus + Parallel Protocol. The Protocol Controller handles all the handshaking signals between the Futurebus + and the local bus interfaces, and incorporates a DMA Controller with built-in FIFOs for fast queueing.

#### **Features**

- The controller implements the complete requirements of the IEEE 896.1 specification as a subset of its features

- Supports Arbitration message sending and receiving

- Supports the two modes of operation (RESTRICTED/ UNRESTRICTED)

- Software configurable double/single pass operation, slow/fast, IBA/Parking and restricted/unrestricted modes of arbitration

- Built-in 1 μs timer for use in the arbitration cycle

- User programmable 16 arbitration delays (8 slow and 8 fast)

- Built-in PLL for accurate delays. The PLL accepts clocks from 2 MHz to 40 MHz in steps of 1 MHz

- Signal to unlock slave modules on transfer of tenure.

Auto unlock through a dummy cycle if the current master locked resources

- Programmable delay for releasing ar\* after issuing COMPETE/IBA\_CMPT. This is to ensure the assertion of the arbitration number during competition, before the release of ar\*. Also this delay ensures there is sufficient time to assert the AD/DATA lines during Idle Bus Arbitration before the release of ar\*

- Read/Write facility with data acknowledge for the host to load arbitration numbers, an arbitration message, and control registers

- On chip parity generator unloads the host of the additional parity generation function

- Separate interrupts to indicate error occurrence and arbitration message received. Interrupts cleared on a register write. Error status is available in a separate status register

- A special output pin to indicate that a POWERFAIL message was received

- Hardwired register to hold the first word of the arbitration message

- FIFO strobe provided to store more than one arbitration message externally to prevent overrun

- Idle Bus Arbitration (IBA) supported

- Parking implemented

- Bus initialization, system reset and Live-insertion supported. (The logic to detect these conditions must be implemented externally.)

- Testability in the form of reading from key registers which include the STATE, MCW, 1 µs timer and programmable input clock divider

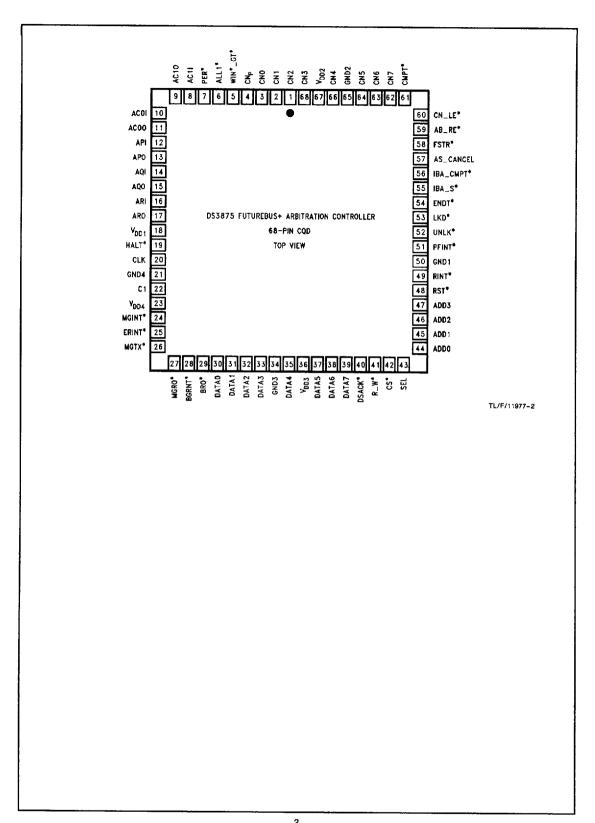

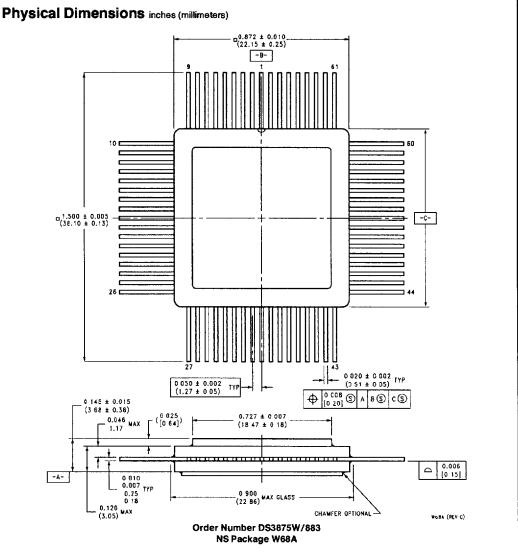

- 68-pin CQD Package

©1995 National Semiconductor Corporation TL/F/11977

RRD B30M105/Printed in U.S.A.

| Pin                                      | # of Pins | Туре   | Description                                                                                                                                                                                                                     |  |  |  |

|------------------------------------------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SIGNAL TO/FROM THE HANDSHAKE TRANSCEIVER |           |        |                                                                                                                                                                                                                                 |  |  |  |

| APO                                      | 1         | 0      | Arbitration handshake signal from the controller.                                                                                                                                                                               |  |  |  |

| AQO                                      | 1         | 0      | Arbitration handshake signal from the controller.                                                                                                                                                                               |  |  |  |

| ARO                                      | 1         | 0      | Arbitration handshake signal from the controller.                                                                                                                                                                               |  |  |  |

| AC0O                                     | 1         | 0      | Arbitration condition signal from the controller.                                                                                                                                                                               |  |  |  |

| AC1O                                     | 1         | 0      | Arbitration condition signal from the controller.                                                                                                                                                                               |  |  |  |

| API                                      | 1         | _      | Arbitration handshake signal from Futurebus +. This signal is the filtered and inverted version of the Futurebus + backplane signal AP*.                                                                                        |  |  |  |

| AQI                                      | 1         | l      | Arbitration handshake signal from Futurebus +. This signal is the filtered and inverted version of the Futurebus + backplane signal AQ*.                                                                                        |  |  |  |

| ARI                                      | 1         | _      | Arbitration handshake signal from Futurebus $+$ . This signal is the filtered and inverted version of the Futurebus $+$ backplane signal AR*.                                                                                   |  |  |  |

| AC0I                                     | 1         | 1      | Arbitration condition signal from Futurebus+.                                                                                                                                                                                   |  |  |  |

| AC11                                     | 1         | _      | Arbitration condition signal from Futurebus + .                                                                                                                                                                                 |  |  |  |

| SIGNAL TO/<br>Arbitration Tr             |           | ARBITR | ATION TRANSCEIVER (Note: These pins are mapped to/from the DS3885 Futurebus+                                                                                                                                                    |  |  |  |

| CN(7:0)                                  | 8         | 1/0    | The bus to carry competition number to/from the arbitration transceiver.                                                                                                                                                        |  |  |  |

| CNp                                      | 1         | 0      | Parity bit of the competition number.                                                                                                                                                                                           |  |  |  |

| CMPT*                                    | 1         | 0      | Enables the Arbitration number onto Futurebus+.                                                                                                                                                                                 |  |  |  |

| AB_RE*                                   | 1         | 0      | Direction control for the competition number bus to/from the transceiver.                                                                                                                                                       |  |  |  |

| CN_LE*                                   | 1         | 0      | Latch enable for latching the Arbitration number from the controller into the transceiver.                                                                                                                                      |  |  |  |

| PER*                                     | 1         | 1      | PARITY ERROR: Indicates that a parity error was detected on the winner's arbitration number.                                                                                                                                    |  |  |  |

| WIN*_GT*                                 | 1         | 1      | Win signal when competing/greater than signal when not competing (used to preempt).                                                                                                                                             |  |  |  |

| ALL1*                                    | 1         | 1      | Indicates that all the arbitration number lines on the bus are asserted (used for messages).                                                                                                                                    |  |  |  |

| SIGNALS TO                               | /FROM THE | PARAL  | LEL PROTOCOL CONTROLLER                                                                                                                                                                                                         |  |  |  |

| BRQ*                                     | 1         | ı      | BUS REQUEST: Indicates to the controller to acquire the bus for the module's use.                                                                                                                                               |  |  |  |

| BGRNT*                                   | 1         | 0      | BUS GRANT: Signal asserted by the controller after the detection of a bus request. The module can start using the bus.                                                                                                          |  |  |  |

| RINT*                                    | 1         | -      | Will put the arbitration controller in phase 0 and release all the bus lines except AR*. A selective reset is performed. The rising edge will release controller from phase 0. This reset is to be used for bus initialization. |  |  |  |

| RST*                                     | 1         | _      | Reset signal from the host. An internal reset is performed. All bus signals are released. The rising edge will put the controller in phase 0 (same as power-up reset).                                                          |  |  |  |

| HALT*                                    | 1         | 1      | Will halt the arbitration controller in phase 0. This signal is for use during live insertion.                                                                                                                                  |  |  |  |

| ENDT*                                    | 1         | _      | END OF TENURE: Indicates the true end of bus tenure of the current master. This line may be asserted only after all the parallel protocol lines are released. (Generated via external logic from BRQ* released.)                |  |  |  |

| Pin Definition (Continued) |           |         |                                                                                                                                                                                                                                                                                                                      |  |  |  |

|----------------------------|-----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin                        | # of Pins | Туре    | Description                                                                                                                                                                                                                                                                                                          |  |  |  |

| SIGNALS TO/F               | ROM THE H | OST (CI | PU Plus External Interface Logic)                                                                                                                                                                                                                                                                                    |  |  |  |

| DATA(7:0)                  | 8         | 1/0     | Data bus for the host to access the register bank of the controller.                                                                                                                                                                                                                                                 |  |  |  |

| ADD(3:0)                   | 4         | 1       | Address bits for the register bank of the controller.                                                                                                                                                                                                                                                                |  |  |  |

| CS*                        | 1         | - 1     | CHIP SELECT: The host can read or write to/from the controller.                                                                                                                                                                                                                                                      |  |  |  |

| Ř_W*                       | 1         | ŀ       | Read/write signal from the host.                                                                                                                                                                                                                                                                                     |  |  |  |

| DSACK*                     | 1         | 0       | Data acknowledge pin for host read/write.                                                                                                                                                                                                                                                                            |  |  |  |

| SEL                        | 1         | -       | SELECT: Determines how the controller latches in data. A "1" on the pin uses the rising edge of CS*. A "0" on the pin uses the falling edge of DSACK*.                                                                                                                                                               |  |  |  |

| MGRQ*                      | 1         | _       | MESSAGE REQUEST: Indicates to the controller to send an arbitration message.                                                                                                                                                                                                                                         |  |  |  |

| MGTX*                      | 1         | 0       | MESSAGE TRANSMIT: Indicates the successful transmission of an arbitration message.                                                                                                                                                                                                                                   |  |  |  |

| ERINT*                     | 1         | 0       | ERROR INTERRUPT: Indicates that an error occurred during the arbitration cycle.                                                                                                                                                                                                                                      |  |  |  |

| MGINT*                     | 1         | 0       | MESSAGE INTERRUPT: Indicates the reception of an arbitration message.                                                                                                                                                                                                                                                |  |  |  |

| PFINT*                     | 1         | 0       | POWER FAIL INTERRUPT: Indicates that a powerfail message was received.                                                                                                                                                                                                                                               |  |  |  |

| EXTERNAL LO                | GIC       |         |                                                                                                                                                                                                                                                                                                                      |  |  |  |

| IBA_CMPT*                  | 1         | 0       | Signal to indicate that the Parallel Protocol controller may assert its bit on the ADDRESS/DATA bus if it is participating in an Idle Bus Arbitration.                                                                                                                                                               |  |  |  |

| iBA_S*                     | 1         | 1       | This signal indicates that IBA was successful. If this module was a competitor in the IBA competition (IBRQ*), then this module is the winner and now the bus master. If this module was the master, but did not compete in the IBA competition and IBA was successful, then the M bit (Status register) is negated. |  |  |  |

| AS_CANCEL                  | 1         | 1       | Indicates the start of the disconnection phase of the current master or cancel the current arbitration cycle.                                                                                                                                                                                                        |  |  |  |

| LKD*                       | 1         | I       | LOCKED: Signal to indicate that resources have been locked in the current tenure and hence generate either a dummy cycle if current master or UNLK* otherwise. (Decoded from Futurebus + Command port output from Data Path Unit.)                                                                                   |  |  |  |

| UNLK*                      | 1         | 0       | UNLOCK: Transfer of tenure indication to the parallel protocol controller for unlocking its resources. Generated only if the LKD* signal is asserted. (To external logic.)                                                                                                                                           |  |  |  |

| FSTR*                      | 1         | 0       | FIFO STROBE: Signal generated to load an external FIFO for received arbitration messages.                                                                                                                                                                                                                            |  |  |  |

| CLK                        | 1         | ı       | Clock input to the internal PLL.                                                                                                                                                                                                                                                                                     |  |  |  |

| C1                         | 1         | 1       | External capacitor input for PLL—0.1 µF.                                                                                                                                                                                                                                                                             |  |  |  |

#### **Electrical Characteristics**

#### **Absolute Maximum Ratings**

The 883 specifications are written to reflect the Reliability Electrical Test Specifications (RETS) established by National Semiconductor for this product. For a copy of the RETS, please contact your local National Semiconductor sales office or distributor.

Supply Voltage

6.5V

Control Input Voltage

5.5V

Power Dissipation at 125°C

1.3W

Storage Temperature Range

-65°C to +150°C

Lead Temperature

260°C

## Recommended Operating Conditions

Supply Voltage, V<sub>DD</sub> 4.5 5.5 V

Operating Free Air Temperature -55 +125 °C

### Electrical Characteristics (Notes 2 and 3) $T_A = -55^{\circ}\text{C}$ to $+125^{\circ}\text{C}$ , $V_{CC} = 5V \pm 10\%$

| Symbol          | Parameter                  | Conditions                                                                       | Min | Max  | Units |

|-----------------|----------------------------|----------------------------------------------------------------------------------|-----|------|-------|

| V <sub>iH</sub> | Minimum Input High Voltage |                                                                                  | 2.8 |      | V     |

| V <sub>IL</sub> | Minimum Input Low Voltage  |                                                                                  |     | 0.75 | V     |

| V <sub>OH</sub> | Voltage Output High        | I <sub>OH</sub> , I <sub>OL</sub> for Several Drivers i.e., I <sub>OL</sub> 4 mA | 2.4 |      | ٧     |

| V <sub>OL</sub> | Voltage Output Low         | I <sub>OH</sub> , I <sub>OL</sub> for Several Drivers i.e., I <sub>OL</sub> 8 mA |     | 0.7  | ٧     |

| lj              | Input Leakage Current      | Input at V <sub>DD</sub> or V <sub>SS</sub>                                      | -3  | 3    | μА    |

| I <sub>DD</sub> | Supply Current             | Dynamic Supply Current                                                           |     | 100  | mA    |

| lcc             | Static Supply Current      | Input at Standby                                                                 |     | 30   | mA    |

Note 1: "Absolute maximum ratings" are those beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the device should be operated at these limits. The table of "Electrical Characteristics" provide conditions for actual device operation.

Note 2: All currents into device pins are positive; all currents out of device pin are negative. All voltages are referenced to device ground unless otherwise specified.

Note 3: All typicals are given for  $V_{DD}$  = 5V, and  $T_A$  = 25°C.

#### **AC Parameters**

#### Legend to AC Parameter Number Assignments

| Parameter<br>Number | Description                         |

|---------------------|-------------------------------------|

| t000~t099           | Phase 0                             |

| t100-t199           | Phase 1                             |

| t200-t299           | Phase 2                             |

| t300-t399           | Phase 3                             |

| t400-t499           | Phase 4                             |

| t500-t599           | Phase 5                             |

| tAXX                | Reset, Initialization               |

| tBXX                | Register Access Data Port           |

| tCXX                | Register Access CN Port - Input     |

| tDXX                | Clearing Interrupts                 |

| tEXX                | FIFO Strobe                         |

| tFXX                | WIN*GT* Valid                       |

| tGXX                | Message Signals                     |

| tHXX                | Busrequest, Busgrant, End of Tenure |

| IJXX                | Locked, Unlock Handshake Signals    |

## AC Parameters (Continued)

## AC Timing Parameters Unless otherwise stated: $T_A = -55^{\circ}C$ to $+125^{\circ}C$ , $V_{CC} = 5V \pm 10\%$

All transitions are specified after the input signals are stable and valid for evaluation. This table will describe the parameters as given in the following pages. All values are given in nanoseconds (ns), unless otherwise stated.

| Number           | Symbol                         | Parameter Description                                                          | Min       | Max                 |

|------------------|--------------------------------|--------------------------------------------------------------------------------|-----------|---------------------|

| t <sub>1</sub>   | t <sub>BQBG</sub>              | BRQ* Asserted to BGRNT* Asserted                                               |           | 36                  |

| t <sub>2</sub>   | t <sub>AQAC</sub>              | AQI Negated to AC0O, AC1O Negated                                              |           | 30                  |

| tg               | t <sub>APIO</sub>              | API Asserted to APO Asserted                                                   |           | 31                  |

| t <sub>4</sub>   | t <sub>RQAP</sub>              | MGRQ* or BRQ* Asserted to APO Asserted                                         |           | 38                  |

| t <sub>5</sub>   | tEDAP                          | (Dummy Cycle) ENDT* Asserted to APO Asserted                                   |           | 46                  |

| t <sub>6</sub>   | t <sub>BQAP</sub>              | (Consecutive Bus Requests) BRQ* Asserted to APO Asserted                       |           | 34                  |

| t <sub>7</sub>   | tHTAP                          | HALT* Negated to APO Asserted                                                  |           | 28                  |

| t <sub>100</sub> | t <sub>CNLEAR</sub> + (0 - 25) | CN_LE* Negated to ARO Negated. Determined by Programmable Value                |           | 4+(0-25)            |

| t <sub>101</sub> | tonle                          | CN_LE* Width                                                                   | 18        | 28                  |

| t <sub>102</sub> | tcns                           | CN Port Setup Time                                                             | 23        |                     |

| t <sub>103</sub> | t <sub>CNZ</sub>               | ARI Negated to TRI-STATE CN Port                                               | 16        |                     |

| t <sub>104</sub> | <sup>‡</sup> IBCAR             | (IBA Mode) IBA-CMPT* Asserted to ARO Negated. Determined by Programmable Value | 20+(0-25) |                     |

| t <sub>105</sub> | tcptar                         | CMPT* Asserted to ARO Negated. Determined by Programmable Value                | 20+(0-25) |                     |

| t <sub>106</sub> | <sup>‡</sup> ACOAR             | (Slow Mode) ACOO Asserted to ARO Negated, Determined by Programmable Value     | 18+(0-25) |                     |

| t <sub>107</sub> | <sup>†</sup> APCNLE            | APO Asserted to CN-LE* Asserted. CTRL3[0], "G0" Bit is Set                     |           | 32                  |

| t <sub>108</sub> | <sup>†</sup> APCPTA            | APO Asserted to CMPT* Asserted                                                 |           | 24                  |

| t <sub>109</sub> | <sup>t</sup> APIBC             | APO Asserted to IBA_CMPT* Asserted                                             |           | 22                  |

| t <sub>110</sub> | t <sub>APAC</sub>              | APO Asserted to AC0O Asserted (Slow Mode)                                      |           | 32                  |

| t <sub>200</sub> | <sup>t</sup> ARABRD            | ARI Negated to AB_RE* Asserted                                                 |           | 62                  |

| t <sub>202</sub> | t <sub>IBSBG</sub>             | (IBA Mode) IBA_S* Asserted to BGRNT* Asserted                                  |           | 40                  |

| t <sub>203</sub> | twinaq.                        | WIN*_GT* Asserted to AQO Asserted. After TA Expired.                           |           | 35                  |

| t <sub>204</sub> | t <sub>AQIO</sub>              | AQI Asserted to AQO Asserted                                                   |           | 24                  |

| t <sub>205</sub> | taraq                          | ARI Negated to AQO Asserted                                                    |           | 30 + T <sub>A</sub> |

| t <sub>207</sub> | tiBSAQ                         | (IBA Mode) IBA-S* Asserted to AQO Asserted                                     |           | 35                  |

| t <sub>300</sub> | t <sub>AC10AP</sub>            | AC10 Asserted to APO Negated                                                   |           | 29                  |

| t <sub>301</sub> | t <sub>ASNAP</sub>             | AS_Cancel* Negated to APO Negated                                              |           | 27                  |

| t <sub>310</sub> | t <sub>APABRD</sub>            | APO Negated to AB_RE* Negated                                                  |           | 10                  |

| t <sub>320</sub> | t <sub>AQAC1</sub>             | AQO Asserted to AC1O Asserted                                                  |           | 13                  |

| t <sub>321</sub> | t <sub>AC1IAPN</sub>           | AC1I Asserted to APO Negated                                                   | 5         | 21                  |

| t <sub>322</sub> | t <sub>ASAAP</sub>             | AS_Cancel* Asserted to APO Negated                                             | 5         | 21                  |

| t <sub>330</sub> | t <sub>AC1IAP</sub>            | AC1I Asserted to APO Negated                                                   |           | 24                  |

| t <sub>340</sub> | t <sub>RQAC</sub>              | MGRQ* or BRQ* Negated to AC0O, AC1O Asserted                                   |           | 40                  |

| t <sub>341</sub> | t <sub>AQAC0</sub>             | AQO Asserted to ACOO Negated                                                   |           | 4                   |

| t <sub>342</sub> | t <sub>AQER</sub>              | AQO Asserted to ERIT* Asserted                                                 |           | 23                  |

| t <sub>400</sub> | t <sub>APCPTN</sub>            | API Negated to CMPT* Negated                                                   |           | 34                  |

## AC Parameters (Continued)

AC Timing Parameters Unless otherwise stated:  $T_A = -55^{\circ}\text{C}$  to  $\pm 125^{\circ}\text{C}$ ,  $V_{CC} = 5\text{V} \pm 10\%$  (Continued) All transitions are specified after the input signals are stable and valid for evaluation. This table will describe the parameters as given in the following pages. All values are given in nanoseconds (ns), unless otherwise stated.

| Number           | Symbol               | Parameter Description                                         | Min | Max |

|------------------|----------------------|---------------------------------------------------------------|-----|-----|

| t <sub>401</sub> | t <sub>AC1IAR</sub>  | AC1I Asserted to ARO Asserted                                 |     | 26  |

| t <sub>403</sub> | tCANAC1              | AS_Cancel* Asserted to AC1O Asserted                          | 7   | 24  |

| t <sub>406</sub> | t <sub>ARIO</sub>    | ARI Asserted to ARO Asserted                                  |     | 25  |

| t <sub>407</sub> | tedar                | ENDT* Asserted to ARO Asserted                                |     | 32  |

| t <sub>500</sub> | t <sub>ARBG</sub>    | ARO Asserted to BGRNT* Asserted                               |     | 12  |

| t <sub>501</sub> | toaq                 | BGRNT*, MGTX*, UNLK* or any Interrupt Asserted to AQO Negated | 3   |     |

| t <sub>502</sub> | t <sub>ARFTR</sub>   | ARO Asserted to FSTR* Negated                                 |     | 10  |

| t <sub>503</sub> | t <sub>ARIBC</sub>   | ARO Asserted to IBACMPT* Negated                              |     | 10  |

| t <sub>504</sub> | <sup>t</sup> ARABSA  | ARO Asserted to MGTX*, UNLK* or any Interrupt Asserted        |     | 10  |

| t <sub>A1</sub>  | <sup>t</sup> RSTPW   | RST* Pulse Width                                              | 50  |     |

| t <sub>A2</sub>  | t <sub>RSTRE</sub>   | Output Reset Time                                             |     | 54  |

| t <sub>A3</sub>  | trstar               | RST* Negated to ARO Asserted                                  |     | 25  |

| t <sub>A4</sub>  | <sup>t</sup> RINTPW  | RINT* Pulse Width                                             | 50  |     |

| t <sub>A5</sub>  | tRINTRE              | Output Initialization Reset Time                              |     | 45  |

| t <sub>B1</sub>  | t <sub>CSPW</sub>    | CS* Pulse Width                                               | 35  |     |

| t <sub>B2</sub>  | <sup>t</sup> CSPWN   | CS* Recovery Time                                             | 15  |     |

| t <sub>B3</sub>  | t <sub>CSDKA</sub>   | CS* Asserted to DSACK* Asserted                               |     | 23  |

| t <sub>B4</sub>  | tADDS                | ADD (3:0) Setup Time                                          | 5   |     |

| t <sub>B5</sub>  | t <sub>ADDH</sub>    | ADD (3:0) Hold Time                                           | 9   |     |

| t <sub>B6</sub>  | t <sub>CSDKN</sub>   | CS* Negated to DSACK* Negated                                 | 5   |     |

| t <sub>B7</sub>  | t <sub>RWS</sub>     | RW* Setup Time                                                | 0   |     |

| t <sub>B8</sub>  | tSELS                | SEL Setup Time                                                | 0   |     |

| t <sub>B10</sub> | <sup>†</sup> DATASDK | Data (7:0) Setup Time with Respect to DSACK*                  | 28  |     |

| t <sub>B11</sub> | <sup>t</sup> DATAHDK | Data (7:0) Hold Time with Respect to DSACK*                   | 0   |     |

| t <sub>B12</sub> | t <sub>SELH</sub>    | SEL Hold Time                                                 | 5   |     |

| t <sub>B24</sub> | <sup>‡</sup> DATASCS | Data (7:0) Setup Time with Respect to CS* Negated             | 15  |     |

| t <sub>B25</sub> | <sup>t</sup> DATAHCS | Data (7:0) Hold Time with Respect to CS* Negated              | 5   |     |

| t <sub>B28</sub> | t <sub>DATAV</sub>   | Data (7:0) Valid Time before DSACK*                           |     |     |

| t <sub>B29</sub> | <sup>t</sup> DATAA   | Data (7:0) Access Time with Respect to CS* Asserted           |     | 33  |

| t <sub>C2</sub>  | t <sub>ABROCNZ</sub> | AB_RE* Negated to CN (7:0) TRI-STATE                          | 0   |     |

| t <sub>D1</sub>  | <sup>†</sup> CSXINTN | CS* Asserted to any Interrupt Negated                         |     | 43  |

## AC Parameters (Continued)

AC Timing Parameters Unless otherwise stated:  $T_A = -55^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$  (Continued) All transitions are specified after the input signals are stable and valid for evaluation. This table will describe the parameters as given in the following pages. All values are given in nanoseconds (ns), unless otherwise stated.

| Number          | Symbol              | Parameter Description                   | Min | Max |

|-----------------|---------------------|-----------------------------------------|-----|-----|

| t <sub>F1</sub> | twinall1            | ALL1* Asserted with Respect to WIN*_GT* |     | 5   |

| t <sub>F2</sub> | WINPER              | PER* Asserted with Respect to WIN*GT*   |     | 5   |

| t <sub>G1</sub> | tMGXN               | MGRQ* Negated to MGTX* Negated          |     | 23  |

| <b>t</b> H2     | t <sub>EDBGN</sub>  | ENDT* Asserted to BGRNT* Negated        |     | 25  |

| ŧ <sub>l1</sub> | <sup>t</sup> LKULKN | LKD* Negated to UNLK* Negated           |     | 25  |

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel 1(800) 272-9959 Fax: 1(800) 737-7018

National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Fac: (+49) 0-180-530 85 86

Emait cnipuge@teym2 nsc com

Deutsch Tet (+49) 0-180-530 85 85

English Tet (+49) 0-180-532 78 32

Français Tet (+49) 0-180-534 16 80

Tet (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Centon Rd. Tsimstratsu, Kowloon Hong Kong Tel (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd. Tel 81-043-299-2309 Fax: 81-043-299-2408

National does not assume any responsibility for use of any directing described, no direct Econess are implied and National reserves the right at any time without notice to change said circuitry and specifications.