#### **FEATURES**

-3 dB bandwidth of 2.2 GHz for A<sub>v</sub> = 12 dB Single resistor programmable gain: 0 dB  $\leq$  A<sub>V</sub>  $\leq$  26 dB **Differential interface** Low noise input stage 2.7 nV/ $\sqrt{Hz}$  at A<sub>V</sub> = 10 dB Low harmonic distortion -79 dBc second at 70 MHz -81 dBc third at 70 MHz OIP3 of 31 dBm at 70 MHz Single-supply operation: 3 V to 5.5 V Low power dissipation: 28 mA at 5 V Adjustable output common-mode voltage Fast settling and overdrive recovery Slew rate of 13,000 V/µs **Power-down capability**

### **APPLICATIONS**

**Differential ADC drivers** Single-ended-to-differential conversion **IF** sampling receivers **RF/IF gain blocks** SAW filter interfacing

# Low Distortion **Differential RF/IF Amplifier**

# AD8351

3145-0

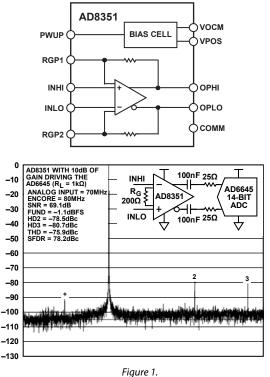

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The AD8351 is a low cost differential amplifier useful in RF and IF applications up to 2.2 GHz. The voltage gain can be set from unity to 26 dB using a single external gain resistor. The AD8351 provides a nominal 150  $\Omega$  differential output impedance. The excellent distortion performance and low noise characteristics of this device allow for a wide range of applications.

The AD8351 is designed to satisfy the demanding performance requirements of communications transceiver applications. The device can be used as a general-purpose gain block, an ADC driver, and a high speed data interface driver, among other functions. The AD8351 can also be used as a single-ended-todifferential amplifier with similar distortion products as in the

differential configuration. The exceptionally good distortion performance makes the AD8351 an ideal solution for 12-bit and 14-bit IF sampling receiver designs.

Fabricated in Analog Devices, Inc., high speed XFCB process, the AD8351 has high bandwidth that provides high frequency performance and low distortion. The quiescent current of the AD8351 is 28 mA typically. The AD8351 amplifier comes in a compact 10-lead MSOP package or in a 16-lead LFCSP package, and operates over the temperature range of -40°C to +85°C.

Rev. D

**Document Feedback**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

# TABLE OF CONTENTS

| Features                                     |

|----------------------------------------------|

| Applications1                                |

| Functional Block Diagram1                    |

| General Description                          |

| Revision History                             |

| Specifications                               |

| Absolute Maximum Ratings5                    |

| ESD Caution                                  |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

| Theory of Operation                          |

| Basic Concepts 12                            |

### **REVISION HISTORY**

| 1/15—Rev. C to Rev. D                          |    |

|------------------------------------------------|----|

| Changes to Noise Distortion Parameter, Table 1 |    |

| Changes to Ordering Guide                      | 19 |

### 3/14-Rev. B to Rev. C

| Updated Format                                    | Universal  |

|---------------------------------------------------|------------|

| Added 16-Lead LFCSP Package                       | Throughout |

| Changes to Features                               | 1          |

| Changes to Table 3 and Added Figure 3; Renumbered | d          |

| Sequentially                                      | 6          |

| Updated Outline Dimensions; Added Figure 52       |            |

| Moved, Changes to Ordering Guide                  | 19         |

|                                                   |            |

#### 2/04—Rev. A to Rev. B

| Changes to Ordering Guide | . 4 |

|---------------------------|-----|

| Changes to TPC 4          | . 5 |

### 3/03—Rev. 0 to Rev. A

| Changes to Ordering Guide | 4  |

|---------------------------|----|

| Change to Table 3         | 15 |

#### 3/03—Revision 0: Initial Version

| Gain Adjustment                        | 12 |

|----------------------------------------|----|

| Common-Mode Adjustment                 | 12 |

| Input and Output Matching              | 12 |

| Single-Ended-to-Differential Operation | 13 |

| ADC Driving                            | 13 |

| Analog Multiplexing                    | 14 |

| I/O Capacitive Loading                 | 14 |

| Transmission Line Effects              | 15 |

| Characterization Setup                 | 16 |

| Evaluation Board                       | 17 |

| Outline Dimensions                     | 19 |

| Ordering Guide                         | 19 |

# **SPECIFICATIONS**

$V_S = 5 V$ ,  $R_L = 150 \Omega$ ,  $R_G = 110 \Omega$  ( $A_V = 10 dB$ ), f = 70 MHz,  $T = 25^{\circ}C$ , parameters specified differentially, unless otherwise noted.

### Table 1.

| Parameter                                     | Test Conditions/Comments                                                               | Min | Тур        | Max | Unit   |

|-----------------------------------------------|----------------------------------------------------------------------------------------|-----|------------|-----|--------|

| DYNAMIC PERFORMANCE                           |                                                                                        |     |            |     |        |

| –3 dB Bandwidth                               | $GAIN = 6 dB, V_{OUT} \le 1.0 V p-p$                                                   |     | 3,000      |     | MHz    |

|                                               | $GAIN = 12 \text{ dB}, V_{OUT} \le 1.0 \text{ V p-p}$                                  |     | 2,200      |     | MHz    |

|                                               | $GAIN = 18 \text{ dB}, V_{OUT} \le 1.0 \text{ V p-p}$                                  |     | 600        |     | MHz    |

| Bandwidth for 0.1 dB Flatness                 | $0 \text{ dB} \le \text{GAIN} \le 20 \text{ dB}, V_{\text{OUT}} \le 1.0 \text{ V p-p}$ |     | 200        |     | MHz    |

| Bandwidth for 0.2 dB Flatness                 | $0 \text{ dB} \le \text{GAIN} \le 20 \text{ dB}, V_{\text{OUT}} \le 1.0 \text{ V p-p}$ |     | 400        |     | MHz    |

| Gain Accuracy                                 | Using 1% resistor for $R_G$ , 0 dB $\leq A_V \leq$ 20 dB                               |     | ±1         |     | dB     |

| Gain Supply Sensitivity                       | $V_{s} \pm 5\%$                                                                        |     | 0.08       |     | dB/V   |

| Gain Temperature Sensitivity                  | -40°C to +85°C                                                                         |     | 3.9        |     | mdB/°C |

| Slew Rate                                     | $R_L = 1 \ k\Omega$ , $V_{OUT} = 2 \ V \ step$                                         |     | 13,000     |     | V/µs   |

|                                               | $R_L = 150 \Omega$ , $V_S = 2 V$ step                                                  |     | 7,500      |     | V/µs   |

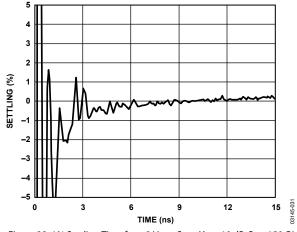

| Settling Time                                 | 1 V step to 1%                                                                         |     | <3         |     | ns     |

| Overdrive Recovery Time                       | $V_{IN} = 4 V \text{ to } 0 V \text{ step}, V_{OUT} \le \pm 10 \text{ mV}$             |     | <2         |     | ns     |

| Reverse Isolation (S12)                       |                                                                                        |     | -67        |     | dB     |

| INPUT/OUTPUT CHARACTERISTICS                  |                                                                                        |     |            |     |        |

| Input Common-Mode Voltage Adjustment Range    |                                                                                        |     | 1.2 to 3.8 |     | v      |

| Max Output Voltage Swing                      | 1 dB compressed                                                                        |     | 4.75       |     | V p-р  |

| Output Common-Mode Offset                     |                                                                                        |     | 40         |     | mV     |

| Output Common-Mode Drift                      | –40°C to +85°C                                                                         |     | 0.24       |     | mV/°C  |

| Output Differential Offset Voltage            |                                                                                        |     | 20         |     | mV     |

| Output Differential Offset Drift              | -40°C to +85°C                                                                         |     | 0.13       |     | mV/°C  |

| Input Bias Current                            |                                                                                        |     | ±15        |     | μA     |

| Input Resistance <sup>1</sup>                 |                                                                                        |     | 5          |     | kΩ     |

| Input Capacitance <sup>1</sup>                |                                                                                        |     | 0.8        |     | рF     |

| CMRR                                          |                                                                                        |     | 43         |     | dB     |

| Output Resistance <sup>1</sup>                |                                                                                        |     | 150        |     | Ω      |

| Output Capacitance <sup>1</sup>               |                                                                                        |     | 0.8        |     | pF     |

| POWER INTERFACE                               |                                                                                        |     |            |     | 1      |

| Supply Voltage                                |                                                                                        | 3   |            | 5.5 | v      |

| PWUP Threshold                                |                                                                                        | -   | 1.3        |     | V      |

| PWUP Input Bias Current                       | PWUP at 5 V                                                                            |     | 100        |     | μA     |

|                                               | PWUP at 0 V                                                                            |     | 25         |     | μA     |

| Quiescent Current                             |                                                                                        |     | 28         | 32  | mA     |

| NOISE/DISTORTION                              |                                                                                        |     |            |     |        |

| 10 MHz                                        |                                                                                        |     |            |     |        |

| Second/Third Harmonic Distortion <sup>2</sup> | $R_L = 1 k\Omega$ , $V_{OUT} = 2 V p-p$                                                |     | -95/-93    |     | dBc    |

|                                               | $R_L = 150 \Omega, V_{OUT} = 2 V p-p$                                                  |     | -80/-69    |     | dBc    |

| Third-Order IMD                               | $R_L = 1 k\Omega$ , f1 = 9.5 MHz, f2 = 10.5 MHz,                                       |     | -90        |     | dBc    |

|                                               | $V_{\text{OUT}} = 2 \text{ V p-p composite}$                                           |     | 50         |     | abe    |

|                                               | $R_L$ = 150 Ω, f1 = 9.5 MHz, f2 = 10.5 MHz,<br>V <sub>OUT</sub> = 2 V p-p composite    |     | -70        |     | dBc    |

| Output Third-Order Intercept                  | f1 = 9.5 MHz, f2 = 10.5 MHz                                                            |     | 33         |     | dBm    |

| Noise Spectral Density (RTI)                  |                                                                                        |     | 2.65       |     | nV/√Hz |

| 1 dB Compression Point                        |                                                                                        |     | 13.5       |     | dBm    |

| Parameter                                     | Test Conditions/Comments                                                                                                                                       | Min | Тур     | Max | Unit   |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|--------|

| 70 MHz                                        |                                                                                                                                                                |     |         |     |        |

| Second/Third Harmonic Distortion <sup>2</sup> | $R_L = 1 \ k\Omega$ , $V_{OUT} = 2 \ V \ p-p$                                                                                                                  |     | -79/-81 |     | dBc    |

|                                               | $R_L = 150 \Omega$ , $V_{OUT} = 2 V p-p$                                                                                                                       |     | -65/-66 |     | dBc    |

| Third-Order IMD                               | $\label{eq:RL} \begin{array}{l} R_{L} = 1 \; k \Omega,  f1 = 69.5 \; MHz,  f2 = 70.5 \; MHz, \\ V_{OUT} = 2 \; V \; p\text{-}p \; composite \end{array}$       |     | -85     |     | dBc    |

|                                               | $R_L = 150 \Omega$ , f1 = 69.5 MHz, f2 = 70.5 MHz, $V_{OUT} = 2 V p$ -p composite                                                                              |     | -69     |     | dBc    |

| Output Third-Order Intercept                  | f1 = 69.5 MHz, f2 = 70.5 MHz                                                                                                                                   |     | 31      |     | dBm    |

| Noise Spectral Density (RTI)                  |                                                                                                                                                                |     | 2.70    |     | nV/√Hz |

| 1 dB Compression Point                        |                                                                                                                                                                |     | 13.3    |     | dBm    |

| 140 MHz                                       |                                                                                                                                                                |     |         |     |        |

| Second/Third Harmonic Distortion <sup>2</sup> | $R_L = 1 \text{ k}\Omega$ , $V_{OUT} = 2 \text{ V } p$ -p                                                                                                      |     | -69/-69 |     | dBc    |

|                                               | $R_L = 150 \Omega$ , $V_{OUT} = 2 V p-p$                                                                                                                       |     | -54/-53 |     | dBc    |

| Third-Order IMD                               | $\label{eq:RL} \begin{array}{l} R_L = 1 \; k\Omega,  f1 = 139.5 \; MHz,  f2 = 140.5 \; MHz, \\ V_{\text{OUT}} = 2 \; V \; p\text{-}p \; composite \end{array}$ |     | -79     |     | dBc    |

|                                               | $R_L = 150 \Omega$ , f1 = 139.5 MHz, f2 = 140.5 MHz, $V_{OUT} = 2 V p$ -p composite                                                                            |     | -67     |     | dBc    |

| Output Third-Order Intercept                  | f1 = 139.5 MHz, f2 = 140.5 MHz                                                                                                                                 |     | 29      |     | dBm    |

| Noise Spectral Density (RTI)                  |                                                                                                                                                                |     | 2.75    |     | nV/√Hz |

| 1 dB Compression Point                        |                                                                                                                                                                |     | 13      |     | dBm    |

| 240 MHz                                       |                                                                                                                                                                |     |         |     |        |

| Second/Third Harmonic Distortion <sup>2</sup> | $R_L = 1 \ k\Omega$ , $V_{OUT} = 2 \ V \ p-p$                                                                                                                  |     | -60/-66 |     | dBc    |

|                                               | $R_L = 150 \Omega$ , $V_{OUT} = 2 V p-p$                                                                                                                       |     | -46/-50 |     | dBc    |

| Third-Order IMD                               | $R_L = 1 \ k\Omega$ , f1 = 239.5 MHz, f2 = 240.5 MHz, $V_{OUT} = 2 V \ p$ -p composite                                                                         |     | -76     |     | dBc    |

|                                               | $R_L = 150 \Omega$ , f1 = 239.5 MHz, f2 = 240.5 MHz, $V_{OUT} = 2 V p$ -p composite                                                                            |     | -62     |     | dBc    |

| Output Third-Order Intercept                  | f1 = 239.5 MHz, f2 = 240.5 MHz                                                                                                                                 |     | 27      |     | dBm    |

| Noise Spectral Density (RTI)                  |                                                                                                                                                                |     | 2.90    |     | nV/√Hz |

| 1 dB Compression Point                        |                                                                                                                                                                |     | 13      |     | dBm    |

<sup>1</sup> Values are specified differentially.

<sup>2</sup> See the Single-Ended-to-Differential Operation section for single-ended-to-differential performance.

# **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| 14010 2.                                  |                 |

|-------------------------------------------|-----------------|

| Parameter                                 | Rating          |

| Supply Voltage VPOS                       | 6 V             |

| PWUP Voltage                              | VPOS            |

| Internal Power Dissipation                | 320 mW          |

| θ <sub>JA</sub>                           | 125°C/W         |

| Maximum Junction Temperature              | 125°C           |

| Operating Temperature Range               | -40°C to +85°C  |

| Storage Temperature Range                 | -65°C to +150°C |

| Lead Temperature Range (Soldering 60 sec) | 300°C           |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

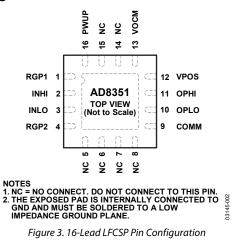

# **PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS**

#### Figure 2. 10-Lead MSOP Pin Configuration

#### **Table 3. Pin Function Descriptions**

| Pin No.      |                    |          |                                                                                                                                                    |

|--------------|--------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Lead MSOP | 16-Lead LFCSP      | Mnemonic | Description                                                                                                                                        |

| 1            | 16                 | PWUP     | Apply a positive voltage (1.3 V $\leq$ V <sub>PWUP</sub> $\leq$ VPOS) to activate device.                                                          |

| 2            | 1                  | RGP1     | Gain Resistor Input 1.                                                                                                                             |

| 3            | 2                  | INHI     | Balanced Differential Input. Biased to midsupply, typically ac-coupled.                                                                            |

| 4            | 3                  | INLO     | Balanced Differential Input. Biased to midsupply, typically ac-coupled.                                                                            |

| 5            | 4                  | RGP2     | Gain Resistor Input 2.                                                                                                                             |

| 6            | 9                  | СОММ     | Device Common. Connect to low impedance ground.                                                                                                    |

| 7            | 10                 | OPLO     | Balanced Differential Output. Biased to VOCM, typically ac-coupled.                                                                                |

| 8            | 11                 | OPHI     | Balanced Differential Output. Biased to VOCM, typically ac-coupled.                                                                                |

| 9            | 12                 | VPOS     | Positive Supply Voltage. 3 V to 5.5 V.                                                                                                             |

| 10           | 13                 | VOCM     | Voltage applied to this pin sets the common-mode voltage at both the input and output. Typically decoupled to ground with a 0.1 $\mu$ F capacitor. |

|              | 5, 6, 7, 8, 14, 15 | NC       | No connect. Do not connect to this pin.                                                                                                            |

|              |                    | EPAD     | Exposed Pad. The exposed pad is internally connected to GND and must be soldered to a low impedance ground plane.                                  |

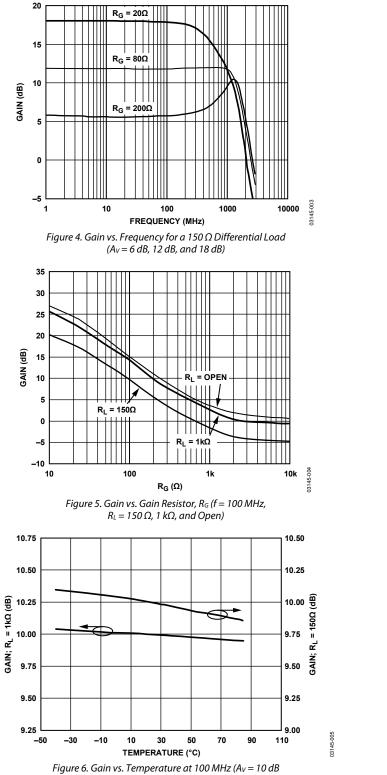

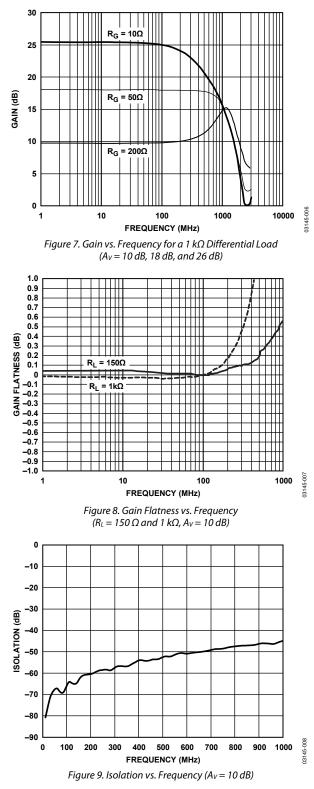

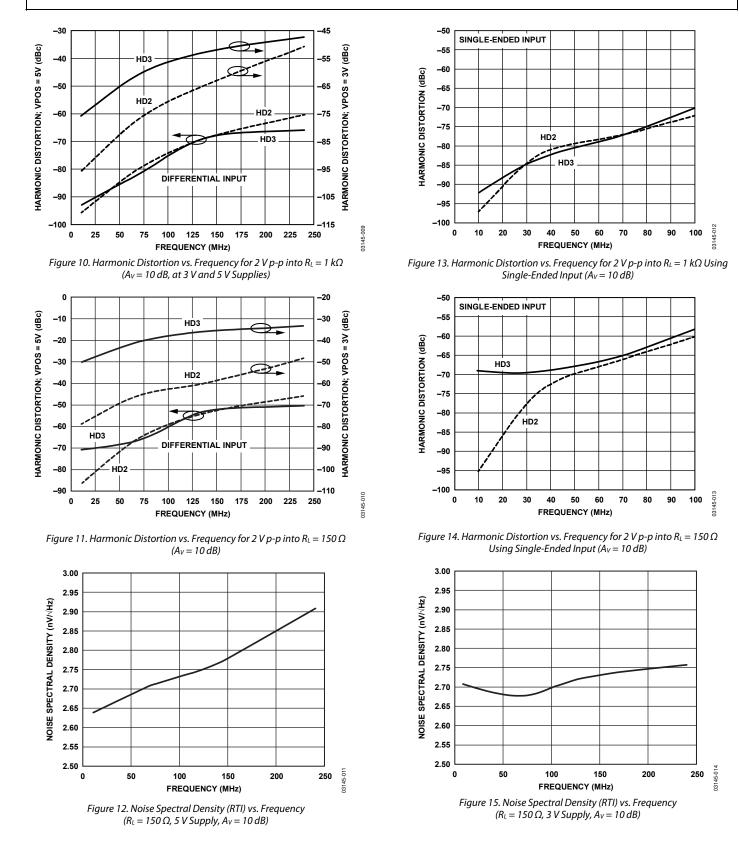

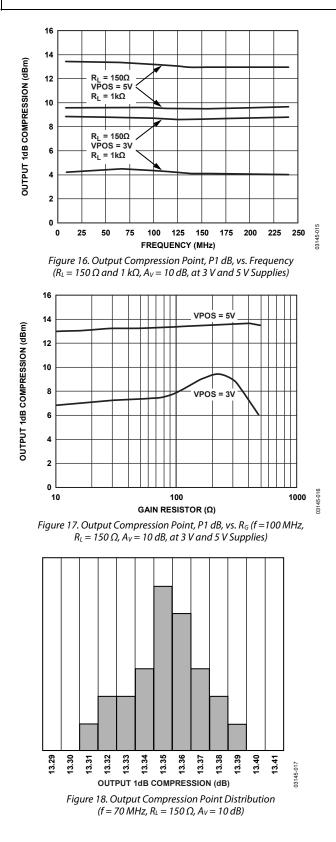

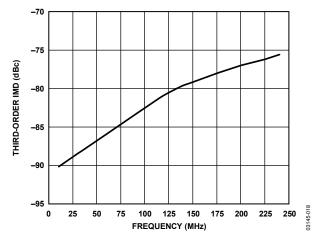

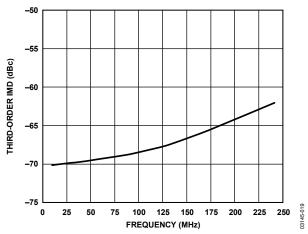

# **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_s = 5 V$ ,  $T = 25^{\circ}C$ , unless otherwise noted.

Figure 19. Third-Order Intermodulation Distortion vs. Frequency for a 2 V p-p Composite Signal into  $R_L = 1 k\Omega (A_V = 10 dB, at 5 V Supplies)$

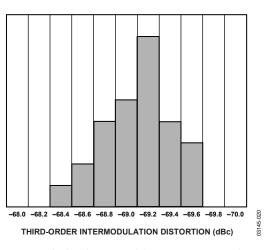

Figure 21. Third-Order Intermodulation Distortion Distribution (f = 70 MHz,  $R_L = 150 \Omega$ ,  $A_V = 10 \text{ dB}$ )

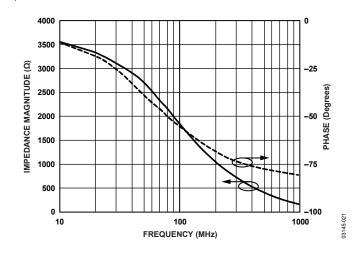

Figure 22. Input Impedance vs. Frequency

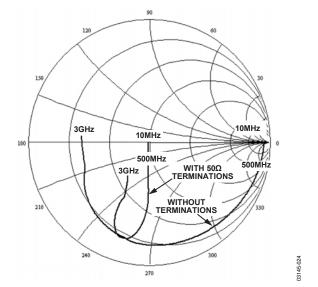

Figure 25. Input Reflection Coefficient vs. Frequency ( $R_s = R_L = 100 \Omega$  With and Without 50  $\Omega$  Terminations)

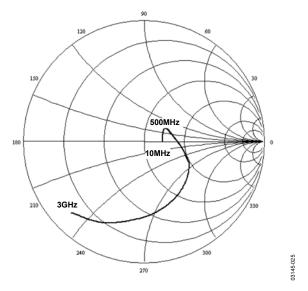

Figure 26. Output Reflection Coefficient vs. Frequency ( $R_s = R_L = 100 \Omega$ )

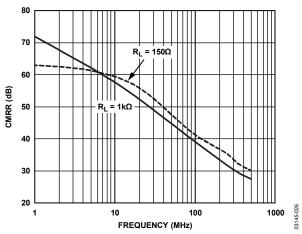

Figure 27. Common-Mode Rejection Ratio, CMRR ( $R_s = 100 \Omega$ )

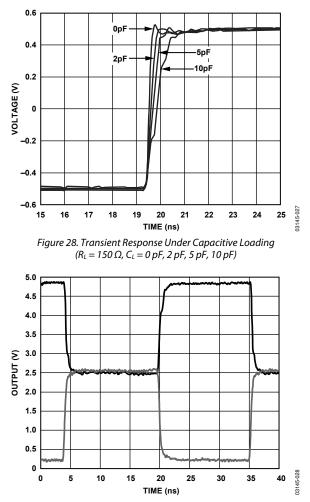

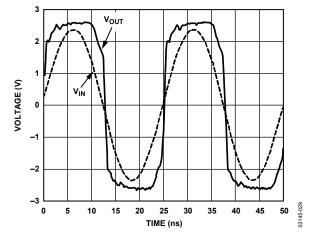

*Figure 29. 2× Output Overdrive Recovery (R<sub>L</sub> = 150 \Omega, A<sub>V</sub> = 10 dB)*

Figure 30. Overdrive Recovery Using Sinusoidal Input Waveform  $R_L = 150 \Omega$ ( $A_V = 10 \text{ dB}$ , at 5 V Supplies)

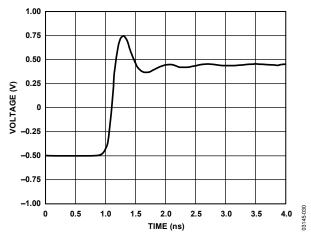

Figure 31. Large Signal Transient Response for a 1 V p-p Output Step  $(A_V = 10 \text{ dB}, R_{IP} = 25 \Omega)$

Figure 32. 1% Settling Time for a 2 V p-p Step ( $A_V = 10 \text{ dB}$ ,  $R_L = 150 \Omega$ )

### AD8351

### THEORY OF OPERATION **BASIC CONCEPTS**

Differential signaling is used in high performance signal chains, where distortion performance, signal-to-noise ratio, and low power consumption is critical. Differential circuits inherently provide improved common-mode rejection and harmonic distortion performance as well as better immunity to interference and ground noise.

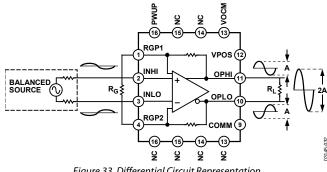

Figure 33. Differential Circuit Representation

Figure 33 illustrates the expected input and output waveforms for a typical application. Usually the applied input waveform is a balanced differential drive, where the signal applied to the INHI and INLO pins are equal in amplitude and differ in phase by 180°. In some applications, baluns may be used to transform a singleended drive signal to a differential signal. The AD8351 may also be used to transform a single-ended signal to a differential signal.

### **GAIN ADJUSTMENT**

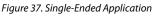

The differential gain of the AD8351 is set using a single external resistor, R<sub>G</sub>, which is connected between the RGP1 pin and the RGP2 pin. The gain can be set to any value between 0 dB and 26 dB using the resistor values specified in Figure 5, with common gain values provided in Table 4. The board traces used to connect the external gain resistor must be balanced and as short as possible to help prevent noise pickup and to ensure balanced gain and stability. The low frequency voltage gain of the AD8351 can be modeled as

$$A_{V} = \frac{R_{L} \times R_{G}(5.6) + 9.2 \times R_{F} \times R_{L}}{R_{G} \times R_{L} \times 4.6 + 19.5 \times R_{G} + \left(R_{L} + R_{F}\right) \times \left(39 + R_{G}\right)} = \left|\frac{V_{OUT}}{V_{IN}}\right|$$

where:

$R_F$  is 350  $\Omega$  (internal).  $R_L$  is the single-ended load resistance.

$R_G$  is the gain setting resistor.

| Table 4. Gain Resistor Selection for Common Gain Values |

|---------------------------------------------------------|

| (Load Resistance Is Specified as Single-Ended)          |

| (Loud Resistance is operation as single Lindea) |                         |                          |  |

|-------------------------------------------------|-------------------------|--------------------------|--|

| Gain, Av                                        | $R_G (R_L = 75 \Omega)$ | $R_G (R_L = 500 \Omega)$ |  |

| 0 dB                                            | 680 Ω                   | 2 kΩ                     |  |

| 6 dB                                            | 200 Ω                   | 470 Ω                    |  |

| 10 dB                                           | 100 Ω                   | 200 Ω                    |  |

| 20 dB                                           | 22 Ω                    | 43 Ω                     |  |

### **COMMON-MODE ADJUSTMENT**

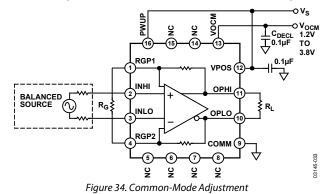

The output common-mode voltage level is the dc offset voltage present at each of the differential outputs. The ac signals are of equal amplitude with a 180° phase difference but are centered at the same common-mode voltage level. The common-mode output voltage level can be adjusted from 1.2 V to 3.8 V by driving the desired voltage level into the VOCM pin, as illustrated in Figure 34.

### **INPUT AND OUTPUT MATCHING**

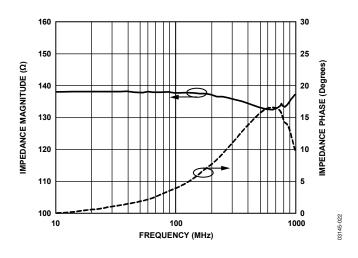

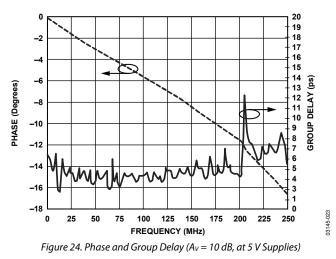

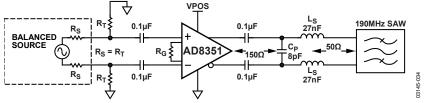

The AD8351 provides a moderately high differential input impedance of 5 k $\Omega$ . In practical applications, the input of the AD8351 is terminated to a lower impedance to provide an impedance match to the driving source, as shown in Figure 35. Place the terminating resistor, R<sub>T</sub>, as close as possible to the input pins to minimize reflections due to impedance mismatch. The 150  $\Omega$ output impedance may need to be transformed to provide the desired output match to a given load. Matching components can be calculated using a Smith chart or by using a resonant approach to determine the matching network that results in a complex conjugate match. The input and output impedances and reflection coefficients are provided in Figure 22, Figure 23, Figure 24, and Figure 25. For additional information on reactive matching to differential sources and loads, refer to the Applications section of the AD8350 data sheet.

Figure 35. Example of Differential SAW Filter Interface ( $f_c = 190 \text{ MHz}$ )

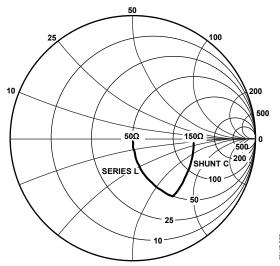

Figure 35 illustrates a surface acoustic wave (SAW) filter interface. Many SAW filters are inherently differential, allowing for a low loss output match. In this example, the SAW filter requires a 50  $\Omega$ source impedance to provide the desired center frequency and Q. The series L shunt C output network provides a 150  $\Omega$  to 50  $\Omega$  impedance transformation at the desired frequency of operation. The impedance transformation is illustrated on a Smith chart in Figure 36.

It is possible to drive a single-ended SAW filter by connecting the unused output to ground using the appropriate terminating resistance. The overall gain of the system is reduced by 6 dB because only half of the signal is available to the input of the SAW filter.

Figure 36. Smith Chart Representation of SAW Filter Output Matching Network

### SINGLE-ENDED-TO-DIFFERENTIAL OPERATION

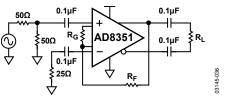

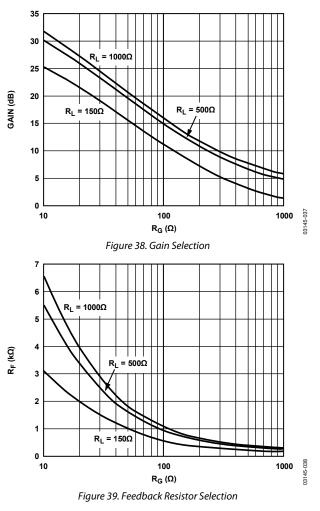

The AD8351 can easily be configured as a single-ended-todifferential gain block, as illustrated in Figure 37. The input signal is ac-coupled and applied to the INHI input. The unused input is ac-coupled to ground. Select the values of C1 through C4 such that their reactances are negligible at the desired frequency of operation. To balance the outputs, an external feedback resistor,  $R_F$ , is required. To select the gain resistor and the feedback resistor, refer to Figure 38 and Figure 39. From Figure 38, select an  $R_G$  for the required dB gain at a given load. Next, select from Figure 39 an  $R_F$  resistor for the selected  $R_G$  and load.

Even though the differential balance is not perfect under these conditions, the distortion performance is still impressive. Figure 13 and Figure 14 show the second and third harmonic distortion performance when driving the input of the AD8351 using a single-ended 50  $\Omega$  source.

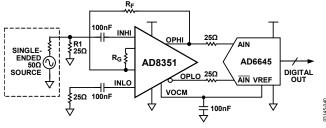

### ADC DRIVING

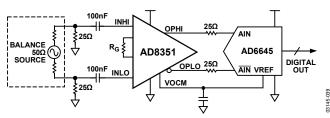

The circuit in Figure 40 represents a simplified front end of the AD8351 driving the AD6645, which is a 14-bit, 105 MSPS ADC. For optimum performance, the AD6645 and the AD8351 are driven differentially. The resistors R1 and R2 present a 50  $\Omega$ differential input impedance to the source with R3 and R4 providing isolation from the analog-to-digital input. The gain setting resistor for the AD8351 is  $R_G$ . The AD6645 presents a 1 k $\Omega$  differential load to the AD8351 and requires a 2.2 V p-p differential signal between AIN and AIN for a full-scale output. This AD8351 circuit then provides the gain, isolation, and source matching for the AD6645. The AD8351 also provides a balanced input, not provided by the balun, to the AD6645, which is essential for second-order cancellation. The signal generator is bipolar, centered around ground. Connecting the VOCM pin (Pin 10 on the MSOP and Pin 13 on the LFCSP) of the AD8351 to the VREF pin of the AD6645 sets the common-mode output voltage of the AD8351 at 2.4 V. This voltage is bypassed with a 0.1 µF capacitor. Increasing the gain of the AD8351 increases the system noise and thus decrease the SNR but does not significantly affect the distortion. The circuit in Figure 40 can provide SFDR performance of better than -90 dBc with a 10 MHz input and -80 dBc with a 70 MHz input at a gain of 10 dB.

Figure 40. ADC Driving Application Using Differential Input

The circuit of Figure 41 represents a single-ended input to differential output configuration of the AD8351 driving the AD6645. In this case, R1 provides the input impedance. R<sub>G</sub> is the gain setting resistor. The resistor R<sub>F</sub> is required to balance the output voltages required for second-order cancellation by the AD6645 and can be selected using a chart (see the Single-Ended-to-Differential Operation section). The circuit depicted in Figure 41 can provide SFDR performance of better than -90 dBc with a 10 MHz input and -77 dBc with a 70 MHz input.

Figure 41. ADC Driving Application Using Single-Ended Input

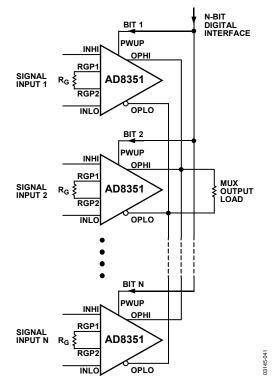

### ANALOG MULTIPLEXING

The AD8351 can be used as an analog multiplexer in applications where it is desirable to select multiple high speed signals. The isolation of each device when in a disabled state (PWUP pin pulled low) is about 60 dBc for the maximum input level of 0.5 V p-p out to 100 MHz. The low output noise spectral density allows for a simple implementation as depicted in Figure 42. The PWUP interface can be easily driven using most standard logic interfaces. By using an N-bit digital interface, up to N devices can be controlled. Output loading effects and noise need to be considered when using a large number of input signal paths. Each disabled AD8351 presents approximately a 700  $\Omega$  load in parallel with the 150  $\Omega$  output source impedance of the enabled device. As the load increases due to the addition of N devices, the distortion performance will degrade due to the heavier loading. Distortion better than -70 dBc can be achieved with four devices muxed into a 1 k $\Omega$  load for signal frequencies up to 70 MHz.

Figure 42. Using Several AD8351s to Form an N-Channel Analog MUX

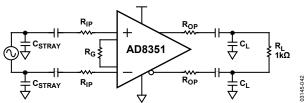

### **I/O CAPACITIVE LOADING**

Input or output direct capacitive loading greater than a few picofarads can result in excessive peaking and/or oscillation outside the pass band. This results from the package and bond wire inductance resonating in parallel with the input/output capacitance of the device and the associated coupling that results internally through the ground inductance. For low resistive load or source resistance, the effective Q is lower, and higher relative capacitance termination or terminations can be allowed before oscillation or excessive peaking occurs. These effects can be eliminated by adding series input resistors (R<sub>IP</sub>) for high source capacitance, or series output resistors (ROP) for high load capacitance. Generally less than 25  $\Omega$  is all that is required for I/O capacitive loading greater than ~2 pF. The higher the C, the smaller the R parasitic suppression resistor required. In addition, R<sub>IP</sub> helps to reduce low gain in-band peaking, especially for light resistive loads.

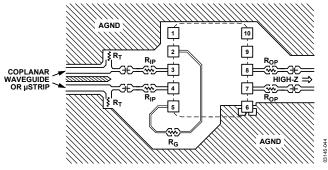

Figure 43. Input and Output Parasitic Suppression Resistors, R<sub>IP</sub> and R<sub>OP</sub>, Used to Suppress Capacitive Loading Effects

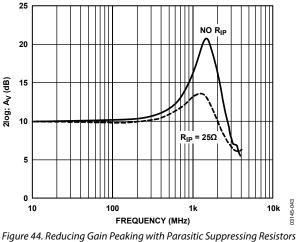

Due to package parasitic capacitance on the R<sub>G</sub> ports, high R<sub>G</sub> values (low gain) cause high ac-peaking inside the pass band, resulting in poor settling in the time domain. As an example, when driving a 1 k $\Omega$  load, using 25  $\Omega$  for R<sub>IP</sub> reduces the peaking by ~7 dB for R<sub>G</sub> equal to 200  $\Omega$  (A<sub>V</sub> = 10 dB) (see Figure 44).

Figure 44. Reducing Gain Peaking with Parasitic Suppressing Resistor:  $(R_{IP} = 25 \Omega, R_L = 1 k\Omega)$

It is important to ensure that all I/O, ground, and R<sub>G</sub> port traces be kept as short as possible. In addition, the ground plane must be removed from under the package. Due to the inverse relationship between the gain of the device and the value of the R<sub>G</sub> resistor, any parasitic capacitance on the R<sub>G</sub> ports can result in gain-peaking at high frequencies. Following the precautions outlined in Figure 45 helps to reduce parasitic board capacitance, thus extending the bandwidth of the device and reducing potential peaking or oscillation.

Figure 45. General Description of Recommended Board Layout for High-Z Load Conditions (10-Lead MSOP Package)

### TRANSMISSION LINE EFFECTS

As noted, stray transmission line capacitance, in combination with package parasitics, can potentially form a resonant circuit at high frequencies, resulting in excessive gain peaking.  $R_F$ transmission lines connecting the input and output networks must be designed to minimize stray capacitance. The output single-ended source impedance of the AD8351 is dynamically set to a nominal value of 75  $\Omega$ . Therefore, for a matched load termination, design the characteristic impedance of the output transmission lines to be 75  $\Omega$ . In many situations, the final load impedance may be relatively high, greater than 1 k $\Omega$ . It is suggested that the board be designed as shown in Figure 45 for high impedance load conditions. In most practical board designs, this requires that the printed circuit board traces be dimensioned to a small width (~5 mils) and that the underlying and adjacent ground planes are far enough away to minimize capacitance.

Typically the driving source impedance into the device is below and terminating resistors are used to prevent input reflections. The transmission line must be designed to have the appropriate characteristic impedance in the low-Z region. The high impedance environment between the terminating resistors and device input pins must not have ground planes underneath or near the signal traces. Small parasitic suppressing resistors may be necessary at the device input pins to help desensitize (de-Q) the resonant effects of the device bond wires and surrounding parasitic board capacitance. Typically, 25  $\Omega$  series resistors (size 0402) adequately de-Q the input system without a significant decrease in ac performance.

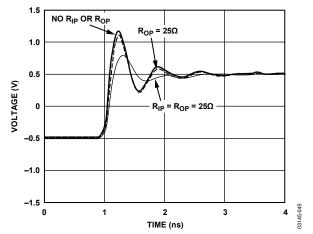

Figure 46 illustrates the value of adding input and output series resistors to help desensitize the resonant effects of board parasitics. Overshoot and undershoot can be significantly reduced with the simple addition of  $R_{IP}$  and  $R_{OP}$ .

Figure 46. Step Response Characteristics With and Without Input and Output Parasitic Suppression Resistors

### **CHARACTERIZATION SETUP**

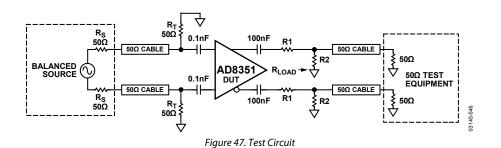

The test circuit used for 150  $\Omega$  and 1 k $\Omega$  load testing is shown in Figure 47. The evaluation board uses balun transformers to simplify interfacing to single-ended test equipment. Balun effects must be removed from the measurements to accurately characterize the performance of the device at frequencies exceeding 1 GHz. The output L-pad matching networks provide a broadband impedance match with minimum insertion loss. The input lines are terminated with 50  $\Omega$  resistors for input impedance matching. The power loss associated with these networks must be accounted for when attempting to measure the gain of the device. The required resistor values and the appropriate insertion loss and correction factors used to assess the voltage gain are shown in Table 5.

Table 5. Load Conditions Specified Differentially

| Load Condition | R1 (Ω) | R2 (Ω) | Total Insertion Loss (dB) | Conversion Factor 20 log (S21) to 20 log $(A_v)$ |

|----------------|--------|--------|---------------------------|--------------------------------------------------|

| 150 Ω          | 43.2   | 86.6   | 5.8                       | 7.6 dB                                           |

| 1 kΩ           | 475    | 52.3   | 15.9                      | 25.9 dB                                          |

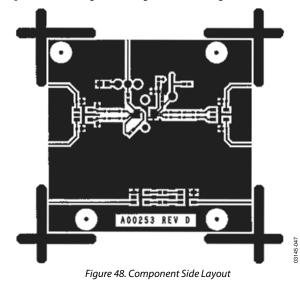

# **EVALUATION BOARD**

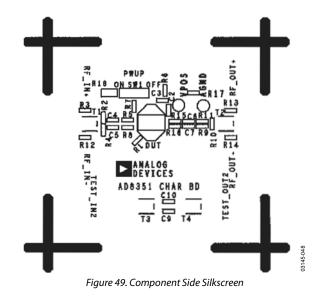

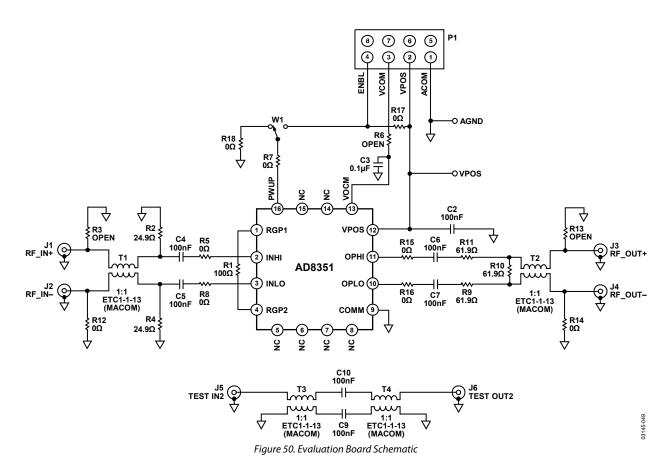

An evaluation board is available for experimentation. Various parameters such as gain, common-mode level, and input and output network configurations can be modified through minor resistor changes. The schematic and evaluation board artwork are presented in Figure 48, Figure 49, and Figure 50.

### Table 6. Evaluation Board Configuration Options

| Component                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Default Condition                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P1-1, P1-2,<br>VPOS, AGND                                     | Supply and Ground Pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Not Applicable                                                                                                                                                                                                                                                    |

| P1-3                                                          | Common-Mode Offset Pin. Allows for monitoring or adjustment of the output common-mode voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Not Applicable                                                                                                                                                                                                                                                    |

| W1, R7, P1-4,<br>R17, R18                                     | Device Enable. Configured such that switch W1 disables the device when Pin 1 is set to ground. Device can be disabled remotely using Pin 4 of header P1.                                                                                                                                                                                                                                                                                                                                                                                                                                               | W1 = Installed<br>R7 = 0 Ω (Size 0603)<br>R17 = R18 = 0 Ω (Size 0603)                                                                                                                                                                                             |

| R2, R3, R4, R5,<br>R8, R12, T1, C4,<br>C5                     | Input Interface. R3 and R12 are used to ground one side of the differential drive interface for single-ended applications. T1 is a 1-to-1 impedance ratio balun used to transform a single-ended input into a balanced differential signal. R2 and R4 are used to provide a differential 50 $\Omega$ input termination. R5 and R8 can be increased to reduce gain peaking when driving from a high source impedance. The 50 $\Omega$ termination provides an insertion loss of 6 dB. C4 and C5 are used to provide ac coupling.                                                                        | R2 = R4 = 24.9 $\Omega$ (Size 0805)<br>R3 = Open (Size 0603)<br>R5 = R8 = R12 = 0 $\Omega$ (Size 0603)<br>C4 = C5 = 10 0 nF (Size 0603)<br>T1 = Macom <sup>™</sup> ETC1-1-13                                                                                      |

| R9, R10, R11,<br>R13, R14, R15,<br>R16, T2, C4, C5,<br>C6, C7 | Output Interface. R13 and R14 are used to ground one side of the differential output interface for single-ended applications. T2 is a 1-to-1 impedance ratio balun used to transform a balanced differential signal into a single-ended signal. R9, R10, and R11 are provided for generic placement of matching components. R15 and R16 allow additional output series resistance when driving capacitive loads. The evaluation board is configured to provide a 150 $\Omega$ to 50 $\Omega$ impedance transformation with an insertion loss of 9.9 dB. C4 through C7 are used to provide ac coupling. | $R9 = R10 = 61.9 \Omega (Size 0603)$<br>$R11 = 61.9 \Omega (Size 0603)$<br>R13 = Open (Size 0603)<br>$R14 = 0 \Omega (Size 0603)$<br>$R15 = R16 = 0 \Omega (Size 0402)$<br>C4 = C5 = 100  nF (Size 0603)<br>C6 = C7 = 100  nF (Size 0603)<br>T2 = Macom ETC1-1-13 |

| R1                                                            | Gain Setting Resistor. Resistor R1 is used to set the gain of the device. Refer to Figure 5 when selecting gain resistor. When R1 is 100 $\Omega$ , the overall system gain of the evaluation board is approximately –6 dB.                                                                                                                                                                                                                                                                                                                                                                            | R1 = 100 Ω (Size 0603)                                                                                                                                                                                                                                            |

| C2                                                            | Power Supply Decoupling. The supply decoupling consists of a 100 nF capacitor to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C2 = 100 nF (Size 0805)                                                                                                                                                                                                                                           |

| R6, C3, P1-3                                                  | Common-Mode Offset Adjustment. Used to trim common-mode output level. By applying a voltage to Pin 3 of header P1, the output common-mode voltage can be directly adjusted. Typically decoupled to ground using a 0.1 µF capacitor.                                                                                                                                                                                                                                                                                                                                                                    | R6 = 0 $\Omega$ (Size 0603)<br>C3 = 0.1 $\mu$ F (Size 0805)                                                                                                                                                                                                       |

| T3, T4, C9, C10                                               | Calibration Networks. Calibration path provided to allow for compensation of the insertion loss of the baluns and the reactance of the coupling capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                            | T3 = T4 = Macom ETC1-1-13<br>C9 = C10 = 100 nF (Size 0603)                                                                                                                                                                                                        |

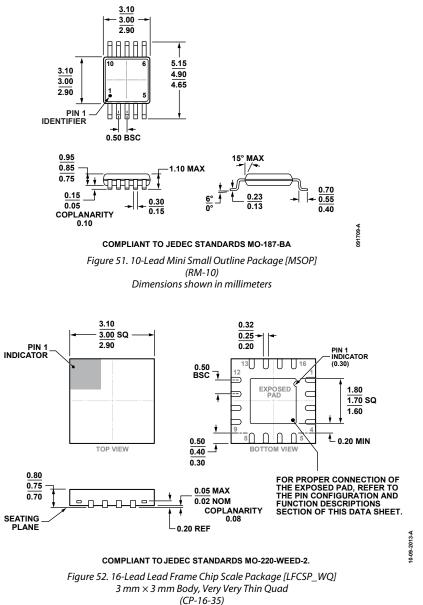

# **OUTLINE DIMENSIONS**

Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                              | Package Option | Branding |

|--------------------|-------------------|--------------------------------------------------|----------------|----------|

| AD8351ARM          | -40°C to +85°C    | 10-Lead Mini Small Outline Package [MSOP]        | RM-10          | JDA      |

| AD8351ARM-REEL7    | -40°C to +85°C    | 10-Lead Mini Small Outline Package [MSOP]        | RM-10          | JDA      |

| AD8351ARMZ         | -40°C to +85°C    | 10-Lead Mini Small Outline Package [MSOP]        | RM-10          | #JDA     |

| AD8351ARMZ-REEL7   | -40°C to +85°C    | 10-Lead Mini Small Outline Package [MSOP]        | RM-10          | #JDA     |

| AD8351ACPZ-R7      | -40°C to +85°C    | 16-Lead Lead Frame Chip Scale Package [LFCSP_WQ] | CP-16-35       | Q20      |

| AD8351-EVALZ       |                   | Evaluation Board                                 |                |          |

<sup>1</sup> Z = RoHS Compliant Part.

©2003–2015 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D03145-0-1/15(D)

www.analog.com

Rev. D | Page 19 of 19