# OCTAL INTELLIGENT SQUIB DRIVER ASIC

**PRELIMINARY DATA**

## 1 FEATURES

- EIGHT SQUIB DEPLOYMENT DRIVERS

- DEPLOYMENT CURRENT AND TIME PROGRAMMABLE VIA SPI, (1.2A/2ms AND 1.75A/4ms)

- CAPABILITY TO DEPLOY WITH 1.47A (2.14A) UNDER 40V (21V) LOAD-DUMP CONDITION AND THE LOW SIDE MOS SHORTED TO -1V.

- 5.5MHZ SPI INTERFACE WITH MESSAGE VALIDATION

- 4 CHANNELS OF DISCRETE/SERIAL LOGIC ARMING INTERFACE PROGRAMMABLE VIA SPI

- DEPLOYMENT DRIVER SELF-DIAGNOSTICS:

- SHORT TO BATTERY/GROUND AND OPEN CIRCUIT

- SQUIB RESISTANCE MEASUREMENT

- SHORT BETWEEN CHANNELS DETI:C-TIONS

- HIGH AND LOW SIDE MOS TESTS

- GROUND LOSS DETECTION

- -40 °C TO +85 °C OPERATING AMBIENT TEMPERATURE

- 4KV ESD CAPABILITY ON ALL OUTPUT-DRIVER PINS AND 2KV ON ALL OTHERS

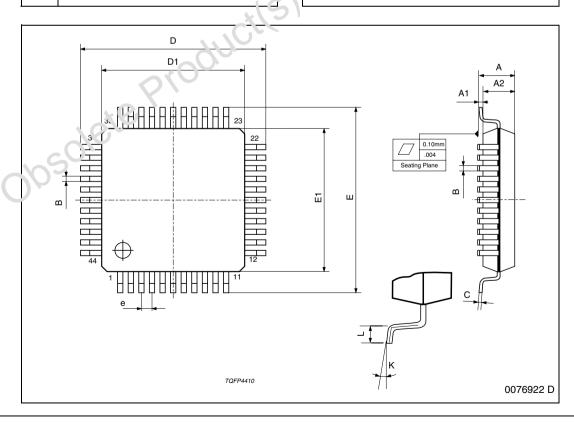

Figure 1. Package

Table 1. Order Codes

| Part Number | Package |

|-------------|---------|

| L9634       | TQFP44  |

# 2 DESCRIPTION

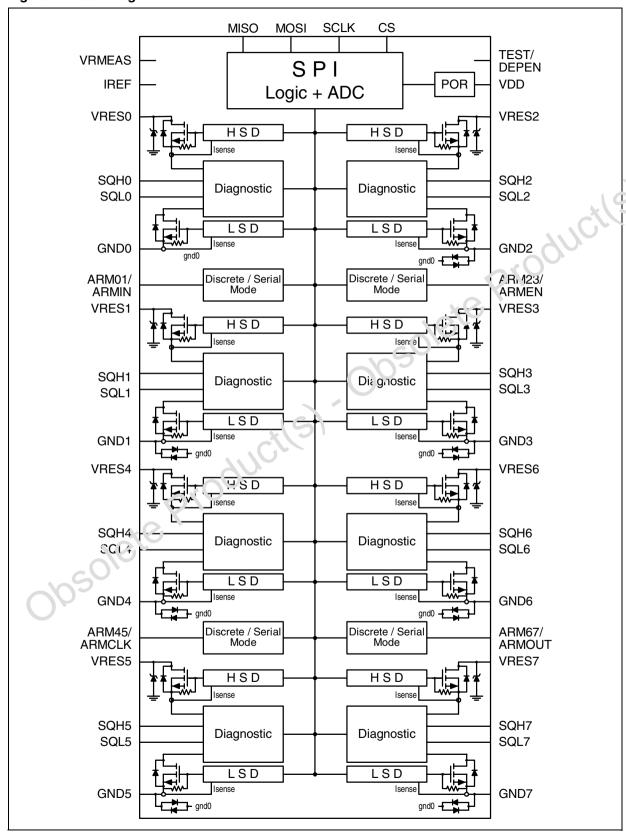

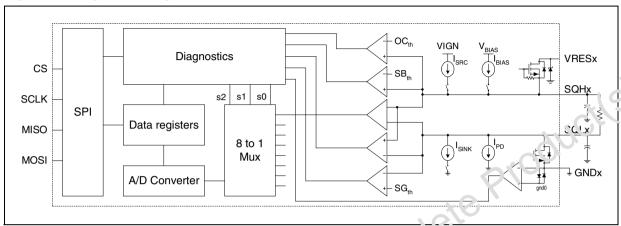

The L9634 is an Octal Intelligent Squib Driver ASIC. It is packaged in a 44pin Thin Quad Flat Pack (TQFP) package and designed using ST's proprietary BCD4 technology. The UH30 is intended to deploy up to eight airbag squib circuits and provide diagnostics for each of the deployment drivers. Each of the eight drivers is sized to deliver up to 1.75A minimum for up to 4ms. The deployment current and time are both programmable via the SPI port

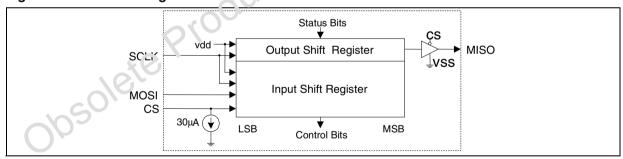

Figure 2. Block Diagram

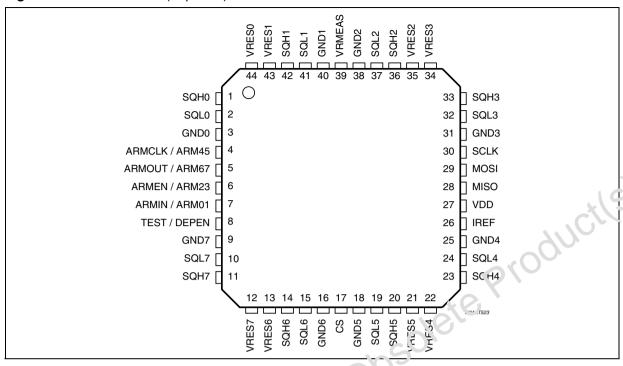

Figure 3. Pin Connection (Top view)

**Table 2. Pin Function**

| N°  | Pin    | Description                            | I/O Type |

|-----|--------|----------------------------------------|----------|

| 1   | SQH0   | High Side Driver Output for Charmel 0  | Out      |

| 2   | SQL0   | Low Side Driver Output or Channel 0    | Out      |

| 3   | GND0   | Power Ground 0                         | -        |

| 4   | ARMCLK | ARM Serial N od > Clock Input          | In       |

|     | ARM45  | Discreta Arm Signal for Channel 4 & 5  | In       |

| 5   | ARMOUT | A'TIN: Serial Mode Data Output         | Out      |

|     | ARM67  | L'iscrete Arm Signal for Channel 6 & 7 | In       |

| 6   | APMEIL | ARM Serial Mode Data Enable            | In       |

| - \ | AFM23  | Discrete Arm Signal for Channel 2 & 3  | In       |

| 7   | ARMIN  | ARM Serial Mode Data Input             | In       |

|     | ARM01  | Discrete Arm Signal for Channel 0 & 1  | In       |

| 8   | TEST   | Test Input Pin                         | In       |

|     | DEPEN  | Deployment Enable                      | In       |

| 9   | GND7   | Power Ground 7                         | -        |

| 10  | SQL7   | Low Side Driver Output for Channel 7   | Out      |

| 11  | SQH7   | High Side Driver Output for Channel 7  | Out      |

| 12  | VRES7  | Reserve Voltage for Loop Channel 7     | In       |

| 13  | VRES6  | Reserve Voltage for Loop Channel 6     | In       |

| 14  | SQH6   | High Side Driver Output for Channel 6  | Out      |

| 15  | SQL6   | Low Side Driver Output for Channel 6   | Out      |

| 16  | GND6   | Power Ground 6                         | -        |

| 17  | CS     | SPI Chip Select                        | In       |

Table 2. Pin Function (continued)

| N° | Pin    | Description                               | I/O Type |

|----|--------|-------------------------------------------|----------|

| 18 | GND5   | Power Ground 5                            | -        |

| 19 | SQL5   | Low Side Driver Output for Channel 5      | Out      |

| 20 | SQH5   | High Side Driver Output for Channel 5     | Out      |

| 21 | VRES5  | Reserve Voltage for Loop Channel 5        | In       |

| 22 | VRES4  | Reserve Voltage for Loop Channel 4        | In       |

| 23 | SQH4   | High Side Driver Output for Channel 4     | Out      |

| 24 | SQL4   | Low Side Driver Output for Channel 4      | Out      |

| 25 | GND4   | Power Ground 4                            | -        |

| 26 | IREF   | External Current Reference Resistor       | Out      |

| 27 | VDD    | VDD Supply Voltage                        | ln I     |

| 28 | MISO   | SPI Data Out                              | Oil      |

| 29 | MOSI   | SPI Data In                               | In       |

| 30 | SCLK   | SPI Clock                                 | In       |

| 31 | GND3   | Power Ground 3                            | -        |

| 32 | SQL3   | Low Side Driver Output for Channel 3      | Out      |

| 33 | SQH3   | High Side Driver Output for Channel 3     | Out      |

| 34 | VRES3  | Reserve Voltage for Loop Channel 3        | In       |

| 35 | VRES2  | Reserve Voltage for Loop Channel 2        | In       |

| 36 | SQH2   | High Side Driver Output for Channel 2     | Out      |

| 37 | SQL2   | Low Side Driver Output for Channel 2      | Out      |

| 38 | GND2   | Power Ground 2                            | -        |

| 39 | VRMEAS | Supply Voltage for Resistance Mans rement | In       |

| 40 | GND1   | Power Ground 1                            | -        |

| 41 | SQL1   | Low Side Driver C เถานเ for Channel 1     | Out      |

| 42 | SQH1   | High Side Driver วิบ.put for Channel 1    | Out      |

| 43 | VRES1  | Reserve 16 tage for Loop Channel 1        | In       |

| 44 | VRES0  | Reserve Voltage for Loop Channel 0        | In       |

# Table 3. Absolute Maximum Ratings \*)

| Symbol          | Parameter                              | Value       | Unit |

|-----------------|----------------------------------------|-------------|------|

| , v Dr          | Supply voltage                         | -0.3 to 6.5 | V    |

|                 | VRMEAS voltage                         | -0.3 to 40  | V    |

|                 | VRES voltage                           | -0.3 to 40  | V    |

|                 | SQHX, SQLX squib high and low side drv | -1 to 40    | V    |

| V <sub>in</sub> | Discrete input voltage                 | -0.3 to 6.5 | V    |

| Tj              | Maximum junction temperature           | +150        | °C   |

<sup>\*)</sup> Maximum ratings are absolute values: exceeding any one of these values may cause permanent damage to the integrated circuit.

# **Table 4. Thermal Data**

| Symbol                | Parameter                              | Value       | Unit |

|-----------------------|----------------------------------------|-------------|------|

| R <sub>thj-amb</sub>  | Thermal Resistance Junction to Ambient | 68          | °C/W |

| R <sub>thj-case</sub> | Thermal Resistance Junction to Case    | 14          | °C/W |

| T <sub>stg</sub>      | Storage Temperature                    | -50 to +175 | °C   |

# 3 ELECTRICAL CHARACTERISTICS

**Table 5. Electrical Characteristics**

(VRES = 6.5 to 40V, VDD = 4.9 to 5.1V, VRMEAS = 7.0V to 26.5V,  $T_{amb}$  = -40°C to +95°C unless otherwise specified)

| Symbol                | Parameter                          | Test Condition                                         | Min.        | Тур. | Max. | Unit |

|-----------------------|------------------------------------|--------------------------------------------------------|-------------|------|------|------|

| V <sub>RST</sub>      | VDD Internal Voltage Reset         | VDD drops until deployment drivers are disabled        | 4.2         |      | 4.7  | V    |

| I <sub>DD</sub>       | VDD Input Current                  | Normal operation                                       |             |      | 5    | mA   |

|                       |                                    | Short to -1V on SQH                                    |             |      | 5    |      |

|                       |                                    | Short to -1V on SQL                                    |             |      | 5    |      |

|                       |                                    | Deployment                                             |             |      | 20   |      |

| V <sub>IH</sub>       | Input Voltage                      | Input Logic = 1                                        |             |      | 2.0  | I.   |

| V <sub>IL</sub>       | MOSI, SCLK, CS, ARMx               | Input Logic = 0                                        | 8.0         |      | AL   |      |

| V <sub>HYS</sub>      | 7                                  |                                                        | 50          | (    | 70   | mV   |

| I <sub>LKG</sub>      | Input Leakage Current              | V <sub>IN</sub> = VDD                                  |             | 01   | 1    | μΑ   |

|                       | MOSI, SCLK                         | V <sub>IN</sub> = 0 to V <sub>IH</sub>                 | -10         |      |      |      |

| V <sub>IH_DEPEN</sub> | DEPEN                              |                                                        | Ole         |      | 2.0  | V    |

| V <sub>IL_DEPEN</sub> | Input Voltage                      |                                                        | Ú.8         |      |      |      |

| V <sub>HYS</sub>      | 1                                  | 105                                                    | 50          |      |      | mV   |

| V <sub>IH_TEST</sub>  | TEST                               | Ob.                                                    |             |      | 8.5  | V    |

| V <sub>IL_TEST</sub>  | Input Voltage                      |                                                        | 5.5         |      |      |      |

| I <sub>PD</sub>       | Input Pulldown Current<br>ARMx, CS | V <sub>IN</sub> = V <sub>II</sub> to VDD               | 10          |      | 50   | μА   |

|                       | DEPEN                              | $\overline{v_{IN}} = V_{IL}$ to VDD                    | 10          |      | 100  |      |

| V <sub>OH</sub>       | Output Voltage<br>MISO             | I <sub>OH</sub> = -800μA                               | VDD-<br>0.8 |      |      | V    |

| V <sub>OL</sub>       |                                    | I <sub>OL</sub> = 1.6mA                                |             |      | 0.4  |      |

| IZ                    | MISO Tri-State Current             | MISO = VDD                                             |             |      | 10   | μΑ   |

|                       | *6                                 | MISO = 0V                                              | -10         |      |      |      |

| Deployment            | Driver: DC specification           |                                                        |             | •    |      | 1    |

| I <sub>LKG</sub>      | CQH Leakage                        | VRMEAS=VDD=0,<br>VRESx=36V, V <sub>SQH</sub> = 0V      |             |      | 50   | μΑ   |

| I <sub>ST(</sub>      | -                                  | VRMEAS=18V; VDD=5V;<br>V <sub>SQH</sub> = -1V          | -5          |      |      | mA   |

| I <sub>LKG</sub>      | VRESx Bias Current <sup>1</sup>    | VRMEAS=18V; VDD=5V;<br>VRESx=36V;SQH shorted to<br>SQL |             |      | 10   | μА   |

| I <sub>LKG</sub>      | SQL Leakage                        | VRMEAS=Vdd=0, V <sub>SQL</sub> =18V                    | -10         |      | 10   | μΑ   |

| I <sub>STG</sub>      |                                    | VRMEAS=18V; VDD=5V;<br>V <sub>SQL</sub> = -1V          | -5          |      |      | mA   |

| I <sub>STB</sub>      | 1                                  | VRMEAS=18V; VDD=5V;<br>V <sub>SQL</sub> = 18V          |             |      | 5    | mA   |

| I <sub>PD</sub>       | SQL Pulldown Current               | V <sub>SQLx</sub> = 1.8V - VDD                         | 500         |      | 700  | μΑ   |

| SG <sub>th</sub>      | Short to Ground Threshold          | VDD = 5.0V                                             | 1.9         | 1    | 2.1  | V    |

| SB <sub>th</sub>      | Short to Battery Threshold         | VDD = 5.0V                                             | 3.9         |      | 4.1  | V    |

Table 5. Electrical Characteristics (continued)

(VRES = 6.5 to 40V, VDD = 4.9 to 5.1V, VRMEAS = 7.0V to 26.5V,  $T_{amb}$  = -40°C to +95°C unless otherwise specified)

| Symbol               | Parameter                                              | Test Condition                                                                    | Min. | Тур. | Max. | Unit               |

|----------------------|--------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|--------------------|

| OC <sub>th</sub>     | Open Circuit Threshold                                 | VDD = 5.0V                                                                        | 1.9  |      | 2.1  | V                  |

| V <sub>I_th</sub>    | MOS Test<br>Load Voltage Detection                     |                                                                                   | 100  |      | 300  | mV                 |

| I <sub>SRC</sub>     | Resistance Measurement<br>Current Source               | VDD = 5.0V;<br>VRMEAS = 7.0V to 26.5V                                             | 38   |      | 42   | mA                 |

| Isink                | Resistance Measurement<br>Current Sink                 |                                                                                   | 45   |      | 55   | mA                 |

| R <sub>DSon</sub>    | Total High and Low Side On<br>Resistance               | High Side MOS + Low Side<br>MOS<br>VRES = 6.9V; I = 1.2A @95°C                    |      |      | 1.5  | Ω                  |

| R <sub>DSon</sub>    | Total High and Low Side On<br>Resistance               | High Side MOS + Low Side<br>MOS<br>VRES = 6.9V; I <sub>VRES</sub> = 1.1A<br>@95°C |      | 01   | 1.5  |                    |

| R <sub>DSon</sub>    | High Side MOS On Resistance                            | VRES = 40V; I <sub>VRES</sub> = 1.1A;<br>Ta = 95°C                                | ×6   |      | 0.50 | Ω                  |

| R <sub>DSon</sub>    | Low Side MOS On Resistance                             | VRES = 40V; I <sub>VRES</sub> = 1.1A;<br>Ta = 95°C                                | S    |      | 1.0  | Ω                  |

| I <sub>DEPLOY</sub>  | Deployment Current (Channel 0, 3, 4, and 7)            | MOSI: Command Mode $C_{11}=0$ ; $R_{LOAD}=3.75\Omega$ ; $V_{LC}=5.5$ to $40V$     | 1.2  |      | 1.47 | А                  |

|                      |                                                        | MOSI: Command Mode D11=1;<br>RLCAD-5.5 Q; VRES=12V to<br>21V                      | 1.75 |      | 2.14 |                    |

| I <sub>LIM</sub>     | Low side MOS current limit (Channel 0, 3, 4, and 7)    | MCCI: Command Mode D11=1/<br>υ, R <sub>LOAD</sub> =5.3Ω; V <sub>SQH</sub> =18V    | 1.75 |      | 2.14 | Α                  |

| IDEPLOY              | Deployment Current<br>(Channel 1, 2, 5, ฉาเ 6)         | MOSI: Command Mode D11=0;<br>R <sub>LOAD</sub> =3.75Ω; VRES=6.9 to<br>40V         | 1.34 |      | 1.64 | Α                  |

|                      | alete,                                                 | MOSI: Command Mode D11=1; $R_{LOAD}$ =5.3 $\Omega$ ; VRES=12V to 21V              | 1.95 |      | 2.39 |                    |

| I <sub>LIM</sub>     | Low side MOS current limit<br>(Channel 1, 2, 5, and 6) | MOSI: Command Mode D11=1/<br>0; R <sub>LOAD</sub> =5.3Ω; V <sub>SQH</sub> =18V    | 1.95 |      | 2.39 | А                  |

| I <sub>BIA</sub> ;   | Diagnostics Bias Current                               | V <sub>SQH</sub> =0V; Part is configured to run in diagnostics mode via SPI       | -7   |      | -4   | I <sub>PD</sub>    |

| V <sub>BIAS</sub>    | Diagnostics Bias Voltage                               | I <sub>SQH</sub> = -1.5mA                                                         | 2.7  |      | 3.3  | V                  |

| R <sub>IREF</sub>    | IREF Resistance Threshold                              | Open Circuit                                                                      |      |      | 62.5 | kΩ                 |

|                      |                                                        | Short Circuit                                                                     | 2.5  |      |      | kΩ                 |

| R <sub>L_RANGE</sub> | Load Resistance Range                                  | $\%0000\ 0000 = 0.0Ω;$<br>$\%1111\ 1111 = 10.0Ω$                                  | 0.0  |      | 10.0 | W                  |

| ADC <sub>ACC</sub>   | ADC Accuracy                                           | $R_L = 4.0\Omega$ to $10.0\Omega$                                                 |      |      | 5    | %                  |

|                      |                                                        | $R_L = 0.0\Omega$ to $4.0\Omega$                                                  |      |      | 5    | counts             |

| ADC <sub>RES</sub>   | ADC Resolution                                         |                                                                                   | 8    |      |      | bits               |

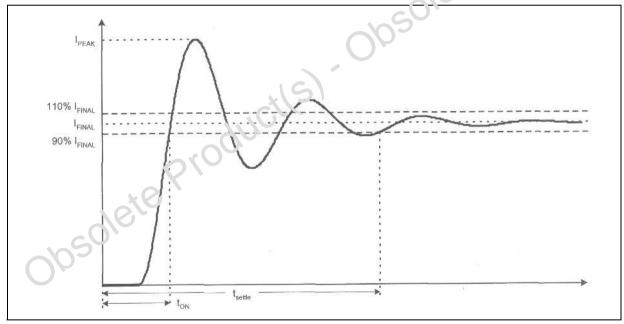

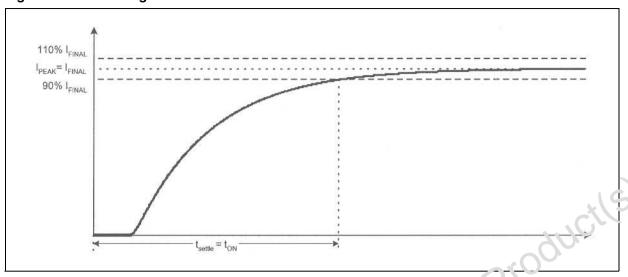

| I <sub>PEAK</sub>    | MOS Transient Response<br>Peak Current                 | See Figure 19 and Figure 20                                                       |      |      | 2.0  | I <sub>FINAL</sub> |

Table 5. Electrical Characteristics (continued)

(VRES = 6.5 to 40V, VDD = 4.9 to 5.1V, VRMEAS = 7.0V to 26.5V,  $T_{amb}$  = -40°C to +95°C unless otherwise specified)

| Symbol              | Parameter                           | Test Condition                                                                                                                              | Min. | Тур. | Max. | Unit |  |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| Deployment          | Deployment Drivers AC Specification |                                                                                                                                             |      |      |      |      |  |

| t <sub>POR</sub>    | POR De-glitch Timer                 |                                                                                                                                             | 5    |      | 20   | μs   |  |

| ton                 | MOSs turn on time                   | ARMx and DEPEN pins<br>asserted<br>Measured from falling edge CS<br>to<br>90% of I <sub>FINAL</sub> ;<br>See Figure 19 and Figure 20        |      |      | 150  | μs   |  |

| t <sub>settle</sub> | MOSs settling time                  | ARMx and DEPEN pins<br>asserted<br>Measured from falling edge CS<br>to<br>90% - 110% of I <sub>FINAL</sub> ;<br>See Figure 19 and Figure 20 |      | 0.5( | 300  | με   |  |

| t <sub>PULSE</sub>  | Pulse Stretch Timer                 | See "Pulse Stretch Timer table"                                                                                                             | 0    |      | 60   | ms   |  |

<sup>1.</sup> Not applicable during the diagnostic.

Figure 4. MOS Settling time and turn-on time 1

Figure 5. MOS Settling time and turn-on time 2

**Table 5. Electrical Characteristics**

| Symbol                 | Parameter                                         | Test Condition                                                                                                                           | ı∕in. | Тур. | Max. | Unit  |

|------------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| t <sub>P_ACC</sub>     | Pulse Stretch Timer Accuracy                      | 60                                                                                                                                       | -20   |      | 20   | %     |

| tGLITCH                | Pulse Stretcher De-glitch timer                   | 003                                                                                                                                      | 5     |      | 25   | μs    |

| t <sub>DEPLOY</sub>    | Deployment Time                                   | VRES = 6.9 - 40V <sup>4</sup><br>(see table)                                                                                             | 2     |      | 2.25 | ms    |

|                        |                                                   | VRES = 12 - 21V <sup>3</sup> ;<br>(se ∋ (abie)                                                                                           | 4     |      | 4.5  |       |

| t <sub>TIMEOUT</sub>   | Diagnostic Bias Current Time                      | ime trom falling edge of CS until<br>JPI diagnostic complete flag is<br>set, in case of Short to GND for a<br>single channel diagnostic. |       |      | 2.5  | ms    |

| t <sub>FLT_DLY</sub>   | Fault Detection Files <sup>2</sup>                |                                                                                                                                          | 10    |      | 50   | μs    |

| I <sub>SLEW</sub>      | Rmeas Current di/dt                               |                                                                                                                                          |       |      | 40   | mA/μs |

| tres                   | Resistance Measurement                            | Duration when I <sub>DIAG_SRC</sub> and I <sub>DIAG_SINK</sub> are connected to SQH and SQL during a Resistance Measurement              |       |      | 2.5  | ms    |

| t <sub>MC°_ON</sub>    | MOS test<br>turn-on time <sup>2</sup>             | On-time of a LS/HS driver during a MOS test                                                                                              |       |      | 2.5  | ms    |

| tDETECT                | MOS test detection window <sup>2</sup>            | Time window to check for a LS/<br>HS MOS fault on a single loop                                                                          |       |      | 7.5  | ms    |

| t <sub>PROP_DLY</sub>  | LS/HS MOS turn off propagation delay <sup>2</sup> | Time is measured from the valid LS/HS MOS condition to the LS/HS turn off                                                                |       |      | 10   | μs    |

| t <sub>DIAG1</sub>     | Diagnostic Time <sup>3</sup>                      | For a single loop;<br>MOS Test Disabled                                                                                                  |       |      | 5    | ms    |

| t <sub>DIAG_MULT</sub> |                                                   | For 8 loops<br>MOS Tests Disabled                                                                                                        |       |      | 40   |       |

Application information only; not tested.

Time from Falling edge of CS until SPI "diagnostic" flag is set.

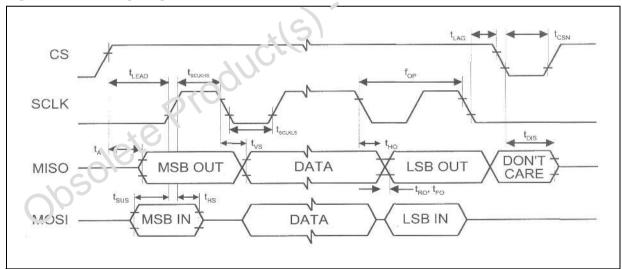

Table 6. SPI Timing (All SPI timing is performed with a 200pF load on MISO unless otherwise noted)

| Item Symbol |                  | Parameter                      | Lin | Limits |      |  |

|-------------|------------------|--------------------------------|-----|--------|------|--|

| item        | Syllibol         | Parameter                      | Min | Max    | Unit |  |

| -           | fop              | Transfer Frequency             | dc  | 5.50   | MHz  |  |

| 1           | tsck             | SCLK Period                    | 181 | -      | ns   |  |

| 2           | tLEAD            | Enable Lead Time               | 65  | -      | ns   |  |

| 3           | t <sub>LAG</sub> | Enable Lag Time                | 50  | -      | ns   |  |

| 4           | tsclkhs          | SCLK High Time                 | 65  | -      | ns   |  |

| 5           | tsclkls          | SCLK Low Time                  | 65  | -      | ns   |  |

| 6           | tsus             | MOSI Input Setup Time          | 20  | -      | ns   |  |

| 7           | t <sub>HS</sub>  | MOSI Input Hold Time           | 20  | -      | ns   |  |

| 8           | t <sub>A</sub>   | MISO Access Time               | -   | 66     | ns   |  |

| 9           | t <sub>DIS</sub> | MISO Disable Time (Note 1)     | -   | 100    | ns   |  |

| 10          | t <sub>VS</sub>  | MISO Output Valid Time         | -   | 45     | ns   |  |

| 11          | t <sub>HO</sub>  | MISO Output Hold Time (Note 1) | 0   | ~40    | ns   |  |

| 12          | t <sub>RO</sub>  | Rise Time (Design Information) | -   | - 30   | ns   |  |

| 13          | t <sub>FO</sub>  | Fall Time (Design Information) | 50, | 30     | ns   |  |

| 14          | t <sub>CSN</sub> | CS Negated Time                | 136 | -      | ns   |  |

Notes: 1. Parameters t<sub>dis</sub> and t<sub>ho</sub> is measured with no additional capacitive load beyond the not not test fixture capacitance on the MISO pin. Additional capacitance during the disable time test erroneously extends the rieasured output disable time, and minimum capacitance on MISO is the worst case for output hold time.

Figure 6. SPI Timing Diagram

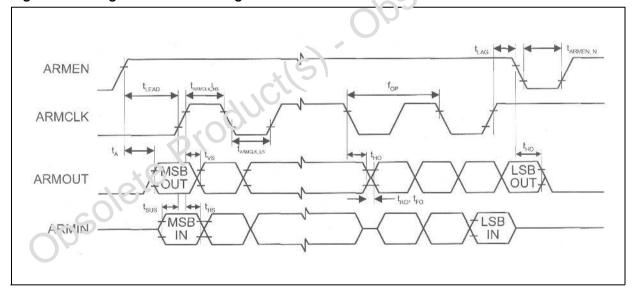

**Table 7. Arming Serial Mode Timing**

(All Arming serial mode timing is performed with a 50pF load on ARMOUT unless otherwise noted)

| Item | Symbol              | Parameter                      | Lim<br>Min | nits<br>Max | Unit |

|------|---------------------|--------------------------------|------------|-------------|------|

| -    | fop                 | Transfer Frequency             | dc         | 2           | MHz  |

| 1    | t <sub>ARMCLK</sub> | ARMCLK Period                  | 500        |             | ns   |

| 2    | t <sub>LEAD</sub>   | Enable Lead Time               | 250        |             | ns   |

| 3    | tLAG                | Enable Lag Time                | 100        |             | ns   |

| 4    | tarmclk_hs          | ARMCLK High Time               | 220        |             | ns   |

| 5    | tarmclk_ls          | ARMCLK Low Time                | 220        |             | ns   |

| 6    | tsus                | ARMIN Input Setup Time         | 30         |             | ns   |

| 7    | t <sub>HS</sub>     | ARMIN Input Hold Time          | 10         |             | ns   |

| 8    | t <sub>A</sub>      | ARMOUT Access Time             |            | 125         | กร   |

| 9    | t <sub>VS</sub>     | ARMOUT Output Valid Time       |            | 190         | ns   |

| 10   | t <sub>HO</sub>     | ARMOUT Output Hold Time        | 10         | ~40         | ns   |

| 11   | t <sub>RO</sub>     | Rise Time (Design Information) |            | 50          | ns   |

| 12   | t <sub>FO</sub>     | Fall Time (Design Information) | .0.        | 30          | ns   |

| 13   | tarmen_n            | ARMEN Negated Time             | 2.70       |             | ns   |

Figure 7. Arming Serial Mode Timing

oducils

# 4 CIRCUIT DESCRIPTION

OSD is an integrated circuit to be used in air bag systems. Its main functions are deployment of the air bag and diagnostics of the SDM (Sensing Deployment Module). The OSD supports 8 de-ployment loops.

The main features of OSD IC are:

- 8 deployment drivers sized to deliver 1.2A min for 2ms min at 40V max or 1.75A min for 4ms min at 21V max (current and time are internally limited while power supply is externally limited).

- 10% accuracy for deployment current.

- 5% accuracy for deployment time.

- High side and Low side current limits programmable via SPI.

- Low-voltage internal reset

- 5.5MHz SPI Interface

- SPI Message Validation

- 4 discrete logic arming inputs

- High and low-side MOS tests

- Squib resistance measurement with 5% accuracy

- Short to -1V protection on all deployment loops (high and low side).

- Capability to deploy with 1.2A min under 40V load-dump condition and the low side MOS is shorted to -1V.

- Capability to deploy with 1.75A min under 21V condition and the lov side MOS is shorted to -1V

- Capability to deploy with 1.75A min, when the high side MOS is shorted to 18V-battery and -1V ground difference.

- Capability to deploy the air bag with 1.2A min @ 6.9 / Vกะร

- Deployment loops short to ground and short to battery detection

- Short between loops detection

- -40°C to +95°C ambient temperature

- Package: 44LD TQFP

- Technology: ST's proprietary BCD Process

#### 4.1 Power On Reset

VDD loss of regulation detection is filtered for tPOR prior to issue an internal reset. This filter is intended to provide protection was short transients on VDD input. When VDD input voltage decreases below VRST for tPOR, OSD undergoes an internal reset. OSD keeps all current sinks and current sources, except the IPD, inactive and all outputs are driven to an inactive state and remains inactive as VDD decays down to OV. When VOD rises above VRST, the outputs and the internal current sinks and current sources are enabled. When OSD is in reset, none of the outputs are momentarily turned on.

# 4.2 Deployment Drivers

The on chip deployment drivers are sized to deliver IDEPLOY. Deployment current and period are programmable via SPI. The high side driver survives deployment condition 1 and 2 as defined here below. SQLx is shorted to ground (-1V) in these two conditions.

**Table 8. Deployment Survivability Conditions**

| No. | Drivers |                     | Conditions              |                   |          |  |  |

|-----|---------|---------------------|-------------------------|-------------------|----------|--|--|

| NO. | Drivers | I <sub>DEPLOY</sub> | Voltage                 | R <sub>LOAD</sub> | Duration |  |  |

| 1.  | SQHx    | 1.47A               | VRESx = 40V; SQLx = -1V | 1.7Ω              | 2.5mS    |  |  |

| 2.  |         | 2.14A               | VRESx = 21V; SQLx = -1V | 1.7Ω              | 4.5mS    |  |  |

| 3.  | SQLx    | 2.14A               | SQHx = 18V              | 1.7Ω              | 4.5mS    |  |  |

The Low Side driver survives deployment condition 3 as defined above.

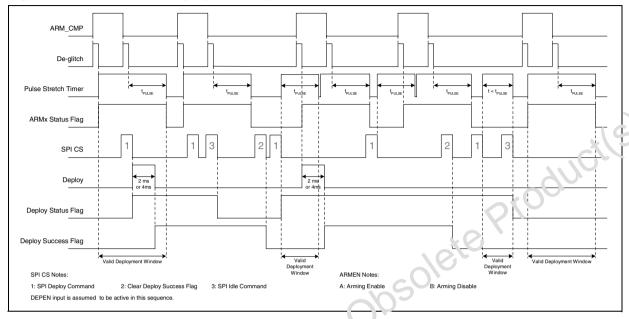

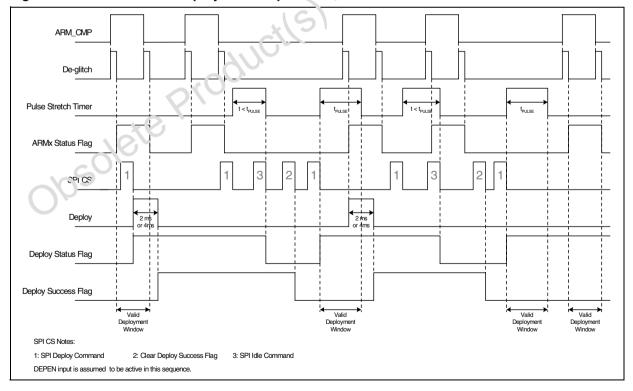

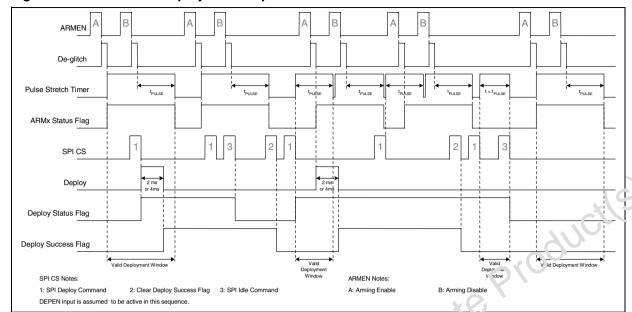

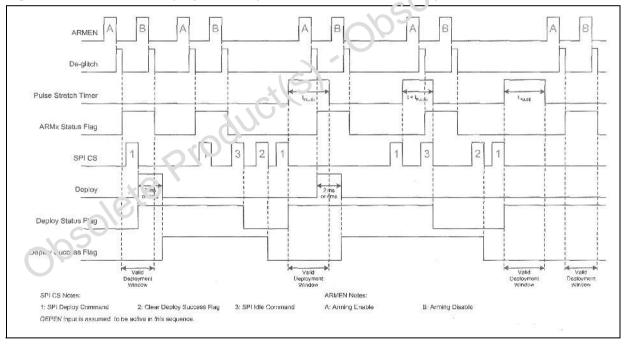

Upon receiving a valid deployment condition, the respective SQH and SQL drivers are turned on. Also, SQH and SQL drivers are turned on momentarily during a MOS diagnostic. Otherwise, SQH and SQL are inactive under any normal, fault, or transient conditions. Upon a successful deployment of the respective SQH and SQL drivers, a deploy command success flag is asserted via SPI. Refer to Figure 4, Figure 5, Figure 6, and Figure 7. for the valid deployment condition and the "Deploy Command Success" timing.

The following power-up conditions are considered as normal operations in OSD. VRES input can be connected to either a power supply output or an ignition voltage. VDD is connected to the 5V output of power supply. When VRES is connected to the power supply, VDD voltage will reach its regulation voltage before VRES voltage is stabilized. In this condition, OSD has a control of its internal logic and prevents an inadvertent turn-on of the drivers.

When VRES is connected to the ignition, VRES voltage will be stabilized before VDD reach its regulation voltage. In this condition, all drivers are inactive. A pulldown on the gates of high side drivers (SQH) is provided to prevent these drivers from momentarily turning-on.

Any fault conditions on OSD does not turn on the SQH and SQL drivers. Only a valid deployment condition turns on the respective SQH and SQL drivers.

#### 4.3 Arming Inputs

The arming inputs serve as a fail-safe mechanism to prevent inadvertent deployment. Along with the SPI deployment bit, these inputs provide redundancy. These pins are used either as discrete outputs or as a serial data communication interface with 4-bit shift register. Pulse stretch are is provided for each channel/loop. Either ARMx signal or SPI deployment bit starts the pulse size oner.

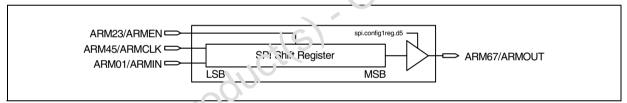

Figure 8. Arming Serial Mode Diagram

When a valid deployment command is sent through the SPI, the pulse stretcher is initiated immediately following the falling edge of CS. When another valid deployment command is sent before the timer for the first command expired, fro timer is refreshed. Sending an idle command terminates the pulse stretch timer operation. ONLY a timer operation started by a valid SPI deployment command is terminated. An idle command does not affect the timer operation started by ARM signal. OSD deploys a channel, ONLY when the respective ARM signal is asserted during a valid pulse stretcher signal. During the deployment, OSD turns on the respective high (SQH) and low side (SQL) drivers for tDEPLOY. Once deployment is initiated it can not be reminated. If one or more channels are deploying, OSD ignores all commands to the respective channels. The rest of the channels resume operation and respond to the SPI commands. Refer to Figure 5 for a deployment diagram initiated by a SPI deployment command.

In a discrete mode, when the ARM signal is asserted (active high), the pulse stretcher signal is asserted after the de-glitch filter time, tGLITCH, expires. The de-glitch filter is used to prevent noise from starting the pulse stretcher. The pulse stretcher timer, tPULSE, is initiated after a de-glitch time of the ARM falling edge. OSD deploys a channel, ONLY when the respective SPI deployment command is sent during a valid pulse stretcher signal. During the deployment, OSD turns on the respective high (SQH) and low side (SQL) drivers for tDEPLOY. When deployment is initiated it can not be stopped. Refer to Figure 4 and Figure 5 for a deployment diagram initiated by an ARM discrete signal.

In serial mode, OSD latch the arm state for each channel from the shift register when ARMEN is negated. After the de-glitch filter time, tGLITCH, of the ARMEN falling edge expires, OSD starts the pulse stretch timer for the respective channel. Serial mode is selected by setting bit D5 in the Deployment Configuration Register 1 (see "Deployment Configuration Register 1 table 15"). OSD deploys a channel, ONLY when the respective SPI deployment command is sent during a valid pulse stretcher signal. During the deploy-

ment, OSD turns on the respective high (SQHx) and low side (SQLx) drivers for tDEPLOY. When deployment is initiated it can not be stopped. Refer to Figure 11 and Figure 12 for a deployment diagram initiated by an arming signal in serial mode.

Figure 9. Discrete Mode: Deployment Sequence with Pulse Stretch Timer Enabled

Figure 10. Discrete Mode: Deployment Sequence with Pulse Stretch Timer Disabled

Figure 11. Serial Mode: Deployment Sequence with Pulse Stretch Timer Enabled

Figure 12. Serial Mode: Deployment Sequence with Pulse Stretch Tinier Disabled

# 4.4 ARM01 / ARMIN

In discrete mode, this pin acts as the ARM input channel 0 and channel 1. In serial mode, this pin acts as the input of Arming shift register.

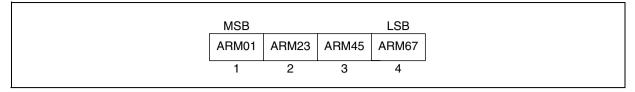

The ARMIN input takes data from the processor or another OSD while ARMEN is asserted. The MSB is the first bit of each word received on ARMIN. The LSB is the last bit of each word received on ARMIN. See Figure 8 below for Aming shift register. This pin has a TTL level compatible input voltages allowing proper operation with another devices using a 3.3V to 5.0V supply.

Figure 13. Arming Shift Register

#### 4.5 ARM23 / ARMEN

In discrete mode, this pin acts as the ARM input channel 2 and channel 3. In serial mode, this pin acts as an active high input to select this device for serial transfers. This pin has a TTL level compatible input voltages allowing proper operation with another devices using a 3.3V to 5.0V supply.

While ARMEN is asserted, arming register data is shifted into the ARMIN pin and shifted-out of the ARMOUT pin on both rising and falling edges of ARMCLK. On the falling edge of ARMEN, OSD latch-in the bits from the shift register, and clear the shift register contents.

#### 4.6 ARM45 / ARMCLK

In discrete mode, this pin acts as the ARM input channel 4 and channel 5. In seria mode, this pin acts as a clock input for serial communication. This pin has a TTL level compatible input voltages allowing proper operation with another devices using a 3.3V to 5.0V supply.

When ARMEN is asserted, on the rising or falling edge of ARMCLK the note level input at the ARMIN pin is shifted into the internal Arming shift register. While MSB in the chift register is shifted-out on the ARMOUT pin. Serial data is shifted in and out of the shift register on each ARMCLK edge. When ARMEN is negated, OSD ignores ARMCLK signal.

A clock edge counter is provided to verify a valid serial arming communication. A valid serial arming communication contains (4n - 1) ARMCLK edges. Other vise, OSD ignores the serial arming messages.

#### 4.7 ARM67 / ARMOUT

In discrete mode, this pin acts as the AN input channel 6 and channel 7. In serial mode, this pin acts as the output of Arming shift register are is pin has a TTL level compatible input voltages allowing proper operation with another devices using a 3.3V to 5.0V supply.

When ARMEN is negated, ARMOUT pin is pulled down. When ARMEN is asserted, the MSB is the first bit of the nibble shifted onto ARMOUT. The LSB is the last bit shifted onto ARMOUT.

### 4.8 TEST / DEPEN (Deployment Enable)

DEPEN is a ueployment enable input, which is an active high input. When DEPEN is negated, it inhibits the high-side and the low-side MOSs from turning on. If DEPEN is negated when a valid deployment is received, OSD inhibits the deployment. If DEPEN is negated when a diagnostic command is received, OSD executes the diagnostic sequence. If a MOS diagnostic is executed while DEPEN is negated, OSD returns a low-side MOS fault. SPI remains functional while this pin is pulled low. When this pin is asserted, OSD is able to drive its high and low side drivers upon receiving a valid deployment command or a MOS diagnostic. DEPEN does not initiate a deployment nor terminate a deployment if it is already started.

To enter a test mode, this pin has to be pulled higher than VIH TEST.

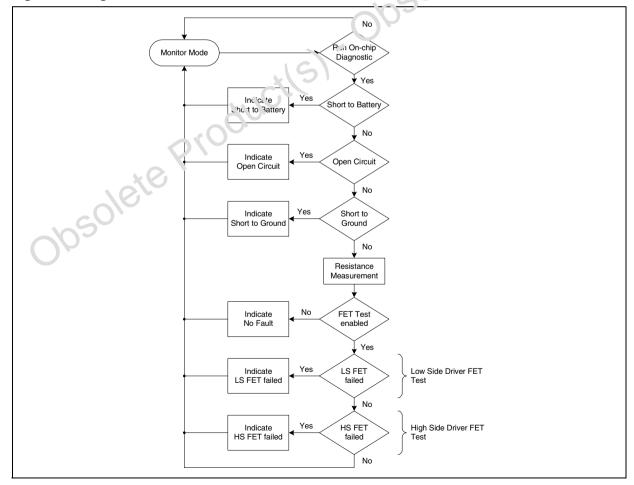

#### 4.9 Deployment Driver Diagnostics

OSD runs an on-chip self-diagnostics when commanded via SPI. By default, OSD is in the monitor mode (D15 & D14 = %11). The on-chip diagnostic operates according to the flow chart shown in Figure 15. If a fault condition is detected, the state machine asserts a fault bit, which serves as a flag to the processor. Once a fault bit asserted, OSD terminates the diagnostic tests for that particular channel and start diagnostic tests on the next channel. The fault information in OSD is sent out through MISO. For diagnostic

mode SPI bit definition.

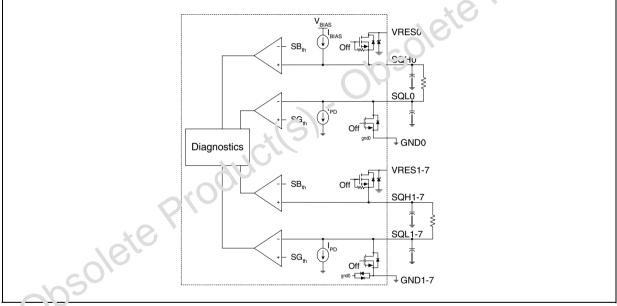

OSD is able to differentiate short to battery, open circuit, and short to ground. A resistance measurement provides the resistance value of a load connected between SQH and SQL. MOS diagnostic verifies the functionality of the high and low side MOS. Refer to Figure 14 for the diagnostic diagram. A detailed operation for each test is described in sections below.

Figure 14. Diagnostic Diagram

Figure 15. Diagnostic Flow Chart

# 4.10 Short Between Loops Diagnostic

OSD has a loop bias voltage that is multiplexed between the eight deployment loops. The bias voltage is pulled-up to VDIAG\_BIAS. Each deployment loop is pulled to ground through a current sink, IPD. If one of these loops is shorted to the one that is biased, a "Short Between Loops" fault bit is asserted and reported via SPI. Refer to Figure 16 for Short Between Loops diagram.

Short between loops test is initiated when OSD receives one of the following message:

- MOSI monitor mode message with bit D12 = '1,' bit D9 = '1,' and bit D8 = '1.'

- MOSI diagnostic mode message with bit D12 = '1' and bit D9 = '1.'

The test terminates when OSD receives one of the following message:

- MOSI monitor mode message with bit D12 = '1,' bit D9 = '1,' and bit D8 = '0'

- MOSI diagnostic mode message with bit D12 = '1' and bit D9 = '0.'

- MOSI command mode with bit D7 through bit D0 = '0.'

If the test is in progress, OSD will continue the test when any of the following messages is received.

- MOSI monitor mode, except the one with bit D12 = '1,' bit D9 = '1,' and bit D8 = '0'

- MOSI register mode

Figure 16. Short Between Loops Diagram

After a POR event, short between loop is disabled. Need to receive a SPI command to execute a short between loop diagnostic.

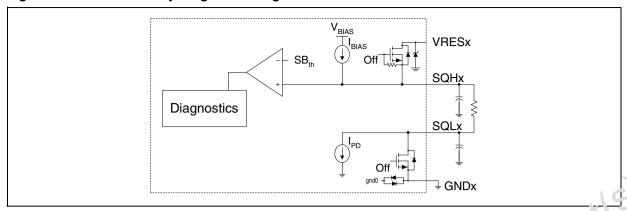

#### 4.11 Short to Battery Diagnostic

During a short to battery test, a current source referenced to VDD is connected to the SQHx. When no short to battery condition exists, SQHx and SQLx are equal to VDIAG\_BIAS. If the voltage on SQHx is above SBth for tFLT\_DLY, OSD will assert the short to battery fault. Refer to Figure 17 for a short to battery test diagram.

Figure 17. Short-to-Battery Diagnostic Diagram

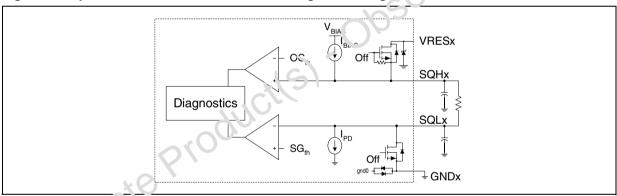

# 4.12 Open Circuit and Short to Ground Diagnostic

During an open circuit or a short to ground test, a current source referenced to  $V_{DIAG\_BIAS}$  is connected to the SQHx. When no open circuit or short to ground condition exists, SQHx and SQLx are equal to  $V_{DIAG\_BIAS}$ . An open circuit fault is detected when SQHx voltage is at  $V_{DIAG\_BIAS}$  and the SQLx voltage is at ground potential. A short to ground is detected when SQLx voltage is at ground potential and the SQHx voltage is below the open circuit threshold,  $OC_{th}$ .

Figure 18. Open Circuit and Short to Ground Diagnostic Diagram

The open circuit and short to ground conditions are summarized in the table below. A fault condition exists for at least term of the table below. A fault condition exists for at least term of the table below. A fault condition exists for at least term of the table below.

Tal le 9. Open Circuit / Short to Ground Fault Condition

| Comparator Output |    | Condition        |

|-------------------|----|------------------|

| ОС                | SG | Condition        |

| 0                 | 0  | Invalid State    |

| 0                 | 1  | Short to Ground  |

| 1                 | 0  | Normal operation |

| 1                 | 1  | Open Circuit     |

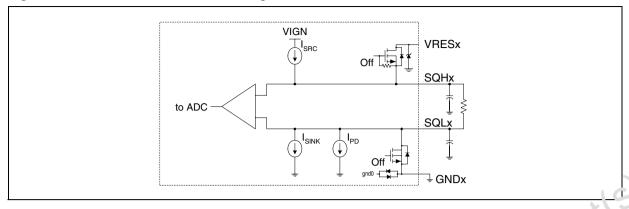

#### 4.13 Resistance Measurement

In a resistance measurement test, OSD provides a current source, ISRC, on SQHx and a current sink, ISINK, on SQLx. The 8-bit ADC is multiplexed between the deployment loops. This ADC converts the voltage across the SQHx and SQLx. The conversion results is stored for SPI retrieval. Figure 19 shows the resistance measurement diagram.

47/

Figure 19. Resistance Measurement Diagram

The ADC has a resolution of 8 bits and an accuracy of 5%. The ADC is robust to disruption that may occur due to adjacent loops short to 40V or -1V.

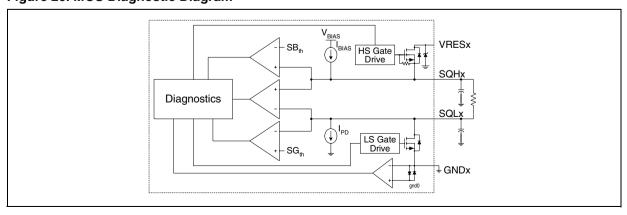

#### 4.14 MOS Diagnostic

During a MOS test, the  $I_{BIAS}$  current source referenced to  $V_{BIAS}$  is connected to the SQHx. In case of normal condition, SQHx and SQLx are equal to  $V_{BIAS}$ .

DEPEN pin is asserted in order to run a MOS diagnostic. If DEPEN pin is negated, OSD will inhibit the high/low side MOS from turning on. In this case, the MOS diagnostic is the minated after to expired and the respective MOS fault bit is set.

# 4.15 Low Side MOS Diagnostic

Upon detection of the following conditions, OSD turns the low side driver off and terminates the diagnostic within the specified time, tPROP\_DLY.

- V<sub>SQL</sub> is less than SGth threshold vcltage

- (V<sub>SQHx</sub> V<sub>SQLx</sub>) is greater than v<sub>1 111</sub>

- V<sub>SOH</sub> is greater than SR<sub>th</sub> threshold voltage

Any of the above conditions 2:e considered as a normal operation. Upon detection any of these conditions, OSD does not set the low side driver fault bits.

On a single channe, high-side and low-side MOS diagnostics is completed within t<sub>DETECT</sub>. A low-side MOS fault bit is only set when t<sub>DETECT</sub> is expired before any of the above conditions are detected. A fault detection filter, t<sub>LL\_DLY</sub>, is provided to protect against short-transients on SQH and SQL pins. See Figure 20 for NOS test diagram.

Figure 20. MOS Diagnostic Diagram

# 4.16 High Side MOS Diagnostic

Upon detection of the following conditions, OSD turns the high side driver off and terminate the diagnostic within the specified time, tprop DLY.

- V<sub>SQH</sub> is greater than SBth threshold voltage

- (V<sub>SQHx</sub> V<sub>SQLx</sub>) is greater than V<sub>I\_TH</sub>

- V<sub>SOI</sub> is less than SG<sub>th</sub> threshold voltage

Any of the above conditions are considered as a normal operation. Upon detection any of these conditions, OSD does not set the high side driver fault bits.

On a single channel, high-side and low-side MOS diagnostics are completed within t<sub>DETECT</sub>. A high-side MOS fault bit is only set when t<sub>DETECT</sub> is expired before any of the above conditions are detected. A fault detection filter, t<sub>FLT\_DLY</sub>, is provided to protect against short-transients on SQH and SQL pins. See Figure 20 for MOS test diagram.

#### 4.17 Loss of Ground Diagnostic

Loss of ground is detected when the power ground of a deployment loop has a high impedance/open connection to the ground. Each channel has a dedicated power ground and a dedicated loss of ground detection. Upon a detection of loss of ground condition, OSD inhibits a diagnostic and a deployment for the respective channel. The rest of the channels are not affected by a loss of ground condition on the other channels. A loss of ground condition does not affect a deployment or a pulse street timer that is already started.

A ground reference for OSD logic is connected to GND0 pin. When OSD catects a high impedance on this ground reference, OSD will go in reset mode.

# 4.18 Serial Peripheral Interface (SPI)

The OSD contains a serial peripheral interface consisting of Serial Clock (SCLK), Serial Data Out (MISO), Serial Data In (MOSI), and Chip Select (CS). This cevice is configured as an SPI slave.

Figure 21. SPI Block Diagram

#### 4.19 Chip Select (CS)

The CS input selects OSD for serial data transfers. This TTL-compatible input has an internal pull-down to command the de-asserted state should an open circuit condition occur When CS is asserted, the MISO pin is released from tri-state mode, and all status information is latched in the SPI shift register. While CS is asserted, register data is shifted in the MOSI pin and shifted out the MISO pin on each subsequent SCLK. When CS is negated, the MISO pin is tri-stated and the fault register reloaded (latched) with the current filtered status data.

To allow sufficient time to reload the fault registers; the CS pin must remain negated for at least  $t_{CSN}$ . CS must also be immune to spurious pulses as defined in the SPI Timing table (MISO may come out of tristate, but no status bits can be cleared and no control bits altered). Glitches on the CS line while SCLK is not running will be ignored, although the MISO pin may be enabled. In each valid CS, OSD allows 16-bit

SPI transfer. OSD ignores all SPI transfers, which are not a 16-bit transfer and issue a SPI fault response in the next valid CS.

#### 4.20 Serial Clock (SCLK)

The SCLK input is the clock signal input for synchronization of serial data transfer. This pin has TTL level compatible input voltages allowing proper operation with microprocessors using a 3.3 to 5.0 volt supply.

When CS is asserted, both the SPI master and this device latch input data on the rising edge of SCLK. The SPI master typically shifts data out on the falling edge of SCLK, as does this device.

# 4.21 Serial Data Output (MISO)

The MISO output pin is in a tri-state condition when CS is negated. When CS is asserted, the MSB is the first bit of the word transmitted on MISO and the LSB is the last bit of the word transmitted on MISO. This pin supplies a "rail to rail" output, so if interfaced to a microprocessor that is using a lower VDD supply, the appropriate microprocessor input pin shall not sink more than IOH and shall not clamp the MISC voltage to less than  $V_{OH(min)}$  while the MISO pin is in a logic "1" state.

## 4.22 Serial Data Input (MOSI)

The MOSI input takes data from the master microprocessor while CS is asserted. The MCS is the first bit of each word received on MOSI and the LSB is the last bit of each word received on MOSI. This pin has TTL level compatible input voltages allowing proper operation with micro-processors using a 3.3 to 5.0 volt supply.

#### 4.23 SPI Transmission

The SPI provides access to read/write to the registers internal to OSD. OSD responses to various commands summarized in the below table. OSD response to the previous command is sent in the next valid CS.

Table 10. OSD SPI Response

| Mode | Bits | MOSI Command           | Mode | Bits | MISO Pooponos      |

|------|------|------------------------|------|------|--------------------|

| D15  | D14  | MOSICOIIIIIana         | D15  | D14  | MISO Response      |

| 0    | 0    | Register Noc 3         | 0    | 0    | Register Mode      |

| 0    | 1    | Command Mode           | 0    | 1    | Command Mode       |

| 1    | 0    | D. agnostic Mode       | 1    | 1    | Status Response    |

| 1    | 1    | Monitor Mode           | 1    | 1    | Status Response    |

| Х    | Х    | SPI Transmission Fault | 1    | 0    | SPI Fault Response |

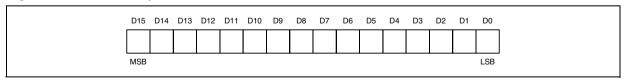

### 4.24 SYI 3:t Definition - MOSI Bit

Figure 22. MOSI Bit Layout

**Table 11. MOSI Mode Bits Definition**

| Bit D15 | Bit D14 | Description     |

|---------|---------|-----------------|

| 0       | 0       | Register Mode   |

| 0       | 1       | Command Mode    |

| 1       | 0       | Diagnostic Mode |

| 1       | 1       | Monitor Mode    |

# 4.25 Register Mode

Register mode message is defined as shown in table below.

**Table 12. MOSI Register Mode Message Definition**

| Bit | State | Description                  |

|-----|-------|------------------------------|

| D15 | 0     | Mode Bits                    |

| D14 | 0     |                              |

| D13 | 0     | Read Configuration Register  |

|     | 1     | Write Configuration Register |

| D12 |       | Address-bit                  |

| D11 |       |                              |

| D10 |       | */3                          |

| D9  |       | GV.                          |

| D8  |       |                              |

| D7  |       | Data-bit Data-bit            |

| D6  |       |                              |

| D5  |       | <i>LC</i> .                  |

| D4  |       |                              |

| D3  |       |                              |

| D2  |       | obsolete                     |

| D1  |       |                              |

| D0  |       |                              |

When bit D13 is set to '1,' OSD writes the data-bit to its internal register. The address bit designates a specific register in OSD. This address-bit is designed as shown below.

When the ADC resistance measurement is addressed, OSD ignores the data-bit. Upon the detection of this ADC resistance measurement on the address-bit, OSD sends the 8-bit resistance measurement value in the register mode response.

A write request contains valid and bits, bit D13 set to '1,' valid address bits and valid data bits. In the next valid CS, a register mode response contains the valid register content and not the echo from previous command.

A read request contains valid mode bits, bit D13 set to '0,' and valid address bits. The data bits will be ignored by the O3D. In the next valid CS, a register mode response contains a valid register content. This register is performined by the address bits sent in the previous command.

**Table 13. Address-bit Definition**

| Bit D12 | Bit D11 | Bit D10 | Bit D9 | Bit D8 | Description                             |

|---------|---------|---------|--------|--------|-----------------------------------------|

| RES     | ADC     | DIAG    | AD1    | AD0    | Program Other Options                   |

| 0       | 0       | 0       | 0      | 0      | STATUS.FLT Configuration Register       |

| 0       | 0       | 0       | 0      | 1      | Deployment Configuration 1 Register     |

| 0       | 0       | 0       | 1      | 0      | Deployment Configuration 2 Register     |

| 0       | 0       | 0       | 1      | 1      | Soft Reset                              |

| RES     | ADC     | DIAG    | AD1    | AD0    | Diagnostic Fault Registers              |

| 0       | 0       | 1       | 0      | 0      | Channel 0 and 1 Register (see table 18) |

| 0       | 0       | 1       | 0      | 1      | Channel 2 and 3 Register, Table 19      |

| 0       | 0       | 1       | 1      | 0      | Channel 4 and 5 Register (see table 20) |

47/

Table 13. Address-bit Definition (continued)

| Bit D12 | Bit D11 | Bit D10 | Bit D9 | Bit D8 | Description                          |

|---------|---------|---------|--------|--------|--------------------------------------|

| 0       | 0       | 1       | 1      | 1      | Channel 6 and 7 Register, Table 21   |

| RES     | ADC     | AD2     | AD1    | AD0    | ADC Resistance Measurement Result    |

| 0       | 1       | 0       | 0      | 0      | 8-bit ADC Measurement Register: Ch 0 |

| 0       | 1       | 0       | 0      | 1      | 8-bit ADC Measurement Register: Ch 1 |

| 0       | 1       | 0       | 1      | 0      | 8-bit ADC Measurement Register: Ch 2 |

| 0       | 1       | 0       | 1      | 1      | 8-bit ADC Measurement Register: Ch 3 |

| 0       | 1       | 1       | 0      | 0      | 8-bit ADC Measurement Register: Ch 4 |

| 0       | 1       | 1       | 0      | 1      | 8-bit ADC Measurement Register: Ch 5 |

| 0       | 1       | 1       | 1      | 0      | 8-bit ADC Measurement Register: Ch 6 |

| 0       | 1       | 1       | 1      | 1      | 8-bit ADC Measurement Register: Ch 7 |

# 4.26 STATUS.FLT Configuration Register

STATUS.FLT register is defined as shown in the below table. The setting of these registers will influence the diagnostic fault indication flag in the status response. If any of these bits set to '1,' OSD inhibits the faults of the respective channels from affecting bit D13 (diagnostic fault flag) in 'ne MISO Status Response. This STATUS.FLT configuration register does not affect the operation of diagnostic fault registers.

**Table 14. STATUS.FLT Configuration Register**

| Bit        | Status | C escription                               |

|------------|--------|--------------------------------------------|

| D7         | 0      | Enable Fault Report on Channel 7 (default) |

|            | 1      | Disable Fault Report ca Channel 7          |

| D6         | 0      | Enable Fault Report on Channel 6 (default) |

|            | 1      | Disable Fault איסיר on Channel 6           |

| D5         | 0      | Enable Fault Deport on Channel 5 (default) |

|            | 1      | Disable Fault Report on Channel 5          |

| D4         | 0      | cnable Fault Report on Channel 4 (default) |

|            | 10,    | Disable Fault Report on Channel 4          |

| D3         | 100    | Enable Fault Report on Channel 3 (default) |

|            | 1      | Disable Fault Report on Channel 3          |

| D.S        | 0      | Enable Fault Report on Channel 2 (default) |

| <u>U</u> A | 1      | Disable Fault Report on Channel 2          |

| 1ن         | 0      | Enable Fault Report on Channel 1 (default) |

|            | 1      | Disable Fault Report on Channel 1          |

| D0         | 0      | Enable Fault Report on Channel 0 (default) |

|            | 1      | Disable Fault Report on Channel 0          |

# 4.27 Deployment Configuration Register 1

The deployment configuration register 1 is defined as shown in the next table. During a deployment event, a write request to this register is inhibited.

**Table 15. Deployment Configuration Register 1**

| Bit | Status | Description                           |

|-----|--------|---------------------------------------|

| D7  |        | Pulse Stretch timer (see table)       |

| D6  |        |                                       |

| D5  | 0      | ARM Parallel Mode (default)           |

|     | 1      | ARM Serial Mode                       |

| D4  | -      | Don't Care                            |

| D3  | 0      | ARM67 Pulse Stretch Disable (default) |

|     | 1      | ARM67 Pulse Stretch Enable            |

| D2  | 0      | ARM45 Pulse Stretch Disable (default) |

|     | 1      | ARM45 Pulse Stretch Enable            |

| D1  | 0      | ARM23 Pulse Stretch Disable (default) |

|     | 1      | ARM23 Pulse Stretch Enable            |

| D0  | 0      | ARM01 Pulse Stretch Disable (default) |

|     | 1      | ARM01 Pulse Stretch Enable            |

Bit D3 through bit D0 is used to inhibit the ARMx signal from initiating the pulse stretch timer. When these bits are "0," ARMx signal is prohibited from initiating the timer. Otherwise, a valid ARMx signal starts the timer. If the timer has already initiated by the SPI deployment command, the ARMx signal does not affect the timer.

Bit D7 and bit D6 is used to set the period of pulse stretch timer. OSD has 8 independent timers for each channel. Either a valid ARMx or a SPI deployment command is capable to start the pulse stretch timer. These bits set the timer duration according to caple. These values are default to %00 after battery connect.

Table 16. Pulse Stretch Timer

| Bit D7  | Bit D6 | Stretch Period (ms) |

|---------|--------|---------------------|

| 0       | 0      | 7.5                 |

| 0       | 1      | 15                  |

| <u></u> | 0      | 30                  |

|         | 1      | 60                  |

# 4.28 Deployment Configuration Register 2

The second deployment configuration register contains bits to configure the deployment period and the deployment current for each loop. During a deployment event, a write request to this register is inhibited. The register is defined as shown in herebelow table.

**Table 17. Deployment Configuration Register 2**

| Bit | Status | Description                                   |

|-----|--------|-----------------------------------------------|

| D7  | 0      | Channel 6/7 2ms Deployment Period (default)   |

|     | 1      | Channel 6/7 4ms Deployment Period             |

| D6  | 0      | Channel 6/7 1.2A Deployment Current (default) |

|     | 1      | Channel 6/7 1.75A Deployment Current          |

| D5  | 0      | Channel 4/5 2ms Deployment Period (default)   |

|     | 1      | Channel 4/5 4ms Deployment Period             |

| D4  | 0      | Channel 4/5 1.2A Deployment Current (default) |

|     | 1      | Channel 4/5 1.75A Deployment Current          |

| D3  | 0      | Channel 2/3 2ms Deployment Period (default)   |

|     | 1      | Channel 2/3 4ms Deployment Period             |

| D2  | 0      | Channel 2/3 1.2A Deployment Current (default) |

|     | 1      | Channel 2/3 1.75A Deployment Current          |

| D1  | 0      | Channel 0/1 2ms Deployment Period (default,   |

|     | 1      | Channel 0/1 4ms Deployment Period             |

| D0  | 0      | Channel 0/1 1.2A Deployment Current (default) |

|     | 1      | Channel 0/1 1.75A Deployment Current          |

#### 4.29 Soft Reset

The soft reset in OSD is achieved by viriting \$AA and \$55 within two subsequent 16-bit SPI transmissions. If the sequence is broken, the processor will be required to re-transmit the sequence. OSD is not in reset if the sequence is not completed viring two subsequent 16-bit SPI transmissions.

#### 4.30 Diagnostic Faul (:) egisters

These diagnostic fault registers contain the fault status for each of the channels. Each register is cleared immediately after a SPI reading on that particular register. The diagnostic fault registers is defined as shown here below:

Table 18. Diagnostic Fault Register: Channel 0 and 1

| Bit | State | Description                                                                      |  |

|-----|-------|----------------------------------------------------------------------------------|--|

| D7  | 0     | No Fault: Channel 1                                                              |  |

|     | 1     | Fault Exists: Channel 1                                                          |  |

| D6  |       | Channel 1                                                                        |  |

| D5  |       | Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22           |  |

| D4  |       | Trefer to Diagnostic Fault-bit Definition table 22                               |  |

| D3  | 0     | No Fault: Channel 0                                                              |  |

|     | 1     | Fault Exists: Channel 0                                                          |  |

| D2  |       | Channel 0 Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22 |  |

Table 19. Diagnostic Fault Register: Channel 2 and 3

| Bit | State | Description                                                                      |   |

|-----|-------|----------------------------------------------------------------------------------|---|

| D7  | 0     | No Fault: Channel 3                                                              |   |

|     | 1     | Fault Exists: Channel 3                                                          |   |

| D6  |       | Channel 3                                                                        |   |

| D5  |       | Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22           |   |

| D4  |       | Trefer to Diagnostic Fault-bit Definition table 22                               |   |

| D3  | 0     | No Fault: Channel 2                                                              |   |

|     | 1     | Fault Exists: Channel 2                                                          |   |

| D2  |       | Channel 2 Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22 | 0 |

Table 20. Diagnostic Fault Register: Channel 4 and 5

| Bit | State | Description                                                                      |

|-----|-------|----------------------------------------------------------------------------------|

| D7  | 0     | No Fault: Channel 5                                                              |

|     | 1     | Fault Exists: Channel 5                                                          |

| D6  |       | Channel 5                                                                        |

| D5  |       | ☐ Diagnostic Fault-bit<br>☐ Refer to Diagnostic Fault-bit Definition tab'e ?2    |

| D4  |       | Helef to Diagnostic Fault-bit Definition tal e 72                                |

| D3  | 0     | No Fault: Channel 4                                                              |

|     | 1     | Fault Exists: Channel 4                                                          |

| D2  |       | Channel 4 Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22 |

Table 21. Diagnostic Fault Register. Channel 2 and 3

| Bit | State | Description                                                                      |

|-----|-------|----------------------------------------------------------------------------------|

| D7  | 0     | No Fault: Channel 7                                                              |

|     | *6    | Fault Exists: Channel 7                                                          |

| D6  | 10    | Channel 7                                                                        |

| D5  |       | Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22           |

| [74 |       | There to Diagnostic Fault-bit Definition table 22                                |

| 6.1 | 0     | No Fault: Channel 6                                                              |

|     | 1     | Fault Exists: Channel 6                                                          |

| D2  |       | Channel 6 Diagnostic Fault-bit Refer to Diagnostic Fault-bit Definition table 22 |

Diagnostic fault bit indicates short between loops, short to battery, open circuit, short to ground, high or low side MOS fault. The channel number is determined by the address bit in register mode command. These faults are decoded as shown in Diagnostic Fault-bit Definition table. Bit D7 and bit D3 indicate if a fault condition exists in the respective channels. Loss of ground fault has the highest priority among all fault conditions.

**A**7/

Table 22. Diagnostic Fault-bit Definition

| D6/D2 | D5/D1 | D4/D0 | Description          |

|-------|-------|-------|----------------------|

| 0     | 0     | 0     | No Fault             |

| 0     | 0     | 1     | Short Between Loops  |

| 0     | 1     | 0     | Short to Battery     |

| 0     | 1     | 1     | Open Fault           |

| 1     | 0     | 0     | Short to Ground      |

| 1     | 0     | 1     | Low Side MOS Fault   |

| 1     | 1     | 0     | High Side MOS Fault  |

| 1     | 1     | 1     | Loss of Ground Fault |

# 4.31 Resistance Measurement Registers

OSD has 8 independent resistance measurement registers. The resistance measurement registers is defined as shown in the table.

**Table 23. ADC Resistance Measurement Register**

| Bit | Description                             |

|-----|-----------------------------------------|

| D7  |                                         |

| D6  |                                         |

| D5  | - WS                                    |

| D4  | 8-bit ADC Resistance Measurement Result |

| D3  | o-bit ADC nesistance Measurement nesuit |

| D2  |                                         |

| D1  | *(2)                                    |

| D0  |                                         |

ADC resistance measurement registers contain the measurement results of each of the OSD deployment channels. The channel number is determined by the address bit in diagnostic command (see Address bit definition table 13)

#### 4.32 Command Mode

Command Mode message is defined as shown in next table.

**Table 24. MOSI Command Mode Message Definition**

| Bit | State | Description       |

|-----|-------|-------------------|

| D15 | 0     | Mode Bits         |

| D14 | 1     |                   |

| D13 |       | Odd Parity        |

| D12 | -     | Don't Care        |

| D11 | -     | Don't Care        |

| D10 | -     | Don't Care        |

| D9  | -     | Don't Care        |

| D8  | -     | Don't Care        |

| D7  | 0     | Channel 7 Idle    |

|     | 1     | Deploy Channel 7  |

| D6  | 0     | Channel 6 Idle    |

|     | 1     | Deploy Channel 6  |

| D5  | 0     | Channel 5 Idle    |

|     | 1     | Deploy Channel 5  |

| D4  | 0     | Channel 4 Idle    |

|     | 1     | Deploy Channel 4  |

| D3  | 0     | Channel 3 Idle    |

|     | 1     | Deploy Channel 3  |

| D2  | 0     | Channel 2 Idle    |

|     | 1     | Deploy Cha irie 2 |

| D1  | 0     | Chanr. 9, 1 Idle  |

|     | 1     | Dapley Channel 1  |

| D0  | 0     | Channel 0 Idle    |

|     | 1     | Deploy Channel 0  |

Odd parity check includes all 16 bits. "Don't care" bit is included in the parity check as well.

Bit D7 to bit D ) is used to start the deployment or the pulse stretch timer. OSD provides an independent timer for each channel. When any of these bits are set to '1,' OSD starts the deployment of the pulse stretch timer for the respective channels. If any of these bits are set to '0' when the pulse stretch timer is still active, OSD terminates the pulse stretch timer for the respective channels. Once deployment is initiated it will not be terminated. During the deployment, OSD will ignore all commands.

When DEPEN is negated, OSD ignores the deploy command. In other words, OSD will not initiate the pulse stretch timer or a deployment in this condition. However, when the pulse stretcher is already started by a deploy command, DEPEN will not terminate the pulse stretch timer. Upon receiving an idle command, OSD will terminates the pulse stretch timer regardless of DEPEN signal. In this case, only a pulse stretch timer that is started by a deploy command that can be terminated by sending an idle command.

# 4.33 Diagnostic Mode

Diagnostic Mode message is defined as shown in table.

**Table 25. MOSI Diagnostic Mode Message Definition**

| Bit      | State | Description                      |

|----------|-------|----------------------------------|

| D15      | 1     | Mode Bits                        |

| D14      | 0     |                                  |

| D13      |       | Odd Parity                       |

| D12      | 0     | Read Status Response Only        |

|          | 1     | Run On-chip Diagnostic           |

| D11      | -     | Don't Care                       |

| D10      | -     | Don't Care                       |

| D9       | 0     | Short Between Loops Test Disable |

|          | 1     | Short Between Loops Test Enable  |

| D8       | 0     | MOS Test Disable                 |

|          | 1     | MOS Test Enable                  |

| D7       | 0     | Disable Channel 7 Diagnostic     |

|          | 1     | Enable Channel 7 Diagnostic      |

| D6       | 0     | Disable Channel 6 Diagnostic     |

|          | 1     | Enable Channel 6 Diagnostic      |

| D5       | 0     | Disable Channel 5 Diagnostic     |

|          | 1     | Enable Channel 5 Diagnostic      |

| D4       | 0     | Disable Channel 4 Diaุnostic     |

|          | 1     | Enable Channel 4 Dia gnostic     |

| D3       | 0     | Disable Channe' 3 Diagnostic     |

|          | 1     | Enable Channel 3 Diagnostic      |

| D2       | 0     | Discuse Channel 2 Diagnostic     |

|          | 1     | Enable Channel 2 Diagnostic      |

| D1       | 0     | Disable Channel 1 Diagnostic     |

|          | 70    | Enable Channel 1 Diagnostic      |

| D0       | 0     | Disable Channel 0 Diagnostic     |

| <u> </u> | 1     | Enable Channel 0 Diagnostic      |

Odr party check includes all 16 bits. "Don't care" bit is included in the parity check as well.

When oit D12 is set to '1,' OSD starts its internal diagnostics on any channels selected in bit D7 through bit D0. When any of bit D7 through bit D0 are set to '1,' OSD performs diagnostics on the respective channels. The diagnostic sequence is shown in Figure 10. When bit D12 is set to '0,' OSD ignores bit D9 through bit D0.

Bit D9 and bit D8 are utilized to control the short between loops and MOS tests. If any of these bits are set to '1,' OSD performs the respective tests to any channels as selected in bit D7 thorugh bit D0. OSD executes these tests based on the diagnostic flow chart, shown in Figure 15.

# 4.34 Monitor Mode

Monitor Mode message is defined as shown in below:

**Table 26. MOSI Monitor Mode Message Definition**

| Bit | State | Description                            |

|-----|-------|----------------------------------------|

| D15 | 1     | Mode Bits                              |

| D14 | 1     |                                        |

| D13 |       | Odd Parity                             |

| D12 | 0     | Read Status Response Only              |

|     | 1     | Write Commands                         |

| D11 | -     | Don't Care                             |

| D10 | -     | Don't Care                             |

| D9  | 0     | Do not modify Short Between Loops Test |

|     | 1     | Modify Short Between Loops Test        |

| D8  | 0     | Disable Short Between Loops Test       |

|     | 1     | Enable Short Between Loops Test        |

| D7  | 0     | Keep Deploy Success Flag Channel 7     |

|     | 1     | Clear Deploy Success Flag Channel 7    |

| D6  | 0     | Keep Deploy Success Flag Channel 6     |

|     | 1     | Clear Deploy Success Flag Channel 6    |

| D5  | 0     | Keep Deploy Success Flag C'ıanı'e 5    |

|     | 1     | Clear Deploy Success Flag Channel 5    |

| D4  | 0     | Keep Deploy Success Flag Channel 4     |

|     | 1     | Clear Deploy Su :ccss F ag Channel 4   |

| D3  | 0     | Keep Deploy Success Flag Channel 3     |

|     | 1     | Clear Deoley Success Flag Channel 3    |

| D2  | 0     | Kອະກ Deploy Success Flag Channel 2     |

|     | 1     | Clear Deploy Success Flag Channel 2    |

| D1  | 0     | Keep Deploy Success Flag Channel 1     |

|     | 10    | Clear Deploy Success Flag Channel 1    |

| D0  | 0     | Keep Deploy Success Flag Channel 0     |

|     | 1     | Clear Deploy Success Flag Channel 0    |

Odr party check includes all 16 bits. "Don't care" bit is included in the parity check as well.

When pit D12 is set to a '0,' OSD ignores all command bits, specified in bit D9 to bit D0.

The monitor mode message is allowed to start or to stop the short between loops test. To start the test, both bit D9 and bit D8 has to be set to '1.' To stop the test, bit D9 is set to '1' and bit D8 is set to '0.' If bit D9 is set to '0,' OSD ignores the state of bit D8. In this condition, OSD does not affect the test. If bit D12 is set to '0,' OSD ignores bit D9 and bit D8.

Bit D7 through bit D0 is used to clear/keep the deploy success flag. When these bits are set to '1,' the flag is cleared. Otherwise, OSD does not affect the state of these flags.

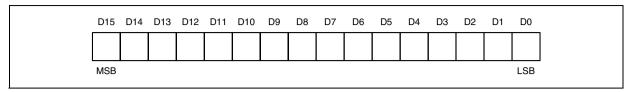

#### 4.35 MISO Bit Definition

# Figure 23. MISO Bit Layout

**Table 27. MISO Mode Bits Definition**

| Bit D15 | Bit D14 | Description            |

|---------|---------|------------------------|

| 0       | 0       | Register Mode Response |

| 0       | 1       | Command Mode Response  |

| 1       | 0       | SPI Fault Response     |

| 1       | 1       | Status Response        |

## 4.36 Register Mode Response

**Table 28. MISO Register Mode Response Definition**

| 1             | 1     | Status Response                                            |                |  |

|---------------|-------|------------------------------------------------------------|----------------|--|

| Register Mode | -     | nse<br>efined as shown in table.<br>de Response Definition | solete Proc    |  |

| Bit           | State |                                                            | . De: cription |  |

| D15           | 0     | Mode Bits                                                  | J.,            |  |

| D14           | 0     | _ /                                                        |                |  |

| D13           |       | Echo of MOSI Read/Mri'e Bit                                |                |  |

| D12           |       | Address Bits                                               |                |  |

| D11           |       | Refer to Arcress-bit Definition table                      |                |  |

| D10           |       | 00.0                                                       |                |  |

| D9            | 0     | <u>K</u> O                                                 |                |  |

| D8            |       |                                                            |                |  |

| D7            | 46    | Data Bits                                                  |                |  |

| D6            | 78,   |                                                            |                |  |

| D5            | ) `   |                                                            |                |  |

| _09           |       |                                                            |                |  |

| Г3            |       |                                                            |                |  |

| D2            |       |                                                            |                |  |

| D1            |       |                                                            |                |  |

| D0            |       |                                                            |                |  |

Bit D13 is used to reflect the status of MOSI Read/Write bit (refer to bit D13 in "MOSI Register Mode Message Definition table").

Bit D7 through bit D0 contain data bits. These data bits contain either diagnostic fault register or ADC resistance measurement register depending upon the MOSI request. Both register are defined as shown in "Diagnostic Fault Register Channel 0 and 1 table" and "ADC Resistance Measurement Register table".

# 4.37 Command Mode Response

Command Mode Response defined as shown below.