### **Optical Microcontroller**

### **General Description**

The DS4830 provides a complete optical control, calibration, and monitor solution based on a low-power, 16-bit, microcontroller core, providing program and RAM data memory. I/O resources include a fast/accurate analog-to-digital converter (ADC), fast comparators with an internal comparison digital-to-analog converter (DAC), 12-bit DACs, 12-bit PWMs, internal and external temperature sensors, fast sample/hold, I<sup>2</sup>C slave host interface, and a multiprotocol serial master/slave interface.

Direct connection of diode-connected transistors, used as remote temperature sensors, is supported as well as expansion to additional external digital temperature sensor ICs using the on-chip master I<sup>2</sup>C interface. An independent slave I<sup>2</sup>C interface facilitates communication to a host microprocessor in addition to password-protected in-system reprogramming of the on-chip flash.

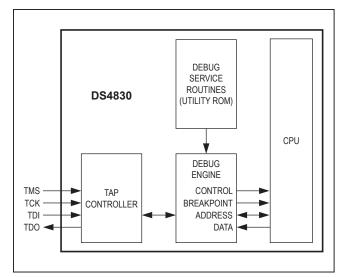

Firmware development is supported by third-party highly versatile C-compilers and development software that programs flash and performs in-circuit debug through the integrated JTAG interface and associated hardware.

### **Applications**

- PON Diplexers and Triplexers: GPON, 10GEPON, XPON OLT, ONU

- Optical Transceivers: XFP, SFP, SFP+, QSFP, 40G, 100G

Ordering Information appears at end of data sheet.

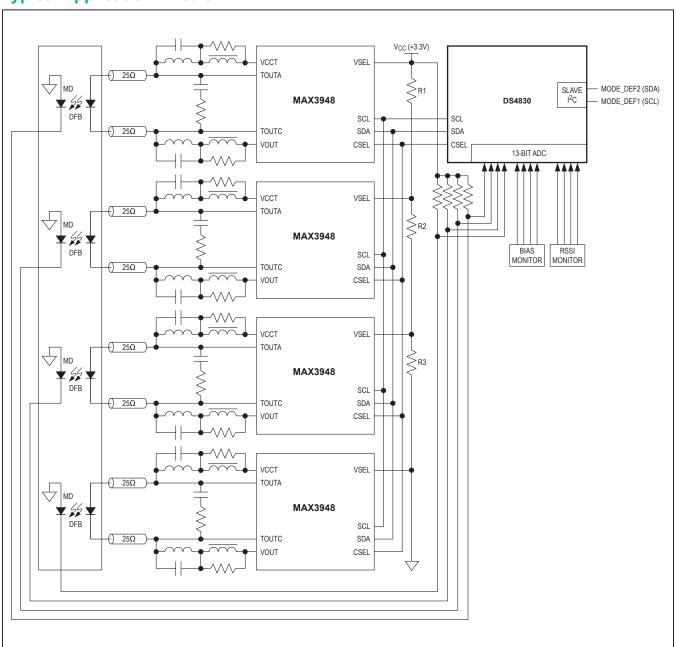

Typical Application Circuit appears at end of data sheet.

#### **Features**

- 16-Bit Low-Power Microcontroller

- 36 kWords Total Program Memory

- · 32 kWords Flash Program Memory

- · 4 kWords ROM Program Memory

- 1 kWords Data RAM

- 8 DAC Channels

- · 12-Bit Buffered Voltage DACs

- · Internal or External Reference

- 10 PWM Channels

- Boost/Buck DC-DC Control with Support for 7-Bit to 12-Bit Resolution and 1MHz Switching Frequency

- Supports 4-Channel TECC H-Bridge Control

- 8-Bit Fast Comparator with 16-Input Mux

- 1.6µs per Comparison

- 13-Bit A/D Converter with 26-Input Mux (27ksps)

- Temperature Measurement Analog Front-End

- Internal Temperature Sensor, ±3°C

- 0.0625°C Resolution

- · Supports Two External Temperature Sensors

- · Differential Rail-Rail Inputs

- 31 GPIO Pins

- Maskable Interrupt Sources

- Internal 20MHz Oscillator, CPU Core Frequency 10MHz

- 4% Accurate from 0°C to +50°C

- Up to 133MHz External Clock for PWM and Timers

- Slave Communication Interface: SPI or 400kHz I<sup>2</sup>C-Compatible 2-Wire

- Master Communication Interface: SPI, 400kHz I<sup>2</sup>C-Compatible, or Maxim 3-Wire Laser Driver

- I<sup>2</sup>C and JTAG Bootloader

- Two 16-Bit Timers

- 2.97V to 3.63V Operating Voltage Range

- Brownout Monitor

- JTAG Port with In-System Debug and Programming

- Low Power Consumption (16mA) with All Analog Active

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, go to: www.maximintegrated.com/errata.

### **Absolute Maximum Ratings**

| V <sub>DD</sub> to GND0.3V to +3.97V                     | Continuous Source Current 20mA per pin, 50mA total |

|----------------------------------------------------------|----------------------------------------------------|

| SCL, SDA, RST0.3V to +3.63V                              | Operating Temperature Range40°C to +85°C           |

| All Other Pins to GND                                    | Storage Temperature Range55°C to +125°C            |

| except REG18 and REG2850.3V to (V <sub>DD</sub> + 0.5V)* | Lead Temperature (soldering, 10s)+300°C            |

| Continuous Sink Current 20mA per pin, 50mA total         | Soldering Temperature (reflow)+260°C               |

<sup>\*</sup>Subject to not exceeding +3.97V.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

#### 40TQFN

| Package Code        | T4055+2        |

|---------------------|----------------|

| Outline Number      | <u>21-0140</u> |

| Land Pattern Number | 90-0016        |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

### **Recommended Operating Conditions**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER                         | SYMBOL          | CONDITIONS | MIN                   | TYP MAX               | UNITS |

|-----------------------------------|-----------------|------------|-----------------------|-----------------------|-------|

| V <sub>DD</sub> Operating Voltage | V <sub>DD</sub> | (Note 1)   | 2.97                  | 3.63                  | V     |

| Input Logic-High                  | V <sub>IH</sub> |            | 0.7 x V <sub>DD</sub> | V <sub>DD</sub> + 0.3 | V     |

| Input Logic-Low                   | V <sub>IL</sub> |            | -0.3                  | 0.3 x V <sub>DD</sub> | V     |

### **DC Electrical Characteristics**

$(V_{DD}$  = 2.97V to 3.63V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{DD}$  = 3.3V,  $T_A$  = +25°C.)

| PARAMETER                       | SYMBOL                   | CONDITIONS                                 | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|--------------------------|--------------------------------------------|------|------|------|-------|

|                                 | I <sub>CPU</sub>         | CPU mode, all analog disabled (Notes 2, 3) |      | 4.8  |      |       |

| Command Command                 | I <sub>FASTCOMP</sub>    |                                            |      | 2    |      |       |

| Supply Current                  | I <sub>SAMPLEHOLDS</sub> | Both sample/hold                           |      | 1.5  |      | mA    |

|                                 | I <sub>ADC</sub>         |                                            |      | 2.8  |      |       |

|                                 | I <sub>DACS</sub>        | Per channel (Note 4)                       |      | 0.6  |      |       |

| Brownout Voltage                | V <sub>BO</sub>          | Monitors V <sub>DD</sub> (Note 1)          |      | 2.7  |      | V     |

| Brownout Hysteresis             | V <sub>BOH</sub>         | Monitors V <sub>DD</sub> (Note 1)          |      | 0.07 |      | V     |

| 1.8V Regulator Initial Voltage  | V <sub>REG18</sub>       | (Note 1)                                   | 1.71 | 1.8  | 1.89 | V     |

| 2.85V Regulator Initial Voltage | V <sub>REG285</sub>      | (Note 1)                                   | 2.8  | 2.85 | 2.9  | V     |

### **DC Electrical Characteristics (continued)**

$(V_{DD}$  = 2.97V to 3.63V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{DD}$  = 3.3V,  $T_A$  = +25°C.)

| PARAMETER                                                                                          | SYMBOL                          | CONDITIONS                                    | MIN                   | TYP                      | MAX                   | UNITS |

|----------------------------------------------------------------------------------------------------|---------------------------------|-----------------------------------------------|-----------------------|--------------------------|-----------------------|-------|

| Clock Frequencies                                                                                  | f <sub>OSC-</sub><br>PERIPHERAL | T <sub>A</sub> = +25°C (Note 5)               |                       | 20                       |                       | MHz   |

|                                                                                                    | fmosc-core                      | $T_A = +25^{\circ}C \text{ (Note 5)}$         |                       | 10                       |                       |       |

| Clock Error                                                                                        | f <sub>ERR</sub>                | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ |                       |                          | ±8                    | %     |

| External Clock Input                                                                               | f <sub>XCLK</sub>               |                                               | 20                    |                          | 133                   | MHz   |

| Voltage Range: GP[15:0],<br>SHEN, DACPW[7:0], REFINA,<br>REFINB                                    | V <sub>RANGE</sub>              | (Note 1)                                      | -0.3                  |                          | V <sub>DD</sub> + 0.3 | V     |

| Output Logic-Low: SCL, SDA,<br>MDIO, MDI, MCL, MCS,<br>REFINA, REFINB, All GPIO<br>Pins            | V <sub>OL1</sub>                | I <sub>OL</sub> = 4mA (Note 1)                |                       |                          | 0.4                   | V     |

| Output Logic-High: SDA, MDIO,<br>MDI, MCL, MCS, REFINA,<br>REFINB, All GPIO Pins Not<br>Open Drain | V <sub>OH1</sub>                | I <sub>OH</sub> = -4mA (Note 1)               | V <sub>DD</sub> - 0.5 |                          |                       | V     |

| Pullup Current: MDIO, MDI,<br>MCL, MCS, All GPIO Pins                                              | I <sub>PU1</sub>                | V <sub>PIN</sub> = 0V                         | 26                    | 55                       | 78                    | μА    |

| GPIO Drive Strength, Extra<br>Strong Outputs: GP0, GP1,                                            | R <sub>HISt</sub>               |                                               |                       | 9                        | 27.6                  | Ω     |

| MCS, PW8, PW9                                                                                      | R <sub>LOSt</sub>               |                                               |                       | 8                        | 25.2                  |       |

| GPIO Drive Strength, Strong<br>Outputs: MDI, DACPW3,                                               | R <sub>HIA</sub>                |                                               |                       | 17                       | 32.4                  | Ω     |

| DACPW6                                                                                             | R <sub>LOA</sub>                |                                               |                       | 12                       | 26.4                  | 22    |

| GPIO Drive Strength, Excluding                                                                     | R <sub>HIB</sub>                |                                               |                       | 27                       | 57                    | Ω     |

| Strong GPIO Outputs                                                                                | R <sub>LOB</sub>                |                                               |                       | 31                       | 63                    |       |

| DAC                                                                                                |                                 |                                               |                       |                          |                       | •     |

| DAC Resolution                                                                                     | DAC <sub>R</sub>                |                                               | 12                    |                          |                       | Bits  |

| DAC Internal Reference<br>Accuracy                                                                 | DACREFACC                       | 2.5V internal reference                       | -1.25                 |                          | +1.25                 | %     |

| DAC Internal Reference Power-<br>Up Speed                                                          | tDACPUP                         | 99% settled                                   |                       | 10                       |                       | μs    |

| Reference Input Full-Scale<br>Range (REFINA, REFINB)                                               | REFFS                           |                                               | 1                     |                          | 2.5                   | V     |

| DAC Operating Current                                                                              | I <sub>DACS</sub>               | Per channel                                   |                       | he DC Ele<br>haracterist |                       |       |

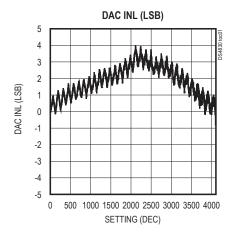

| DAC Integral Nonlinearity                                                                          | DACINL                          | 12-bit at 2.5V reference                      |                       | 12                       |                       | LSB   |

|                                                                                                    |                                 |                                               |                       |                          |                       |       |

DC Electrical Characteristics (continued)  $(V_{DD} = 2.97V \text{ to } 3.63V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = 3.3V, T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                       | SYMBOL                   | CONDITIONS                                                                                      | MIN   | TYP        | MAX   | UNITS |

|-------------------------------------------------|--------------------------|-------------------------------------------------------------------------------------------------|-------|------------|-------|-------|

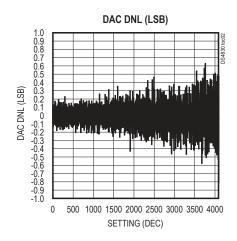

| DAC Differential Nonlinearity                   | DACDNL                   | 12-bit at 2.5V reference, guaranteed by design, not production tested                           |       |            | 1     | LSB   |

| DAC Offset                                      | V <sub>OFFSET-DAC</sub>  | At code "0"                                                                                     | 0     |            | 18    | mV    |

| DAC Source Load Regulation                      | I <sub>DAC-SOURCE</sub>  | 0 to full-scale output                                                                          |       |            | 8.6   | mV/mA |

| DAC Sink Capability and Sink<br>Load Regulation | R <sub>DAC-SINK</sub>    | 0 to 0.5V output, limited by output buffer impedance                                            |       | 500        |       | Ω     |

| Load Negulation                                 | I <sub>DAC-SINK</sub>    | 0.5V to full-scale output                                                                       |       |            | 11.5  | mV/mA |

| DAC Settling Time                               | t <sub>DAC</sub>         | Output load capacitance between 33pF and 270pF, from 10% to 90%                                 |       | 10         |       | μs    |

| FAST COMPARATOR/QUICK T                         | RIPS                     |                                                                                                 |       |            |       |       |

| Fast Comparator Resolution                      | FC <sub>R</sub>          |                                                                                                 | 8     |            |       | Bits  |

| Fast Comparator Internal<br>Reference Accuracy  | FCREFACC                 |                                                                                                 | -1.25 |            | +1.25 | %     |

| Fast Comparator Operating Current               | IFASTCOMP                |                                                                                                 |       | the DC Ele |       |       |

| Fast Comparator Full Scale                      | V <sub>FS-COMP</sub>     |                                                                                                 | 2.38  | 2.42       | 2.48  | V     |

| Fast Comparator Integral Nonlinearity           | INL                      | Differential mode, 2.2nF capacitor at input, tested at worst-case positions                     |       |            | ±2    | LSB   |

| Fast Comparator Differential Nonlinearity       | DNL                      | Differential mode, 2.2nF capacitor at input, guaranteed by design                               |       |            | 1     | LSB   |

| Fast Comparator Offset                          | V <sub>OFFSET-COMP</sub> |                                                                                                 |       |            | 2     | LSB   |

| Fast Comparator Input<br>Resistance             | R <sub>IN-COMP</sub>     | (Note 6)                                                                                        |       | 15         |       | ΜΩ    |

| Fast Comparator Input<br>Capacitance            | C <sub>IN-COMP</sub>     |                                                                                                 |       | 4          |       | pF    |

| Fast Comparator Sample Rate                     | f <sub>COMP</sub>        |                                                                                                 |       | 625        |       | ksps  |

| ADC                                             |                          |                                                                                                 |       |            |       |       |

| ADC Resolution                                  | ADC <sub>R</sub>         | Default or slow ADC clock setting                                                               | 13    |            |       | Bits  |

| ADC Internal Reference<br>Accuracy              | ADCREFACC                |                                                                                                 | -0.85 |            | +0.85 | %     |

| ADC Operating Current                           | I <sub>ADC</sub>         |                                                                                                 |       | the DC Ele |       |       |

| ADC Full-Scale 1                                | V <sub>FS-ADC1</sub>     |                                                                                                 |       | 1.2        |       | V     |

| ADC Full-Scale 2                                | V <sub>FS-ADC2</sub>     |                                                                                                 |       | 0.6        |       | V     |

| ADC Full-Scale 3                                | V <sub>FS-ADC3</sub>     |                                                                                                 |       | 2.4        |       | V     |

| ADC Full-Scale 4                                | V <sub>FS-ADC4</sub>     |                                                                                                 |       | 4.8        |       | V     |

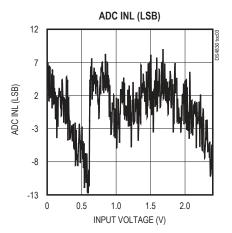

| ADC Integral Nonlinearity                       | ADCINL                   | Computed using end points best fit: 13-bit, +25°C, V <sub>DD</sub> = 3.3V, V <sub>FS-ADC3</sub> |       | 10         |       | LSB   |

Maxim Integrated | 4 www.maximintegrated.com

DC Electrical Characteristics (continued)  $(V_{DD} = 2.97V \text{ to } 3.63V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = 3.3V, T_A = +25^{\circ}\text{C}.)$

| PARAMETER                                                      | SYMBOL                  | CONDITIONS                                                                                    | MIN    | TYP   | MAX   | UNITS           |

|----------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------|--------|-------|-------|-----------------|

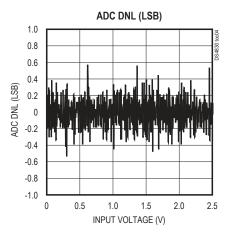

| ADC Differential Nonlinearity                                  | ADCDNL                  | V <sub>FS</sub> = 1.2V                                                                        |        | ±0.5  |       | LSB             |

| ADC Sample-Sample Deviation                                    |                         | ADC full-scale set to V <sub>FS-ADC3</sub>                                                    |        | 5     |       | LSB             |

| ADC Offset                                                     | V <sub>OFFSET-ADC</sub> | 13-bit, V <sub>FS</sub> = 1.2V                                                                | -8     | +1    | +8    | LSB             |

| GP[15:0] Input Resistance                                      | R <sub>IN-ADC</sub>     |                                                                                               |        | 15    |       | ΜΩ              |

| ADC Sample Rate                                                | f <sub>SAMPLE</sub>     | (Note 7)                                                                                      | 8      |       |       | ksps            |

| ADC Temperature Conversion Time                                | t <sub>TEMP</sub>       |                                                                                               |        | 4.2   |       | ms              |

| Internal Temperature<br>Measurement Error                      | TINTERR                 | (Note 8)                                                                                      |        | ±2    |       | °C              |

| Remote Temperature<br>Measurement Error<br>(DS4830 Error Only) | TREM <sub>ERR</sub>     | (Note 8)                                                                                      |        | ±2    |       | °C              |

| SAMPLE/HOLD                                                    |                         |                                                                                               |        |       |       |                 |

| Sample/Hold Input Range                                        | V <sub>SHP</sub>        | ADC-SHN[1:0] = GND                                                                            | 0      |       | 1     | V               |

| Sample/Hold Capacitance                                        | C <sub>SH</sub>         | ADC-SHP[1:0] to ADC-SHN[1:0]                                                                  |        | 5     |       | pF              |

| Sample Input Leakage                                           | I <sub>SHLKG</sub>      | ADC-SHP[1:0] and ADC-SHN[1:0] connected to GND                                                |        |       | 1.2   | μA              |

| Sample Time                                                    | t <sub>S</sub>          | ADC-SHP[1:0] and ADC-SHN[1:0] connected to 50Ω voltage source                                 | 300    |       |       | ns              |

| Sample Conversion Complete                                     | t <sub>h</sub>          | Time from valid sample to ADC data available                                                  |        |       | 320   | μs              |

| Sample Offset                                                  | V <sub>SH-OFF</sub>     | Measured at 10mV                                                                              | -10    | -1.6  | +7    | mV              |

| Sample Error                                                   | ERR <sub>SH</sub>       | $V_{ADC-SHP}$ to $V_{ADC-SHN}$ = 300mV,<br>$t_{S}$ = 300ns, driven with 50Ω voltage<br>source | -4     |       | +4    | %               |

| Sample Discharge Strength                                      | R <sub>DIS</sub>        | ADC-SHP[1:0] or ADC-SHN[1:0] to<br>GND                                                        |        | 900   |       | Ω               |

| FLASH MEMORY                                                   |                         |                                                                                               |        |       |       |                 |

| E E T.                                                         | t <sub>ME</sub>         | Mass erase                                                                                    | 22.9   | 24.14 | 25.35 |                 |

| Flash Erase Time                                               | t <sub>PE</sub>         | Page erase                                                                                    | 22.9   | 24.14 | 25.35 | ms              |

| Flash Programming Time per<br>Word                             | t <sub>PROG</sub>       | (Note 9)                                                                                      | 69     | 74    | 79    | μs              |

| Flash Programming<br>Temperature                               | T <sub>FLASH</sub>      |                                                                                               | -40    |       | +85   | °C              |

| Flash Endurance                                                | n <sub>FLASH</sub>      | T <sub>A</sub> = +50°C, guaranteed by design                                                  | 20,000 |       |       | Write<br>Cycles |

| Data Retention                                                 | t <sub>RET</sub>        | T <sub>A</sub> = +50°C, guaranteed by design                                                  | 100    |       |       | Years           |

Maxim Integrated | 5 www.maximintegrated.com

### **AC Electrical Characteristics**

(V<sub>DD</sub> = 2.97V to 3.63V,  $T_A$  = -40°C to +85°C, unless otherwise noted.)

| PARAMETER                                                   | SYMBOL                | CONDITIONS                        | MIN                    | TYP  | MAX | UNITS |

|-------------------------------------------------------------|-----------------------|-----------------------------------|------------------------|------|-----|-------|

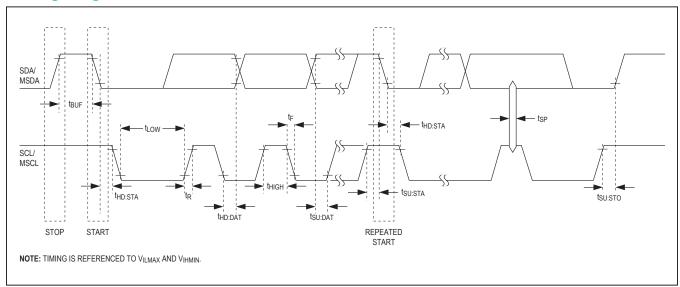

| I <sup>2</sup> C-COMPATIBLE INTERFACE (S                    | ee Figure 1)          |                                   |                        |      |     |       |

| SCL/MSCL Clock Frequency                                    | f <sub>SCL</sub>      | Timeout not enabled               |                        |      | 400 | kHz   |

| SCL Bootloader Clock Frequency                              | f <sub>SCL:BOOT</sub> |                                   |                        |      | 100 | kHz   |

| Bus Free Time Between a STOP and START Condition            | t <sub>BUF</sub>      |                                   | 1.3                    |      |     | μs    |

| Hold Time (Repeated)<br>START Condition                     | thd:STA               | (Note 10)                         | 0.6                    |      |     | μs    |

| Low Period of SCL/MSCL Clock                                | t <sub>LOW</sub>      |                                   | 1.3                    |      |     | μs    |

| High Period of SCL/MSCL Clock                               | tHIGH                 |                                   | 0.6                    |      |     | μs    |

| Setup Time for a (Repeated)<br>START Condition              | tsu:sta               |                                   | 0.6                    |      |     | μs    |

| Data Hold Time (Note 11)                                    | <b>+</b>              | Receive                           | 0                      |      |     | ne    |

| Data Hold Time (Note 11)                                    | thd:dat               | Transmit                          | 300                    |      |     | ns    |

| Data Setup Time                                             | tsu:dat               | (Note 12)                         | 100                    |      |     | ns    |

| SCL/MSCL, SDA/MSDA<br>Capacitive Loading                    | C <sub>B</sub>        | (Note 12)                         |                        |      | 400 | pF    |

| Rise Time of Both SDA and SCL Signals                       | t <sub>R</sub>        | (Note 12)                         | 20 + 0.1C <sub>B</sub> |      | 300 | ns    |

| Fall Time of Both SDA and SCL Signals                       | t <sub>F</sub>        | (Note 12)                         | 20 + 0.1C <sub>B</sub> |      | 300 | ns    |

| Setup Time for STOP Condition                               | t <sub>SU:STO</sub>   |                                   | 0.6                    |      |     | μs    |

| Spike Pulse Width That Can Be<br>Suppressed by Input Filter | t <sub>SP</sub>       | (Note 13)                         |                        | 50   |     | ns    |

| SCL/MSCL and SDA/MSDA Input Capacitance                     | C <sub>BIN</sub>      |                                   |                        | 5    |     | pF    |

| SMBus Timeout                                               | tsmbus                |                                   |                        | 30   |     | ms    |

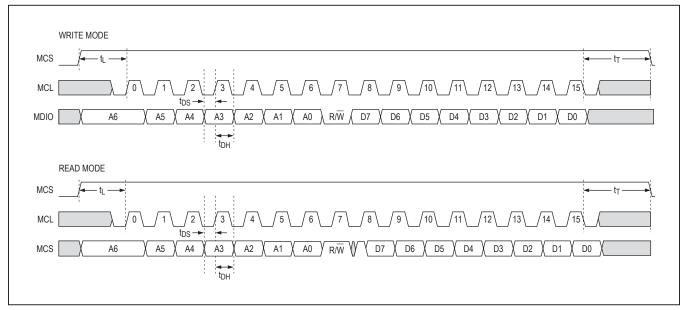

| 3-WIRE DIGITAL INTERFACE (Se                                | e Figure 2)           |                                   |                        |      |     |       |

| MCL Clock Frequency                                         | f <sub>SCLOUT</sub>   |                                   |                        | 1000 |     | kHz   |

| MCL Duty Cycle                                              | t <sub>3WDC</sub>     |                                   |                        | 50   |     | %     |

| MDIO Setup Time                                             | t <sub>DS</sub>       |                                   |                        | 100  |     | ns    |

| MDIO Hold Time                                              | t <sub>DH</sub>       |                                   |                        | 100  |     | ns    |

| MCS Pulse-Width Low                                         | t <sub>CSW</sub>      |                                   |                        | 500  |     | ns    |

| MCS Leading Time Before the First MCL Edge                  | t∟                    |                                   |                        | 500  |     | ns    |

| MCS Trailing Time After the Last MCL Edge                   | t <sub>T</sub>        |                                   |                        | 500  |     | ns    |

| MDIO, MCL Load                                              | C <sub>B3W</sub>      | Total bus capacitance on one line |                        | 10   |     | pF    |

# AC Electrical Characteristics (continued) $(V_{DD} = 2.97V \text{ to } 3.63V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                                                      | SYMBOL                  | CONDITIONS MIN TYP MAX                      | UNITS |

|----------------------------------------------------------------|-------------------------|---------------------------------------------|-------|

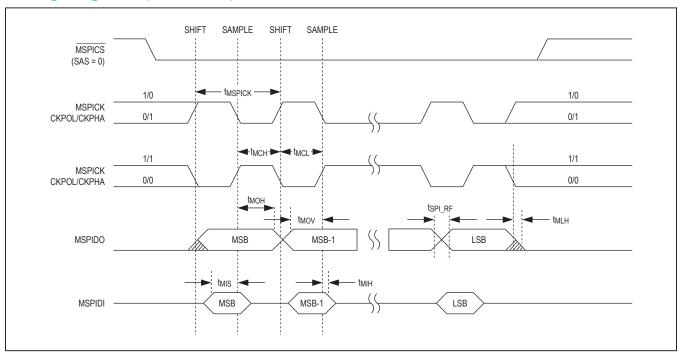

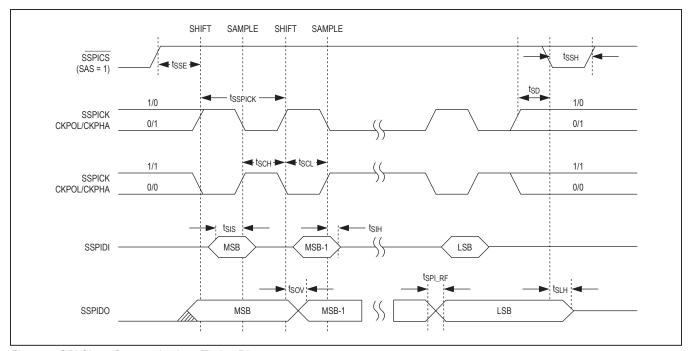

| SPI DIGITAL INTERFACE (See Fi                                  | gure 3 and Fig          | gure 4)                                     |       |

| SPI Master Operating Frequency                                 | 1/t <sub>MSPICK</sub>   | f <sub>SYS</sub> /2                         | MHz   |

| SPI Slave Operating Frequency                                  | 1/t <sub>SSPICK</sub>   | f <sub>SYS</sub> /4                         | MHz   |

| SPI I/O Rise/Fall Time                                         | t <sub>SPI_RF</sub>     | $C_L = 15pF$ , pullup = $560\Omega$         | ns    |

| MSPICK Output Pulse-Width High/Low                             | t <sub>MCH</sub> , tMCL | tMSPICK/2 - tSPI_<br>RF                     | ns    |

| MSPIDO Output Hold After<br>MSPICK Sample Edge                 | t <sub>мон</sub>        | tMSPICK/2 - tSPI_<br>RF                     | ns    |

| MSPIDO Output Valid to MSPICK<br>Sample Edge<br>(MSPIDO Setup) | t <sub>MOV</sub>        | tMSPICK/2 - tSPI_<br>RF                     | ns    |

| MSPIDI Input Valid to MSPICK<br>Sample Edge (MSPIDI Setup)     | t <sub>MIS</sub>        | 2t <sub>SPI_RF</sub>                        | ns    |

| MSPIDI Input to MSPICK<br>Sample Edge Rise/Fall Hold           | t <sub>MIH</sub>        | 0                                           | ns    |

| MSPICK Inactive to MSPIDO Inactive                             | t <sub>MLH</sub>        | tMSPICK/2 - tSPI_<br>RF                     | ns    |

| SSPICK Input Pulse-Width High/<br>Low                          | tsch, tscl              | tsspick/2                                   | ns    |

| SSPICS Active to First Shift Edge                              | t <sub>SSE</sub>        | t <sub>SPI_RF</sub>                         | ns    |

| SSPIDI Input to SSPICK Sample<br>Edge Rise/Fall Setup          | t <sub>SIS</sub>        | t <sub>SPI_RF</sub>                         | ns    |

| SSPIDI Input from SSPICK<br>Sample Edge Transition Hold        | tsiH                    | t <sub>SPI_RF</sub>                         | ns    |

| SSPIDO Output Valid After<br>SSPICK Shift Edge Transition      | tsov                    | 2t <sub>SPI_RF</sub>                        | ns    |

| SSPICS Inactive                                                | tssh                    | tsspick + tspi_rf                           | ns    |

| SSPICK Inactive to SSPICS Rising                               | t <sub>SD</sub>         | t <sub>SPI_RF</sub>                         | ns    |

| SSPIDO Output Disabled After SSPICS Edge Rise                  | t <sub>SLH</sub>        | 2t <sub>SSPICK</sub> + 2t <sub>SPI_RF</sub> | ns    |

Maxim Integrated | 7 www.maximintegrated.com

### **AC Electrical Characteristics (continued)**

$(V_{DD} = 2.97V \text{ to } 3.63V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$

| PARAMETER                             | SYMBOL            | CONDITIONS | MIN | TYP                | MAX | UNITS |

|---------------------------------------|-------------------|------------|-----|--------------------|-----|-------|

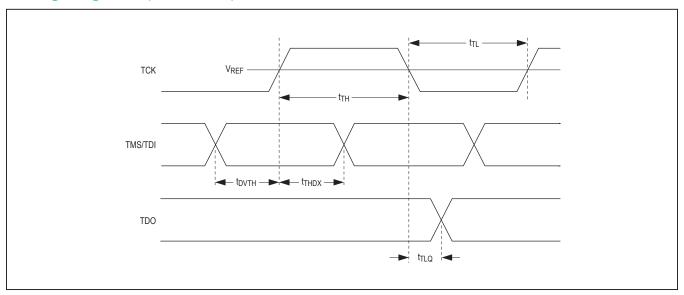

| JTAG DIGITAL INTERFACE (See           | Figure 5)         |            |     |                    |     |       |

| JTAG Logic Reference                  | V <sub>REF</sub>  |            |     | V <sub>DD</sub> /2 |     | V     |

| TCK High Time                         | t <sub>TH</sub>   |            |     | 0.5                |     | μs    |

| TCK Low Time                          | t <sub>TL</sub>   |            |     | 0.5                |     | μs    |

| TCK Low to TDO Output                 | t <sub>TLQ</sub>  |            |     | 0.125              |     | μs    |

| TMS, TDI Input Setup to TCK<br>High   | <sup>t</sup> DVTH |            |     | 0.25               |     | μs    |

| TMS, TDI Input Hold After TCK<br>High | t <sub>THDX</sub> |            |     | 0.25               |     | μs    |

- Note 1: All voltages are referenced to GND. Currents entering the IC are specified as positive, and currents exiting the IC are specified as negative.

- Note 2: Maximum current assuming 100% CPU duty cycle.

- This value does not include current in GPIO, SCL, SDA, MDIO, MDI, MCL, REFINA, and REFINB. Note 3:

- Note 4: Using internal reference.

- Note 5: There is one internal oscillator. The oscillator (peripheral clock) goes through a 2:1 divider to create the core clock.

- Note 6: Guaranteed by design.

- Note 7: ADC conversions are delayed up to 1.6µs if the fast comparator is sampling the selected ADC channel. This can cause a slight decrease in the ADC sampling rate.

- Note 8: Temperature readings average 64 times.

- Note 9: Programming time does not include overhead associated with the utility ROM interface.

- Note 10: f<sub>SCL</sub> must meet the minimum clock low time plus the rise/fall times.

- Note 11: This device internally provides a hold time of at least 75ns for the SDA signal (referred to the V<sub>IH:MIN</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- Note 12: C<sub>B</sub>—Total capacitance of one bus line in pF.

- Note 13: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

### **Timing Diagrams**

Figure 1. I<sup>2</sup>C Timing Diagram

Figure 2. 3-Wire Timing Diagram

### **Timing Diagrams (continued)**

Figure 3. SPI Master Communications Timing Diagram

Figure 4. SPI Slave Communications Timing Diagram

### **Timing Diagrams (continued)**

Figure 5. JTAG Timing Diagram

### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

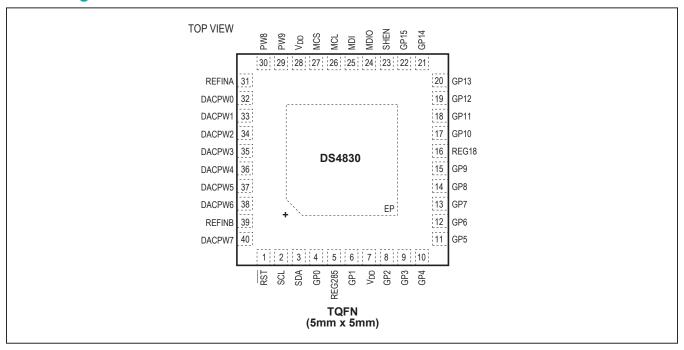

### **Pin Configuration**

### **Pin Description**

| PIN | NAME            | INPUT<br>STRUCTURE(S)     | OUTPUT<br>STRUCTURE        | POWER-ON<br>STATE | SELECTABLE FUNCTIONS (FIRST COLUMN IS DEFAULT FUNCTION) |                             |             | -         | PORT |

|-----|-----------------|---------------------------|----------------------------|-------------------|---------------------------------------------------------|-----------------------------|-------------|-----------|------|

| 1   | RST             | Digital                   | Open Drain                 | High<br>Impedance | RST                                                     | _                           | _           | _         | _    |

| 2   | SCL             | Digital                   | Open Drain                 | High<br>Impedance | I <sup>2</sup> C Slave<br>Clock SCL                     | SPI<br>SSPICK               | _           | _         | _    |

| 3   | SDA             | Digital                   | Open Drain                 | High<br>Impedance | I <sup>2</sup> C Slave<br>Data SDA                      | SPI<br>SSPIDI               | _           | _         |      |

| 4   | GP0             | ADC/Digital Input         | Push-Pull,<br>Extra Strong | 55µA Pullup       | ADC-S0                                                  | ADC-<br>D0P                 | PW0         | _         | P2.0 |

| 5   | REG285          | V <sub>REG</sub>          | None                       | 2.85V             | Only function 2.8                                       | on is for by<br>5V internal |             | citor for |      |

| 6   | GP1             | ADC/Digital Input         | Push-Pull,<br>Extra Strong | 55µA Pullup       | ADC-S1                                                  | ADC-<br>D0N                 | PW1         | _         | P2.1 |

| 7   | V <sub>DD</sub> | Voltage Supply, ADC Input | None                       | V <sub>DD</sub>   | ADC-VDD                                                 | _                           | _           | _         | _    |

| 8   | GP2             | SH Input, ADC Input       | None                       | High<br>Impedance | ADC-S2                                                  | ADC-<br>SHP0                | ADC-<br>D1P | _         | _    |

## **Pin Description (continued)**

| PIN | NAME  | INPUT<br>STRUCTURE(S)                                    | OUTPUT<br>STRUCTURE  | POWER-ON<br>STATE |                                         | SELECTABLE FUNCTIONS (FIRST COLUMN IS DEFAULT FUNCTION) |               |               | PORT |

|-----|-------|----------------------------------------------------------|----------------------|-------------------|-----------------------------------------|---------------------------------------------------------|---------------|---------------|------|

| 9   | GP3   | SH input, ADC Input                                      | None                 | High<br>Impedance | ADC-S3                                  | ADC-<br>SHN0                                            | ADC-<br>D1N   | _             | _    |

| 10  | GP4   | ADC/Digital Input                                        | Push-Pull            | 55μA Pullup       | JTAG TCK                                | ADC-S4                                                  | ADC-<br>D2P   | _             | P6.0 |

| 11  | GP5   | ADC/Digital Input                                        | Push-Pull            | 55µA Pullup       | JTAG TDI                                | ADC-S5                                                  | ADC-<br>D2N   | _             | P6.1 |

| 12  | GP6   | ADC/Digital Input                                        | Push-Pull            | 55µA Pullup       | ADC-S6                                  | ADC-<br>D3P                                             | PW2           | SPI<br>SSPIDO | P2.2 |

| 13  | GP7   | ADC/Digital Input                                        | Push-Pull            | 55µA Pullup       | ADC-S7                                  | ADC-<br>D3N                                             | PW3           | SPI<br>SSPICS | P2.3 |

| 14  | GP8   | ADC/Digital I/P,<br>External Temp A+ I/P<br>(ADC-TEXT_A) | Push-Pull            | 55μΑ Pullup       | ADC-S8                                  | ADC-<br>D4P                                             | _             | _             | P2.4 |

| 15  | GP9   | ADC/Digital I/P,<br>External Temp A- I/P<br>(ADC-TEXT_A) | Push-Pull            | 55μΑ Pullup       | ADC-S9                                  | ADC-<br>D4N                                             | _             | _             | P2.5 |

| 16  | REG18 | V <sub>REG</sub>                                         | None                 | 1.8V              | Pin for 1.8V regulator bypass capacitor |                                                         |               | _             |      |

| 17  | GP10  | ADC/Digital I/P,<br>External Temp A+ I/P<br>(ADC-TEXT_B) | Push-Pull            | 55μA Pullup       | JTAG TMS                                | ADC-<br>S10                                             | ADC-<br>D5P   | _             | P6.2 |

| 18  | GP11  | ADC/Digital I/P,<br>External Temp A+ I/P<br>(ADC-TEXT_B) | Push-Pull            | 55μΑ Pullup       | JTAG TDO                                | ADC-<br>S11                                             | ADC-<br>D5N   | _             | P6.3 |

| 19  | GP12  | SH Input, ADC/Digital Input                              | Push-Pull            | 55µA Pullup       | ADC-S12                                 | ADC-<br>SHP1                                            | ADC-<br>D6P   | _             | P0.0 |

| 20  | GP13  | SH Input, ADC/Digital Input                              | Push-Pull            | 55µA Pullup       | ADC-S13                                 | ADC-<br>SHN1                                            | ADC-<br>D6N   | _             | P0.1 |

| 21  | GP14  | ADC/Digital Input                                        | Push-Pull            | 55µA Pullup       | ADC-S14                                 | ADC-<br>D7P                                             | SHEN1         | _             | P0.2 |

| 22  | GP15  | ADC/Digital Input                                        | Push-Pull            | 55µA Pullup       | ADC-S15                                 | ADC-<br>D7N                                             | _             | _             | P0.3 |

| 23  | SHEN  | Digital                                                  | Push-Pull            | 55µA Pullup       | SHEN0                                   | _                                                       | _             | _             | P6.4 |

| 24  | MDIO  | Digital                                                  | Push-Pull            | 55µA Pullup       | 3-Wire Data<br>MDIO                     | I <sup>2</sup> C<br>MSDA                                | SPI<br>MSPIDO | PW4           | P1.0 |

| 25  | MDI   | Digital                                                  | Push-Pull,<br>Strong | 55μA Pullup       | _                                       | _                                                       | SPI<br>MSPIDI | PW5           | P1.3 |

| 26  | MCL   | Digital                                                  | Push-Pull            | 55μA Pullup       | 3-Wire Clock<br>MCL                     | I <sup>2</sup> C<br>MSCL                                | SPI<br>MSPICK | PW6           | P1.1 |

## **Pin Description (continued)**

| PIN | NAME     | INPUT<br>STRUCTURE(S)                      | OUTPUT<br>STRUCTURE        | POWER-ON<br>STATE | SELECTABLE FUNCTIONS (FIRST COLUMN IS DEFAULT FUNCTION) |     |               |     | PORT |

|-----|----------|--------------------------------------------|----------------------------|-------------------|---------------------------------------------------------|-----|---------------|-----|------|

| 27  | MCS      | Digital                                    | Push-Pull,<br>Extra Strong | 55μA Pullup       | 3-Wire Chip<br>Select MCS                               | _   | SPI<br>MSPICS | PW7 | P1.2 |

| 28  | $V_{DD}$ | Voltage Supply                             | None                       | $V_{DD}$          | ADC-VDD                                                 | _   | _             | _   | _    |

| 29  | PW9      | Digital                                    | Push-Pull,<br>Extra Strong | 55µA Pullup       | PW9                                                     | _   | _             | _   | P0.7 |

| 30  | PW8      | Digital                                    | Push-Pull,<br>Extra Strong | 55µA Pullup       | PW8                                                     | _   | _             | _   | P0.6 |

| 31  | REFINA   | Reference, ADC/Digital<br>Input (ADC_REFA) | Push-Pull                  | 55µA Pullup       | ADC-<br>REFINA                                          | _   | _             | _   | P2.6 |

| 32  | DACPW0   | Digital                                    | Push-Pull                  | 55μA Pullup       | DAC0, FS<br>= REFINA<br>or Internal<br>Reference        | PW0 | _             | _   | P0.4 |

| 33  | DACPW1   | Digital                                    | Push-Pull                  | 55μA Pullup       | DAC1, FS<br>= REFINA<br>or Internal<br>Reference        | PW1 | _             | _   | P0.5 |

| 34  | DACPW2   | Digital                                    | Push-Pull                  | 55μA Pullup       | DAC2, FS<br>= REFINA<br>or Internal<br>Reference        | PW2 | CLKIN         | _   | P6.5 |

| 35  | DACPW3   | Digital                                    | Push-Pull,<br>Strong       | 55μA Pullup       | DAC3, FS<br>= REFINA<br>or Internal<br>Reference        | PW3 | _             | _   | P1.5 |

| 36  | DACPW4   | Digital                                    | Push-Pull                  | 55μA Pullup       | DAC4, FS<br>= REFINB<br>or Internal<br>Reference        | PW4 | _             | _   | P1.6 |

| 37  | DACPW5   | Digital                                    | Push-Pull                  | 55μA Pullup       | DAC5, FS<br>= REFINB<br>or Internal<br>Reference        | PW5 | _             | _   | P1.7 |

| 38  | DACPW6   | Digital                                    | Push-Pull,<br>Strong       | 55μA Pullup       | DAC6, FS<br>= REFINB<br>or Internal<br>Reference        | PW6 | _             | _   | P6.6 |

| 39  | REFINB   | Reference, ADC/<br>Digital Input           | Push-Pull                  | 55μA Pullup       | ADC-<br>REFINB                                          | _   | _             | _   | P1.4 |

### **Pin Description (continued)**

| PIN | NAME   | INPUT<br>STRUCTURE(S)        | OUTPUT<br>STRUCTURE | POWER-ON<br>STATE | SELECTABLE FUNCTIONS (FIRST COLUMN IS DEFAULT FUNCTION) |     |   |   | PORT |

|-----|--------|------------------------------|---------------------|-------------------|---------------------------------------------------------|-----|---|---|------|

| 40  | DACPW7 | Digital                      | Push-Pull           | 55μA Pullup       | DAC7, FS<br>= REFINB<br>or Internal<br>Reference        | PW7 | _ | _ | P2.7 |

| _   | EP     | Exposed Pad (Connect to GND) | _                   | GND               | _                                                       | _   | _ | _ | _    |

**Note:** Bypass  $V_{DD}$ , REG285, and REG18 each with a 1µF X5R and 10nF capacitors to ground. All input-only pins and open-drain outputs are high impedance after  $V_{DD}$  exceeds  $V_{BO}$  and prior to code execution. Pins configured as GPIO have a weak internal pullup. See the <u>Selectable Functions</u> table for more information.

### **Selectable Functions**

| FUNCTION NAME                     | DESCRIPTION                                                                                                                                                                     |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADC-D[7:0][P/N]                   | Differential Inputs to ADC. Also used for external temperature sensors.                                                                                                         |

| ADC-REFIN[A/B]                    | REFINA and REFINB Monitor Inputs to ADC                                                                                                                                         |

| ADC-S[15:0]                       | Single-Ended Inputs to ADC                                                                                                                                                      |

| ADC-SH[P/N][1:0]                  | Sample/Hold Inputs 1 and 0                                                                                                                                                      |

| ADC-VDD                           | V <sub>DD</sub> Monitor Input to ADC                                                                                                                                            |

| DAC[7:0]                          | Voltage DAC Outputs                                                                                                                                                             |

| MCL, MCS, MDIO                    | Maxim Proprietary 3-Wire Interface, MCL (Clock), MCS (Chip Select), MDIO (Data). Used to control the MAX3798 family of high-speed laser drivers.                                |

| MSCL, MSDA                        | I <sup>2</sup> C Master Interface: MSCL (I <sup>2</sup> C Master Slave), MSDA (I <sup>2</sup> C Master Data)                                                                    |

| MSPICK, MSPICS, MSPIDI,<br>MSPIDO | SPI Master Interface: MSPICK (Clock), MSPICS (Active-Low Chip Select), MSPIDI (Data In), MSPIDO (Data Out)                                                                      |

| P0.n, P1.n, P2.n, P6.n            | General-Purpose Inputs/Outputs. Can also function as interrupts.                                                                                                                |

| PW[9:0]                           | PWM Outputs                                                                                                                                                                     |

| RST                               | Used by JTAG and as Active-Low Reset for Device                                                                                                                                 |

| SCL, SDA                          | I <sup>2</sup> C Slave Interface: SCL (I <sup>2</sup> C Slave Clock), SDA (I <sup>2</sup> C Slave Data). These also function as a password-protected programming interface.     |

| SHEN[1:0]                         | Sample/Hold Enable Inputs. Can also function as interrupts.                                                                                                                     |

| SSPICK, SSPICS, SSPIDI,<br>SSPIDO | SPI Slave Interface: SSPICK (Clock), SSPICS (Active-Low Chip Select), SSPIDI (Data In), SSPIDO (Data Out). In SPI slave mode, the I <sup>2</sup> C slave interface is disabled. |

| TCK, TDI, TDO, TMS                | JTAG Interface Pins. Also includes RST.                                                                                                                                         |

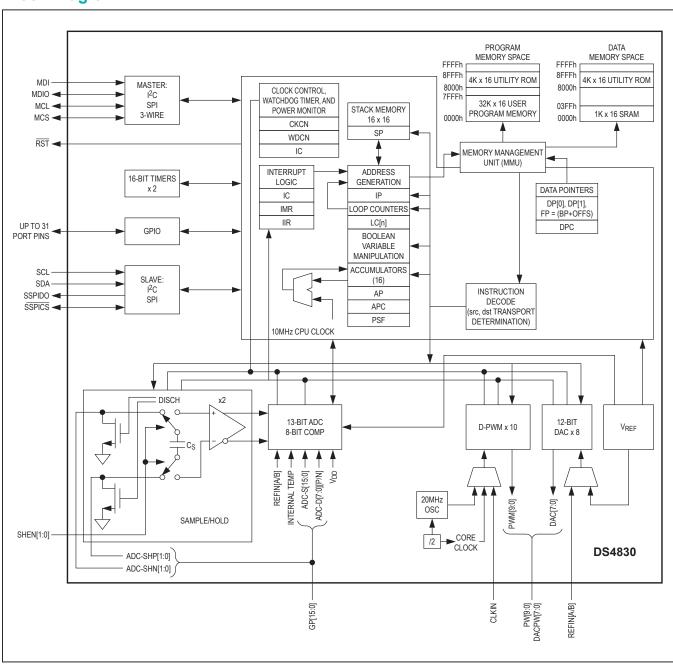

### **Block Diagram**

### **Detailed Description**

The following is an introduction to the primary features of the DS4830 optical microcontroller. More detailed descriptions of the device features can be found in the DS4830 User's Guide.

#### **Microcontroller Core Architecture**

The device employs a low-power, low-cost, high-performance, 16-bit RISC microcontroller with on-chip flash memory. It is structured on an advanced, 16 accumulator-based, 16-bit RISC architecture. Fetch and execution operations are completed in one cycle without pipelining, since the instruction contains both the op code and data. The highly efficient core is supported by 16 accumulators and a 16-level hardware stack, enabling fast subroutine calling and task switching. Data can be quickly and efficiently manipulated with three internal data pointers. Multiple data pointers allow more than one function to access data memory without having to save and restore data pointers each time. The data pointers can automatically increment or decrement following an operation, eliminating the need for software intervention.

#### **Module Information**

Top-level instruction decoding is extremely simple and based on transfers to and from registers. The registers are organized into functional modules, which are in turn divided into the system register and peripheral register groups.

Peripherals and other features are accessed through peripheral registers. These registers reside in modules 0 to 5. The following provides information about the specific module in which each peripheral resides:

- Module 0: Timer 1, GPIO Ports 0, 1, and 2

- Module 1: I<sup>2</sup>C Master, GPIO Port 6, SPI Slave, SVM

- Module 2: I<sup>2</sup>C Slave, Analog-to-Digital Converter (ADC), Sample/Hold, Temperature, 3-Wire Master

- Module 3: Timer 2, MAC-Related Registers

- Module 4: Digital-to-Analog Converter (DAC)

- Module 5: Quick Trips, SPI Master, PWM

#### **Instruction Set**

The instruction set is composed of fixed-length, 16-bit instructions that operate on registers and memory locations. The instruction set is highly orthogonal, allowing arithmetic and logical operations to use any register along with the accumulator. Special-function registers control the peripherals and are subdivided into register modules.

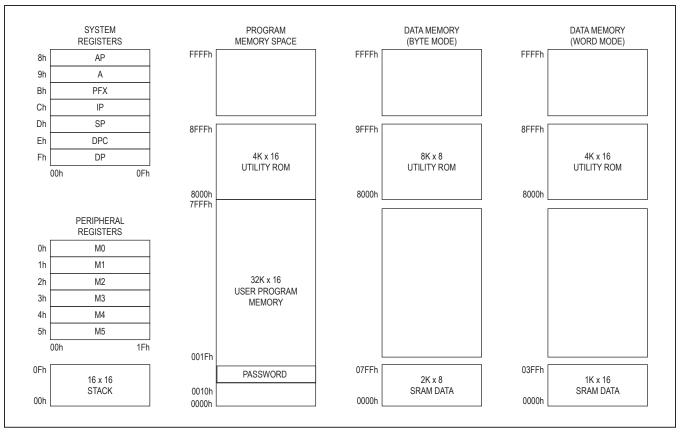

### **Memory Organization**

The device incorporates several memory areas:

- 32 kWords of flash memory for application program storage

- 1 kWords of SRAM for storage of temporary variables

- 4 kWords of utility ROM contain a debugger and program loader

- 16-level stack memory for storage of program return addresses and general-purpose use

The memory is implemented with separate address spaces for program memory, data memory, and register space. ROM, application code, and data memory can be placed into a single contiguous memory map. The device allows data memory to be mapped into program space, permitting code execution from data memory. In addition, program memory can be mapped into data space, permitting code constants to be accessed as data memory. Figure 6 shows the DS4830's memory map when executing from program memory space. Refer to the DS4830 User's Guide for memory map information when executing from data or ROM space.

The incorporation of flash memory allows field upgrade of the firmware. Flash memory can be password protected with a 16-word key, denying access to program memory by unauthorized individuals.

#### **Utility ROM**

The utility ROM is a 4 kWord block of internal ROM memory that defaults to a starting address of 8000h. The utility ROM consists of subroutines that can be called from application software, which includes the following:

- In-system programming (bootstrap loader) over JTAG or I<sup>2</sup>C-compatible interfaces

- In-circuit debug routines

- Internal self-test routines

- Callable routines for in-application flash programming

Following any reset, execution begins in the utility ROM. The ROM software determines whether the program execution should immediately jump to location 0000h, the start of application code, or to one of the special routines mentioned. Routines within the utility ROM are firmware-accessible and can be called as subroutines by the application software. More information on the utility ROM contents is contained in the DS4830 User's Guide.

Figure 6. Memory Map When Program is Executing from Flash Memory

#### **Password**

Some applications require protection against unauthorized viewing of program code memory. For these applications, access to in-system programming, in-application programming, or in-circuit debugging functions is prohibited until a password has been supplied. The password is defined as the 16 words of physical program memory at addresses 0010h–001Fh.

A single password lock (PWL) bit is implemented in the device. When the PWL is set to 1 (power-on-reset default) and the contents of the memory at addresses 0010h–001Fh are any value other than all FFh or 00h, the password is required to access the utility ROM, including in-circuit debug and in-system programming routines that allow reading or writing of internal memory. When PWL is cleared to 0, these utilities are fully accessible without the

password. The password is automatically set to all ones following a mass erase.

Detailed information regarding the password can be found in the  $\underline{\sf DS4830~User's~Guide}$ .

#### **Stack Memory**

A 16-bit, 16-level internal stack provides storage for program return addresses. The stack is used automatically by the processor when the CALL, RET, and RETI instructions are executed and interrupts serviced. The stack can also be used explicitly to store and retrieve data by using the PUSH, POP, and POPI instructions.

On reset, the stack pointer, SP, initializes to the top of the stack (0Fh). The CALL, PUSH, and interrupt-vectoring operations increment SP, then store a value at the location pointed to by SP. The RET, RETI, POP, and POPI operations retrieve the value at SP and then decrement SP.

### **Programming**

The microcontroller's flash memory can be programmed by one of two methods: in-system programming or in application programming. These provide great flexibility in system design as well as reduce the life-cycle cost of the embedded system. Programming can be password protected to prevent unauthorized access to code memory.

### **In-System Programming**

An internal bootstrap loader allows the device to be programmed over the JTAG or I<sup>2</sup>C compatible interfaces. As a result, system software can be upgraded in-system, eliminating the need for a costly hardware retrofit when software updates are required.

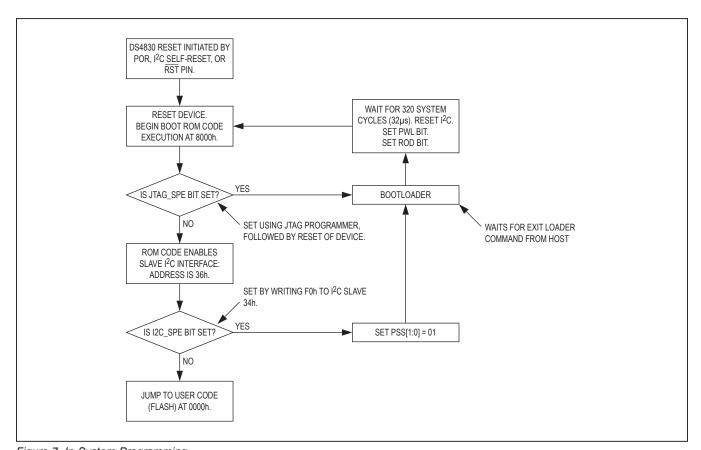

The programming source select (PSS) bits in the ICDF register determine which interface is used for boot load-

ing operation. The device supports JTAG and I<sup>2</sup>C as an interface corresponding to the 00 and 01 bits of PSS, respectively. See Figure 7.

### **In-Application Programming**

The in-application programming feature allows the microcontroller to modify its own flash program memory. This allows on-the-fly software updates in mission-critical applications that cannot afford downtime. Alternatively, it allows the application to develop custom loader software that can operate under the control of the application software. The utility ROM contains firmware-accessible flash programming functions that erase and program flash memory. These functions are described in detail in the DS4830 User's Guide.

Figure 7. In-System Programming

### **Register Set**

Sets of registers control most device functions. These registers provide a working space for memory operations as well as configuring and addressing peripheral registers on the device. Registers are divided into two major types: system registers (special-purpose registers, or SPRs) and peripheral registers (special-function registers, or SFRs). The common register set, also known as the system registers, includes the ALU, accumulator registers, data pointers, interrupt vectors and control, and stack pointer. The peripheral registers define additional functionality, and the functionality is broken up into discrete modules. Both the system registers and the peripheral registers are described in detail in the DS4830 User's Guide.

### **System Timing**

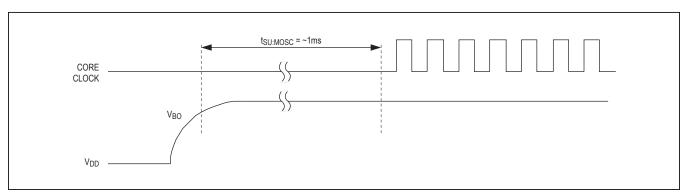

The device generates its 10MHz instruction clock (MOSC) internally. On power-up, the oscillator's output (which cannot be accessed externally) is disabled until  $V_{DD}$  rises above  $V_{BO}$ . Once this threshold is reached, the output is enabled after approximately 1ms, clocking the device. See Figure 8.

### **System Reset**

The device features several sources that can be used to reset the DS4830.

#### **Power-On Reset**

An internal power-on-reset (POR) circuit is used to enhance system reliability. This circuit forces the device to perform a POR whenever a rising voltage on  $V_{DD}$  climbs above  $V_{BO}$ . When this happens the following events occur:

- All registers and circuits enter their reset state.

- The POR flag (WDCN.7) is set to indicate the source of the reset.

- Code execution begins at location 8000h when the reset condition is released.

#### **Brownout Detect/Reset**

The device features a brownout detect/reset function. Whenever the power monitor detects a brownout condition (when  $V_{DD} < V_{BO}$ ), it immediately issues a reset and stays in that state as long as  $V_{DD}$  remains below  $V_{BO}$ . Once  $V_{DD}$  voltage rises above  $V_{BO}$ , the device waits for  $t_{SU:MOSC}$  before returning to normal operation, also referred to as CPU state. If a brownout occurs during  $t_{SU:MOSC}$ , the device again goes back to the brownout state. Otherwise, it enters into CPU state. In CPU state, the brownout detector is also enabled.

On power-up, the device always enters brownout state first and then follows the above sequence. The reset issued by brownout is the same as POR. Any action performed after POR also happens on brownout reset.

All the registers that are cleared on POR are also cleared on brownout reset.

Figure 8. System Timing

### **Watchdog Timer Reset**

The watchdog timer provides a mechanism to reset the processor in the case of undesirable code execution. The watchdog timer is a hardware timer designed to be periodically reset by the application software. If the software operates correctly, the timer is reset before it reaches its maximum count. However, if undesirable code execution prevents a reset of the watchdog timer, the timer reaches its maximum count and resets the processor.

The watchdog timer is controlled through two bits in the WDCN register (WDCN[5:4]: WD[1:0]). Its timeout period can be set to one of the four programmable intervals ranging from 2<sup>12</sup> to 2<sup>21</sup> system clock (MOSC) periods (0.409ms to 0.210s). The watchdog interrupt occurs at the end of this timeout period, which is 512 MOSC clock periods, or approximately 50µs, before the reset. The reset generated by the watchdog timer lasts for four system clock cycles, which is 0.4µs. Software can determine if a reset is caused by a watchdog timeout by checking the watchdog timer reset flag (WTRF) in the WDCN register. Execution resumes at location 8000h following a watchdog timer reset.

#### **External Reset**

Asserting RST low causes the device to enter the reset state. The external reset function is described in the DS4830 User's Guide. Execution resumes at location 8000h after RST is released. The DAC and PWM outputs are unchanged during execution of external reset.

### **Internal System Reset**

The host can issue an I<sup>2</sup>C command (BBh) to reset the communicating device. This reset has the same effect as the external reset as far as the reset values of all registers are concerned. Also, an internal system reset can occur when the in-system programming is done (ROD = 1). The DAC and PWM outputs are unchanged during execution of an internal reset.

Further details are available in the DS4830 User's Guide.

### **Programmable Timer**

The device features two general-purpose programmable timers. Various timing loops can be implemented using the timers. Each general-purpose timer uses three SFRs. GTCN is the general control register, GTV is the timer value register, and GTC is the timer compare register. The timer can be used in two modes: free-running mode and compare mode with interrupts. Both are described in detail in the DS4830 User's Guide.

The functionality of the timers can be accessed through three SFRs for each of the general-purpose timers. The timer SFRs are accessed in module 0 and module 3. Detailed information regarding the timer block can be found in the DS4830 User's Guide.

### **Hardware Multiplier**

The hardware multiplier (multiply-accumulate, or MAC module) is a very powerful tool, especially for applications that require heavy calculations. This multiplier can execute the multiply or multiply-negate, or multiply-accumulate or multiply-subtract operation for signed or unsigned operands. The MAC module uses eight SFRs, mapped as register 0h–05h and 08h–09h in module M3.

### **System Interrupts**

Multiple interrupt sources are available to respond to internal and external events. The microcontroller architecture uses a single interrupt vector (IV) and single interrupt-service routine (ISR) design. For maximum flexibility, interrupts can be enabled globally, individually, or by module. When an interrupt condition occurs, its individual flag is set, even if the interrupt source is disabled at the local, module, or global level. Interrupt flags must be cleared within the firmware-interrupt routine to avoid repeated interrupts from the same source. Application software must ensure a delay between the write to the flag and the RETI instruction to allow time for the interrupt hardware to remove the internal interrupt condition. Asynchronous interrupt flags require a one-instruction delay and synchronous interrupt flags require a two-instruction delay.

When an enabled interrupt is detected, execution jumps to a user-programmable interrupt vector location. The IV register defaults to 0000h on reset or power-up, so if it is not changed to a different address, application firmware must determine whether a jump to 0000h came from a RST or interrupt source.

Once control has been transferred to the ISR, the interrupt identification register (IIR) can be used to determine if a system register or peripheral register was the source of the interrupt. In addition to IIR, MIIR registers are implemented to indicate which particular function under a peripheral module has caused the interrupt. The device contains six peripheral modules, M0 to M5. An MIIR register is implemented in modules M1 and M2. The MIIRs are 16-bit read-only registers and all of them default to all zeros on system reset. Once the module that causes the interrupt is singled out, it can then be interrogated for the specific interrupt source and software can take

appropriate action. Interrupts are evaluated by application code allowing the definition of a unique interrupt priority scheme for each application. Interrupt sources are available from the watchdog timer, the ADC (including sample/holds), fast comparators, the programmable timer, SVM, the I<sup>2</sup>C-compatible master and slave interface, 3-wire, master and slave SPI, and all GPIO pins.

#### I/O Port

The device allows for most inputs and outputs to function as general-purpose input and/or output pins. There are four ports: P0, P1, P2, and P6. Note that there is no port corresponding to P6.7. The 7th bit of port 6 is non-functional in all SFRs. Each pin is multiplexed with at least one special function, such as interrupts, I/O pins, or JTAG pins, etc.

The GPIO pins have Schmitt trigger receivers and full CMOS output drivers and can support alternate functions. The ports can be accessed through SFRs (PO[0,1,2,6], PI[0,1,2,6], PD[0,1,2,6], EIE[0,1,2,6], EIF[0,1,2,6], and EIES[0,1,2,6]) in modules 0 and 1, and each pin can be individually configured. The pin is either high impedance or a weak pullup when defined as an input, dependent on the state of the corresponding bit in the output register. In addition, each pin can function as external interrupt with individual enable, flag and active edge selection, when programmed as input.

The I/O port SFRs are accessed in module 0 and 1. Detailed information regarding the GPIO block can be found in the <u>DS4830 User's Guide</u>.

#### **DAC Outputs**

The device provides eight 12-bit DAC outputs with multiple reference options. An internal 2.5V reference is provided. There are also two selectable external references. REFINA can be selected as the full-scale reference for DAC0 to DAC3. REFINB can be selected as the full-scale reference for DAC4 to DAC7. The DAC outputs are voltage buffered. Each DAC can be individually disabled and put into a low-power power-down mode using DACCFG. An external reset does not affect the DAC outputs.

If a DAC output is used during the lifetime of the DS4830, the DAC must always be enabled to guarantee meeting the INL and offset specifications. If a pin is used for a DAC, it should be used only for the DAC function. The pin's function should not be switched between DAC and PWM or switched between DAC and GPIO.

The DAC SFRs are accessed in module 4. Detailed information regarding the DAC block can be found in the DS4830 User's Guide.

### **PWM Outputs**

The device provides 10 independently configurable PWM outputs. The PWM outputs are configured using three SFRs: PWMCN, PWMDATA, and PWNSYNC. Using PWMCN and PWMDATA, individual PWM channels can be programmed for unique duty cycles (DCYCn), configurations (PWMCFGn), and delays (PWMDLYn), where n represents the PWM channel number.

The PWM clock can be obtained from the core clock, peripheral clock, or an external clock, depending on CLK\_SEL bits programmed in individual PWMCFGn registers. The PWMCFGn register also enables/disables the corresponding PWM output and selects the PWM polarity. The user can set the duty cycle and the frequency of each PWM output individually by configuring the corresponding DCYCn register and the PWMCFGn register.

The device allows 4-slot or 32-slot pulse spreading options for each PWM channel. The PWM outputs can be configured to be output on an alternate location using the configuration register. PWMDLY is a 12-bit register used for providing starting delay on different PWM channels, and can be used to create multiphase PWM operation.

Different channels can be synchronized using the PWMSYNC register. Doing so effectively brings the channels in phase by restarting the channels that are to be synchronized. An external reset does not affect the PWM outputs.

The PWM SFRs are accessed in module 5. Detailed information regarding the PWM block can be found in the DS4830 User's Guide.

# Analog-to-Digital Converter and Sample/Hold

The analog-to-digital converter (ADC) controller is the digital interface block between the CPU and the ADC. It provides all the necessary controls to the ADC and the CPU interface. The ADC uses a set of SFRs for configuring the ADC in desired mode of operation.

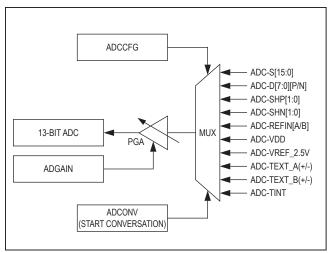

The device contains a 13-bit ADC with an input mux (<u>Figure 9</u>). The mux selects the ADC input from 16 single-ended or eight differential inputs. Additionally, the channels can be configured to convert internal and external temperature,  $V_{DD}$ , internal reference, or REFINA/B. Two channels can be programmed to be sample/hold inputs. The internal channel is used exclusively to measure the die temperature. The SFR registers control the ADC.

#### **ADC**

When used in voltage input mode, the voltage applied on the corresponding channel (differential or single-ended) is converted to a digital readout. The ADC can be set up to continuously poll selected input channels (continuous-sequence mode) or run a short burst of conversions and enter a shutdown mode to conserve power (singlesequence mode).

In voltage mode there are four full-scale values that can be programmed. These values can be trimmed by modifying the associated gain registers (ADCG1, ADCG2, ADCG3, ADCG4). By default these are set to 1.2V, 0.6V, 2.4V, and 4.8V full scale.

Figure 9. ADC Block Diagram

The ADCCLK is derived from the system clock with division ratio defined by the ADC control register. An A/D conversion takes 15 ADCCLK cycles to complete with additional four core clocks used for data processing. Internally every channel is converted twice and the average of two conversions is written to the data buffer. This gives each conversion result in (30 x ADC Clock Period + 800ns). ADC sampling rate is approximately 40ksps for the fastest ADC clock (core clock/8). In applications where extending the acquisition time is desired, the sample can be acquired over a prolonged period determined by the ADC control register.

Each ADC channel can have its own configuration, such as differential mode select, data alignment select, acquisition extension enable, and ADC gain select, etc. The ADC also has 24 (0 to 23) 16-bit data buffers for conversion result storage. The ADC data available interrupt flag (ADDAI) can be configured to trigger an interrupt following a predetermined number of samples. Once set, ADDAI can be cleared by software or at the start of a conversion process.

### Sample/Hold

Pin combinations GP2-GP3 and GP12-GP13 can be used for sample/hold conversions if enabled in the SHCN register. These two can be independently enabled or disabled by writing a 1 or 0 to their corresponding bit locations in SHCN register. A data buffer location is reserved for each channel. When a particular channel is enabled, a sample of the input voltage is taken when a signal is issued on the SHEN pin, converted and stored in the corresponding data buffer.

The two sample/hold channels can sample simultaneously on the same SHEN signal or different SHEN signals depending on the SH DUAL bit in the SHCN SFR.

The sample/hold data available interrupt flag (SHnDAI) can be configured to trigger an interrupt following sample completion. Once set, SHnDAI can be cleared by software.

Each sample/hold circuit consists of a sampling capacitor, charge injection nulling switches, and a buffer. Also included is a discharge circuit used to discharge parasitic capacitance on the input node and the sample capacitor before sampling begins. The negative input pins can be used to reduce ground offsets and noise.

#### **Temperature Measurement**

The device provides an internal temperature sensor for die temperature monitoring and two external remote temperature-sensing channels. In external temperature mode, current is forced into an external diode that is connected between user-specified channel pins (GP8-GP9 or GP10-GP11). The diode temperature is obtained by measuring the diode voltages at multiple bias currents.

These temperature channels can be enabled independently by setting the appropriate bit locations in the TEMPCN register. Whenever a temperature conversion is complete, the corresponding flag (INTDAI for internal conversion, EX0DAI and EX1DAI for external conversion) is set. These can be configured to cause an interrupt, and can be cleared by software. The temperature measurement resolution is 0.0625°C.

The device can use all the three modes explained above simultaneously by using a time-slicing mechanism performed by the internal controller. The ADC-related SFRs are accessed in module 1 and module 2. For details about this and the three blocks, refer to the ADC section of the DS4830 User's Guide.

### **Fast Comparator/Quick Trips**

The device supports 8-bit quick-trip comparison functionality. The quick trips are required to continuously monitor user-defined channels in a round-robin sequence.

The quick- trip controller allows the user control of the list of channels to monitor. Each mode has a corresponding choice of list of channels for the round robin.

In any mode of quick-trip operation, the quick trip (analog) performs two comparisons on any selected channel.

- 1) Comparison with a high-threshold value.

- 2) Comparison with a low-threshold value.