TMP816 SLVS787A – MAY 2009– REVISED JUNE 2015

# TMP816 Variable-Speed Single-Phase Full-Wave Fan-Motor Predriver

Technical

Documents

Sample &

Buv

## **1** Features

- Predriver for Single-Phase Full-Wave Drive

- PNP-NMOS is used as an external power TR, enabling high-efficiency low-consumption drive by means of the low-saturation output and single-phase full-wave drive. (PMOS-NMOS also applicable)

- External PWM Input Enables Variable-Speed Control

- Separately-excited upper direct PWM (f = 25 kHz) control method, enabling highly silent speed control

- Current Limiter Circuit

- Chopper-type current limit at start

- Reactive Current-Cut Circuit

- Reactive current before phase change is cut to enable silent and low-consumption drive

- Minimum Speed Setting Pin

- Minimum speed can be set with external resistor. The start assistance circuit enables start at extremely low speed.

- Constant-Voltage Output Pin for Hall Bias

- Lock Protection and Automatic Reset Functions

Rotation Speed Detection (FG) and Lock Detection (RD) Outputs

Support &

Community

## 2 Applications

Tools &

Software

- Server Fans

- Appliance Fans

## **3 Description**

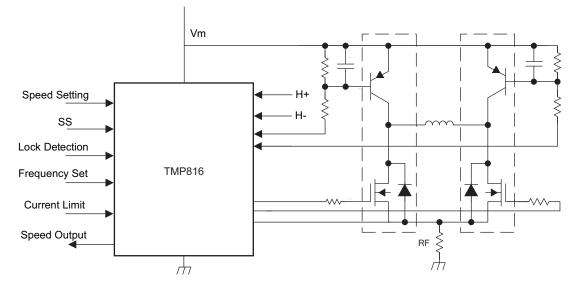

The TMP816 is a single-phase bipolar variable-speed fan-motor predriver that works with an external PWM signal. A highly efficient, quiet, and low-power consumption motor driver circuit with a large variable speed can be implemented by adding a small number of external components.

The TMP816 device is optimal for driving large-scale fan motors (with large air volume and large current) such as those used in servers and consumer products.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| TMP816      | TSSOP (PW) | 4.40 mm × 6.50 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

### Simplified Schematic

2

# **Table of Contents**

| 1 | Feat          | lures                            | 1 |  |  |  |  |

|---|---------------|----------------------------------|---|--|--|--|--|

| 2 | Арр           | lications                        | 1 |  |  |  |  |

| 3 | Description 1 |                                  |   |  |  |  |  |

| 4 | Rev           | ision History                    | 2 |  |  |  |  |

| 5 | Pin           | Configuration and Functions      | 3 |  |  |  |  |

| 6 | Spe           | cifications                      | 4 |  |  |  |  |

|   | 6.1           | Absolute Maximum Ratings         | 4 |  |  |  |  |

|   | 6.2           | ESD Ratings                      | 4 |  |  |  |  |

|   | 6.3           | Recommended Operating Conditions | 4 |  |  |  |  |

|   | 6.4           | Thermal Information              | 4 |  |  |  |  |

|   | 6.5           | Electrical Characteristics       | 5 |  |  |  |  |

|   | 6.6           | Typical Characteristics          | 5 |  |  |  |  |

| 7 | Deta          | ailed Description                |   |  |  |  |  |

|   | 7.1           | Overview                         | 6 |  |  |  |  |

|   | 7.2           | Functional Block Diagram         | 6 |  |  |  |  |

|   |               |                                  |   |  |  |  |  |

|    | 7.4   | Device Functional Modes           | 10 |

|----|-------|-----------------------------------|----|

| 8  | Appl  | ications and Implementation       | 11 |

|    | 8.1   | Application Information           | 11 |

|    | 8.2   | Typical Application               | 11 |

| 9  | Pow   | er Supply Recommendations         | 14 |

| 10 | Layo  | out                               | 14 |

|    | 10.1  | Layout Guidelines                 | 14 |

|    | 10.2  | Layout Example                    | 14 |

| 11 | Devi  | ce and Documentation Support      | 15 |

|    | 11.1  | Community Resources               | 15 |

|    | 11.2  | Trademarks                        | 15 |

|    | 11.3  | Electrostatic Discharge Caution   | 15 |

|    | 11.4  | Glossary                          | 15 |

| 12 | Mec   | hanical, Packaging, and Orderable |    |

|    | Infor | mation                            | 15 |

## **4** Revision History

#### Changes from Original (May 2009) to Revision A

Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section. ..... 1

#### XAS ISTRUMENTS

www.ti.com

Page

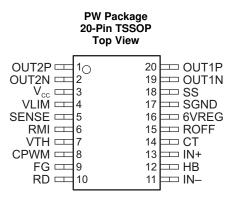

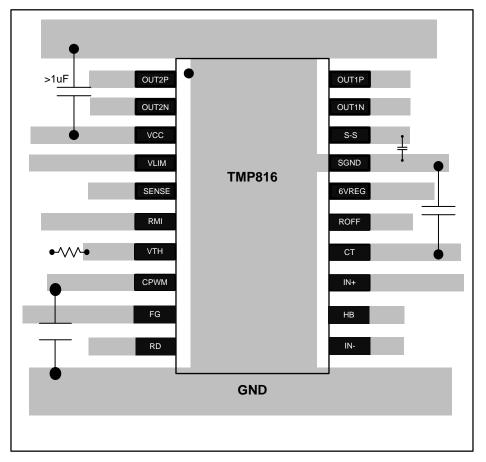

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN   |     | 1/0 | DECODIDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-------|-----|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO. | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| OUT2P | 1   | 0   | Upper-side driver output                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| OUT2N | 2   | 0   | Lower-side driver output                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| VCC   | 3   |     | Power supply. For the CM capacitor that is a power stabilization capacitor for PWM drive and for absorption of kickback, the capacitance of 0.1 $\mu F$ to 1 $\mu F$ is used. In this device, the lower TR performs current regeneration by switching the upper TR. Connect CM between V <sub>CC</sub> and GND, with the thick pattern and along the shortest route. Use a Zener diode if kickback causes excessive increase of the supply voltage, because such increase may damage the device. |  |  |

| VLIM  | 4   | I   | Activates the current limiter when SENSE voltage is higher than VLIM voltage. Connect to 6VREG when not used.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| SENSE | 5   | I   | Sense input. Connect to GND when not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| RMI   | 6   | I   | Minimum speed setting. Connect to 6VREG when not used. If device power can be removed before power is removed from RMI, insert a current limiting resistor to prevent inflow of large current.                                                                                                                                                                                                                                                                                                   |  |  |

| VTH   | 7   | I   | VTH voltage is generated by filtering the PWM-IN input. If device power can be removed before power is removed from VTH, insert a current limiting resistor to prevent inflow of large current.                                                                                                                                                                                                                                                                                                  |  |  |

| CPWM  | 8   | 0   | Connect to capacitor CP to set the PWM oscillation frequency. With CP = 100 pF, oscillation occurs at 25 kHz and provides the basic frequency of PWM.                                                                                                                                                                                                                                                                                                                                            |  |  |

| FG    | 9   | 0   | Open collector output, which can detect the rotation speed using the FG output according to the phase shift. Leave open when not used.                                                                                                                                                                                                                                                                                                                                                           |  |  |

| RD    | 10  | 0   | Open collector output. Outputs low during rotation and high at stop. Leave open when not used.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| IN–   | 11  | I   | Hall input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| HB    | 12  | 0   | This is a Hall element bias, that is, the 1.5-V constant-voltage output.                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| IN+   | 13  | I   | Hall input. Make connecting traces as short as possible to prevent carrying of noise. To futher limit noise, insert a capacitor between IN+ and IN–. The Hall input circuit is a comparator having a hysteresis of 20 mV. The application should ensure that the Hall input level more than three times (60 mVp-p) this hysteresis.                                                                                                                                                              |  |  |

| СТ    | 14  | 0   | Lock detection time setting. Capacitor CT is connected.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| ROFF  | 15  | I   | Sets the soft switching time to cut the reactive current before phase change. Connect to 6VREG when not used.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 6VREG | 16  | 0   | 6-V regulator output                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| SGND  | 17  |     | Connected to the control circuit power supply system.                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

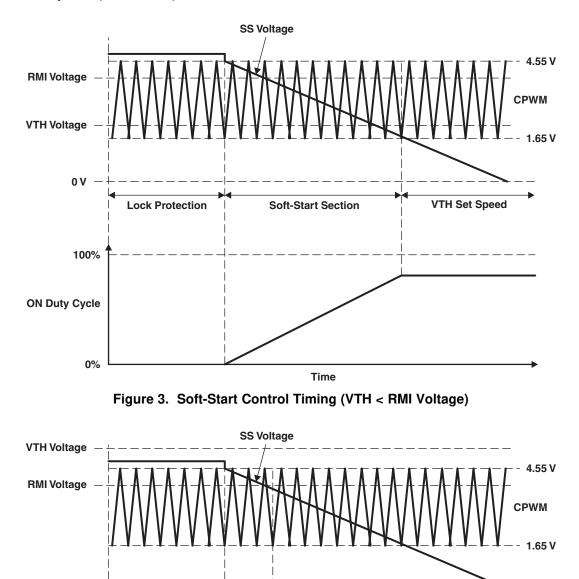

| SS    | 18  | 0   | Connect to soft-start setting capacitor. Connect the capacitor between 6VREG and SS. Enables setting of the soft-start time according to the capacity of the capacitor (see Figure 3 and Figure 4). Connect to ground if not used.                                                                                                                                                                                                                                                               |  |  |

| OUT1N | 19  | 0   | Lower-side driver output                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| OUT1P | 20  | 0   | Upper-side driver output                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                    |                              |                            | MIN | MAX | UNIT |

|------------------------------------|------------------------------|----------------------------|-----|-----|------|

| $V_{CC}$                           | Supply voltage               |                            |     | 18  | V    |

| V <sub>OUT</sub>                   | Output voltage               | OUT1P, OUT1N, OUT2P, OUT2N |     | 18  | v    |

| I <sub>OUT</sub>                   | Continuous output<br>current | OUT1P, OUT1N, OUT2P, OUT2N |     | 50  |      |

| I <sub>HB</sub>                    | Continuous output<br>current | НВ                         |     | 10  | mA   |

| $V_{\text{TH}}$                    | Input voltage                | VTH                        |     | 8   |      |

| V <sub>RD</sub><br>V <sub>FG</sub> | Output voltage               | RD, FG                     |     | 18  | V    |

| I <sub>RD</sub><br>I <sub>FG</sub> | Continuous output<br>current | RD, FG                     |     | 10  | mA   |

| T <sub>stg</sub>                   | Storage temperature          |                            | -65 | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                                       | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>                           | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $\ensuremath{\text{pins}^{(2)}}$ | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

$T_A = 25^{\circ}C$

|                 |                                       |                 | MIN | MAX | UNIT |

|-----------------|---------------------------------------|-----------------|-----|-----|------|

| V <sub>CC</sub> | Supply voltage                        |                 | 6   | 16  | V    |

| $V_{TH}$        | VTH input voltage                     | Full-speed mode | 0   | 7   | V    |

| VICM            | Hall input common phase input voltage |                 | 0.2 | 3   | V    |

| T <sub>A</sub>  | Operating free-air temperature        |                 | -30 | 95  | °C   |

#### 6.4 Thermal Information

|                       |                                              | TMP816     |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                       |                                              | 20 PINS    |      |

| R <sub>eJA</sub>      | Junction-to-ambient thermal resistance       | 83         | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 90.6       | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 42.1       | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 24.3       | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 0.9        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 51.5       | °C/W |

(1) For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, SPRA953.

## 6.5 Electrical Characteristics

$V_{CC}$  = 12 V,  $T_A$  = 25°C (unless otherwise noted)

|                                      | PARAMETER                      |          | TEST CONDITIONS                                      | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------|--------------------------------|----------|------------------------------------------------------|------|------|------|------|

| V <sub>6VREG</sub>                   | Output voltage                 | 6VREG    | I <sub>HB</sub> = 5 mA                               | 5.8  | 6    | 6.15 | V    |

| V <sub>CRH</sub>                     | High-level output voltage      |          |                                                      | 4.35 | 4.55 | 4.75 | V    |

| V <sub>CRL</sub>                     | Low-level output voltage       | CPWM     |                                                      | 1.45 | 1.65 | 1.85 | V    |

| f <sub>PWM</sub>                     | Oscillation frequency          |          | CP = 100 pF                                          | 18   | 25   | 32   | kHz  |

| V <sub>CTH</sub>                     | High-level output voltage      |          |                                                      | 3.4  | 3.6  | 3.8  | V    |

| V <sub>CTL</sub>                     | Low-level output voltage       |          |                                                      | 1.4  | 1.6  | 1.8  | V    |

| I <sub>CT1</sub>                     | Charge current                 | CT       |                                                      | 1.6  | 2    | 2.5  | μA   |

| I <sub>CT2</sub>                     | Discharge current              |          |                                                      | 0.16 | 0.2  | 0.28 | μA   |

| R <sub>CT</sub>                      | Charge/discharge current ratio |          |                                                      | 8    | 10   | 12   |      |

| V <sub>ON</sub>                      | Output voltage                 | OUT_N    | I <sub>O</sub> = 20 mA                               | 4    | 10   |      | V    |

| I <sub>OP</sub>                      | Sink current                   | OUT_P    |                                                      | 15   | 20   |      | mA   |

| $V_{\text{HN}}$                      | Hall input sensitivity         | H+, H-   | Zero peak value<br>(including offset and hysteresis) |      | 10   | 20   | mV   |

| V <sub>RD</sub><br>V <sub>FG</sub>   | Low-level output voltage       | - RD, FG | $I_{RD} = 5 \text{ mA or } I_{FG} = 5 \text{ mA}$    |      | 0.15 | 0.3  | V    |

| I <sub>RDL</sub><br>I <sub>FGL</sub> | Output leakage current         | nD, FG   | $V_{RD} = 16 \text{ V or } V_{FG} = 16 \text{ V}$    |      |      | 30   | μA   |

| I <sub>SS</sub>                      | Discharge current              | SS       | $V_{SS} = 1 V$                                       | 0.4  | 0.5  | 0.6  | μA   |

|                                      | Supply ourrent                 |          | During drive                                         | 4    | 10   | 14   | mA   |

| I <sub>CC</sub>                      | Supply current                 |          | During lock protection                               | 4    | 10   | 14   | ШA   |

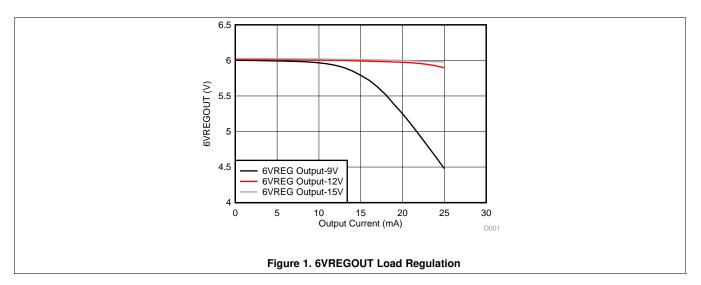

## 6.6 Typical Characteristics

**TMP816** SLVS787A – MAY 2009 – REVISED JUNE 2015

www.ti.com

## 7 Detailed Description

### 7.1 Overview

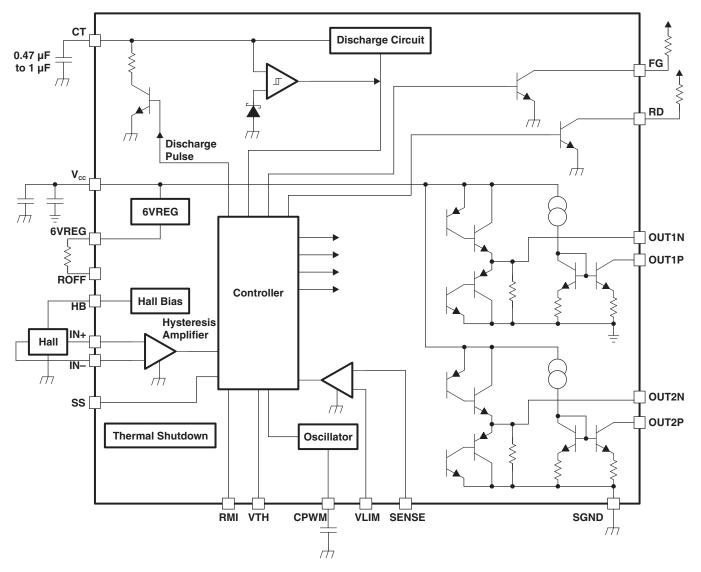

The TMP816 device is a single phase bipolar predriver which uses the hall sensor & speed control inputs for driving the single phase motor connected through H Bridge. The predriver outputs are designed for driving top side P-type devices and bottom side N-channel FETs in the bridge. Multiple protections like overcurrent, soft-start, speed control, lock detect, speed feedback and minimum speed are incorporated in the device.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

### 7.3.1 Speed Control

The speed control functionality is obtained by VTH pin of the device. For pulsed inputs user can supply a 20-kHz to 100-kHz frequency input (20 kHz to 50 kHz recommended on the pin with a current limiting resistor in between. If not used, this pin needs to be connected to ground for full speed.)

#### Feature Description (continued)

#### 7.3.2 Soft-Start

Soft-Start Time can be adjusted using the S-S pin. Connect this capacitor between 6VREG and S-S Pin. Connected to GND if not used.

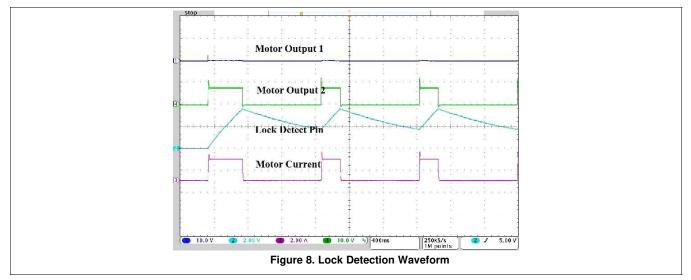

#### 7.3.3 Lock Detection

When the rotor is locked by external means or load conditions, The Lock detection feature helps to protect the circuit by not allowing the current to rise beyond control. A hiccup mechanism is also provided. The Lock detection is enabled by a connection to the lock detection capacitor. The constant current charge and discharge circuits cause drive stop when the pin voltage rises to 3.8V and enabling it back when voltage reached to 1.8V.

If lock detection feature is not desired in the application, this pin needs to be connected to ground.

#### 7.3.4 Current Limit

Current limit resistor is connected in a return path of H Bridge connection. This input is connected to the SENSE pin where the Current is limited when the voltage across this resistor crosses the voltage at VLIM Pin.

If not used, this pin needs to be connected to ground.

#### 7.3.5 Speed Output

The speed of the motor while running can be observed at the FG pin which is an open collector output and needs to be pulled high for using it.

#### 7.3.6 Drive Frequency Selection

The P-channel switches in the device are switched with higher frequency whose duty cycle is decided by the speed control input. The frequency of the operation can be decided by the capacitor connected at the CPWM pin.

## Feature Description (continued)

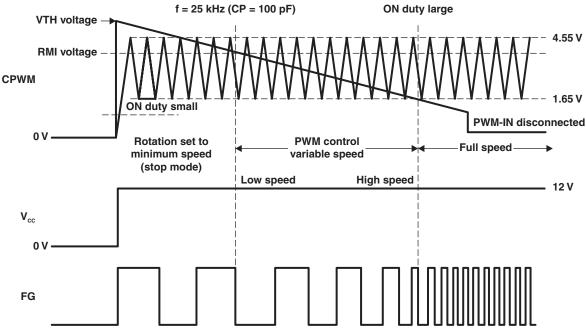

A. Minimum speed setting (stop) mode

PWM-IN input is filtered to generate the VTH voltage. At low speed, the fan rotates with the minimum speed set with RMI during low speed. If the minimum speed is not set (RMI = 6VREG), the fan stops.

B. Low  $\leftrightarrow$  high-speed mode

PWM control is made through comparison of oscillation and VTH voltages with CPWM changing between 1.6 V  $\leftrightarrow$  4.6 V.

Upper and lower TRs are turned ON when the VTH voltage is higher. The upper output TR is turned OFF when the VTH voltage is lower, and the coil current is regenerated in the lower TR. Therefore, as the VTH voltage lowers, the output ON duty increases, increasing the coil current and raising the motor speed. The rotation speed is fed back by the FG output.

C. Full speed mode

The full-speed mode becomes effective with the VTH voltage of 1.65 V or less. (VTH must be equal to GND when the speed control is not used.)

D. PWM-IN input disconnection mode

When the PWM-IN input pin is disconnected, VTH becomes 1.65 V or less and the output enables full drive at 100%. The fan runs at full speed (see Figure 5).

## Figure 2. Control Timing

## Feature Description (continued)

0 V

100%

0%

Copyright © 2009–2015, Texas Instruments Incorporated

**ON Duty Cycle**

Lock Protection

Soft-

Start Section **RMI Set Speed**

Figure 4. Soft-Start Control Timing (VTH > RMI Voltage)

Time

$\text{OUT1} \rightarrow \text{2}$  Drive

$OUT2 \rightarrow 1$  Drive

During rotation, regeneration in lower TR

Н

\_

Н

\_

\_

L

\_

OFF

www.ti.com

## 7.4 Device Functional Modes

Н

L

L

Н

Н

L

Н

L

L

Н

L

Н

| IN– | IN+  | СТ  | OUT1P | OUT1N | OUT2P  | OUT2N  | FG    | RD    | MODE                               |

|-----|------|-----|-------|-------|--------|--------|-------|-------|------------------------------------|

| Н   | L    | L   | L     | -     | -      | Н      | L     | L     | $OUT1 \rightarrow 2 \text{ drive}$ |

| L   | Н    |     | _     | Н     | L      | -      | OFF   |       | $OUT2 \rightarrow 1 \text{ drive}$ |

| Н   | L    | Н   | OFF   | -     | -      | Н      | L     | OFF   | Lock protection                    |

| L   | Н    |     | -     | Н     | OFF    | -      | OFF   |       |                                    |

|     |      |     |       |       |        |        |       |       |                                    |

| VTH | CPWM | IN– | IN+   | OUT   | [1P OL | JT1N ( | OUT2P | OUT2N | MODE                               |

\_

Н

\_

н

L

\_

OFF

\_

#### Table 1. Truth Table

| 10 | Submit Documentation Feedback |

|----|-------------------------------|

|    |                               |

## 8 Applications and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

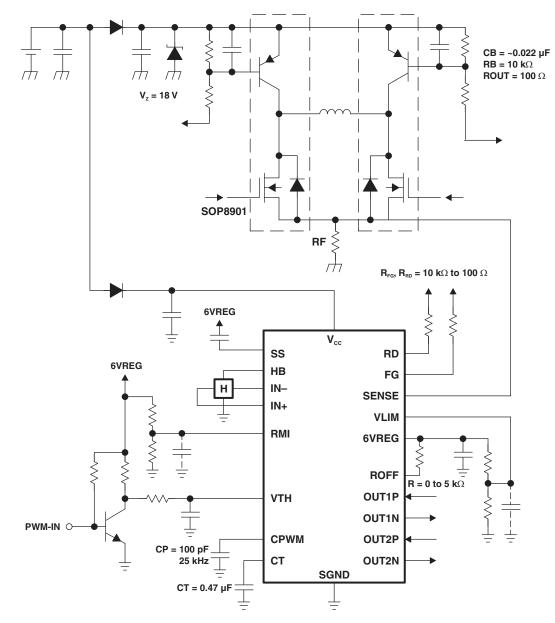

#### 8.1 Application Information

The TMP816 device needs few external components for the features described in *Feature Description*. The device needs a  $1-\mu$ F or more capacitor connected at VCC. The device generates 6-V regulated output, which can be used for pullups in the circuit as well as the Hall sensor.

### 8.2 Typical Application

Figure 5. 12-V Sample Application Circuit

11

## **Typical Application (continued)**

### 8.2.1 Design Requirements

For this design example, use the following parameters:

- Input Voltage: 6 to 16 V

- VCC capacitor: 1 μF or more

- H Bridge Top side: P-channel FETs or PNP transistors

- Bottom side: N-channel FETs

## 8.2.2 Detailed Design Procedure

Pins:

- CPWM Capacitor: 100 pF for 25-kHz switching or appropriate.

- VTH Pin connected to Ground for full-speed or supplied with pulsed input.

- RMI Pin Pulled high to 6VREG output or external connection if required.

- ROFF pulled to 6VREG.

- · 6VREG connected to Hall Sensor. Hall sensor differential inputs connected to IN+ and IN-.

- SENSE pin or GND.

- CT connected to Lock Detection capacitor (0.47 μF or calculated values) or to GND.

- Drive outputs connected to the Gates of the H bridge switches.

- Pullup on FG.

Power Supply:

• Make sure the power supply has set with sufficient current limit at the decided at the motor voltage.

Build the circuit with previously recommended connections at the pins.

Test the motor circuit with hardware connected to it.

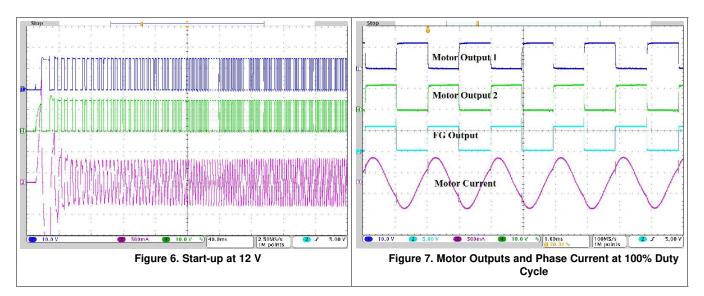

## 8.2.3 Application Curves

## **Typical Application (continued)**

## 9 Power Supply Recommendations

For testing purposes, a current limited source can be connected with voltage between 6-to 16-V on the printedcircuit-board. Use a 1-µF capacitor (minimum) to meet load transient requirements.

## 10 Layout

### 10.1 Layout Guidelines

Connect a minimum of 1-uF or greater capacitor close to power supply pins. Connect other capacitors and resistors according to the calculations (for example, pullup resistors should be connected at various pins, the c capacitors should be connected at lock detect, and so forth.)

## 10.2 Layout Example

Figure 9. Recommended Layout

## **11** Device and Documentation Support

## 11.1 Community Resources

The following links connect to TI community resources. Linked contents are provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

TI E2E<sup>™</sup> Online Community *TI's Engineer-to-Engineer (E2E) Community.* Created to foster collaboration among engineers. At e2e.ti.com, you can ask questions, share knowledge, explore ideas and help solve problems with fellow engineers.

**Design Support** *TI's Design Support* Quickly find helpful E2E forums along with design support tools and contact information for technical support.

### 11.2 Trademarks

E2E is a trademark of Texas Instruments. All other trademarks are the property of their respective owners.

### 11.3 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 11.4 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

Texas

STRUMENTS

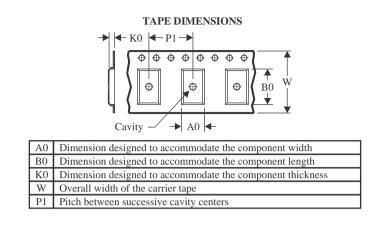

## TAPE AND REEL INFORMATION

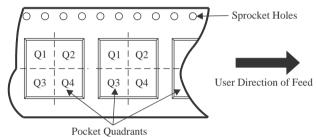

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *A | II dimensions | are | nominal |  |

|----|---------------|-----|---------|--|

|    |               |     |         |  |

|    |               |     |         |  |

| Device    | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-----------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TMP816PWR | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

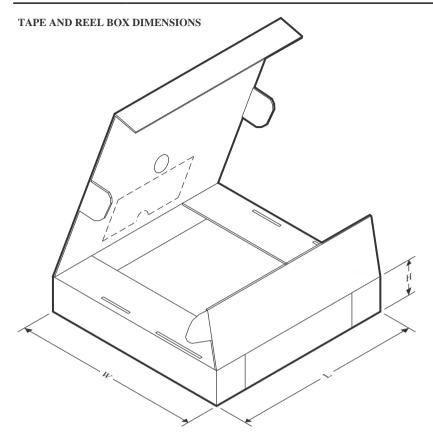

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

\*All dimensions are nominal

| Device    | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-----------|--------------|-----------------|------|------|-------------|------------|-------------|

| TMP816PWR | TSSOP        | PW              | 20   | 2000 | 356.0       | 356.0      | 35.0        |

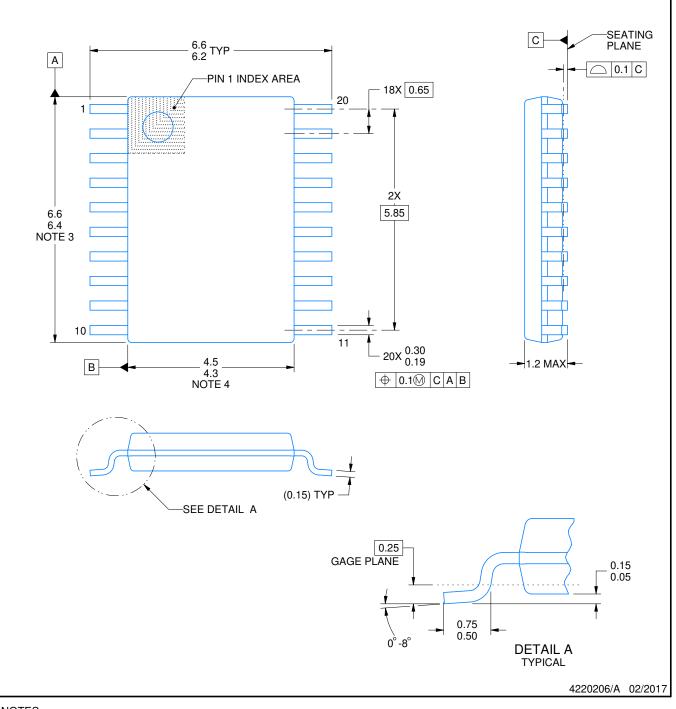

# **PW0020A**

# **PACKAGE OUTLINE**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M. 2. This drawing is subject to change without notice. 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-153.

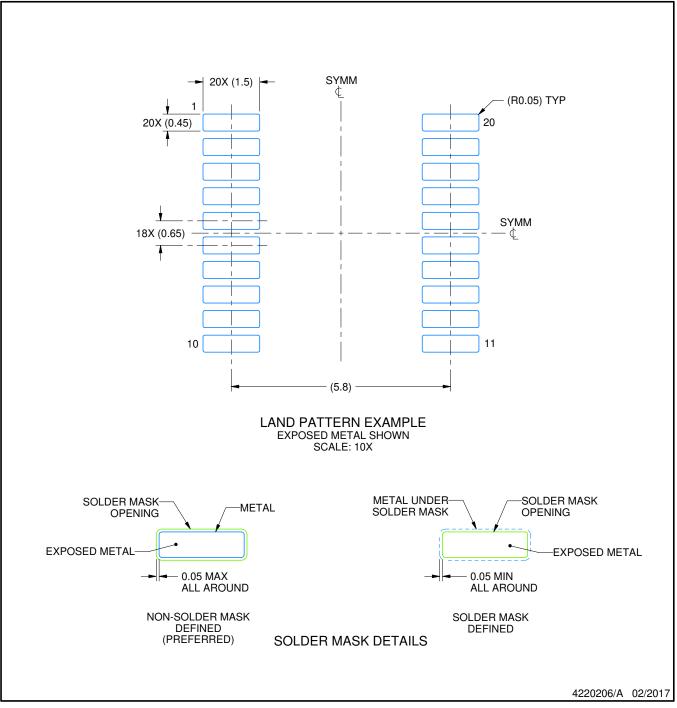

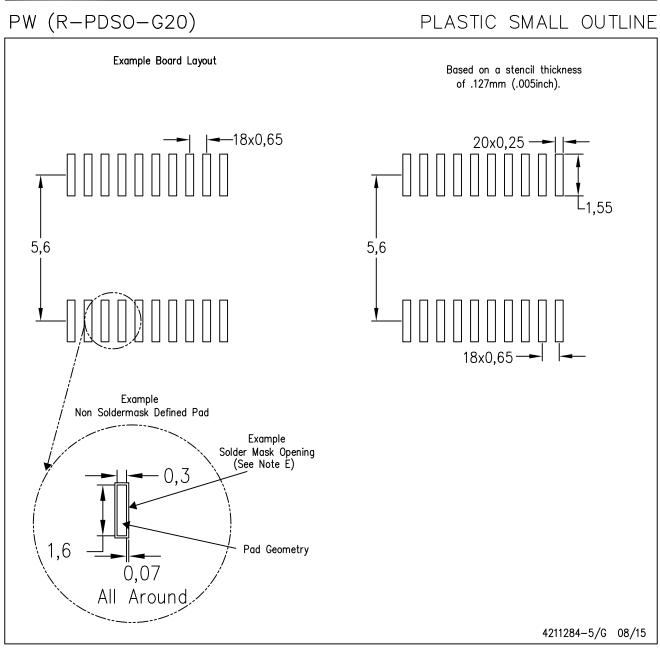

# PW0020A

# **EXAMPLE BOARD LAYOUT**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

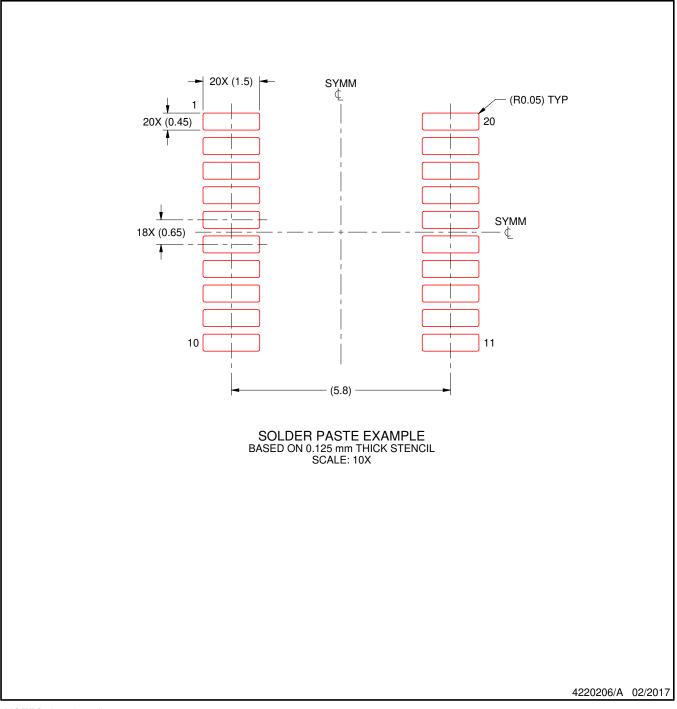

# PW0020A

# **EXAMPLE STENCIL DESIGN**

# TSSOP - 1.2 mm max height

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# LAND PATTERN DATA

NOTES: Α. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

C. Publication IPC-7351 is recommended for alternate design.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated