# 6 A High-Speed MOSFET Drivers

The NCP4420/NCP4429 are 6 A (peak), single output, MOSFET drivers. The NCP4429 is an inverting driver while the NCP4420 is a non–inverting driver. These drivers are fabricated in CMOS for lower power and more efficient operation versus bipolar drivers.

Both drivers have TTL–compatible inputs, which can be driven as high as  $V_{DD} + 0.3 \ V$  or as low as  $-5 \ V$  without upset or damage to the device. This eliminates the need for external level shifting circuitry and its associated cost and size. The output swing is rail–to–rail ensuring better drive voltage margin, especially during power up/power down sequencing. Propagational delay time is only 55 nsec (typ.) and the output rise and fall times are only 25 nsec (typ.) into 2500 pF across the useable power supply range.

Unlike other drivers, the NCP4420/NCP4429 are virtually latch-up proof. They can replace three or more discrete components saving PCB area, costs and improving overall system reliability.

#### **Features**

- Latch–Up Protected: Will Withstand > 1.5 A Reverse Output Current

- Logic Input Will Withstand Negative Swing Up to 5 V

- ESD Protected (4 kV)

- Matched Rise and Fall Times (25 nsec)

- High Peak Output Current (6 A Peak)

- Wide Operating Range (4.5 V to 18 V)

- High Capacitive Load Drive (10,000 pF)

- Short Delay Time (55 nsec Typ)

- Logic High Input, any Voltage (2.4 V to V<sub>DD</sub>)

- Low Supply Current with Logic "1" Input (450 μA)

- Low Output Impedance (2.5 Ω)

- Output Voltage Swing to within 25 mV of Ground or V<sub>DD</sub>

- Temperature Range –40°C to +85°C

#### **Applications**

- Switch–Mode Power Supplies

- Motor Controls

- Pulse Transformer Driver

- Class D Switching Amplifiers

## ON Semiconductor®

http://onsemi.com

#### MARKING DIAGRAM

SO-8 D SUFFIX CASE 751

PDIP-8 P SUFFIX CASE 626

x = Device Number (0 or 9)

YY. Y = Year

WW = Work Week

X = Assembly ID Code

Z = Subcontractor ID Code

CO = Country of Orgin

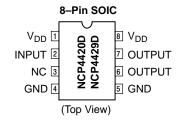

#### **PIN CONNECTIONS**

#### **ORDERING INFORMATION**

| Device                      | Package | Shipping         |

|-----------------------------|---------|------------------|

| NCP4420DR2<br>Non–Inverting | SO-8    | 2500 Tape & Reel |

| NCP4429DR2<br>Inverting     | SO-8    | 2500 Tape & Reel |

| NCP4420P<br>Non-Inverting   | PDIP-8  | 50 Units/Rail    |

| NCP4429P<br>Inverting       | PDIP-8  | 50 Units/Rail    |

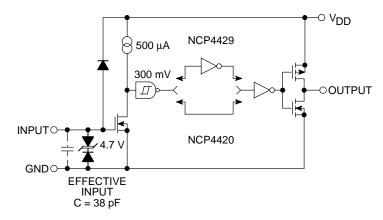

#### **FUNCTIONAL BLOCK DIAGRAM**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Rating                                                   | _  | Value                   | Unit  |

|----------------------------------------------------------|----|-------------------------|-------|

| Supply Voltage                                           |    | +20                     | V     |

| Input Voltage                                            |    | –5.0 to V <sub>DD</sub> | V     |

| Input Current (V <sub>IN</sub> > V <sub>DD</sub> )       | V  | 50                      | mA    |

| Power Dissipation, $T_A \le 70^{\circ}C$<br>SOIC<br>PDIP | 0  | 470<br>730              | mW    |

| Derating Factors (To Ambient) SOIC PDIP                  | ), | 4.0<br>8.0              | mW/°C |

| Storage Temperature Range, T <sub>stg</sub>              |    | -65 to +150             | °C    |

| Operating Temperature (Chip)                             |    | +150                    | °C    |

| Operating Temperature Range (Ambient), T <sub>A</sub>    |    | -40 to +85              | °C    |

| Lead Temperature (Soldering, 10 sec)                     |    | +300                    | °C    |

<sup>\*</sup>Static—sensitive device. Unused devices must be stored in conductive material. Protect devices from static discharge and static fields. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS** ( $T_A = +25^{\circ}C$ with 4.5 V $\leq V_{DD} \leq 18$ V, unless otherwise specified.)

| Characteristic             | Symbol                | Test Conditions                                     | Min                    | Тур | Max                  | Unit |  |

|----------------------------|-----------------------|-----------------------------------------------------|------------------------|-----|----------------------|------|--|

| Input                      |                       |                                                     |                        |     |                      |      |  |

| Logic 1 High Input Voltage | V <sub>IH</sub>       | _                                                   | 2.4                    | 1.8 | _                    | V    |  |

| Logic 0 Low Input Voltage  | V <sub>IL</sub>       | _                                                   | _                      | 1.3 | 0.8                  | V    |  |

| Input Voltage Range        | V <sub>IN</sub> (Max) | _                                                   | -5.0                   | _   | V <sub>DD</sub> +0.3 | V    |  |

| Input Current              | I <sub>IN</sub>       | $0 \text{ V} \leq \text{V}_{IN} \leq \text{V}_{DD}$ | -10                    | ı   | 10                   | μΑ   |  |

| Output                     |                       |                                                     |                        |     |                      |      |  |

| High Output Voltage        | V <sub>OH</sub>       | See Figure 1                                        | V <sub>DD</sub> -0.025 | _   | -                    | ٧    |  |

| Low Output Voltage         | V <sub>OL</sub>       | See Figure 1                                        | -                      | _   | 0.025                | ٧    |  |

| Output Resistance, High    | R <sub>OH</sub>       | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V | -                      | 2.1 | 2.8                  | Ω    |  |

| Output Resistance, Low     | R <sub>OL</sub>       | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V | _                      | 1.5 | 2.5                  | Ω    |  |

| Characteristic                                | Symbol           | Test Conditions                                  | Min    | Тур        | Max        | Unit     |

|-----------------------------------------------|------------------|--------------------------------------------------|--------|------------|------------|----------|

| Output                                        |                  |                                                  |        |            |            |          |

| Peak Output Current                           | I <sub>PK</sub>  | V <sub>DD</sub> = 18 V<br>(See Figure 5)         | -      | 6.0        | _          | А        |

| Latch–Up Protection Withstand Reverse Current | I <sub>REV</sub> | Duty Cycle $\leq 2\%$<br>t $\leq 300 \mu s$      | 1.5    | -          | _          | А        |

| Switching Time (Note 1)                       | •                | ·                                                |        |            |            |          |

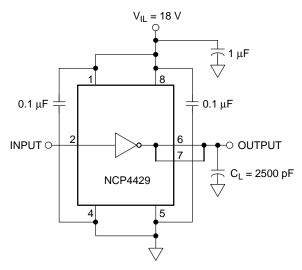

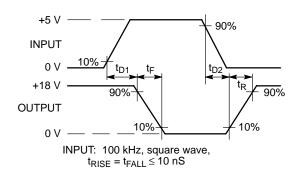

| Rise Time                                     | t <sub>R</sub>   | Figure 1, C <sub>L</sub> = 2500 pF               | -      | 25         | 35         | nsec     |

| Fall Time                                     | t <sub>F</sub>   | Figure 1, C <sub>L</sub> = 2500 pF               | -      | 25         | 35         | nsec     |

| Delay Time 1                                  | t <sub>D1</sub>  | Figure 1                                         | -      | 55         | 75         | nsec     |

| Delay Time 2                                  | t <sub>D2</sub>  | Figure 1                                         | -      | 55         | 75         | nsec     |

| Power Supply                                  |                  | ·                                                |        |            |            | 2        |

| Power Supply Current                          | I <sub>S</sub>   | V <sub>IN</sub> = 3.0 V<br>V <sub>IN</sub> = 0 V | -<br>- | 0.45<br>55 | 1.5<br>150 | mA<br>μA |

| Operating Input Voltage                       | V <sub>DD</sub>  | -                                                | 4.5    | -          | 18         | V        |

<sup>1.</sup> Switching times guaranteed by design.

## **ELECTRICAL CHARACTERISTICS** (Measured over operating temperature range with $4.5 \text{ V} \leq \text{V}_{DD} \leq 18 \text{ V}$ , unless otherwise specified.)

| specifica.)                |                       |                                                                   |                        |            |                      |          |

|----------------------------|-----------------------|-------------------------------------------------------------------|------------------------|------------|----------------------|----------|

| Characteristic             | Symbol                | Test Conditions                                                   | Min                    | Тур        | Max                  | Unit     |

| Input                      |                       |                                                                   |                        |            |                      |          |

| Logic 1 High Input Voltage | V <sub>IH</sub>       | -                                                                 | 2.4                    | _          | -                    | V        |

| Logic 0 Low Input Voltage  | V <sub>IL</sub>       | -                                                                 |                        | -          | 0.8                  | V        |

| Input Voltage Range        | V <sub>IN</sub> (Max) | <b></b>                                                           | -5.0                   | _          | V <sub>DD</sub> +0.3 | V        |

| Input Current              | I <sub>IN</sub>       | $0 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{DD}}$ | -10                    | -          | 10                   | μΑ       |

| Output                     |                       |                                                                   |                        |            |                      |          |

| High Output Voltage        | V <sub>OH</sub>       | See Figure 1                                                      | V <sub>DD</sub> -0.025 | _          | -                    | V        |

| Low Output Voltage         | V <sub>OL</sub>       | See Figure 1                                                      | -                      | _          | 0.025                | V        |

| Output Resistance, High    | R <sub>OH</sub>       | l <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V               | -                      | 3.0        | 5.0                  | Ω        |

| Output Resistance, Low     | R <sub>OL</sub>       | I <sub>OUT</sub> = 10 mA,<br>V <sub>DD</sub> = 18 V               | _                      | 2.3        | 5.0                  | Ω        |

| Switching Time (Note 1)    | 0),                   |                                                                   |                        |            |                      |          |

| Rise Time                  | lt <sub>R</sub>       | Figure 1, C <sub>L</sub> = 2500 pF                                | -                      | 32         | 60                   | nsec     |

| Fall Time                  | t <sub>F</sub>        | Figure 1, C <sub>L</sub> = 2500 pF                                | -                      | 34         | 60                   | nsec     |

| Delay Time 1               | t <sub>D1</sub>       | Figure 1                                                          | -                      | 50         | 100                  | nsec     |

| Delay Time 2               | t <sub>D2</sub>       | Figure 1                                                          | -                      | 65         | 100                  | nsec     |

| Power Supply               |                       |                                                                   |                        |            |                      |          |

| Power Supply Current       | I <sub>S</sub>        | $V_{IN} = 3.0 \text{ V}$<br>$V_{IN} = 0 \text{ V}$                |                        | 0.45<br>60 | 3.0<br>400           | mA<br>μA |

| Operating Input Voltage    | V <sub>DD</sub>       | _                                                                 | 4.5                    | -          | 18                   | V        |

|                            |                       |                                                                   |                        |            |                      |          |

<sup>1.</sup> Switching times guaranteed by design.

Figure 1. Switching Time Test Circuit

#### **TYPICAL CHARACTERISTICS**

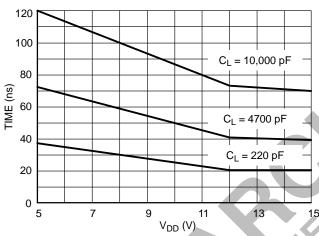

Figure 2. Rise Time vs. Supply Voltage

Figure 3. Fall Time vs. Supply Voltage

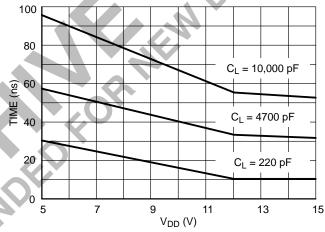

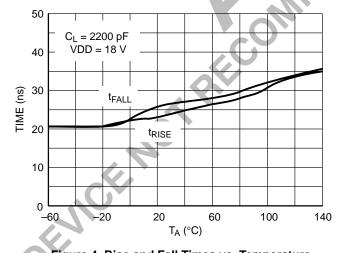

Figure 4. Rise and Fall Times vs. Temperature

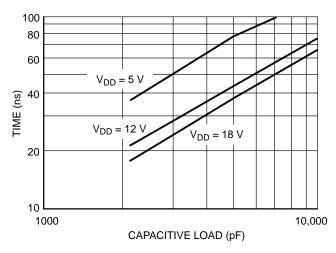

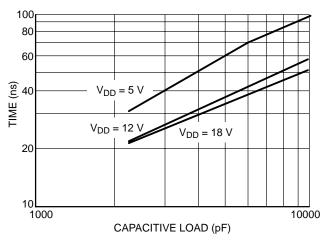

Figure 5. Rise Time vs. Capacitive Load

#### **TYPICAL CHARACTERISTICS**

Figure 6. Fall Time vs. Capacitive Load

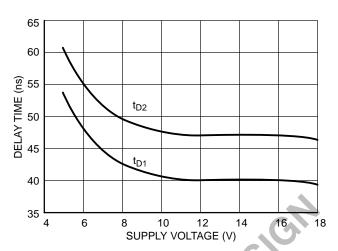

Figure 7. Propagation Delay Time vs.Supply Voltage

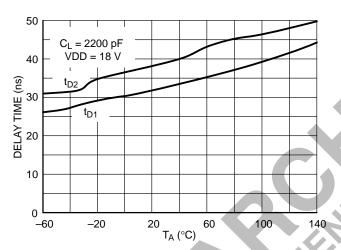

Figure 8. Propagation Delay Time vs. Temperature

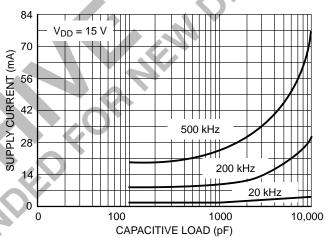

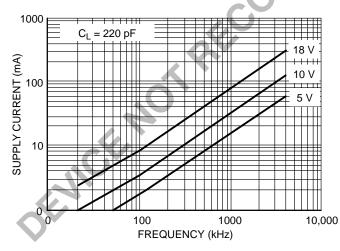

Figure 9. Supply Current vs. Capacitive Load

Figure 10. Supply Current vs. Frequency

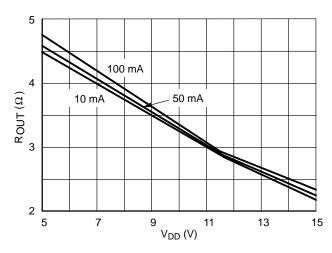

Figure 11. High-State Output Resistance

#### **TYPICAL CHARACTERISTICS**

200 LOAD = 2200 pF160 DELAY TIME (ns) 120 INPUT 2.4 V INPUT 3 V 80 JNPUT 5 V 40 INPUT 8 V AND 10 V 0 14 5 6 8 9 10 11 12 15 7  $V_{DD}(V)$

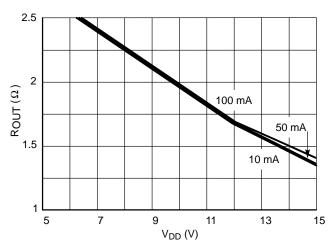

Figure 12. Low-State Output Resistance

Figure 13. Effect of Input Amplitude on Propagation Delay

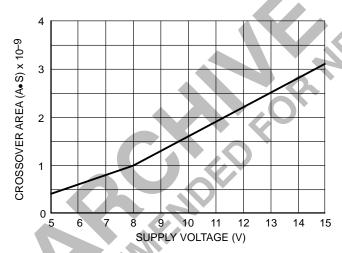

Figure 14. Total nA•S Crossover\*

\*The values on this graph represent the loss seen by the driver during one complete cycle. For a single transition, divide the value by 2.

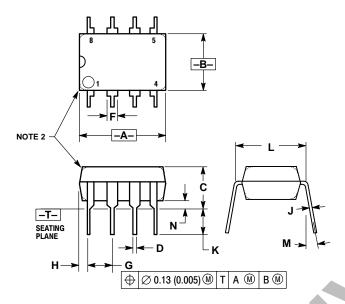

#### **PACKAGE DIMENSIONS**

PDIP-8 **P SUFFIX** CASE 626-05 ISSUE K

- NOTES:

1. DIMENSION L TO CENTER OF LEAD WHEN

- FORMED PARALLEL.

2. PACKAGE CONTOUR OPTIONAL (ROUND OR

- SQUARE CORNERS).

3. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

|     | MILLIN | IETERS | INC      | HES   |

|-----|--------|--------|----------|-------|

| DIM | MIN    | MAX    | MIN      | MAX   |

| Α   | 9.40   | 10.16  | 0.370    | 0.400 |

| В   | 6.10   | 6.60   | 0.240    | 0.260 |

| С   | 3.94   | 4.45   | 0.155    | 0.175 |

| D   | 0.38   | 0.51   | 0.015    | 0.020 |

| F   | 1.02   | 1.78   | 0.040    | 0.070 |

| G   | 2.54   | BSC    | 0.100    | BSC   |

| Н   | 0.76   | 1.27   | 0.030    | 0.050 |

| J   | 0.20   | 0.30   | 0.008    | 0.012 |

| K   | 2.92   | 3.43   | 0.115    | 0.135 |

| L   |        | BSC    |          | BSC   |

| М   |        | 10°    |          | → 10° |

| N   | 0.76   | 1.01   | 0.030    | 0.040 |

|     |        | 4      | V        |       |

|     |        | N      | <b>V</b> |       |

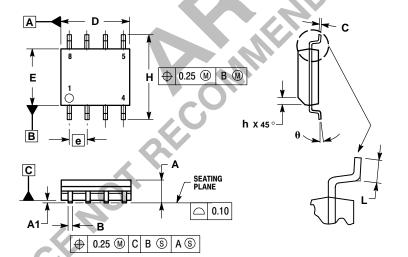

SO-8 **D SUFFIX** CASE 751-06 ISSUE T

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.

2. DIMENSIONS ARE IN MILLIMETER.

3. DIMENSION D AND E DO NOT INCLUDE MOLD PROTECTION OF AND EDUCATION OF THE PROTECTION OF THE PROTECTION OF THE PROTECTION OF T

- PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

- DIMENSION B DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |      |  |  |  |

|-----|-------------|------|--|--|--|

| DIM | MIN         | MAX  |  |  |  |

| Α   | 1.35        | 1.75 |  |  |  |

| A1  | 0.10        | 0.25 |  |  |  |

| В   | 0.35        | 0.49 |  |  |  |

| С   | 0.19        | 0.25 |  |  |  |

| D   | 4.80        | 5.00 |  |  |  |

| E   | 3.80        | 4.00 |  |  |  |

| е   | 1.27 BSC    |      |  |  |  |

| Н   | 5.80        | 6.20 |  |  |  |

| h   | 0.25        | 0.50 |  |  |  |

| L   | 0.40        | 1.25 |  |  |  |

| Δ   | n۰          | 7 0  |  |  |  |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

**Phone:** 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax:** 303–675–2176 or 800–344–3867 Toll Free USA/Canada

Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

**JAPAN**: ON Semiconductor, Japan Customer Focus Center 2–9–1 Kamimeguro, Meguro–ku, Tokyo, Japan 153–0051

Phone: 81–3–5773–3850 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local

Sales Representative.