## **S1D13742 Mobile Graphics Engine**

# **Hardware Functional Specification**

Document Number: X63A-A-001-06.6

| ΝI | $\sim$ | ГΙ | $\sim$ |   |

|----|--------|----|--------|---|

| IN | O٦     | ı  | С      | ⊏ |

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. When exporting the products or technology described in this material, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You are requested not to use, to resell, to export and/or to otherwise dispose of the products (and any technical information furnished, if any) for the development and/or manufacture of weapon of mass destruction or for other military purposes.

All brands or product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2004-2018. All rights reserved.

# **Table of Contents**

| 1 | Introduct | tion                           | 7    |

|---|-----------|--------------------------------|------|

|   | 1.1 Scop  | pe                             | 7    |

|   | 1.2 Over  | erview Description             | 7    |

| 2 | Features  | ·                              | 8    |

|   | 2.1 Integ | grated Frame Buffer            | 8    |

|   | 2.2 CPU   | J Interface                    | 8    |

|   | 2.3 Inpu  | ut Data Formats                | 8    |

|   | 2.4 Disp  | play Support                   | 8    |

|   | 2.5 Disp  | play Modes                     | 8    |

|   | 2.6 Disp  | play Features                  | 9    |

|   | 2.7 Cloc  | ck Source                      | 9    |

|   | 2.8 Misc  | cellaneous                     | 9    |

| 3 | Block Dia | agram                          | . 10 |

| 4 | Pinout Di | liagram                        | . 11 |

|   | 4.1 Pin-0 | Out                            | . 11 |

|   | 4.2 Pin l | Descriptions                   | . 12 |

|   | 4.2.1     | Intel 80 Host Interface        | 13   |

|   | 4.2.2     | LCD Interface                  | 14   |

|   | 4.2.3     | Clocks                         | 14   |

|   | 4.2.4     | Miscellaneous                  | 15   |

|   | 4.2.5     | Power And Ground               | 16   |

|   | 4.3 Sum   | nmary of Configuration Options | . 17 |

| 5 | Pin Mapp  | ping                           | . 18 |

|   | 5.1 Intel | ll 80 Data Pins                | . 18 |

|   | 5.2 LCD   | D Interface Pin Mapping        | . 19 |

|   | 5.3 LCD   | D Interface Data Pins          | . 20 |

| 6 | D.C. Cha  | ıracteristics                  | . 21 |

|   | 6.1 Abso  | solute Maximum Ratings         | . 21 |

|   | 6.2 Reco  | ommended Operating Conditions  | . 21 |

|   | 6.3 Elec  | ctrical Characteristics        | . 22 |

| 7 | A.C. Cha  | ıracteristics                  | . 25 |

|   |           | ck Timing                      |      |

|   | 7.1.1     | Input Clocks                   | 25   |

|   | 7.1.2     | PLL Clock                      |      |

|   | 7.2 RES   | SET# Timing                    | . 28 |

|   | 7.3 Host  | st interface Timing            | . 29 |

|    | 7.3.1 Intel 80 Interface Timing - 1.8 Volt                        | 29         |

|----|-------------------------------------------------------------------|------------|

|    | 7.3.2 Intel 80 Interface Timing - 3.3 Volt                        | 31         |

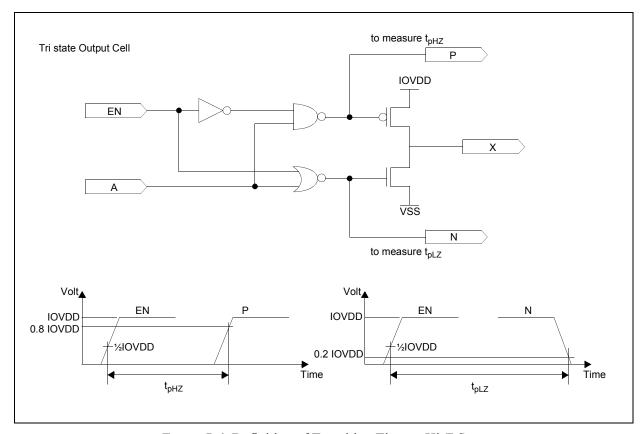

|    | 7.3.3 Definition of Transition Time to Hi-Z State                 | 3          |

|    | 7.4 Display Interface                                             | 34         |

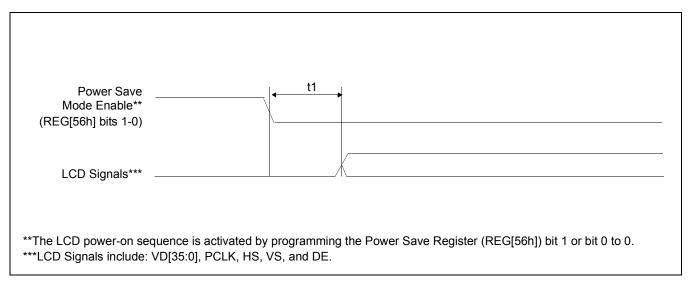

|    | 7.4.1 TFT Power-On Sequence                                       | 35         |

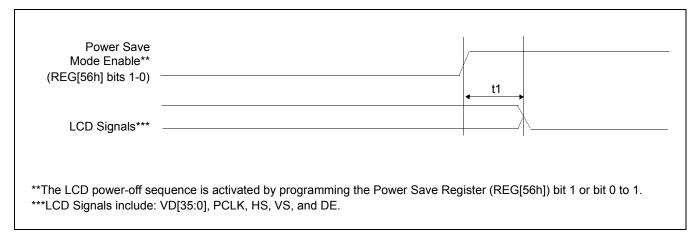

|    | 7.4.2 TFT Power-Off Sequence                                      | 6          |

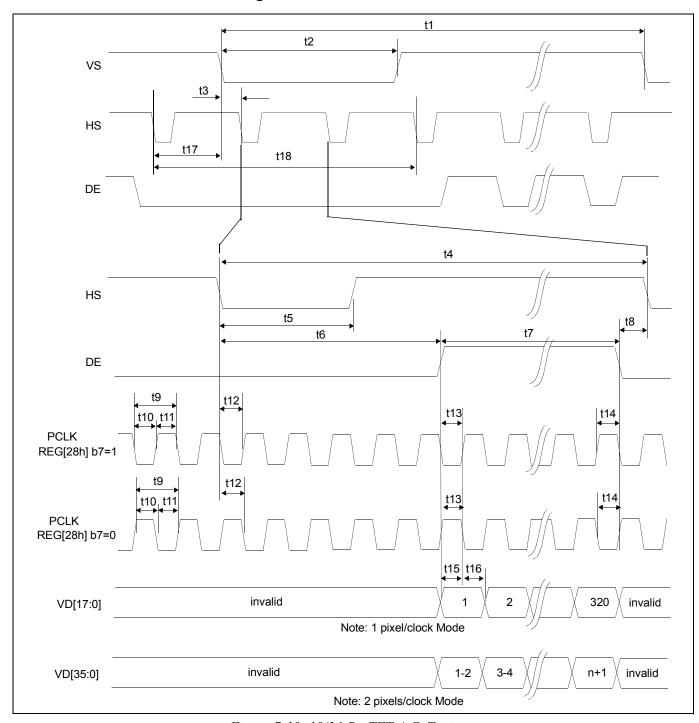

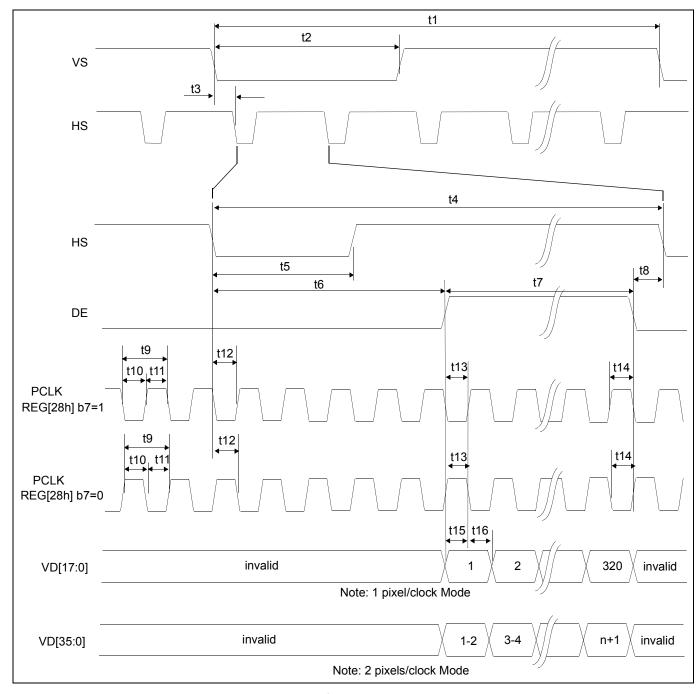

|    | 7.4.3 18/36-Bit TFT Panel Timing                                  | 37         |

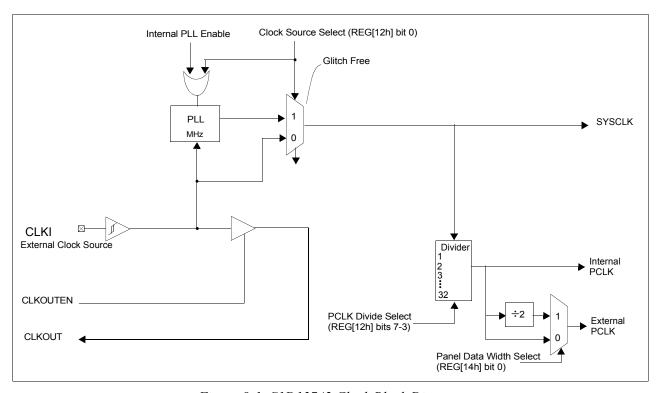

| 8  | Clocks                                                            | 9          |

|    | 8.1 Clock Descriptions                                            |            |

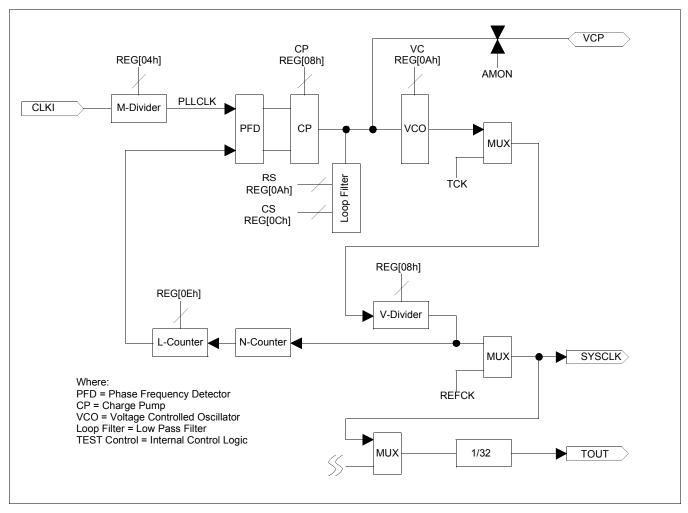

|    | 8.2 PLL Block Diagram                                             |            |

|    | 8.3 Clocks versus Functions                                       | 1          |

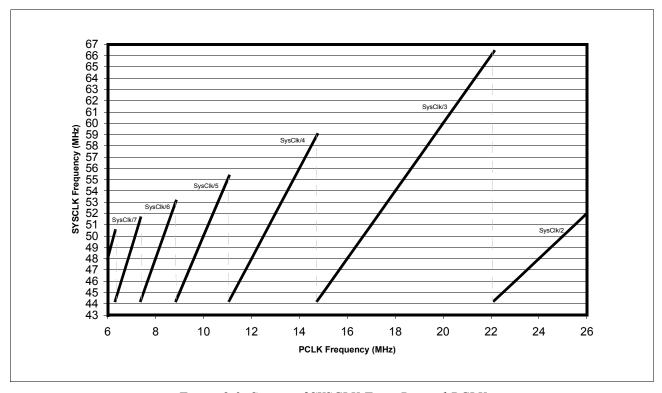

|    | 8.4 Setting SYSCLK and PCLK                                       | 12         |

| 9  | Registers                                                         | 13         |

|    | 9.1 Register Mapping                                              |            |

|    | 9.2 Register Set                                                  | ļ4         |

|    | 9.3 Register Descriptions                                         | <b>I</b> 5 |

|    | 9.3.1 Read-Only Configuration Registers                           | ŀ5         |

|    | 9.3.2 Clock Configuration Registers                               | 16         |

|    | 9.3.3 Panel Configuration Registers                               | ;1         |

|    | 9.3.4 Input Mode Register                                         | 54         |

|    | 9.3.5 Display Mode Registers                                      | ;9         |

|    | 9.3.6 Window Settings                                             | 53         |

|    | 9.3.7 Memory Access                                               | 55         |

|    | 9.3.8 Gamma Correction Registers                                  | 7          |

|    | 9.3.9 Miscellaneous Registers                                     | 59         |

|    | 9.3.10 General Purpose IO Pins Registers                          | 1          |

| 10 | Frame Rate Calculation                                            | '3         |

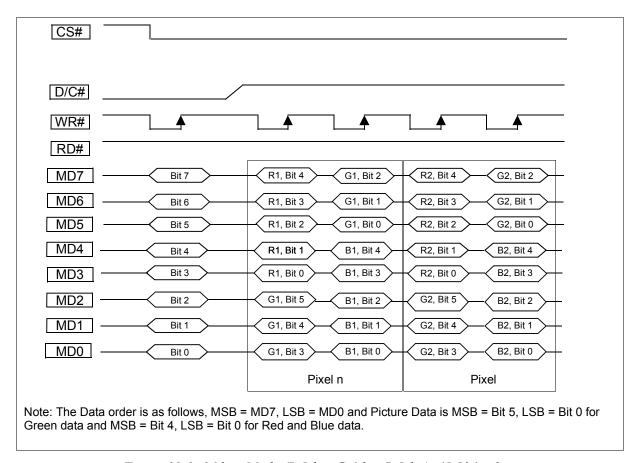

| 11 | Intel 80, 8-bit Interface Color Formats                           | '4         |

|    | 11.1 16 bpp Mode (R 5-bit, G 6-bit, B 5-bit), 65,536 colors       |            |

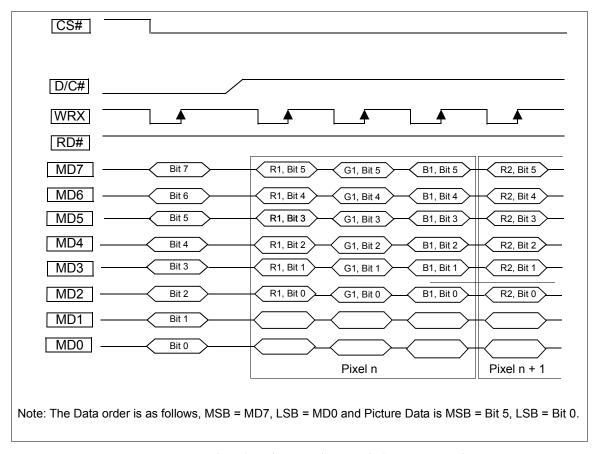

|    | 11.2 18 bpp (R 6-bit, G 6-bit, B 6-bit), 262,144 colors           | 15         |

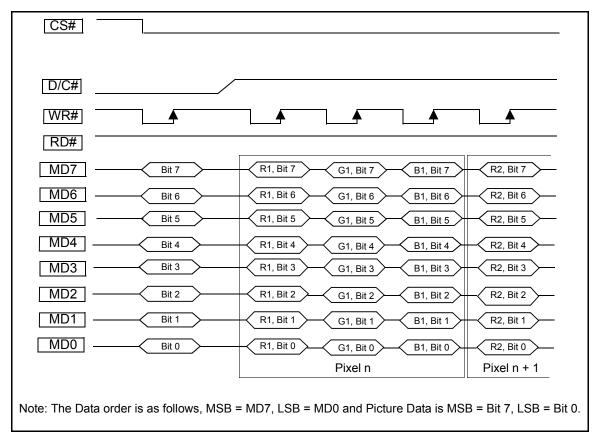

|    | 11.3 24 bpp (R 8-bit, G 8-bit, B 8-bit), 16,777,216 colors        | 6          |

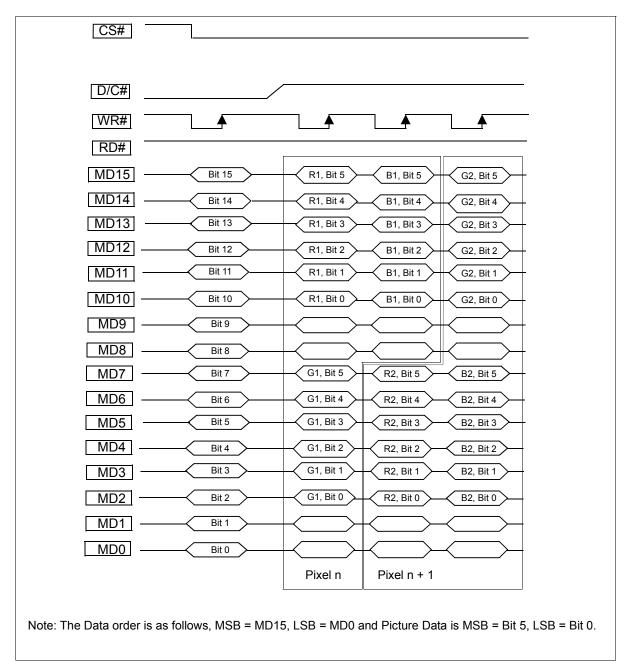

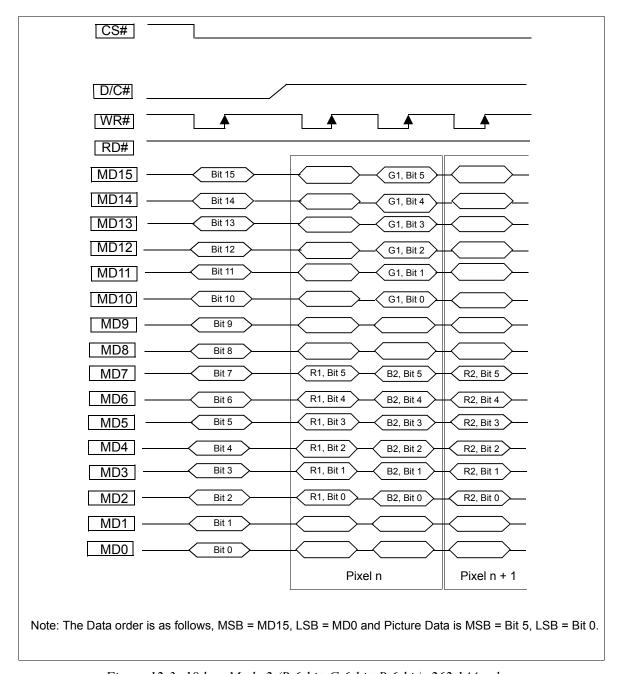

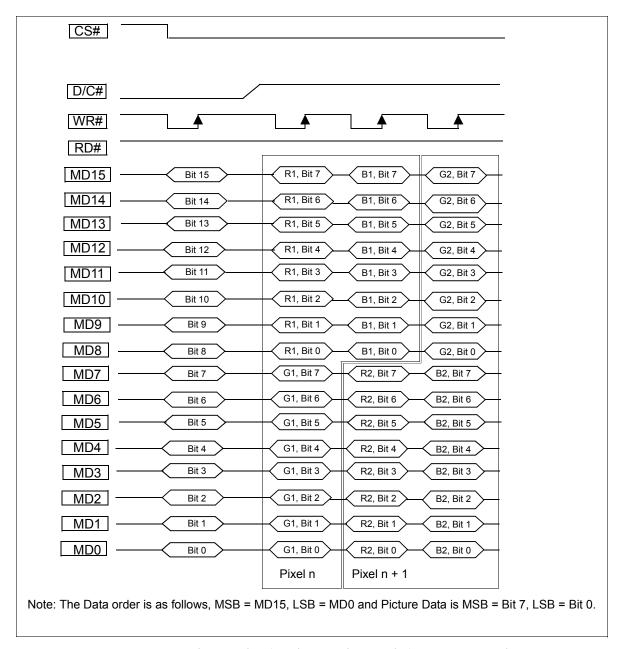

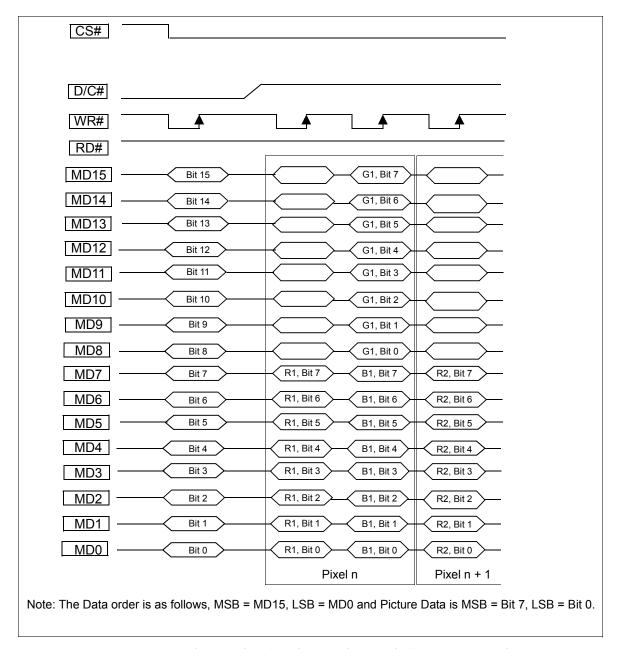

| 12 | Intel 80, 16-bit Interface Color Formats                          | 7          |

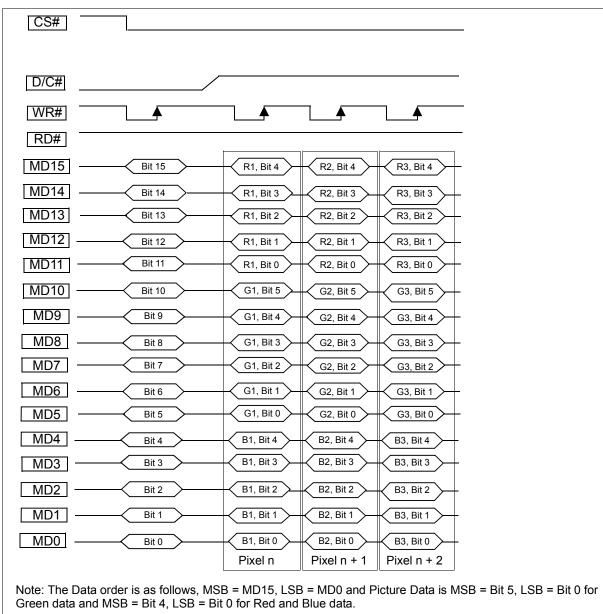

|    | 12.1 16 bpp (R 5-bit, G 6-bit, B 5-bit), 65,536 colors            |            |

|    | 12.2 18 bpp Mode 1 (R 6-bit, G 6-bit, B 6-bit), 262,144 colors    |            |

|    | 12.3 18 bpp Mode 2 (R 6-bit, G 6-bit, B 6-bit), 262,144 colors    | 19         |

|    | 12.4 24 bpp Mode 1 (R 8-bit, G 8-bit, B 8-bit), 16,777,216 colors |            |

|    | 12.5 24 bpp Mode 2 (R 8-bit, G 8-bit, B 8-bit), 16,777,216 colors | 31         |

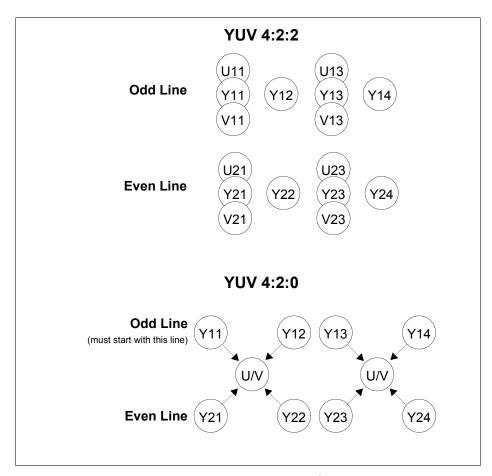

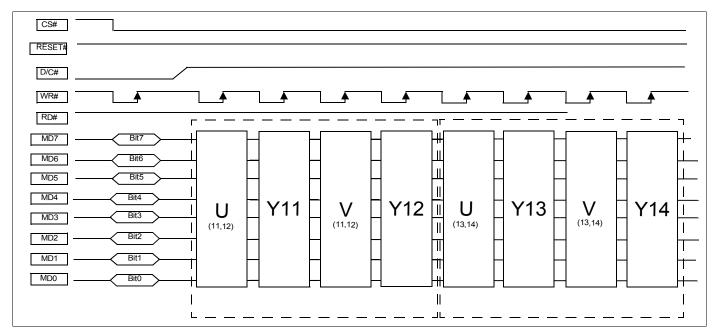

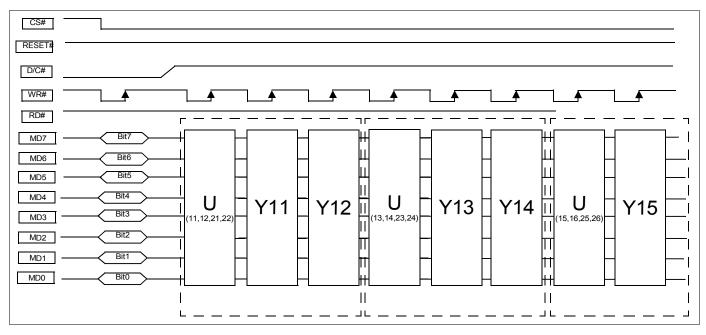

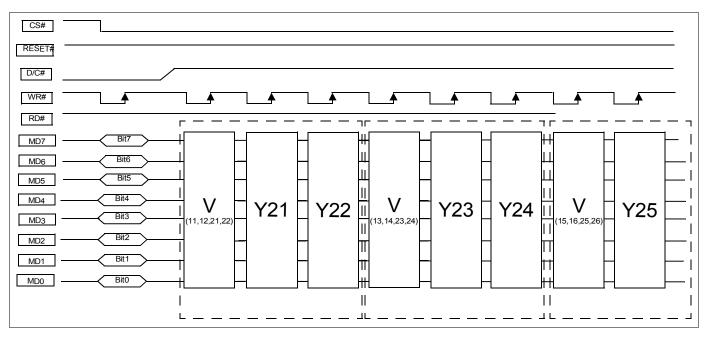

| 13 | YUV Timing                                                        | 2          |

|    | 13.1 YUV 4:2:2 with Intel 80, 8-bit Interface                     |            |

|    | 13.2 YUV 4:2:0 ODD Line with Intel 80, 8-bit Interface   |

|----|----------------------------------------------------------|

|    | 13.3 YUV 4:2:0 EVEN Line with Intel 80, 8-bit Interface  |

|    | 13.4 YUV 4:2:2 with Intel 80, 16-bit Interface           |

|    | 13.5 YUV 4:2:0 ODD Line with Intel 80, 16-bit Interface  |

|    | 13.6 YUV 4:2:0 EVEN Line with Intel 80, 16-bit Interface |

| 14 | Gamma Correction Look-Up Table Architecture              |

|    | 14.1 Gamma Correction Example Programming                |

| 15 | Display Data Format                                      |

| 16 | SwivelView™                                              |

|    | 16.1 Concept                                             |

|    | 16.2 90° SwivelView <sup>TM</sup>                        |

|    | 16.2.1 Register Programming                              |

|    | 16.3 180° SwivelView <sup>TM</sup>                       |

|    | 16.3.1 Register Programming                              |

|    | 16.4 270° SwivelView <sup>TM</sup>                       |

|    | 16.4.1 Register Programming                              |

| 17 | Host Interface                                           |

|    | 17.1 Using the Intel 80 Interface                        |

|    | 17.1.1 Register write procedure                          |

|    | 17.1.2 Register read procedure                           |

|    | 17.1.3 New Window Aperture Write procedure               |

|    | 17.1.4 Opening Multiple Windows                          |

|    | 17.1.5 Individual Memory Location Reads                  |

| 18 | Double Buffer Description                                |

|    | 18.1 Double Buffer Controller                            |

| 19 | Interfacing the S1D13742 and a TFT Panel                 |

|    | 19.1 Overview                                            |

|    | 19.1.1 Electrical Interface                              |

|    | 19.1.2 S1D13742 Register Settings for 352x416 TFT Panel  |

|    | 19.1.3 S1D13742 Register Settings for 800x480 TFT Panel  |

|    | 19.2 Host Bus Timing                                     |

|    | 19.2.1 Host Bus Timing for 352x416 TFT Panel             |

|    | 19.2.2 Host Bus Timing for 800x480 TFT Panel             |

|    | 19.3 Panel Timing                                        |

|    | 19.3.1 Panel Timing for 352x416 Panel                    |

|    | 19.3.2 Panel Timing for 800x480 Panel                    |

|    | 19.4 Example Play.exe Scripts                            |

|    | 19.5 References                                          |

|    | 19.5.1 Documents                                         |

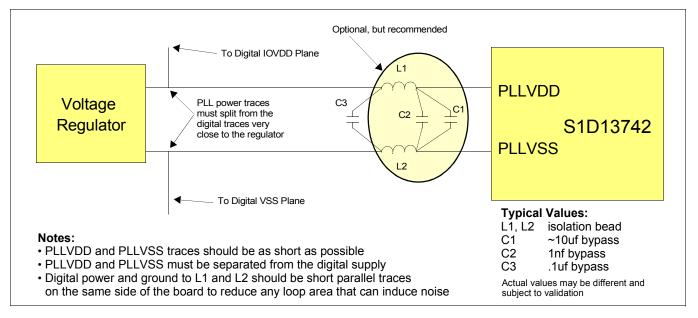

| 20 | PLL Power Supply Considerations      | 122 |

|----|--------------------------------------|-----|

|    | 20.1 Guidelines for PLL Power Layout | 122 |

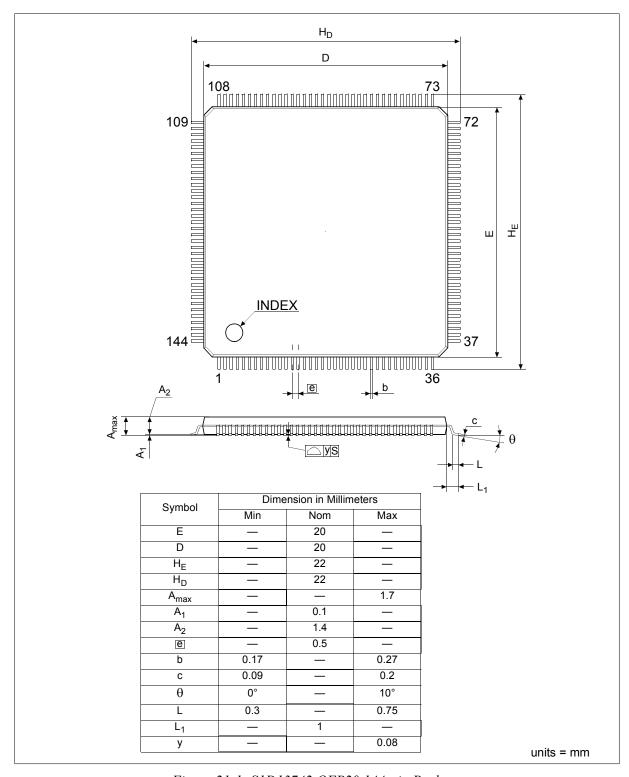

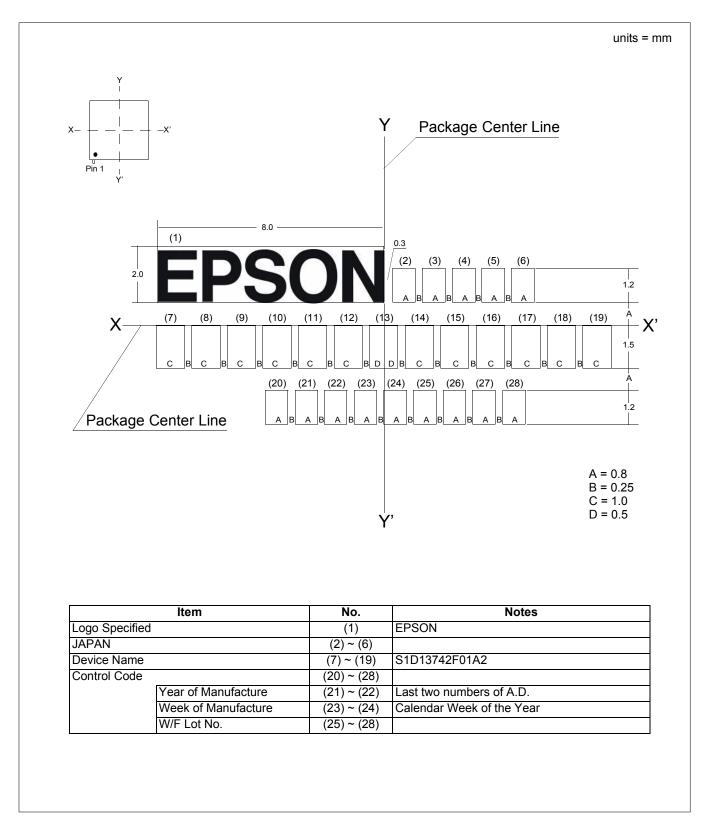

| 21 | Mechanical Data                      | 124 |

| 22 | Change Record                        | 126 |

| 23 | Sales and Technical Support          | 128 |

## 1 Introduction

## 1.1 Scope

This is the Hardware Functional Specification for the S1D13742 Embedded Memory LCD Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Video Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check the Epson Research and Development Website at vdc.epson.com for the latest revision of this document before beginning any development.

We appreciate your comments on our documentation. Please contact us via email at vdc-documentation@ea.epson.com.

## 1.2 Overview Description

The S1D13742 is a color LCD graphics controller with an embedded 768K byte display buffer. The S1D13742 supports a 8/16-bit Intel 80 CPU architecture while providing high performance bandwidth into display memory allowing for fast screen updates.

Products requiring a rotated display image can take advantage of the SwivelView<sup>TM</sup> feature which provides hardware rotation of the display memory transparent to the software application. Resolutions supported include 800x480 single buffered and 352x416 double buffered.

The S1D13742 uses a double-buffer architecture to prevent any visual tearing during streaming video screen updates.

## 2 Features

### 2.1 Integrated Frame Buffer

• Embedded 768K byte SRAM display buffer.

### 2.2 CPU Interface

- 8/16-bit Intel 80 interface (used for display or register data).

- Chip select is used to select device. When inactive, any input data/command will be ignored.

### 2.3 Input Data Formats

- RGB: 8:8:8, 6:6:6, 5:6:5 (8:8:8 will be truncated to 16 or 18 bpp).

- YUV 4:2:2, 4:2:0 (Internal YUV to RGB Converter stored as 16 or 18 bpp).

### Note

All input data must be internally converted to the same format before being stored in the display buffer. Different data types can not be mixed within a common display buffer.

### 2.4 Display Support

- Active Matrix TFT interface.

- 18/36-bit interface.

- Supports resolutions up to 800x480.

## 2.5 Display Modes

- 16/18 bit-per-pixel (bpp) color depths.

- 16 bpp to 18 bpp conversion: Input data can be converted from 16 bpp to 18 bpp in one of three ways.

- 1. RGB (5:6:5) msb copying to create new lsb for the Red and Blue components. This conversion is done prior to storing in memory, as this allows for 16 bpp and 18 bpp input data to be mixed.

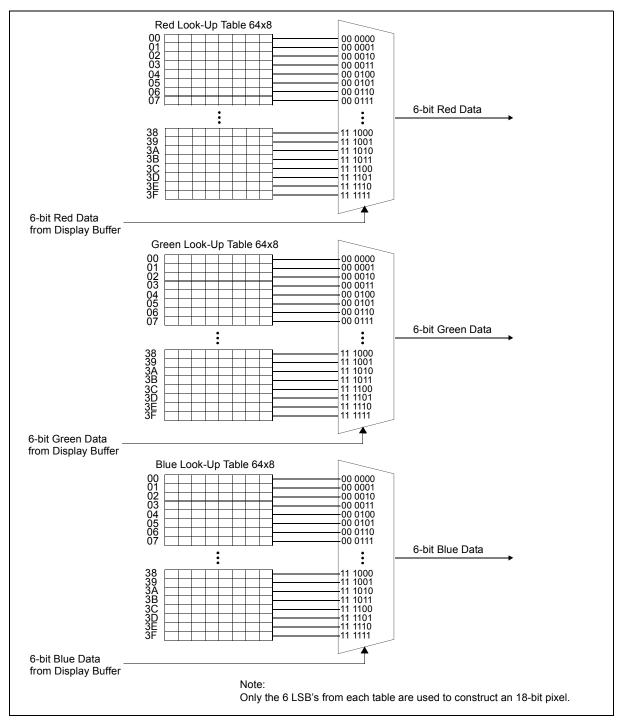

- Gamma Correction Look-Up-Tables: there are three, 64 position, 8-bit wide LUT's. The data stored in memory can be used as an index into these tables. The LUT's are placed on the display side and therefore do not affect the data stored in memory.

- 3. RGB (5:6:5) stored in memory: LUT is by-passed. Copy msb to lsb for red and blue during the display read from memory.

### 2.6 Display Features

- All display writes will be handled by window apertures/position for complete or partial display updates. All window coordinates are referenced to top left corner of the displayed image (even in a rotated display, the top-left corner is maintained and no host side translation need take place).

- SwivelView<sup>TM</sup>: 90°, 180°, 270° counter-clockwise hardware rotation of display image.

All displayed windows can have independent rotation. No additional programming necessary when enabling these modes.

- Double-Buffer available to prevent image tearing during streaming input. Resolutions supported must fit inside 384K bytes (½ of total available display buffer). Typical resolution of 352x416.

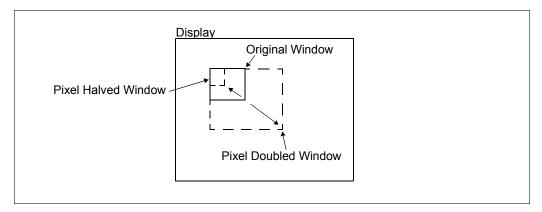

- Pixel Doubling: Horizontal and Vertical averaging for smooth doubling of a single window.

- Pixel Halving: no limitation on number of windows.

### 2.7 Clock Source

- Internal programmable PLL.

- Single MHz clock input: CLKI.

- CLKI available as CLKOUT (separate CLKOUTEN pin associated with output).

- output state = 0 when disabled.

### 2.8 Miscellaneous

- Hardware / Software Power Save mode.

- Input pin to Enable/Disable Power Save Mode.

- General Purpose Input/Output pins are available (GPIO[7:0]).

- INT pin associated with selectable GPIO inputs.

- Package: QFP20 144-pin package

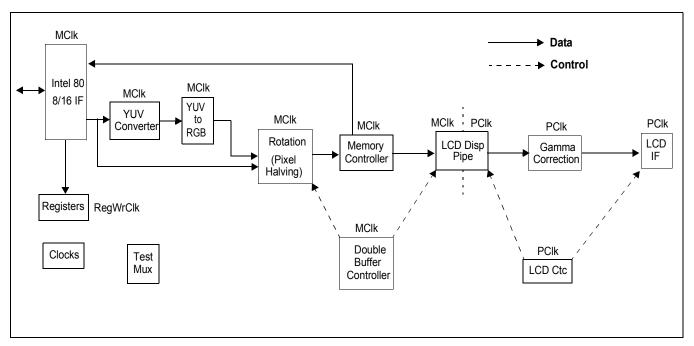

# 3 Block Diagram

Figure 3-1: Block Diagram

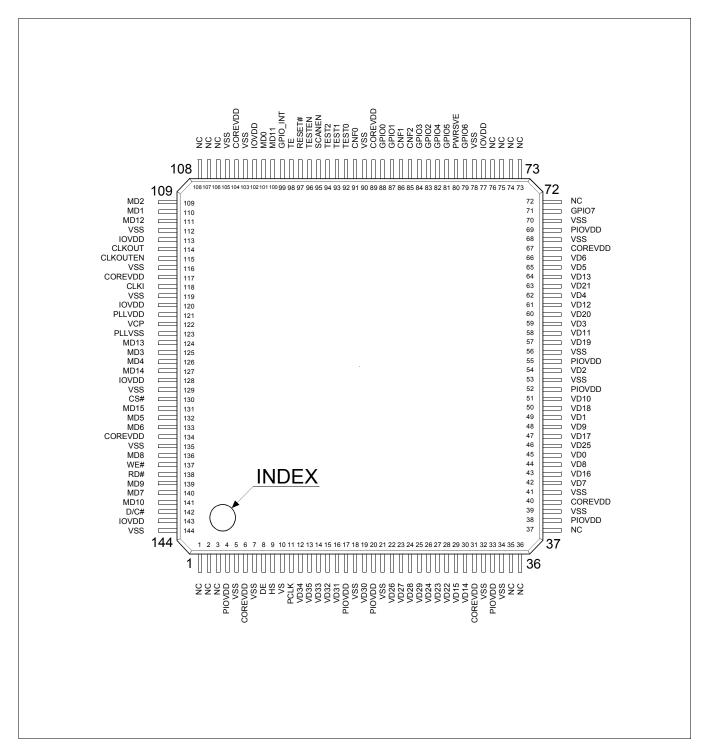

# 4 Pinout Diagram

### 4.1 Pin-Out

Figure 4-1: S1D13742 QFP20 Pinout (Top View)

## 4.2 Pin Descriptions

### Key:

### Pin Types

Input 0 Output

10 Bi-Directional (Input/Output)

Power pin

### **RESET# / Power Save Status**

High level output L Low level output Hi-Z High Impedance

Table 4-1: Cell Description

| Item    | Description                                                               |

|---------|---------------------------------------------------------------------------|

| HI      | H System <sup>1</sup> LVCMOS <sup>3</sup> Input Buffer                    |

| HIS     | H System LVCMOS Schmitt Input Buffer                                      |

| HID     | H System LVCMOS Input Buffer with pull-down resistor                      |

| НО      | H System LVCOMOS Output buffer                                            |

| НВ      | H System LVCMOS Bidirectional Buffer                                      |

| HBD     | H System LVCMOS Bidirectional Buffer with pull-down resistor              |

| HB_DSEL | H System LVCMOS Bidirectional Buffer with Drive Selector                  |

| LIDS    | L System <sup>2</sup> LVCMOS Schmitt Input Buffer with pull-down resistor |

| LITR    | L System Transparent Input Buffer                                         |

<sup>&</sup>lt;sup>1</sup> H System is IOVDD and PIOVDD (see Section 6, "D.C. Characteristics"). <sup>2</sup> L System is COREVDD (see Section 6, "D.C. Characteristics").

<sup>&</sup>lt;sup>3</sup> LVCMOS is Low Voltage CMOS (see Section 6, "D.C. Characteristics").

## 4.2.1 Intel 80 Host Interface

Table 4-2: Host Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin#                      | Cell | IO<br>Voltage | RESET#<br>State | Power<br>Save<br>Status | Description                                                                                                                                                                                                                                           |

|----------|------|----------------------------------|------|---------------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |      |                                  |      |               |                 |                         | Intel 80 Data lines.                                                                                                                                                                                                                                  |

|          |      | 131,127,<br>124,111,<br>100,141, |      |               |                 |                         | <ul> <li>For the S1D13742B00, when the 8-bit bus interface is selected by CNF1, MD[15:8] are pulled low by internal resistors.</li> <li>For the S1D13742B01, when the 8-bit bus</li> </ul>                                                            |

| MD[15:0] | Ю    | 139,136,<br>140,133,<br>132,126, | НВ   | IOVDD         | Hi-Z            | Hi-Z                    | interface is selected by CNF1, MD[15:8] should be connected to VSS.                                                                                                                                                                                   |

|          |      | 125,109,<br>110,101              |      |               |                 |                         | Note: The Host Data lines can be swapped (i.e. MD15 = MD0) using the CNF0 pin. For details, see Section 4.3, "Summary of Configuration Options" on page 17.                                                                                           |

| WE#      | I    | 137                              | HI   | IOVDD         | Input           | Input                   | This input pin is the Write Enable signal.                                                                                                                                                                                                            |

| RD#      | I    | 138                              | HI   | IOVDD         | Input           | Input                   | This input pin is the Read Enable signal.                                                                                                                                                                                                             |

| CS#      | Ι    | 130                              | HI   | IOVDD         | Input           | Input                   | This input pin is the Chip Select signal.                                                                                                                                                                                                             |

| D/C#     | I    | 142                              | НІ   | IOVDD         | Input           | Input                   | This input pin is used to select between Intel 80 address and data                                                                                                                                                                                    |

| TE       | 0    | 98                               | НО   | IOVDD         | L               | L                       | Tearing Effect: this pin will reflect the VSYNC, HSYNC or the OR'd combination status of the display.                                                                                                                                                 |

| GPIO_INT | 0    | 99                               | НО   | IOVDD         | L               | Output                  | This interrupt pin is associated with selected GPIO pins when configured as inputs or outputs. Interrupt functionality is not affected by Power Save. See Section 9.3.10, "General Purpose IO Pins Registers" on page 71 for operational description. |

| RESET#   | I    | 97                               | HI   | IOVDD         | Input           | Input                   | Active low input to set all internal registers to the default state and to force all signals to their inactive states.                                                                                                                                |

### 4.2.2 LCD Interface

Table 4-3: LCD Interface Pin Descriptions

| Pin Name | Туре | QFP<br>Pin #                                                                                                                                | Cell        | IO<br>Voltage | RESET#<br>State | Power<br>Save<br>Status | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|-----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VD[35:0] | Ю    | 13,12,14,15,<br>16,19,25,24,<br>23,22,46,26,<br>27,28,63,60,<br>57,50,47,43,<br>29,30,64,61,<br>58,51,48,44,<br>42,66,65,62,<br>59,54,49,45 | HB_<br>DSEL | PIOVDD        | L               | L                       | Panel Data bits 35-0. VD[35:0] are used for all modes. In 2 pixels/clock mode, VD[17:0] represent the 1st pixel sent in a 2 pixel/clock operation.  Note: The Panel Data Lines can be swapped (i.e. VD23 = VD0) using the VD Data Swap bit, REG[14h] bit 7.  Note: The VD output drive is selectable between 2.5mA and 6.5mA using the CNF2 pin. For details, see Section 4.3, "Summary of Configuration Options" on page 17. |

| VS       | 0    | 10                                                                                                                                          | НО          | PIOVDD        | Н               | L                       | This output pin is the Vertical Sync pulse                                                                                                                                                                                                                                                                                                                                                                                    |

| HS       | 0    | 9                                                                                                                                           | НО          | PIOVDD        | Н               | L                       | This output is the Horizontal Sync pulse                                                                                                                                                                                                                                                                                                                                                                                      |

| PCLK     | 0    | 11                                                                                                                                          | НО          | PIOVDD        | CLKI            | L                       | This output pin is the Data Clock                                                                                                                                                                                                                                                                                                                                                                                             |

| DE       | 0    | 8                                                                                                                                           | НО          | PIOVDD        | L               | Ĺ                       | This output pin is the Data Enable                                                                                                                                                                                                                                                                                                                                                                                            |

### Note

The LCD interface requires a separate power rail (PIOVDD) to support the configurable IO drive. For details, see the CNF2 description in Section 4.3, "Summary of Configuration Options" on page 17.

### Note

Input of VD[35:0] is used for production test only.

### 4.2.3 Clocks

Table 4-4: Clock Input Pin Descriptions

| Pin Name | Туре | QFP<br>Pin# | Cell | IO<br>Voltage | RESET#<br>State | Power<br>Save<br>Status | Description                                                                                      |

|----------|------|-------------|------|---------------|-----------------|-------------------------|--------------------------------------------------------------------------------------------------|

| CLKI     | -    | 118         | HIS  | IOVDD         | Input           | Input                   | MHz input for PLL operation or MHz input if PLL is bypassed                                      |

|          |      |             |      |               |                 |                         | Input frequency range: 1MHz ~ 33MHz                                                              |

| CLKOUT   | 0    | 114         | НО   | IOVDD         |                 | CLKI                    | This output pin represents the CLKI pin if enabled by CLKOUTEN. When disabled the output is low. |

| CLROOT   |      | 114         | 110  | IOVDD         | _               | OLINI                   | <b>Note:</b> this output is not affected by the various power save modes                         |

| CLKOUTEN | I    | 115         | HI   | IOVDD         | Input           | Input                   | This pin enables/disables the CLKOUT pin.                                                        |

## 4.2.4 Miscellaneous

Table 4-5: Miscellaneous Pin Descriptions

| Pin Name  | Туре | QFP<br>Pin#                                                       | Cell | IO<br>Voltage | RESET#<br>State | Power<br>Save<br>Status | Description                                                                                                                            |

|-----------|------|-------------------------------------------------------------------|------|---------------|-----------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| CNF[2:0]  | ı    | 85,86,91                                                          | HI   | IOVDD         | Input           | Input                   | These inputs are used for power-up configuration. For details, see Section 4.3, "Summary of Configuration Options" on page 17.         |

|           |      |                                                                   |      |               |                 |                         | Note: These pins must be connected directly to IOVDD or VSS.                                                                           |

| TESTEN    | I    | 96                                                                | LIDS | IOVDD         | _               | _                       | Test Enable input used for production test only This pin should be left unconnected for normal use.                                    |

| GPIO[7:0] | Ю    | 71,79,81,<br>82,84,83,<br>87,88                                   | HBD  | IOVDD         | L               | Pull<br>Down<br>Active  | These pins are general purpose input/output pins. These pins have internal pull-down resistors which can be controlled using REG[64h]. |

| PWRSVE    | ı    | 80                                                                | НІ   | IOVDD         | Input           | Input                   | This pin enables/disables the Standby Power Save Mode                                                                                  |

|           |      |                                                                   |      |               |                 |                         | When unused this pin must be connected to VSS.                                                                                         |

| TEST[2:0] | I    | 94,93,92                                                          | HID  | IOVDD         |                 |                         | These are Test Function pins and are used for production test only. These pins should be left unconnected for normal operation.        |

| SCANEN    | I    | 95                                                                | HID  | IOVDD         | _               | _                       | This is the Test Scan Enable input and is used for production test only. This pin should be left unconnected for normal operation.     |

| VCP       | I    | 122                                                               | LITR | PLLVDD        | _               | _                       | This is the PLL VCP Test pin and is used for production test only. This pin should be left unconnected for normal operation.           |

| NC        | _    | 1,2,3,<br>35,36,<br>37,72,<br>73,74,<br>75,76,<br>106,107,<br>108 | _    | _             | _               | _                       | These pins are not connected.                                                                                                          |

## 4.2.5 Power And Ground

Table 4-6: Power And Ground Pin Descriptions

| Pin Name | Туре | QFP<br>Pin #                                                                                 | Cell | Description                             |

|----------|------|----------------------------------------------------------------------------------------------|------|-----------------------------------------|

| COREVDD  | Р    | 6,31,40,67,89,<br>104,117,134                                                                | Р    | Core power supply                       |

| IOVDD    | Р    | 77,102,113,<br>120,128,143                                                                   | Р    | IO power supply for the host interface  |

| PIOVDD   | Р    | 4,17,20,33,38,<br>52,55,69                                                                   | Р    | IO power supply for the panel interface |

| PLLVDD   | Р    | 121                                                                                          | Р    | PLL power supply                        |

| PLLVSS   | Р    | 123                                                                                          | Р    | GND for PLL                             |

| VSS      | Р    | 5,7,18,21,32,<br>34,39,41,53,<br>56,68,70,78,<br>90,103,105,<br>112,116,119,<br>129, 135,144 | Р    | GND                                     |

## 4.3 Summary of Configuration Options

These pins are used for power-up configuration and must be connected directly to IOVDD or VSS. The state of CNF[2:0] may be changed at any time.

Table 4-7: Summary of Power-On/Reset Options

| Configuration | Power-On/Reset State                                                                            |                                                                                               |  |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Input         | 1 (connected to IOVDD)                                                                          | 0 (Connected to VSS)                                                                          |  |  |  |  |  |  |

| CNF0          | Host Data Lines are normal:  If CNF1 = 1, then D15 = D15, etc.  If CNF1 = 0, then D7 = D7, etc. | Host Data Lines are swapped: If CNF1 = 1, then D15 = D0, etc. If CNF1 = 0, then D7 = D0, etc. |  |  |  |  |  |  |

| CNF1          | Host Data is 16-bit                                                                             | Host Data is 8-bit                                                                            |  |  |  |  |  |  |

| CNF2          | PIOVDD output current (I <sub>OL2</sub> ) = 6.5mA                                               | PIOVDD output current (I <sub>OL2</sub> ) = 2.5mA                                             |  |  |  |  |  |  |

### Note

When CNF1=0, all Register access is 8-bit only.

When CNF1 =1 (16-bit): All Register access is 8-bit ONLY (the most significant byte on the data bus is ignored) except the Memory Data Port. Access to the Memory Data Port is 16-bit.

# 5 Pin Mapping

### 5.1 Intel 80 Data Pins

This function is controlled by CNF [1:0]

Table 5-1: S1D13742B00 Intel 80 Data Pin Mapping

| Pin Name | 16-Bit Data<br>No Swap<br>(CNF1=1, CNF0=1) | 16-Bit Data<br>Swapped<br>(CNF1=1, CNF0=0) | 8-Bit Data<br>No Swap<br>(CNF1=0, CNF0=1) | 8-Bit Data<br>Swapped<br>(CNF1=0, CNF0=0) |

|----------|--------------------------------------------|--------------------------------------------|-------------------------------------------|-------------------------------------------|

| MD15     | MD15                                       | MD0                                        | Pulled Low by<br>Internal Resistor        | Pulled Low by<br>Internal Resistor        |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| MD8      | MD8                                        | MD7                                        | Pulled Low by<br>Internal Resistor        | Pulled Low by<br>Internal Resistor        |

| MD7      | MD7                                        | MD8                                        | MD7                                       | MD0                                       |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| MD0      | MD0                                        | MD15                                       | MD0                                       | MD7                                       |

Table 5-2: S1D13742B01 Intel 80 Data Pin Mapping

| Pin Name | 16-Bit Data<br>No Swap<br>(CNF1=1, CNF0=1) | 16-Bit Data<br>Swapped<br>(CNF1=1, CNF0=0) | 8-Bit Data<br>No Swap<br>(CNF1=0, CNF0=1) | 8-Bit Data<br>Swapped<br>(CNF1=0, CNF0=0) |

|----------|--------------------------------------------|--------------------------------------------|-------------------------------------------|-------------------------------------------|

| MD15     | MD15                                       | MD0                                        | Hi-Z                                      | Hi-Z                                      |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| MD8      | MD8                                        | MD7                                        | Hi-Z                                      | Hi-Z                                      |

| MD7      | MD7                                        | MD8                                        | MD7                                       | MD0                                       |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| •        | •                                          | •                                          | •                                         | •                                         |

| MD0      | MD0                                        | MD15                                       | MD0                                       | MD7                                       |

## 5.2 LCD Interface Pin Mapping

Table 5-3: LCD Interface Pin Mapping for Mode 1 and Mode 2

|      |               |          | рр     |          |           | 18b      |        |          |

|------|---------------|----------|--------|----------|-----------|----------|--------|----------|

| Pin  | Single        | (18-bit) |        | (36-bit) | Single    | (18-bit) | Double | (36-bit) |

| Name | Normal        | Swap     | Normal | Swap     | Normal    | Swap     | Normal | Swap     |

| VS   | Vertical Sync |          |        |          |           |          |        |          |

| HS   |               |          |        | Horizor  | ntal Sync |          |        |          |

| PCLK |               |          |        | Pixel    | Clock     |          |        |          |

| DE   |               |          |        | Data     | Enable    |          |        |          |

| VD0  | B4            | R4       | B4     | R4       | B0        | R5       | В0     | R5       |

| VD1  | В0            | R3       | В0     | R3       | B1        | R4       | B1     | R4       |

| VD2  | B1            | R2       | B1     | R2       | B2        | R3       | B2     | R3       |

| VD3  | B2            | R1       | B2     | R1       | В3        | R2       | В3     | R2       |

| VD4  | В3            | R0       | В3     | R0       | B4        | R1       | B4     | R1       |

| VD5  | B4            | R4       | B4     | R4       | B5        | R0       | B5     | R0       |

| VD6  | G0            | G5       | G0     | G5       | G0        | G5       | G0     | G5       |

| VD7  | G1            | G4       | G1     | G4       | G1        | G4       | G1     | G4       |

| VD8  | G2            | G3       | G2     | G3       | G2        | G3       | G2     | G3       |

| VD9  | G3            | G2       | G3     | G2       | G3        | G2       | G3     | G2       |

| VD10 | G4            | G1       | G4     | G1       | G4        | G1       | G4     | G1       |

| VD11 | G5            | G0       | G5     | G0       | G5        | G0       | G5     | G0       |

| VD12 | R4            | B4       | R4     | B4       | R0        | B5       | R0     | B5       |

| VD13 | R0            | В3       | R0     | В3       | R1        | B4       | R1     | B4       |

| VD14 | R1            | B2       | R1     | B2       | R2        | В3       | R2     | В3       |

| VD15 | R2            | B1       | R2     | B1       | R3        | B2       | R3     | B2       |

| VD16 | R3            | В0       | R3     | В0       | R4        | B1       | R4     | B1       |

| VD17 | R4            | B4       | R4     | B4       | R5        | В0       | R5     | B0       |

| VD18 | driven 0      | driven 0 | B4     | R4       | driven 0  | driven 0 | В0     | R5       |

| VD19 | driven 0      | driven 0 | В0     | R3       | driven 0  | driven 0 | B1     | R4       |

| VD20 | driven 0      | driven 0 | B1     | R2       | driven 0  | driven 0 | B2     | R3       |

| VD21 | driven 0      | driven 0 | B2     | R1       | driven 0  | driven 0 | В3     | R2       |

| VD22 | driven 0      | driven 0 | В3     | R0       | driven 0  | driven 0 | B4     | R1       |

| VD23 | driven 0      | driven 0 | B4     | R4       | driven 0  | driven 0 | B5     | R0       |

| VD24 | driven 0      | driven 0 | G0     | G5       | driven 0  | driven 0 | G0     | G5       |

| VD25 | driven 0      | driven 0 | G1     | G4       | driven 0  | driven 0 | G1     | G4       |

| VD26 | driven 0      | driven 0 | G2     | G3       | driven 0  | driven 0 | G2     | G3       |

| VD27 | driven 0      | driven 0 | G3     | G2       | driven 0  | driven 0 | G3     | G2       |

| VD28 | driven 0      | driven 0 | G4     | G1       | driven 0  | driven 0 | G4     | G1       |

| VD29 | driven 0      | driven 0 | G5     | G0       | driven 0  | driven 0 | G5     | G0       |

| VD30 | driven 0      | driven 0 | R4     | B4       | driven 0  | driven 0 | R0     | B5       |

| VD31 | driven 0      | driven 0 | R0     | В3       | driven 0  | driven 0 | R1     | B4       |

| VD32 | driven 0      | driven 0 | R1     | B2       | driven 0  | driven 0 | R2     | В3       |

| VD33 | driven 0      | driven 0 | R2     | B1       | driven 0  | driven 0 | R3     | B2       |

| VD34 | driven 0      | driven 0 | R3     | В0       | driven 0  | driven 0 | R4     | B1       |

| VD35 | driven 0      | driven 0 | R4     | B4       | driven 0  | driven 0 | R5     | В0       |

## 5.3 LCD Interface Data Pins

This function is controlled by REG[14h] bit 7.

Table 5-4: LCD Interface Data Pin Mapping

| Pin Name | 36-Bit Data<br>No Swap<br>REG[14] b7=0 | 36-Bit Data<br>Swapped<br>REG[14] b7=1 | 18-Bit Data<br>No Swap<br>REG[14] b7=0 | 18-Bit Data<br>Swapped<br>REG[14] b7=1 |

|----------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|

| VD35     | VD35                                   | VD0                                    | Driven Low                             | Driven Low                             |

| •        | •                                      | •                                      | •                                      | •                                      |

| •        | •                                      | •                                      | •                                      | •                                      |

| •        | •                                      | •                                      | •                                      | •                                      |

| VD18     | VD18                                   | VD17                                   | Driven Low                             | Driven Low                             |

| VD17     | VD17                                   | VD18                                   | VD17                                   | VD0                                    |

| •        | •                                      | •                                      | •                                      | •                                      |

| •        | •                                      | •                                      | •                                      | •                                      |

| •        | •                                      | •                                      | •                                      | •                                      |

| VD0      | VD0                                    | VD35                                   | VD0                                    | VD17                                   |

## 6 D.C. Characteristics

## 6.1 Absolute Maximum Ratings

Table 6-1: Absolute Maximum Ratings

| Symbol               | Parameter               | Rating                  | Units |

|----------------------|-------------------------|-------------------------|-------|

| Core V <sub>DD</sub> | Core Supply Voltage     | VSS - 0.3 ~ 2.0         | V     |

| PLL V <sub>DD</sub>  | PLL Supply Voltage      | VSS - 0.3 ~ 2.0         | V     |

| IO V <sub>DD</sub>   | Host IO Supply Voltage  | COREVDD ~ 4.0           | V     |

| PIO V <sub>DD</sub>  | Panel IO Supply Voltage | COREVDD ~ 4.0           | V     |

| V <sub>IN</sub>      | Input Signal Voltage    | VSS - 0.3 ~ IOVDD + 0.3 | V     |

| V <sub>OUT</sub>     | Output Signal Voltage   | VSS - 0.3 ~ IOVDD + 0.3 | V     |

| I <sub>OUT</sub>     | Output Signal Current   | ±10                     | mA    |

## **6.2 Recommended Operating Conditions**

Table 6-2: Recommended Operating Conditions

| Symbol               | Parameter               | Condition | Min  | Тур  | Max   | Units |

|----------------------|-------------------------|-----------|------|------|-------|-------|

| Core V <sub>DD</sub> | Core Supply Voltage     | VSS = 0 V | 1.40 | 1.50 | 1.60  | V     |

| PLL V <sub>DD</sub>  | PLL Supply Voltage      | VSS = 0 V | 1.40 | 1.50 | 1.60  | V     |

| IO V <sub>DD</sub>   | Host IO Supply Voltage  | VSS = 0 V | 1.65 | _    | 3.6   | V     |

| PIO V <sub>DD</sub>  | Panel IO Supply Voltage | VSS = 0 V | 1.65 | _    | 3.6   | V     |

| V <sub>IN</sub>      | Input Voltage           | _         | VSS  | _    | IOVDD | V     |

| T <sub>OPR</sub>     | Operating Temperature   | _         | -40  | +25  | +85   | °C    |

| T <sub>stg</sub>     | Storage Temperature     | _         | -65  |      | +150  | °C    |

### Note

There are no special Power On/Off requirements with respect to sequencing the various VDD pins. There are also no special requirements for the IO signals, however Inputs should not be floating. If the input signals were to power up in a valid cycle, the S1D13742 would decode the cycle.

### 6.3 Electrical Characteristics

The following characteristics are for: IOVDD. VSS = 0V,  $T_{OPR} = -40$  to +85°C.

*Table 6-3: Electrical Characteristics for IOVDD or PIOVDD* =  $1.8V \pm 0.15V$

| Symbol              | Parameter                    | Condition                                                              | Min           | Тур   | Max    | Units |

|---------------------|------------------------------|------------------------------------------------------------------------|---------------|-------|--------|-------|

| I <sub>QALL</sub>   | Quiescent Current            | CLKI stopped (grounded), Sleep Mode enabled, all power supplies active |               | 100   | _      | μА    |

| I <sub>PLL</sub>    | PLL Current                  | f <sub>PLL</sub> = 54MHz                                               | _             | 500   | 1000   | μΑ    |

| I <sub>CORE</sub>   | Operation Peak Current       | COREVDD Power Pin                                                      | _             | _     | 62     | mA    |

| P <sub>CORE</sub>   | Core Typical Operating Power |                                                                        | _             | 9.15  | _      | mW    |

| P <sub>PLL</sub>    | PLL Typical Operating Power  | see Note 1                                                             | _             | 0.7   | _      | mW    |

| P <sub>PIO</sub>    | PIO Typical Operating Power  | See Note 1                                                             | _             | 2.8   | _      | mW    |

| P <sub>HIO</sub>    | HIO Typical Operating Power  |                                                                        | _             | 0.018 | _      | mW    |

| P <sub>CORE</sub>   | Core Typical Operating Power |                                                                        | _             | 10.9  | _      | mW    |

| P <sub>PLL</sub>    | PLL Typical Operating Power  | and Note 2                                                             | _             | 0.77  | _      | mW    |

| P <sub>PIO</sub>    | PIO Typical Operating Power  | see Note 2                                                             | _             | 2.124 | _      | mW    |

| P <sub>HIO</sub>    | HIO Typical Operating Power  |                                                                        | _             | 0.001 | _      | mW    |

| I <sub>IZ</sub>     | Input Leakage Current        | _                                                                      | -5            | _     | 5      | μА    |

| I <sub>OZ</sub>     | Output Leakage Current       | _                                                                      | -5            | _     | 5      | μА    |

| IOV <sub>OH2</sub>  | High Level Output Voltage    | IOV <sub>DD</sub> = min<br>I <sub>OH2</sub> = -2.5mA                   | IOVDD - 0.40  | _     | IOVDD  | V     |

| PIOV <sub>OH2</sub> | High Level Output Voltage    | PIOVDD = min<br>I <sub>OH2</sub> = -2.5mA                              | PIOVDD - 0.40 | _     | PIOVDD | V     |

| PIOV <sub>OH4</sub> | High Level Output Voltage    | PIOVDD = min<br>I <sub>OH2</sub> = -6.5mA                              | PIOVDD - 0.40 | _     | PIOVDD | V     |

| IOV <sub>OL2</sub>  | Low Level Output Voltage     | IOVDD = min<br>I <sub>OL2</sub> = 2.5mA                                | VSS           | _     | 0.40   | V     |

| PIOV <sub>OL2</sub> | Low Level Output Voltage     | PIOVDD = min<br>I <sub>OL2</sub> = 2.5mA                               | VSS           | _     | 0.40   | V     |

| PIOV <sub>OL4</sub> | Low Level Output Voltage     | PIOVDD = min<br>I <sub>OL2</sub> = 6.5mA                               | VSS           | _     | 0.40   | V     |

| IOV <sub>IH</sub>   | High Level Input Voltage     | CMOS Input                                                             | 1.27          | _     | _      | V     |

| PIOV <sub>IH</sub>  | High Level Input Voltage     | CMOS Input                                                             | 1.27          | _     | _      | V     |

| IOV <sub>IL</sub>   | Low Level Input Voltage      | CMOS Input                                                             | _             | _     | 0.57   | V     |

| PIOV <sub>IL</sub>  | Low Level Input Voltage      | CMOS Input                                                             |               | _     | 0.57   | V     |

| IOV <sub>T+</sub>   | Positive Trigger Voltage     | CMOS Schmitt                                                           | 0.57          | _     | 1.56   | V     |

| IOV <sub>T-</sub>   | Negative Trigger Voltage     | CMOS Schmitt                                                           | 0.33          | _     | 1.27   | V     |

| IO V <sub>H</sub>   | Hysteresis Voltage           | CMOS Schmitt                                                           | 0.24          | _     | _      | V     |

| R <sub>PU1</sub>    | Pull-Up Resistance Type1     | V <sub>I</sub> = VSS                                                   | 40            | 100   | 240    | kΩ    |

| R <sub>PD1</sub>    | Pull-Down Resistance Type1   | V <sub>I</sub> = VDD                                                   | 40            | 100   | 240    | kΩ    |

| R <sub>PU2</sub>    | Pull-Up Resistance Type2     | V <sub>I</sub> = VSS                                                   | 80            | 200   | 480    | kΩ    |

| R <sub>PD2</sub>    | Pull-Down Resistance Type2   | V <sub>I</sub> = VDD                                                   | 80            | 200   | 480    | kΩ    |

| C <sub>IO</sub>     | Pin Capacitance              | f = 1MHz, VDD = 0V                                                     | _             | _     | 8      | pF    |

### Note

- Typical Operating Current Environment: 352x416 K2 TFT panel with PCLK divide by 4. SYSCLK=48.5MHz from PLL, PLL Source from 19.2MHz CLKI input. 18bpp memory storage. COREVDD and PLLVDD to 1.5V, HIOVDD, PIOVDD to 1.8V

- Typical Operating Current Environment: 800 x 480 TFT panel with PCLK divide by 3. SYSCLK= 59MHz from PLL, PLL Source from 12MHz CLKI input. 16bpp memory storage. COREVDD and PLLVDD to 1.5V, HIOVDD, PIOVDD to 1.8V

The following characteristics are for: IOVDD. VSS = 0V,  $T_{OPR} = -40$  to +85 °C.

*Table 6-4: Electrical Characteristics for IOVDD or PIOVDD* =  $2.8V \pm 0.14V$

| Symbol              | Parameter                  | Condition                                                                    | Min              | Тур | Max    | Units |

|---------------------|----------------------------|------------------------------------------------------------------------------|------------------|-----|--------|-------|

| I <sub>QALL</sub>   | Quiescent Current          | CLKI stopped (grounded),<br>Sleep Mode enabled, all power<br>supplies active | _                | 120 | _      | μА    |

| I <sub>PLL</sub>    | PLL Current                | f <sub>PLL</sub> = 54MHz                                                     | _                | 500 | 1000   | μΑ    |

| I <sub>CORE</sub>   | Operation Peak Current     | COREVDD Power Pin                                                            | _                | _   | 62     | mA    |

| I <sub>IZ</sub>     | Input Leakage Current      | _                                                                            | -5               | _   | 5      | μΑ    |

| I <sub>OZ</sub>     | Output Leakage Current     | _                                                                            | -5               | _   | 5      | μΑ    |

| IOV <sub>OH2</sub>  | High Level Output Voltage  | $IOV_{DD}$ = min<br>$I_{OH2}$ = -3.6mA                                       | IOVDD - 0.40     | _   | IOVDD  | V     |

| PIOV <sub>OH2</sub> | High Level Output Voltage  | PIOVDD = min<br>I <sub>OH2</sub> = -3.6mA                                    | PIOVDD -<br>0.40 | _   | PIOVDD | V     |

| PIOV <sub>OH4</sub> | High Level Output Voltage  | PIOVDD = min<br>I <sub>OH2</sub> = -10.8mA                                   | PIOVDD -<br>0.40 | _   | PIOVDD | V     |

| IOV <sub>OL2</sub>  | Low Level Output Voltage   | IOVDD = min<br>I <sub>OL2</sub> = 3.6mA                                      | VSS              | _   | 0.40   | V     |

| PIOV <sub>OL2</sub> | Low Level Output Voltage   | PIOVDD = min<br>I <sub>OL2</sub> = 3.6mA                                     | VSS              | _   | 0.40   | V     |

| PIOV <sub>OL4</sub> | Low Level Output Voltage   | PIOVDD = min<br>I <sub>OL2</sub> = 10.8mA                                    | VSS              | _   | 0.40   | V     |

| IOV <sub>IH</sub>   | High Level Input Voltage   | CMOS Input                                                                   | 1.75             | _   | _      | V     |

| PIOV <sub>IH</sub>  | High Level Input Voltage   | CMOS Input                                                                   | 1.75             | _   | _      | V     |

| IOV <sub>IL</sub>   | Low Level Input Voltage    | CMOS Input                                                                   | _                | _   | 0.70   | V     |

| PIOV <sub>IL</sub>  | Low Level Input Voltage    | CMOS Input                                                                   | _                | _   | 0.70   | V     |

| IOV <sub>T+</sub>   | Positive Trigger Voltage   | CMOS Schmitt                                                                 | 0.93             | _   | 2.36   | V     |

| IOV <sub>T-</sub>   | Negative Trigger Voltage   | CMOS Schmitt                                                                 | 0.53             | _   | 1.92   | V     |

| IO V <sub>H</sub>   | Hysteresis Voltage         | CMOS Schmitt                                                                 | 0.40             | _   | _      | V     |

| R <sub>PU1</sub>    | Pull-Up Resistance Type1   | V <sub>I</sub> = VSS                                                         | 24               | 60  | 144    | kΩ    |

| R <sub>PD1</sub>    | Pull-Down Resistance Type1 | V <sub>I</sub> = VDD                                                         | 24               | 60  | 144    | kΩ    |

| R <sub>PU2</sub>    | Pull-Up Resistance Type2   | V <sub>I</sub> = VSS                                                         | 48               | 120 | 288    | kΩ    |

| R <sub>PD2</sub>    | Pull-Down Resistance Type2 | V <sub>I</sub> = VDD                                                         | 48               | 120 | 288    | kΩ    |

| C <sub>IO</sub>     | Pin Capacitance            | f = 1MHz, VDD = 0V                                                           | _                | _   | 8      | pF    |

### Note

- 1. Typical Operating Current Environment:

- 352x416 K2 TFT panel with PCLK divide by 4. SYSCLK=48.5MHz from PLL, PLL Source from 19.2MHz CLKI input. 18bpp memory storage. COREVDD and PLLVDD to 1.5V, HIOVDD, PIOVDD to 2.8V

- Typical Operating Current Environment: 800 x 480 TFT panel with PCLK divide by 3. SYSCLK= 59MHz from PLL, PLL Source from 12MHz CLKI input. 16bpp memory storage. COREVDD and PLLVDD to 1.5V, HIOVDD, PIOVDD to 2.8V

The following characteristics are for: IOVDD, VSS = 0V,  $T_{OPR}$  = -40 to +85°C.

Table 6-5: Electrical Characteristics for IOVDD or PIOVDD =  $3.3V \pm 0.3V$

| Symbol              | Parameter                  | Condition                                  | Min              | Тур | Max    | Units |

|---------------------|----------------------------|--------------------------------------------|------------------|-----|--------|-------|

| I <sub>QALL</sub>   | Quiescent Current          | Quiescent Conditions                       | _                | 160 | _      | μА    |

| I <sub>PLL</sub>    | PLL Current                | f <sub>PLL</sub> = 54MHz                   | _                | 500 | 1000   | μА    |

| I <sub>CORE</sub>   | Operation Peak Current     | COREVDD Power Pin                          | _                | _   | 62     | mA    |

| I <sub>IZ</sub>     | Input Leakage Current      | _                                          | -5               | _   | 5      | μΑ    |

| I <sub>OZ</sub>     | Output Leakage Current     | _                                          | -5               | _   | 5      | μΑ    |

| IOV <sub>OH2</sub>  | High Level Output Voltage  | $IOV_{DD} = min$<br>$I_{OH2} = -4.0mA$     | IOVDD - 0.40     | _   | IOVDD  | V     |

| PIOV <sub>OH2</sub> | High Level Output Voltage  | PIOVDD = min<br>I <sub>OH2</sub> = -4.0mA  | PIOVDD -<br>0.40 | _   | PIOVDD | V     |

| PIOV <sub>OH4</sub> | High Level Output Voltage  | PIOVDD = min<br>I <sub>OH2</sub> = -12.0mA | PIOVDD -<br>0.40 | _   | PIOVDD | V     |

| IOV <sub>OL2</sub>  | Low Level Output Voltage   | IOVDD = min<br>I <sub>OL2</sub> = 4.0mA    | VSS              | _   | 0.40   | V     |

| PIOV <sub>OL2</sub> | Low Level Output Voltage   | PIOVDD = min<br>I <sub>OL2</sub> = 4.0mA   | VSS              | _   | 0.40   | V     |

| PIOV <sub>OL4</sub> | Low Level Output Voltage   | PIOVDD = min<br>I <sub>OL2</sub> = 12.0mA  | VSS              | _   | 0.40   | V     |

| IOV <sub>IH</sub>   | High Level Input Voltage   | CMOS Input                                 | 2.20             | _   | _      | V     |

| PIOV <sub>IH</sub>  | High Level Input Voltage   | CMOS Input                                 | 2.20             | _   | _      | V     |

| IOV <sub>IL</sub>   | Low Level Input Voltage    | CMOS Input                                 | _                | _   | 0.80   | V     |

| PIOV <sub>IL</sub>  | Low Level Input Voltage    | CMOS Input                                 | _                | _   | 0.80   | V     |

| IOV <sub>T+</sub>   | Positive Trigger Voltage   | CMOS Schmitt                               | 1.40             | _   | 2.70   | V     |

| IOV <sub>T-</sub>   | Negative Trigger Voltage   | CMOS Schmitt                               | 0.60             | _   | 1.80   | V     |

| IO V <sub>H</sub>   | Hysteresis Voltage         | CMOS Schmitt                               | 0.45             | _   | _      | V     |

| R <sub>PU1</sub>    | Pull-Up Resistance Type1   | V <sub>I</sub> = VSS                       | 20               | 50  | 120    | kΩ    |

| R <sub>PD1</sub>    | Pull-Down Resistance Type1 | V <sub>I</sub> = VDD                       | 20               | 50  | 120    | kΩ    |

| R <sub>PU2</sub>    | Pull-Up Resistance Type2   | V <sub>I</sub> = VSS                       | 40               | 100 | 240    | kΩ    |

| R <sub>PD2</sub>    | Pull-Down Resistance Type2 | V <sub>I</sub> = VDD                       | 40               | 100 | 240    | kΩ    |

| C <sub>IO</sub>     | Pin Capacitance            | f = 1MHz, VDD = 0V                         | _                |     | 8      | pF    |

## 7 A.C. Characteristics

### Conditions:

$$\begin{split} & \text{IOVDD} = \text{PIOVDD} = 1.8V \pm 0.15V \text{ or } 2.8V \pm 0.14V \\ & T_A = \text{-}40^\circ \text{ C to } 85^\circ \text{ C} \\ & T_{rise} \text{ and } T_{fall} \text{ for all inputs except Schmitt and CLKI must be } \leq 50 \text{ ns } (10\% \sim 90\%) \\ & T_{rise} \text{ and } T_{fall} \text{ for all Schmitt must be } \leq 5 \text{ ms } (10\% \sim 90\%) \\ & C_L = 8 \text{pF} \sim 30 \text{pF (MD[15:0])} \\ & C_L = 15 \text{pF (TE, GPIO\_INT, CLKOUT)} \\ & C_L = 30 \text{pF (LCD Panel/GPIO Interface)} \end{split}$$

## 7.1 Clock Timing

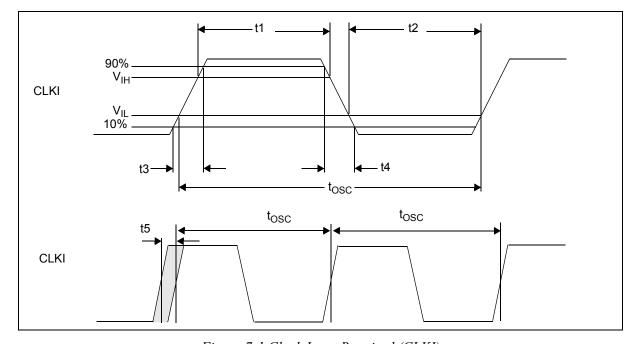

### 7.1.1 Input Clocks

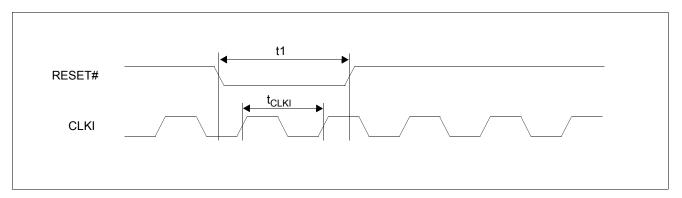

Figure 7-1 Clock Input Required (CLKI)

| Table 7-1  | Clock In   | put Requir  | ements     | (CLKI) |

|------------|------------|-------------|------------|--------|

| I WOLC / I | CIOCIV III | pul Iloquii | CITICITIES | CLILI  |

| Symbol             | Parameter                                          | Min                 | Тур                | Max                 | Units |

|--------------------|----------------------------------------------------|---------------------|--------------------|---------------------|-------|

| f <sub>OSC</sub>   | Input clock frequency - PLL used for System Clock  | 1                   |                    | 66                  | MHz   |

| (see note 6)       | Input clock frequency - CLKI used for System Clock | 0                   |                    | 68.90               | MHz   |

| tosc               | Input clock period                                 |                     | 1/f <sub>OSC</sub> | _                   | μS    |

| t1                 | Input clock pulse width high                       | 0.4t <sub>OSC</sub> | _                  | 0.6t <sub>OSC</sub> | μS    |

| t2                 | Input clock pulse width low                        | 0.4t <sub>OSC</sub> | _                  | 0.6t <sub>OSC</sub> | μS    |

| t3                 | Input clock rise time (10% - 90%)                  |                     | _                  | 5.0                 | ns    |

| t4                 | Input clock fall time (90% - 10%)                  | _                   | _                  | 5.0                 | ns    |

| t5                 | Input clock period jitter (see notes 2 and 4)      | -300                |                    | 300                 | ps    |

| t6<br>(see note 1) | Input clock cycle jitter (see notes 3 and 4)       | -300                |                    | 300                 | ps    |

- 1. t6 = 2\*t<sub>OSC</sub>

- 2. The input clock period jitter is the displacement relative to the center period (reciprocal of the center frequency).

- 3. The input clock cycle jitter is the difference in period between adjacent cycles.

- 4. The jitter characteristics must satisfy both the t5 and t6 characteristics

- 5. Input Duty cycle is not critical and can be 40/60

- 6. The minimum System Clock frequency required for correct operation depends on the cycle length of the Intel 80 interface. See Section 8.4, "Setting SYSCLK and PCLK" on page 42 for more details.

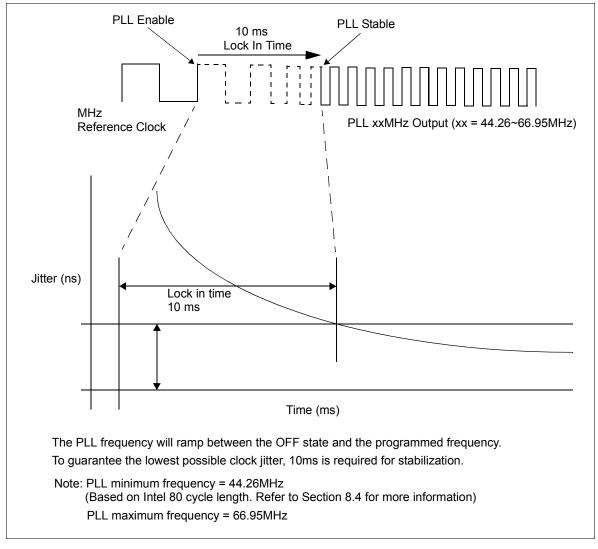

### 7.1.2 PLL Clock

The PLL circuit is an analog circuit and is very sensitive to noise on the input clock waveform or the power supply. Noise on the clock or the supplied power may cause the operation of the PLL circuit to become unstable or increase the jitter.

Due to these noise constraints, it is highly recommended that the power supply traces or the power plane for the PLL be isolated from those of other power supplies. Filtering should also be used to keep the power as clean as possible. The jitter of the input clock waveform should be as small as possible.

Figure 7-2: PLL Start-Up Time

Table 7-2: PLL Clock Requirements

| Symbol             | Parameter                      | Min                | Max   | Units |

|--------------------|--------------------------------|--------------------|-------|-------|

| f <sub>PLL</sub>   | PLL output clock frequency     | 44.26 <sup>1</sup> | 66.95 | MHz   |

| t <sub>PJref</sub> | PLL output clock period jitter | -3                 | 3     | %     |

| t <sub>PDuty</sub> | PLL output clock duty cycle    | 40                 | 60    | %     |

| t <sub>PStal</sub> | PLL output stable time         |                    | 10    | ms    |

<sup>&</sup>lt;sup>1</sup> Refer to Section 8.4, "Setting SYSCLK and PCLK" on page 42.

## 7.2 RESET# Timing

Figure 7-3 S1D13742 RESET# Timing

Table 7-3 S1D13742 RESET# Timing

| Symbol | Parameter                | Min | Max | Units |

|--------|--------------------------|-----|-----|-------|

| t1     | Active Reset Pulse Width | 1   | _   | CLKI  |

## 7.3 Host interface Timing

## 7.3.1 Intel 80 Interface Timing - 1.8 Volt

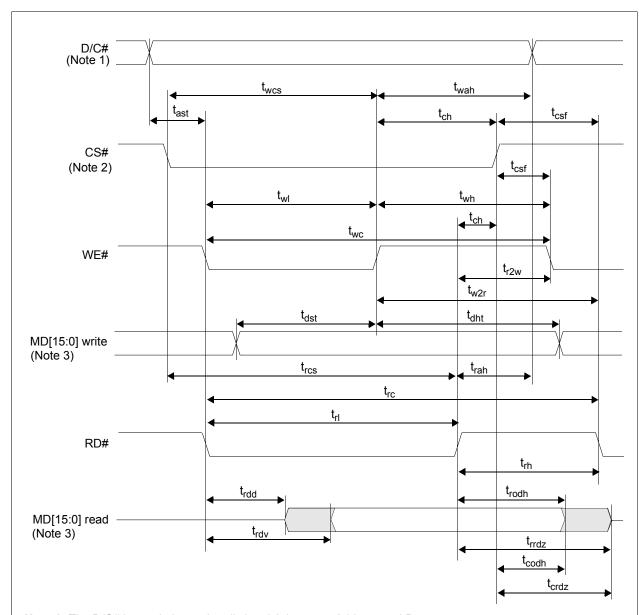

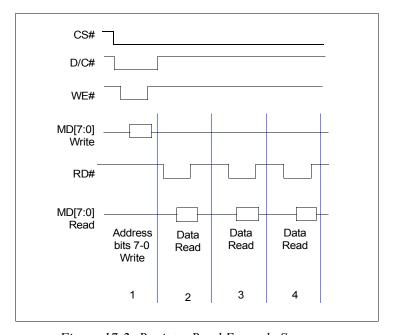

**Note 1:** The D/C# input pin is used to distinguish between Address and Data.

**Note 2:** The CS# pin can be kept low between write and read pulses as the register addresses will auto-increment. The register address will auto-increment in word increments for all register access except the Memory Data Port. Writes to the Memory Data Port will not increment the register address to support burst data writes to memory.

Note 3: When CNF1=0, only MD[7:0] are used.

When CNF1=1, MD[15:0] are used for accesses to the Memory Data Port. MD[7:0] are used for all other accesses.

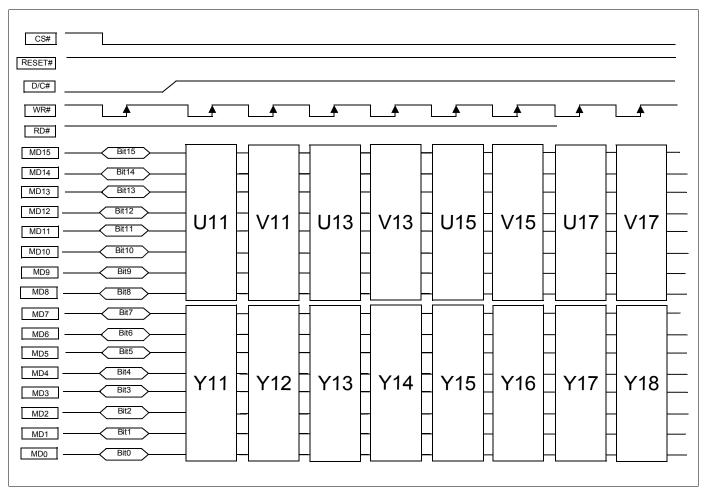

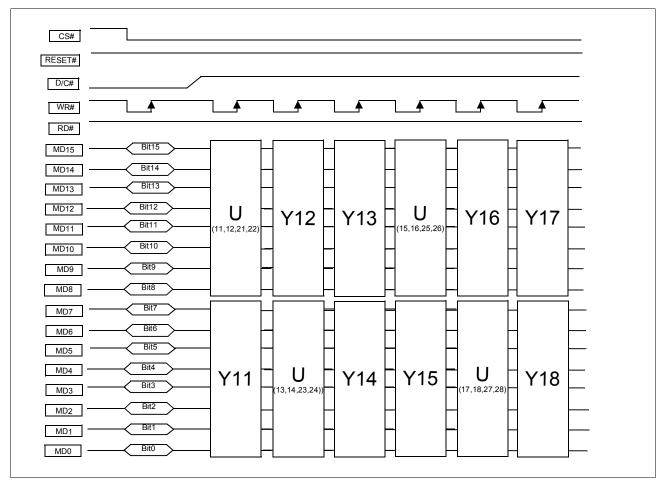

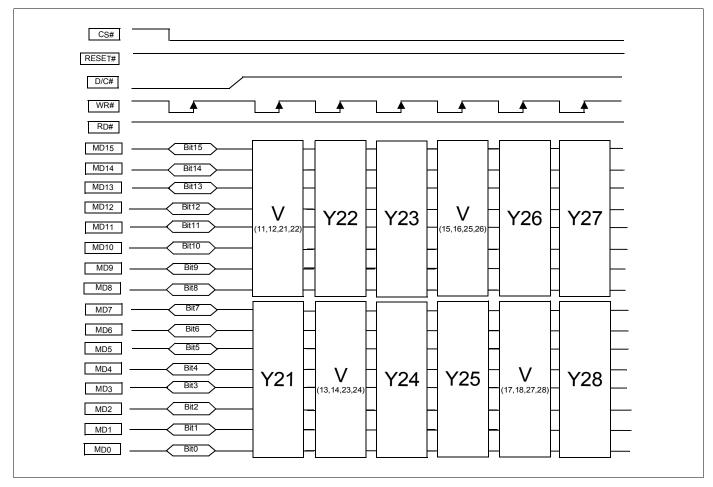

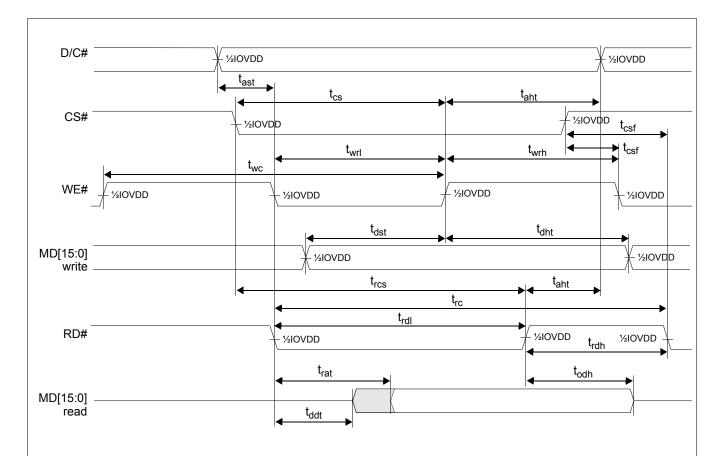

Figure 7-4: Intel 80 Input A.C. Characteristics - 1.8 Volt

Table 7-4: Intel 80 Input A.C. Characteristics - 1.8 Volt

| Signal   | Symbol            | Parameter                                  | Min                               | Max          | Unit | Description |

|----------|-------------------|--------------------------------------------|-----------------------------------|--------------|------|-------------|

|          | t <sub>ast</sub>  | Address setup time (read/write)            | 1                                 | _            | ns   |             |

| D/C#     | t <sub>wah</sub>  | Address hold time (write)                  | 5                                 | _            | ns   |             |

|          | t <sub>rah</sub>  | Address hold time (read)                   | 29                                | _            | ns   |             |

|          | t <sub>wcs</sub>  | Chip Select setup time (write)             | t <sub>wl</sub>                   | _            | ns   |             |

| CS#      | t <sub>rcs</sub>  | Chip Select setup time (read)              | t <sub>rl</sub>                   | _            | ns   |             |

| US#      | t <sub>ch</sub>   | Chip Select hold time (read/write)         | 0                                 | _            | ns   |             |

|          | t <sub>csf</sub>  | Chip Select Wait time (read/write)         | 1                                 | _            | ns   |             |

|          |                   | Register Write cycle                       | 12                                | _            | ns   |             |

|          | t <sub>wc</sub>   | LUT write cycle                            | 2SYSCLK + 1                       | _            | ns   |             |

| WE#      |                   | Memory write cycle                         | 2SYSCLK + 1                       | _            | ns   |             |

| V V C#   | t <sub>wl</sub>   | Pulse low duration                         | 5                                 | _            | ns   |             |

|          | t <sub>wh</sub>   | Pulse high duration                        | t <sub>wc</sub> - t <sub>wl</sub> | _            | ns   |             |

|          | t <sub>w2r</sub>  | WR# rising edge to RD# falling edge        | 11                                | _            | ns   | Note 1      |

|          | t <sub>r2w</sub>  | RD# rising edge to WR# falling edge        | 26                                | _            | ns   | Note 2      |

|          | t <sub>rc</sub>   | Read cycle                                 | t <sub>rl</sub> + t <sub>rh</sub> | _            | ns   |             |

| RD#      | t <sub>rl</sub>   | Pulse low duration                         | t <sub>rdv</sub>                  | _            | ns   |             |

|          |                   | Pulse high duration for Registers          | 35                                | _            | ns   |             |

|          | t <sub>rh</sub>   | Pulse high duration for Memory and LUT     | 1SYSCLK + 26                      | _            | ns   |             |

|          | t <sub>dst</sub>  | Write data setup time                      | 4                                 | _            | ns   |             |

|          | t <sub>dht</sub>  | Write data hold time                       | 5                                 | _            | ns   |             |

|          | t <sub>rodh</sub> | Read data hold time from RD# rising edge   | 11                                | _            | ns   |             |

|          | t <sub>rrdz</sub> | RD# rising edge to MD Hi-Z                 | _                                 | 31           | ns   |             |

|          | t <sub>codh</sub> | Read data hold time from CS# rising edge   | 1                                 | _            | ns   |             |

|          | t <sub>crdz</sub> | CS# rising edge to MD Hi-Z                 | _                                 | 8            | ns   |             |

| MD[15:0] |                   | RD# falling edge to MD valid for Registers | _                                 | 16           | ns   |             |

| (Note 3) | t <sub>rdv</sub>  | RD# falling edge to MD valid for LUT       | _                                 | 4SYSCLK + 26 | ns   | CL=30pF     |

|          |                   | RD# falling edge to MD valid for Memory    | _                                 | 5SYSCLK + 19 | ns   |             |

|          |                   | RD# falling edge to MD valid for Registers | _                                 | 11           | ns   |             |

|          |                   | RD# falling edge to MD valid for LUT       | _                                 | 4SYSCLK + 21 | ns   | CL = 8pF    |

|          |                   | RD# falling edge to MD valid for Memory    |                                   | 5SYSCLK + 14 | ns   |             |

|          | t                 | RD# falling edge to MD driven              | 4                                 | _            | ns   | CL=30pF     |

|          | t <sub>rdd</sub>  | RD# falling edge to MD driven              | 3                                 | _            | ns   | CL = 8pF    |

### Note

- 1. For a read cycle after a write cycle, MD[15:0] must be driven Hi-Z a maximum of t<sub>rdd</sub> after the falling edge of RD#.

- 2. For a write cycle after a read cycle, MD[15:0] should not be driven by the host until  $t_{rrdz}$  after the rising edge of RD#.

- 3. When CNF1=0, only MD[7:0] are used. When CNF1=1, MD[7:0] are used for all accesses except for the Memory Data Port when MD[15:0] are used.

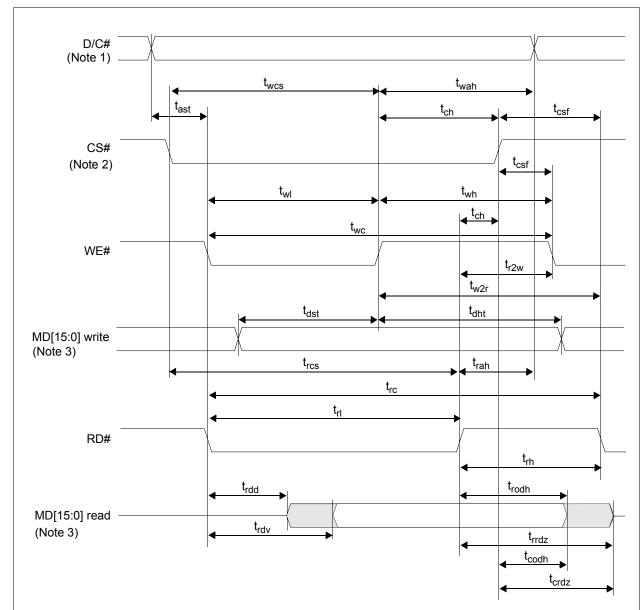

## 7.3.2 Intel 80 Interface Timing - 3.3 Volt

Note 1: The D/C# input pin is used to distinguish between Address and Data.

**Note 2:** The CS# pin can be kept low between write and read pulses as the register addresses will auto-increment. The register address will auto-increment in word increments for all register access except the Memory Data Port. Writes to the Memory Data Port will not increment the register address to support burst data writes to memory.

Note 3: When CNF1=0, only MD[7:0] are used.

When CNF1=1, MD[15:0] are used for accesses to the Memory Data Port. MD[7:0] are used for all other accesses.

Figure 7-5: Intel 80 Input A.C. Characteristics - 3.3 Volt

Table 7-5: Intel 80 Input A.C. Characteristics - 3.3 Volt

| Signal       | Symbol            | Parameter                                  | Min                               | Max          | Unit | Description |

|--------------|-------------------|--------------------------------------------|-----------------------------------|--------------|------|-------------|

|              | t <sub>ast</sub>  | Address setup time (read/write)            | 1                                 | _            | ns   |             |

| D/C#         | t <sub>wah</sub>  | Address hold time (write)                  | 5                                 | _            | ns   |             |

|              | t <sub>rah</sub>  | Address hold time (read)                   | 29                                | _            | ns   |             |

|              | t <sub>wcs</sub>  | Chip Select setup time (write)             | t <sub>wl</sub>                   | _            | ns   |             |

| CS#          | t <sub>rcs</sub>  | Chip Select setup time (read)              | t <sub>rl</sub>                   | _            | ns   |             |

| US#          | t <sub>ch</sub>   | Chip Select hold time (read/write)         | 0                                 | _            | ns   |             |

|              | t <sub>csf</sub>  | Chip Select Wait time (read/write)         | 1                                 | _            | ns   |             |

|              |                   | Register Write cycle                       | 12                                | _            | ns   |             |

|              | t <sub>wc</sub>   | LUT write cycle                            | 2SYSCLK + 1                       | _            | ns   |             |

| WE#          |                   | Memory write cycle                         | 2SYSCLK + 1                       | _            | ns   |             |

| VV <i>⊏#</i> | t <sub>wl</sub>   | Pulse low duration                         | 5                                 | _            | ns   |             |

|              | t <sub>wh</sub>   | Pulse high duration                        | t <sub>wc</sub> - t <sub>wl</sub> | _            | ns   |             |

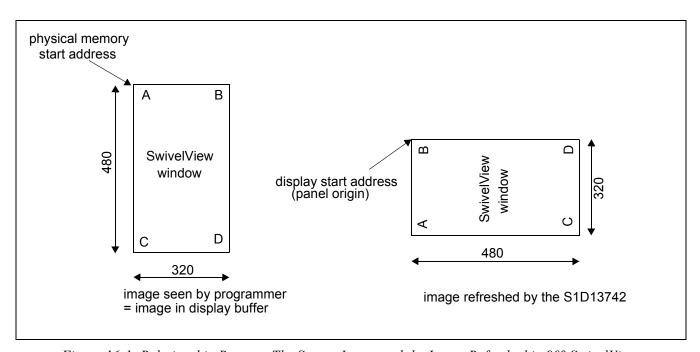

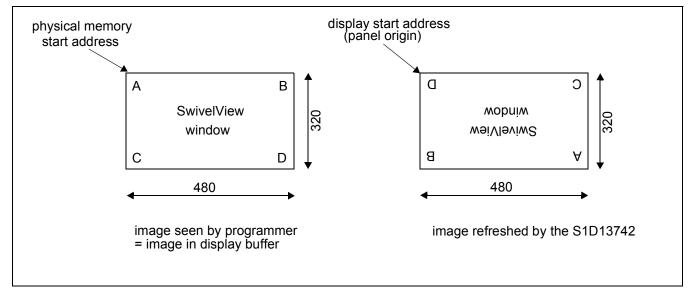

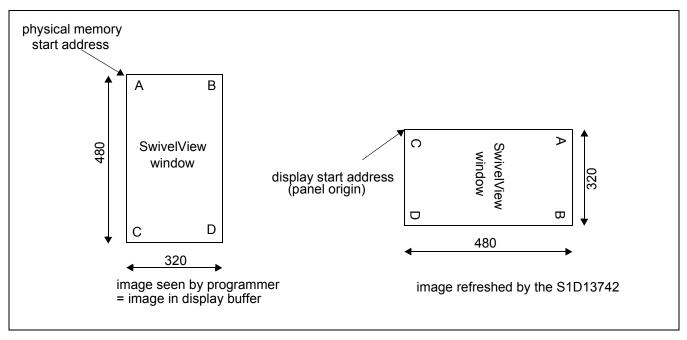

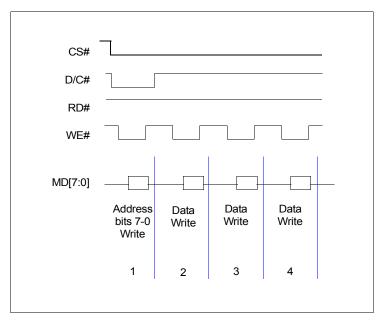

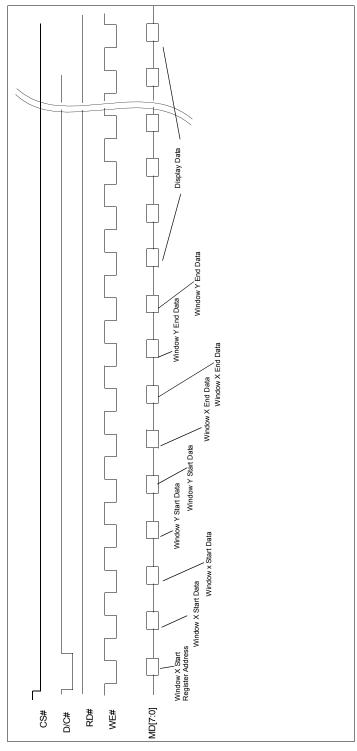

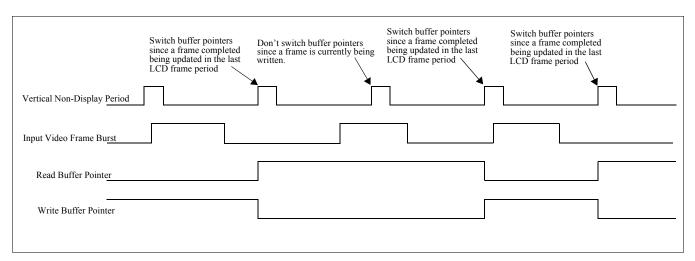

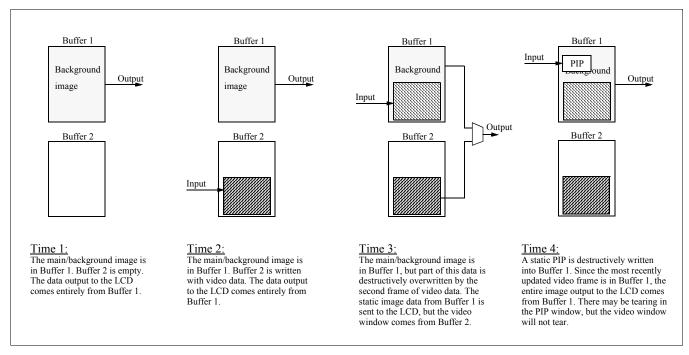

|              | t <sub>w2r</sub>  | WR# rising edge to RD# falling edge        | 16                                | _            | ns   | Note 1      |