19-4564; Rev 0; 4/09

EVALUATION KIT AVAILABLE 7-Bit, Programmable VCOM Reference with 30x MOTP Memory

## **General Description**

The MAX9660 provides a programmable reference voltage for VCOM adjustment in TFT-LCD panels. A 7-bit, current digital-to-analog converter (DAC) sinks current from an external resistor-divider string to create the VCOM reference voltage, which then serves as the input to a voltage buffer capable of driving out high current.

The MAX9660 includes multiple one-time programmable (MOTP) memory to store the DAC code on the chip, eliminating the need for external EEPROM. The chip supports up to 30 write operations to MOTP memory.

The MAX9660 has an I $^2\mathrm{C}$  interface to set the VCOM reference voltage and write into MOTP memory.

### **Applications**

TFT-LCD Panels

Instrumental Control Voltage Source

## **Ordering Information**

| PART        | TEMP RANGE      | PIN-PACKAGE |

|-------------|-----------------|-------------|

| MAX9660ATA+ | -40°C to +125°C | 8 TDFN-EP*  |

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*EP = Exposed pad.

# Features

- VCOM Amplifier with 900mA Peak Output Current

- Integrated Nonvolatile Memory to Store VCOM Setting

- ♦ 7-Bit, Adjustable Sink-Current Device

- ◆ Resistor-Adjustable, Full-Scale Range

- ♦ 2.5V to 3.6V Logic Supply Range

- ♦ 8V to 20V Analog Supply Range

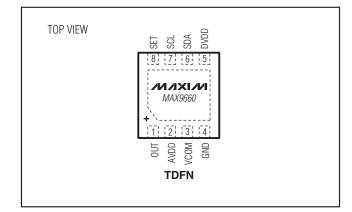

### Pin Configuration

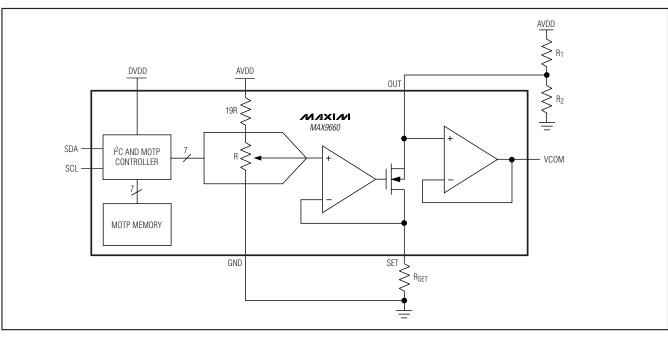

# **Functional Diagram**

###

\_\_\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

Supply Voltage

**MAX9660**

| Supply vollage                 |                     |

|--------------------------------|---------------------|

| DVDD, SET, SCL, and SDA to GND | 0.3V to +4V         |

| AVDD to GND                    | 0.3V to +22V        |

| OUT to GND                     | 0.3V to +22V        |

| VCOM to GND                    | 0.3V to AVDD + 0.3V |

| Continuous Current             |                     |

| SDA                            | 10mA                |

| VCOM                           | ±100mA              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 8-Pin TDFN-EP (derate 18.5mW/°C above                 | +70°C)         |

| Single-Layer Board                                    | 1481mW         |

| 8-Pin TDFN-EP (derate 24.4mW/°C above                 | +70°C)         |

| Multilayer Board                                      | 1951mW         |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             |                |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(V_{DVDD} = 3.3V, V_{AVDD} = 16V, V_{GND} = 0, R_{SET} = 6.8k\Omega$ , no load,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                           | SYMBOL          | CONDITIONS                                                                                             | MIN                        | TYP  | MAX            | UNITS |

|-----------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------|----------------------------|------|----------------|-------|

| SUPPLIES                                            |                 |                                                                                                        |                            |      |                |       |

| Digital Supply Voltage Range                        | Vdvdd           |                                                                                                        | 2.5                        | 3.3  | 3.6            | V     |

| Analog Supply Voltage Range                         | Vavdd           |                                                                                                        | 8                          |      | 20             | V     |

| Analog Quiescent Current                            | IAVDD           |                                                                                                        |                            | 4.5  | 10             | mA    |

| Analog Supply Current Range for<br>Programming MOTP | IAVDD           | $T_{A} = +25^{\circ}C$                                                                                 |                            | 15   | 20<br>45       | mA    |

| Digital Quiescent Current                           | IDVDD           | $T_{A} = +85^{\circ}C$                                                                                 |                            | 200  | 43<br>500      | μA    |

| MOTP Programming Times                              | MOTPSET         |                                                                                                        | 30                         |      |                | Times |

| VCOM OUTPUT (VCOM)                                  |                 |                                                                                                        |                            |      |                |       |

| Common-Mode Range                                   |                 |                                                                                                        | 0.2                        |      | Vavdd<br>- 0.2 | V     |

| Total Output Error                                  | VERR            | $T_A = +25^{\circ}C$ ,<br>V <sub>VCOM</sub> from 2V to V <sub>AVDD</sub> - 2V                          | -22                        |      | +22            | mV    |

| Output Voltage Swing Low                            | V <sub>OL</sub> | $I_L = -5mA, V_{OUT} = 0$                                                                              |                            |      | 150            | mV    |

| Output Voltage Swing High                           | V <sub>OH</sub> | IL = +5mA, V <sub>OUT</sub> = V <sub>AVDD</sub>                                                        | V <sub>AVDD</sub><br>- 150 |      |                | mV    |

| Output Load Regulation                              | LR              | $I_{L} = -80 \text{mA} \text{ to } +80 \text{mA}$                                                      |                            | ±0.2 |                | mV/mA |

| Chart Circuit Current (Nate 2)                      |                 | VCOM = AVDD                                                                                            |                            | -900 |                |       |

| Short-Circuit Current (Note 2)                      | I <sub>SC</sub> | VCOM = GND                                                                                             |                            | +900 |                | mA    |

| Power-Supply Rejection Ratio                        | PSRR            | $8V \le V_{AVDD} \le 20V, V_{OUT} = 5V$                                                                | 70                         |      |                | dB    |

| Slew Rate                                           | SR              | $4V_{P-P}$ at VCOM, 10% to 90%, $R_L = 10k\Omega$ , $C_L = 20pF$                                       |                            | 45   |                | V/µs  |

| Bandwidth                                           | dB              | $\label{eq:RL} \begin{split} R_L &= 10 k \Omega,  C_L = 20 pF, \\ V_VCOM &= 100 m V_{P-P} \end{split}$ |                            | 20   |                | MHz   |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDD} = 3.3V, V_{AVDD} = 16V, V_{GND} = 0, R_{SET} = 6.8k\Omega$ , no load,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                       | SYMBOL                            | CONDITIONS                                        | MIN                        | ТҮР   | MAX                        | UNITS |

|-------------------------------------------------|-----------------------------------|---------------------------------------------------|----------------------------|-------|----------------------------|-------|

| DVR                                             |                                   |                                                   |                            |       |                            |       |

| OUT Voltage Range                               | Vout                              |                                                   | V <sub>SET</sub> +<br>0.5V |       | 20                         | V     |

| Resolution                                      | RES                               |                                                   | 7                          |       |                            | Bits  |

| Integral Nonlinearity Error                     | INL                               |                                                   |                            | 0.125 |                            | LSB   |

| Differential Nonlinearity Error                 | DNL                               |                                                   |                            | 0.125 |                            | LSB   |

| AVDD to V <sub>SET</sub> Ratio                  | AVDD/V <sub>SET</sub>             |                                                   |                            | 20:1  |                            | V/V   |

| Set External Resistance                         | R <sub>SET</sub>                  | V <sub>AVDD</sub> = 8V<br>V <sub>AVDD</sub> = 18V | 3.35<br>6.75               |       | 67<br>135                  | kΩ    |

| Set Current                                     | ISET                              | Through R <sub>SET</sub>                          |                            |       | 134                        | μA    |

| Set Zero-Scale Error                            | SETZSE                            |                                                   |                            |       | ±2                         | LSB   |

| Set Full-Scale Error                            | SET <sub>FSE</sub>                |                                                   |                            |       | ±4                         | LSB   |

| LOGIC INPUTS (SDA, SCL)                         | ·                                 | ·                                                 | ·                          |       |                            |       |

| Input High Voltage                              | VIH                               |                                                   | 0.7 x<br>V <sub>DVDD</sub> |       |                            | V     |

| Input Low Voltage                               | VIL                               |                                                   |                            |       | 0.3 x<br>V <sub>DVDD</sub> | V     |

| SDA Output Low Voltage                          | V <sub>OL</sub>                   | I <sub>SINK</sub> = 6mA                           |                            |       | 0.4                        | V     |

| Input Leakage Current                           | I <sub>IH</sub> , I <sub>IL</sub> | 0V or V <sub>DVDD</sub>                           | -3                         | 0.01  | +3                         | μA    |

| Input Capacitance                               |                                   |                                                   |                            | 5     |                            | рF    |

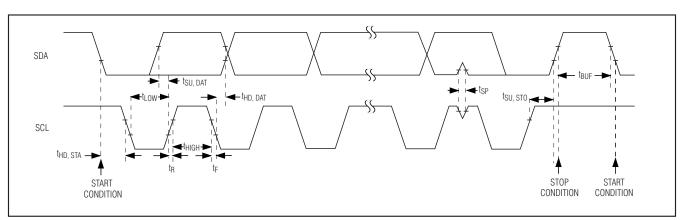

| I <sup>2</sup> C TIMING CHARCTERISTICS          |                                   |                                                   |                            |       |                            |       |

| Serial-Clock Frequency                          | fSCL                              |                                                   | 0                          |       | 400                        | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF                              |                                                   | 1.3                        |       |                            | μs    |

| Hold Time START Condition                       | <sup>t</sup> hd, sta              |                                                   | 0.6                        |       |                            | μs    |

| SCL Pulse-Width Low                             | tLOW                              |                                                   | 1.3                        |       |                            | μs    |

| SCL Pulse-Width High                            | thigh                             |                                                   | 0.6                        |       |                            | μs    |

| Setup Time for a START<br>Condition             | ts∪, sta                          |                                                   | 0.6                        |       |                            | μs    |

| Data Hold Time                                  | thd, dat                          |                                                   | 0                          |       | 900                        | ns    |

| Data Setup Time                                 | tsu, dat                          | (Note 3)                                          | 100                        |       |                            | ns    |

| SDA and SCL Receiving Rise<br>Time              | t <sub>R</sub>                    | (Note 4)                                          | 20 +<br>0.1C <sub>B</sub>  |       | 300                        | ns    |

| SDA and SCL Receiving Fall<br>Time              | tF                                | (Note 4)                                          | 20 +<br>0.1C <sub>B</sub>  |       | 300                        | ns    |

| SDA Transmitting Fall Time                      | tF                                | (Note 4)                                          | 20 +<br>0.1C <sub>B</sub>  |       | 250                        | ns    |

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DVDD} = 3.3V, V_{AVDD} = 16V, V_{GND} = 0, R_{SET} = 6.8k\Omega$ , no load,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                       | SYMBOL | CONDITIONS | MIN | ТҮР | МАХ | UNITS |

|---------------------------------|--------|------------|-----|-----|-----|-------|

| Bus Capacitance                 | CB     |            |     |     | 400 | рF    |

| Pulse Width of Suppressed Spike | tsp    |            | 0   |     | 50  | ns    |

**Note 1:** All devices are 100% production tested at  $T_A = +25^{\circ}C$ . Specifications over temperature limits are guaranteed by design. **Note 2:** Short-circuit current is for a 1µs pulsed current only, not to exceed thermal characteristics of package.

Note 3: Data hold time is tested in receive mode only.

Note 4: C<sub>B</sub> is in pF.

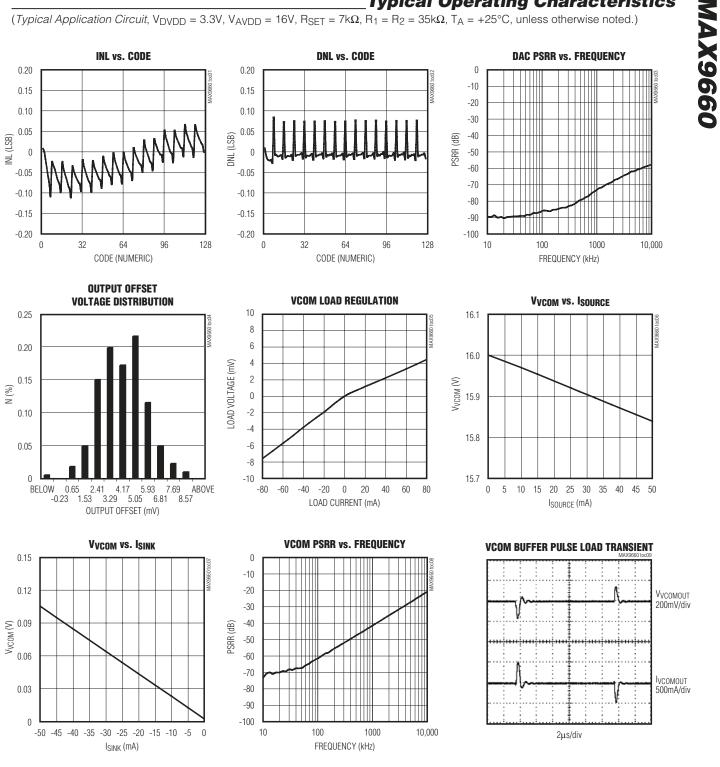

# **Typical Operating Characteristics**

(*Typical Application Circuit*,  $V_{DVDD} = 3.3V$ ,  $V_{AVDD} = 16V$ ,  $R_{SET} = 7k\Omega$ ,  $R_1 = R_2 = 35k\Omega$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

5

## **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                 |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT  | Adjustable Sink Current for Integrated VCOM Voltage Buffer. OUT connects to the resistive voltage-<br>divider between AVDD and GND.                                                                                                                      |

| 2   | AVDD | Analog Power Supply. Bypass AVDD with 0.1µF and 10µF capacitors in parallel to GND.                                                                                                                                                                      |

| 3   | VCOM | VCOM Output                                                                                                                                                                                                                                              |

| 4   | GND  | Ground                                                                                                                                                                                                                                                   |

| 5   | DVDD | Digital Power Supply. Bypass DVDD with 0.1µF capacitor to GND.                                                                                                                                                                                           |

| 6   | SDA  | I <sup>2</sup> C-Compatible Serial-Data Input/Output                                                                                                                                                                                                     |

| 7   | SCL  | I <sup>2</sup> C-Compatible Serial-Clock Input                                                                                                                                                                                                           |

| 8   | SET  | Full-Scale Sink-Current Adjustment Input. Connect a resistor, R <sub>SET</sub> , from SET to GND to set the full-scale adjustable sink current. The full-scale adjustable sink current is equal to:<br>$\left(\frac{V_{AVDD}}{20 \times R_{SET}}\right)$ |

|     | EP   | Exposed Pad. Connect EP to GND.                                                                                                                                                                                                                          |

## **Detailed Description**

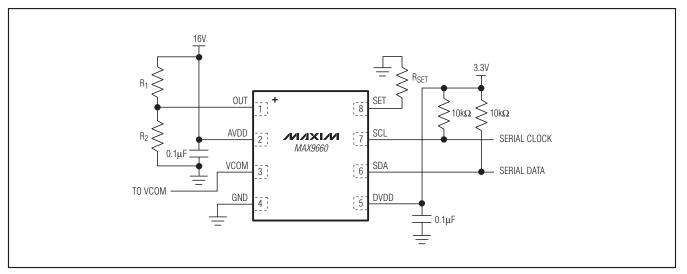

The MAX9660, a programmable VCOM buffer, replaces the mechanical potentiometer that is used for adjusting the VCOM voltage with an electrical solution (see the *Typical Application Circuit*). The MAX9660 attaches to an external resistor-divider (resistors R<sub>1</sub> and R<sub>2</sub>) and sinks a programmable current I<sub>OUT</sub> to create the VCOM reference voltage. The resolution of the current DAC that generates I<sub>OUT</sub> is 7 bits. The DAC is ratiometric relative to V<sub>AVDD</sub> and is monotonic over all operating conditions. The external resistor R<sub>SET</sub> sets the full-scale sink current and the minimum value of the VCOM reference voltage. The external resistor-divider and the AVDD supply set the maximum value of the VCOM reference voltage.

The VCOM reference voltage is the input to the integrated voltage buffer, which can source and sink 900mA so that VCOM can quickly recover after a polarity inversion or a horizontal line change. The MAX9660 features output short-circuit protection and soft-start to reduce inrush current.

The user can store the DAC setting in a type of nonvolatile memory known as MOTP. On power-up, MOTP sets the DAC register to the last stored setting. The DAC register and the MOTP can be programmed through the I<sup>2</sup>C interface.

#### 7-Bit DAC

An internal 7-bit DAC sinks current  $\mathsf{I}_{\mathsf{OUT}}.$  The following equations determine the value of  $\mathsf{I}_{\mathsf{OUT}}:$

$$I_{OUT} = \left(\frac{CODE + 1}{2^N}\right) \times \left(\frac{V_{AVDD}}{20 \times R_{SET}}\right)$$

where CODE is the numeric value of the DAC's binary input code and N is the bits of resolution. For the MAX9660, N = 7 and CODE ranges from 0 to 127.

The MAX9660 pulls I<sub>OUT</sub> through the external resistordivider comprised of R<sub>1</sub> and R<sub>2</sub>. The resulting voltage V<sub>OUT</sub> is given by the following formula:

$$V_{VCOM} = \left(\frac{R_2}{R_1 + R_2}\right) \times V_{AVDD} \times \left(1 - \left(\frac{CODE + 1}{128}\right) \left(\frac{R_1}{20 \times R_{SET}}\right)\right)$$

#### VCOM Amplifier

The buffer attached to V<sub>OUT</sub> holds the VCOM voltage stable while providing the ability to source and sink 900mA into the backplane of a TFT-LCD panel. The buffer can directly drive the capacitive load of the TFT-LCD backplane without the need for a series resistor in most cases. The VCOM amplifier has current limiting on its output to protect its bond wires.

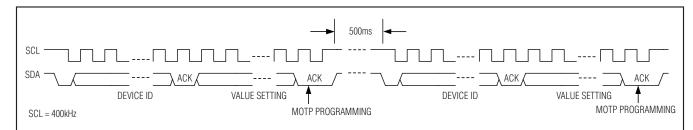

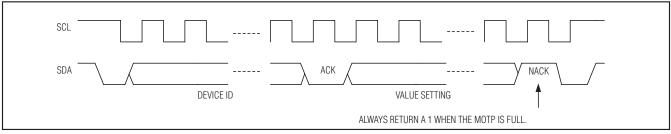

Figure 1. MOTP programming interval. Wait 500ms after issuing a write command to MOTP memory before starting another write command to MOTP memory.

Figure 2. Example of a write command to MOTP memory after MOTP memory is full. The MAX9660 responds with a NACK.

#### Multiple One-Time Programmable Memory (MOTP) Programming

DAC codes can be written into MOTP memory up to 30 times because the MOTP memory is a bank of 30 onetime programmable registers. See the *Write Data Format* section for a description of how to use the I<sup>2</sup>C interface to write data into MOTP.

After an I<sup>2</sup>C write operation to MOTP memory, the MAX9660 requires a maximum of 500ms to burn the data into the MOTP register (see Figure 1). During this time, do not perform another write operation to MOTP memory. If a write operation to MOTP memory is attempted during this time, the MAX9660 responds with a not acknowledge (NACK).

The MAX9660 integrates MOTP memory that can be programmed 30 times. After 30 writes to MOTP memory, the MAX9660 responds with a not acknowledge (NACK) to all future write attempts (see Figure 2).

#### I<sup>2</sup>C Serial Interface

The MAX9660 features an I<sup>2</sup>C/SMBus<sup>™</sup>-compatible, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the MAX9660 and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The master generates

SMBus is a trademark of Intel Corp.

device writes data to the MAX9660 by transmitting the proper slave address followed by the data word. Each transmit sequence is framed by a START (S) condition and a STOP (P) condition. Each word transmitted to the MAX9660 is 8 bits long and is followed by an acknowledge clock pulse. A master reading data from the MAX9660 transmits the proper slave address followed by a series of nine SCL pulses. The MAX9660 transmits data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START condition, a not acknowledge, and a STOP condition. SDA operates as both an input and an open-drain output. A pullup resistor, typically greater than 500 $\Omega$ , is required on the SDA bus. SCL operates as only an input. A pullup resistor, typically greater than 500 $\Omega$ , is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output. Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX9660 from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

SCL and initiates data transfer on the bus. A master

7

**MAX9660**

Figure 3. I<sup>2</sup>C Serial-Interface Timing Diagram

#### **Table 1. Slave Address**

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0  | WRITE ADDRESS | READ ADDRESS |

|----|----|----|----|----|----|----|-----|---------------|--------------|

| 1  | 0  | 0  | 1  | 1  | 1  | 1  | R/W | 0x9E          | 0x9F         |

#### Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

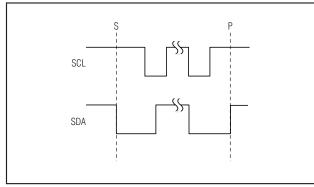

#### START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 4). A START condition from the master signals the beginning of a transmission to the MAX9660. The master terminates transmission, and frees the bus, by issuing a STOP condition.

#### Early STOP Conditions

The MAX9660 recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition. For proper operation, do not send a STOP condition during the same SCL high pulse as the START condition.

#### Slave Address

The slave address is defined as the 7 most significant bits (MSBs) followed by the read/write ( $R/\overline{W}$ ) bit. Set the  $R/\overline{W}$  bit to 1 to configure the MAX9660 to read mode.

Set the R/W bit to 0 to configure the MAX9660 to write mode. The address is the first byte of information sent to the MAX9660 after the START condition. Table 1 shows the possible addresses for the MAX9660.

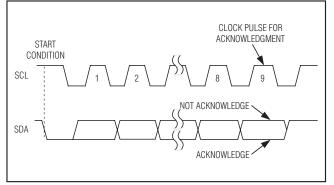

#### Acknowledge

The acknowledge bit (ACK) is a clocked ninth bit that the MAX9660 uses to handshake receipt of each byte of data when in write mode (see Figure 5). The MAX9660 pulls down SDA during the entire mastergenerated ninth clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master may retry communication. The master pulls down SDA during the ninth clock cycle to acknowledge receipt of data when the MAX9660 is in read mode. An acknowledge bit is sent by the master after each read byte to allow data transfer to continue. A not-acknowledge bit is sent when the master reads the final byte of data from the MAX9660, followed by a STOP condition.

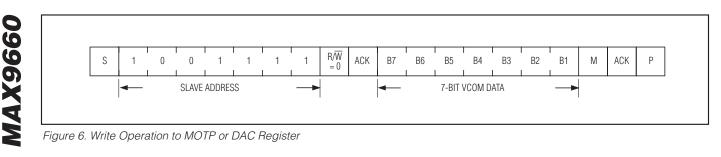

#### Write Data Format

A write to the MAX9660 consists of transmitting a START condition, the slave address with the R/W bit set to 0, 7-bit data, M bit, and a STOP condition. Figure 6 illustrates the proper frame format for writing 7 bits of data to the MAX9660. The slave address with the R/W bit set to 0 indicates that the master intends to write

Figure 4. START and STOP Conditions

Figure 5. Acknowledge

## \_Register Map

**MAX9660**

| REG  | B7 | B6 | B5 | B4 | B3 | В3 | B1 | В0 | FACTORY<br>INITIALIZATION | R/W |

|------|----|----|----|----|----|----|----|----|---------------------------|-----|

| VCOM | d6 | d5 | d4 | d3 | d2 | d1 | d0 | М  | 64                        | R/W |

## Table 2. I2C Register

| BITS  | DESCRIPTION                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7:B1 | 7-bit DAC data                                                                                                                                                                                           |

|       | Data location indicator (M bit). The M bit identifies the register for the data to be written to.<br>M = 0, the data is written to the MOTP register.<br>M = 1, the data is written to the DAC register. |

data to the MAX9660. The MAX9660 acknowledges receipt of the address byte during the master-generated ninth SCL pulse. The second byte sent to the MAX9660 contains the 7-bit data that is written to the DAC latch or MOTP. The M bit after bit B1 identifies the register to be written to, as shown in Table 2. When M = 0, the MOTP is written to, and when M = 1, the DAC register is written to. An acknowledge pulse from the MAX9660 signals receipt of the VCOM data byte. The master signals the end of transmission by issuing a STOP condition.

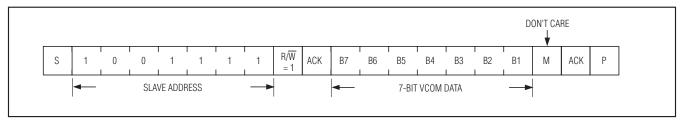

#### Read Data Format

The master presets the address pointer by first sending the MAX9660's slave address with the R/W bit set to 1 after a START condition. The MAX9660 acknowledges receipt of its slave address and the register address by pulling SDA low during the ninth SCL clock pulse. The MAX9660 transmits the contents of the DAC register as 7-bit data and the eighth bit, M, is don't care. Transmitted data is valid on the rising edge of the master-generated serial clock (SCL). A STOP condition is issued after reading the data byte. The master acknowledges receipt of the read byte during the acknowledge clock pulse. The final byte must be followed by a not acknowledge from the master and then a STOP condition. Figure 7 illustrates the frame format for reading data from the MAX9660.

# Applications Information

#### **Power-Up and Power-Down Operation**

During power-up, the digital supply must be powered up first. The analog supply should not be powered up until the digital supply has stabilized. During this time, the MOTP register value is loaded into the DAC register (0x40 is the factory-programmed default). Once AVDD is above approximately 7V, the VCOM amplifier has enough headroom and powers up proportionally with AVDD.

For power-down, AVDD must be powered down first to 0V, and then DVDD can safely be powered down.

Figure 7. Read Operation to MOTP or DAC Register

#### **Power Supplies and Bypass Capacitors**

The MAX9660 operates from a single 8V to 20V analog supply (AVDD) and a 2.5V to 3.6V digital supply (DVDD). Bypass AVDD to GND with 0.1 $\mu$ F and 10 $\mu$ F capacitors in parallel. Use an extensive ground plane to ensure optimum performance. Bypass DVDD to GND with a 0.1 $\mu$ F capacitor. The 0.1 $\mu$ F bypass capacitors should be placed as close as possible to their respective pins.

Refer to the MAX9660 evaluation kit for a proven PCB layout.

#### **Layout and Grounding**

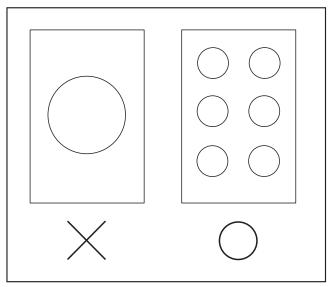

#### Exposed Pad

The exposed pad on the TDFN package is electrically connected to GND. Solder the exposed pad to a ground plane to provide a low thermal resistance to ground for heat dissipation. Do not route traces under these packages. The layout of the exposed pad should have multiple small through-holes over a single large through-hole as shown as Figure 8. Thermal resistance between top and ground layer can be reduced. In addition, the vias should be flooded with solder for best thermal performance.

Figure 8. Multiple small through-holes are recommended over a single large through-hole in PCB layout.

# **Typical Application Circuit**

**Chip Information**

PROCESS: BiCMOS

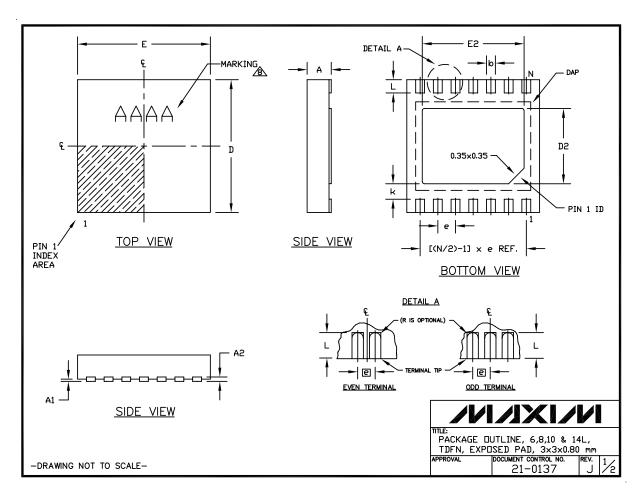

## **Package Information**

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 8 TDFN-EP    | T833+2       | <u>21-0137</u> |

**MAX9660**

## Package Information (continued)

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages.

| COMMON                                                                      |                                                                    | ISIONS                                                                                     | PACKAGE V                                                                                                                                                                | ARIAT                                 | IONS                                              |            |             |                |           |               |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------------------------------|------------|-------------|----------------|-----------|---------------|

| SYMBOL                                                                      | MIN.                                                               | MAX.                                                                                       | PKG. CODE                                                                                                                                                                | Ν                                     | D2                                                | E2         | е           | JEDEC SPEC     | b         | [(N/2)-1] x e |

| А                                                                           | 0.70                                                               | 0.80                                                                                       | T633-2                                                                                                                                                                   | 6                                     | 1.50±0.10                                         | 2.30±0.10  | 0.95 BSC    | MO229 / WEEA   | 0.40±0.05 | 1.90 REF      |

| D                                                                           | 2.90                                                               | 3.10                                                                                       | T833-2                                                                                                                                                                   | 8                                     | 1.50±0.10                                         | 2.30±0.10  | 0.65 BSC    | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| E                                                                           | 2.90                                                               | 3.10                                                                                       | T833-3                                                                                                                                                                   | 8                                     | 1.50±0.10                                         | 2.30±0.10  | 0.65 BSC    | MO229 / WEEC   | 0.30±0.05 | 1.95 REF      |

| A1                                                                          | 0.00                                                               | 0.05                                                                                       | T1033-1                                                                                                                                                                  | 10                                    | 1.50±0.10                                         | 2.30±0.10  | 0.50 BSC    | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

| L                                                                           | 0.20                                                               | 0.40                                                                                       | T1033MK-1                                                                                                                                                                | 10                                    | 1.50±0.10                                         | 2.30±0.10  | 0.50 BSC    | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

| k                                                                           | 0.25                                                               | MIN.                                                                                       | T1033-2                                                                                                                                                                  | 10                                    | 1.50±0.10                                         | 2.30±0.10  | 0.50 BSC    | MO229 / WEED-3 | 0.25±0.05 | 2.00 REF      |

| A2                                                                          | 0.20                                                               | REF.                                                                                       | T1433-1                                                                                                                                                                  | 14                                    | 1.70±0.10                                         | 2.30±0.10  | 0.40 BSC    |                | 0.20±0.05 | 2.40 REF      |

|                                                                             |                                                                    |                                                                                            | T1433-2                                                                                                                                                                  | 14                                    | 1.70±0.10                                         | 2.30±0.10  | 0.40 BSC    |                | 0.20±0.05 | 2.40 REF      |

|                                                                             |                                                                    |                                                                                            | T1433-3F                                                                                                                                                                 | 14                                    | 1.70±0.10                                         | 2.30±0.10  | 0.40 BSC    |                | 0.20±0.05 | 2.40 REF      |

| 2. COPL<br>3. WARP<br>4. PACK<br>5. DRAW<br>6. "N" IS<br>7. NUME<br>8. MARK | ANARITY<br>AGE SH<br>AGE LE<br>ING CO<br>S THE<br>BER OF<br>ING IS | ' SHALL NO<br>IALL NOT E<br>NGTH/PACK<br>NFORMS TO<br>TOTAL NUMI<br>LEADS SHO<br>FOR PACKA | N mm. ANGLES IN<br>IT EXCEED 0.08 m<br>XCEED 0.10 mm.<br>AGE WIDTH ARE CC<br>) JEDEC M0229, E<br>BER OF LEADS.<br>WN ARE FOR REFI<br>AGE ORIENTATION R<br>TO BOTH LEADED | m.<br>DNSID<br>XCEP<br>EREN(<br>EFER) | ERED AS S<br>T DIMENSIO<br>CE ONLY.<br>ENCE ONLY. | NS "D2" AN | ID "E2", AN |                | 1433–2.   |               |

|                                                                             |                                                                    |                                                                                            |                                                                                                                                                                          |                                       |                                                   |            |             |                |           |               |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_\_\_ 13

Maxim is a registered trademark of Maxim Integrated Products, Inc.